高度な技術プロセスによって製造されたチップを自動車に追加し、データセンターでの使用モデルを変更するプロセスでは、信頼性に関連する新しい疑問が生じ始めます。

信頼性は、自動車、クラウドコンピューティング、産業用モノのインターネットなどの市場に参入する新しいチップにとって重要な利点の1つになりつつありますが、チップが長期にわたって機能することを証明するのはますます困難になっています。

過去には、通常、信頼性は集積回路工場の問題と考えられていました。 コンピューターと携帯電話用に設計されたチップは、ピーク時で動作するように設計されており、平均2〜4年の通常使用が可能です。 その後、機能が低下し始め、ユーザーは製品の次のリビジョンに更新され、新機能、速度、およびバッテリ寿命の延長を誇っていました。 しかし、新しい市場、または過去にあまり洗練されていない電子機器を使用していた市場の開発により、自動車、機械学習、モノのインターネット、産業のモノのインターネット、仮想現実および拡張現実、ホームオートメーション、クラウドテクノロジー、暗号通貨マイニング-信頼性は単純ではなくなりました大きなチェックリストのアイテム。

これらの各ターゲット市場は、チップの使用方法と使用条件を決定する固有のニーズと特性を示しています。 そして、これは順番に、彼らの老化、安全性、その他の要因に深刻な影響を及ぼします。 以下のステートメントを考慮してください。

- 信頼性は、長年にわたって単純に測定されることはなくなりました。 使用パターンは劇的に変化しています。 現代の車は、アイドル時間の90-95%の時間になる可能性があり、ロボモービルは5-10%の時間アイドル状態になります。 これは、電子機器の開発、および技術の開発で使用される主なビジネスモデルに影響します。

- 「機能的」または「十分に良い」と見なされるものの定義は、高度な電子機器が常により複雑になっているため、変化しています。 過去には、ひび割れまたは汚れたドローンまたはロボットカメラが交換されました。 しかし、高度なデバイスにさらに洗練された電子機器を追加することで、機能的に適切な動作の範囲内にとどまることにより、レンズのひび割れの影響を補うことができます。 一方、より複雑でないシステムで受け入れられたものは、システムの許容誤差が厳しくなるため、受け入れられないと見なすことができます。

- モデリングの劣化と品質は、以前よりもはるかに多くの要因の影響を受けます。これらの要因の一部は、チップを開発する際に明白ではない場合さえあります。 たとえば、高品質で知られているチップは、プリント回路基板上の他のチップまたはデバイスと組み合わせると異なる動作をする場合があります。

電子機器の使用は変化しています。 これは、新しいテクノロジーと方法論の適応に関して歴史的に最も保守的なデータセンターでも発生します。

「エージングはクロック速度と電力に依存しますが、以前はサーバーが作業を行うために時々電源がオンになり、その後ほとんどの時間はスタンバイモードでした」とARMの CEOであるSimon Sigars氏は述べています。 「クラウドテクノロジーに目を向けると、継続的な使用に基づいているため、開発基準を変更する必要があります。 これにより、長期的なパフォーマンスのためにチップを適切に設計する方法について多くの疑問が生じます。」

ミレニアムの初めには、平均サーバー負荷は5-15%のレベルでしたが、この傾向は1990年代から続いています。機器の故障を恐れるITスペシャリストは、1台のサーバーで1つまたは2つ以上のアプリケーションを実行することに消極的でした。 この状況を変更した2つのイベントが発生しました。 まず、エネルギーのコストが上昇し始めました。 第二に、さらに重要なこととして、企業は、IT部門が設備保守部門ではなく、使用されるエネルギーのコストを担当するように再編成されました。 両方の要因により、仮想化ソフトウェアの売上が増加し、サーバーの使用率が増加し、電源供給と冷却が必要なサーバーの数が減少しました。

クラウドコンピューティングは、運用効率を新たなレベルに引き上げます。 彼らの目標は、データセンター全体でコンピューティングタスクのバランスをとることにより負荷を最大化することです。 これにより、同じラック内のサーバーだけでなく、すべてのサーバーの負荷の割合を増やしたり、現在不要なサーバーをすばやくオフにしたりできます。 このアプローチはエネルギー使用の観点からは効果的ですが、電子回路の劣化と経年劣化に深刻な影響を及ぼします。

「チップが完全に故障するまで、老化の加速が見られます」と、Helicのマーケティング担当副社長、Magdi Abadir氏は述べています。 「彼らはビートを見逃し始めているか、ジッタが増加しています。 または、誘電体の故障があります。 そして、何かが故障するたびに、大事な雪崩が起こり、それも世話をする必要があります。 老化モデルの多くは、ケースバイケースで電子機器が使用されていたときに開発されました。 そして今、チップは常に動作します。 ブロックはチップ内部で加熱され、エージングを加速します。 このため、さまざまな奇妙な現象に遭遇する可能性があります。 多くの企業は、エージングモデルを更新していません。 彼らは、デバイスが3〜4年続くと推測しましたが、故障はもっと早く起こる可能性があります。 元の設計からの逸脱は最初から小さいかもしれませんが、経年変化はそれらを増加させます。

増加する負荷の傾向は車に浸透し、完全に自動化された車両が人間のドライバーに取って代わるまでそうし続けます。 ロボモバイルはますます多くの情報を処理していますが、その一部はレーダー、LIDAR、カメラなどのセンサーから流れます。 このデータはすべて、以前よりも高速に、より高い精度で処理する必要があります。これにより、電子機器に大きな負荷がかかります。

「 ADASの最小信頼性[ 高度な運転支援システム/約 perev。 ]は15年で、以前のモジュールでは2〜5年をはるかに超えています」とANSYSの最高技術責任者であるNorman Chen氏は述べています。 -高齢化とは、単に仕事の時間だけではありません。 NBTI [ 負のバイアス温度不安定性-しきい値電圧シフト/約。 perev。 ]、 エレクトロマイグレーション 、これは温度、ESD [ 静電放電 ]および熱結合に関連する可能性があります。

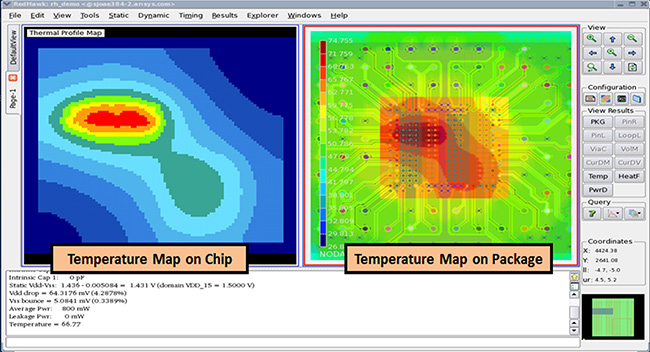

チップとハウジングの温度シミュレーション

多くの自動車部品サプライヤーは、極端な温度、機械的振動、およびさまざまなノイズレベルに耐えられるチップをすでに製造していますが、そのような負荷は、高度な製造プロセスを使用して製造されたCMOSチップに長い間適用されていません。 多くの業界関連の情報源は、すべてのデータの処理のために、自動車メーカーが10/7 nmプロセスを使用してチップを開発していることを確認しています。 問題は、環境にさらされたときに長時間動作するこれらのデバイスの信頼性を示す十分な量の実データがないことです。

「私たちは異なる設計をしなければなりません」とSegars氏は言いました。 -アイデアの1つによると、最終的には、ほとんどアイドル状態にならないため、必要な車は少なくなります。 しかし、別のことがあります:ロボモービルはより多くの仕事をし、より早く消耗します。 結局のところ、すべてが最終的に消耗します。 タスクは、電子機器がメカニクスよりも早く摩耗しないようにすることです。そのためには、異なるデザインを作成する必要があります。 より正確な態度からノイズまで、サージを最小限に抑えることすべてを考慮してください。」

より細かい絶縁、より薄い基板

信頼性を高めることの皮肉な側面の1つは、50年の進歩と矛盾することです。その目的は、経済上の理由から2年に1回、超小型回路素子のサイズを縮小することでした。 そして、これは通常、より薄い誘電体とワイヤの使用、および動的電力の増加を意味します。 そしてますます、これはより薄い基板を使用することを意味します。 最先端の技術プロセスでは、これにより電流リーク、ノイズ量、エレクトロマイグレーションなどの影響が増加しました。

Fraunhofer EASの品質および信頼性マネージャーであるAndre Lang氏は、「回路の観点から、プロセスのばらつきに何らかの形で対処する必要があります」と述べています。 -しかし、開発の観点からは、システムが既知の欠陥にどのように対処するかを考慮する必要があります。 ロボモービルを使用する場合、中央センサーを使用して、どのセンサーからどの情報を使用するかを決定する必要があります。 それらの1つは汚れているか、失敗する可能性があります。」

これは、システム全体のコンテキストで実行する必要があるため、モデリングの劣化をより困難にします。 「システムの大部分は、NBTI、単位面積あたりの欠陥数の増加、プロセスの逸脱など、電子回路の劣化の一因となります」とラング氏は述べています。 彼は、別の大きな問題は、利用可能なすべてのデータを処理せずに欠陥の原因を特定することであると指摘しました。

何がうまくいかないかの例

さまざまなアプローチ

プロセスの偏差は、新しい製造プロセスごとに増加します。 過去10年間で、スマートフォンが音色を確立しました(2007年にiPhoneが登場しました)。 現在、高度な技術プロセスの最大のユーザーは、データマイニング、機械学習、AI、クラウドサービスのサーバーです。

プロセス偏差と信頼性の関係について詳しく説明しますが、偏差があると、経年劣化に関連する影響を正確にモデル化することが難しくなります。 このため、この問題を解決するために、複雑な統計モデリングやシミュレーションから、チップ上のセンサーの位置や内部ケースまで、いくつかの異なるアプローチがすでに登場しています。

シノプシスの研究開発担当チーフエンジニアであるラルフアイバーソンは、次のように述べています。「ローカルおよびグローバルに機能するランダムウォークアプローチを使用して、熱源の温度上昇を追跡する必要があります。 「ランダムトラバーサルを使用すると、電圧が平均化されるため、デルタはゼロになります。」

これはモデルの構築に役立ちますが、5 nm以下のスケールの抵抗率は常に一定ではありません、とIversonは言います。 表面効果が役割を果たし、データは常に銅接触を表すとは限らないため、よりローカライズされたデータが必要です。 この分野では、このようなレベルの不確実性を抽象的に説明するのが難しいため、ハイブリッドアプローチが出現し始めています。

シーメンスビジネスのメンターマーケティングディレクターであるミックテゲトフは、次のように述べています。 -メーカーからの関心が高まっており、電子機器の設計の自動化に関与する企業は、負荷のかかったチップの経年劣化をすでにシミュレートしています。 これで十分ですか? どのモデルも、現実世界を近似するための試みにすぎません。 シミュレーションを実行し、長時間動作する必要があるチップを作成するためにできる限りのことを行いますが、物理テストに戻り、たとえば、チップをオーブンに入れて身体活動を作成する必要があります。 目の前で、ますます多くの電子機器がテストされています。」

アナログと数字

これまで、すべての陳腐化モデリングはデジタル回路に焦点を合わせてきました。 アナログシステムは、老化にまったく新しい視点を追加します。

「企業は老朽化プロセスに精通しており、エンジンコンパートメントに近い場所にあるチップのプロセス偏差があるため、盲目的に進みません」と、MoortecのCTOであるOliver King氏は述べています。 「しかし、アナログ回路では、ばらつきがはるかに大きくなります。」 デジタルチップは単に動作を停止します。 アナログは少し悪くなり、少し正確性が低下し始める可能性があるため、それに適応する必要があります。 従来、アナログシステムの開発者は、デジタルシステムの開発者ほど厳密なジオメトリ要件を提示していませんでした。 エレクトロマイグレーションは、電流密度と同様に依然として問題です。 しかし、老化の影響はそれほど顕著ではありません。 それでも、修理の条件と、何らかの措置を講じる必要があるかどうかを考えると、チップをより積極的に開発する必要があります。

ラムバスの製品管理担当シニアディレクターのフランクフェロも同意します。 「 PHYチップの主な問題は周囲温度です。 大きくなると、パフォーマンスは「フロート」状態になり始めるため、再キャリブレーションが必要です。 ユーザーには、いわゆる「クリスマステスト」があります。 これは、寒い季節にプレイステーションまたはその他の電子機器をガレージに保管し、クリスマスの朝に電源を入れると、デバイスがすぐに寒いモードから動作モードに切り替わる必要がある場合です。 同じことは、自動車や基地局のメモリシステムにも当てはまります。 老化はこれらのシステムに影響を及ぼし、悪影響を排除するために再調整する必要があります。

フェロによると、PHYは強制故障テスト、電圧、温度変動など、デジタルコンポーネントと同じテストに合格しています。 しかし、PHYはこれらの変動により変化するように設計されており、特に偏差が電力と速度に影響する高度な製造プロセスでは、デジタル回路に統合するのは非常に困難です。

アナログ回路は、多くの場合、いわゆる「ミッションプロファイル」に基づいて開発されます。 ロボモービルの特定の機能は、ロボモービル用に特別に設計された集積回路のサイクログラムです。

「私たちが遭遇した大きな問題の1つは、これらのデバイスをさまざまなケースで使用できることです」と、IC and PCB Groupのチーフマーケティング担当者であるArt Schaldenbrand氏は述べています。 -デバイスは多くの点で故障する可能性があります。 無効にするように設計されたさまざまな負荷を選択します。 温度が不安定になると、デバイスの10%が故障する可能性がありますが、これは最悪のシナリオです。 チップの劣化をより良く表現する方法が必要です。 finFETの場合、負荷はフラットとは異なるため、さまざまな現象をモデル化する必要があります。

シェルおよびその他の未知

ムーアの法則の減速に伴い、パフォーマンスと開発の柔軟性を向上させるために、ますます多くの企業が高度なパッケージングに目を向けています。 ストレスと老化を判断するための高度なパッケージングをモデル化する方法はまだ明確ではありません。 特に、非常に多数のパッケージングオプションが原因で問題が発生します。そのため、誰が勝つかがわからないのです。 また、これらの技術の一部の相対的な新規性にも影響され、ケース内で何が起こっているかを時間で示す必要があります。

「シェルレイヤーは、他のコンポーネントまたは負荷に近すぎる可能性があります」と、Helic Abadir氏は述べています。 -これらすべてをモデル化する必要があります。 また、陳腐化する前であっても、作業に影響を与える要因の数が増えているため、老化をモデル化する必要があります。 したがって、場所が重要になります。 回路の周囲でコンポーネントの移動を開始すると、共振周波数が変わります。 これには簡単なルールはありません。 スキーム全体を分析する必要があります。問題が発生した場合は、何かを移動する必要があります。」

複雑な回路では、時間の経過とともに信頼性に影響を与える可能性のある他の異常があります。 一部の使用パターンは、他のパターンよりも頻繁に回路のオンとオフを切り替えることができ、負荷が大きくなります。

ケイデンスのチーフソフトウェアアーキテクトであるJusan Syaiは、次のように述べています。 -デバイスが小さいほど、老化の影響が強くなります。 負荷が高くなり、エージングが速くなります。」

説明されているすべての問題に対処する方法は、まだ完全には理解されていません。 それらのいくつかは、明らかに新しい材料と技術を必要とします。

「パワーエレクトロニクスは、シリコンデバイスから、より高いスイッチング周波数で、より効率的に、より高い温度で動作できるSiCおよびGaNに移行しています」と、メンターのエレクトロニクスの産業マーケティングディレクター、ジョンペリーは述べています。 「場合によっては、これにより、パワーエレクトロニクスをモーターの近く、つまりより高い温度条件に配置できるようになります。 他の場合では、より高い温度に耐えることができる半導体の使用は、冷却需要が少ないことを意味します。 ただし、半導体は密閉する必要があり、その後、このエンクロージャは高温にも耐える必要があります。多くのお金が新しい技術に注がれています-例えば、水晶を植えるための材料として使用される焼結銀、ワイヤ接続の代わりにクリップ、IGBTのようなパワーデバイスのパッケージングは、材料、処理および開発技術の面で劇的な変化を受けます」

おわりに

高度な技術プロセスに切り替えたり、デバイスの安全性が重要な市場で長期間使用したりすると、老化、ストレス、その他の影響がますます問題を引き起こしているという事実に対する態度。

「出発点は、顧客が今日私たちに質問をしていることです」とラングは言いました。 -開始点はクライアントごとに異なりますが、質問がよく寄せられます。多くはこの問題に対処し始めたばかりです。それらは電圧または温度の上昇に直面しており、過剰な負荷の影響を推定するために特定の実験が行われています。しかし、劣化がスキーム全体にどのように影響するかを正確に理解することは困難です。複雑なチップにはさらに多くの作業が必要です。」

しかし、態度の変化に伴い、これらの問題を解決するための人々の貢献も変わります。チップ開発者は、モデリングの劣化とエージングについて考え始めています。10年前のパワーエレクトロニクスと同様、これらはすべて間もなく変更されます。