はじめに

一部の人々にとって、FPGA SoCは理解を超えたものであり、この記事ではこの誤解を修正する必要があります。 空のプロジェクトから燃えるLEDまで、プログラムの作成をゼロから分析しましょう。 そもそも、プロジェクトはDE1-SoCデバッグボードで実行されたものであり、このマニュアルを扱っていれば、アルテラボードを使用して他のボードに簡単に適合させることができます。 さあ始めましょう!

FPGAファームウェアの作成

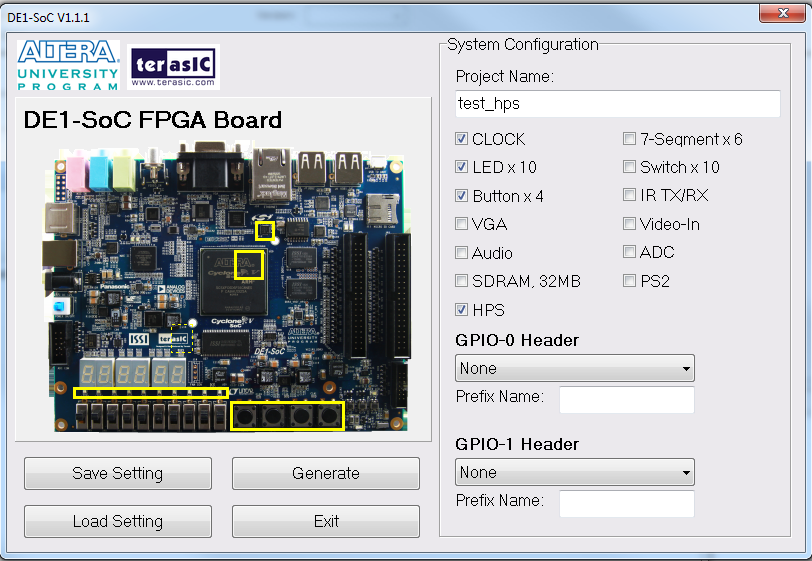

ファームウェアを作成するには、明らかにQuartusプロジェクトが必要です。 ただし、このプロジェクトは標準的な方法(プロジェクトウィザードを使用)ではなく、DE1-SoCボードに付属のユーティリティを使用して作成します。

このユーティリティは、Verilogで記述された最上位ファイルを生成し、選択した要素の宣言を含めます。 CLOCK、HPS(SoC)、ボタン、LEDが必要です。 [生成]をクリックすると、Quartusプロジェクトが取得されます。 この方法でプロジェクトを作成する主な利点は、ユーティリティが私たちのためにこれを行ったため、FPGAピンをPin Plannerに割り当てる必要がなく、それにより多くの時間を節約できることです。

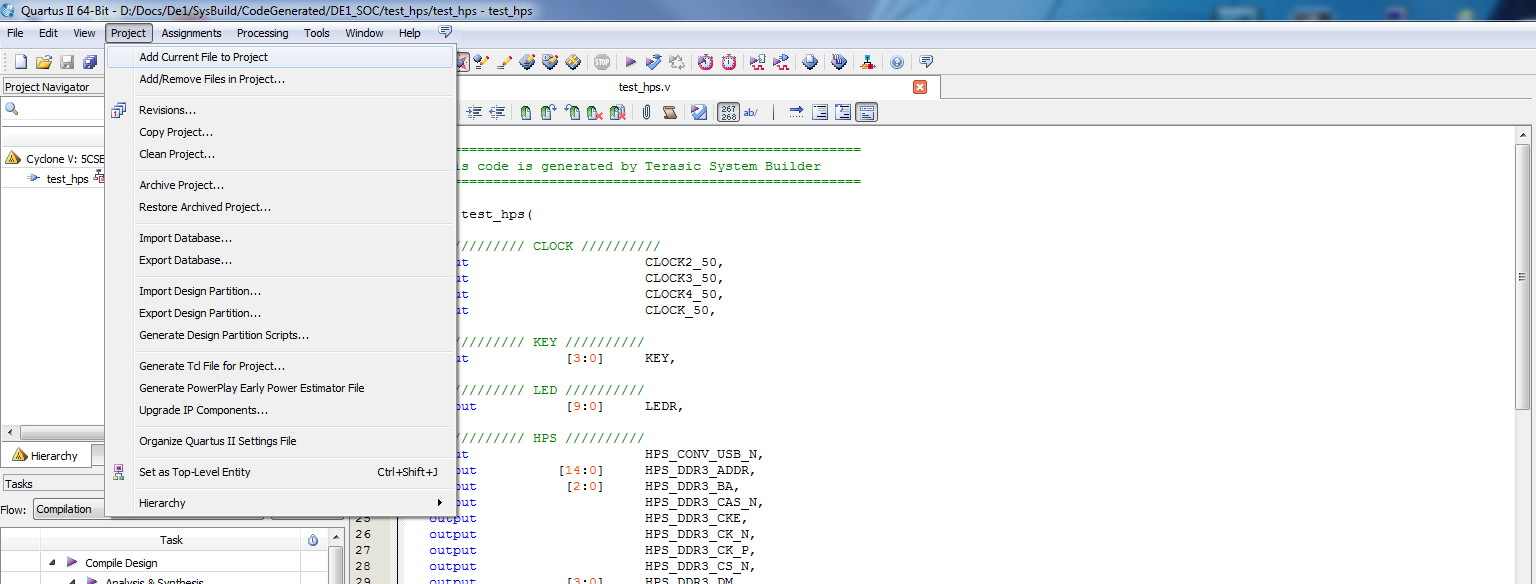

生成されたファイルをプロジェクトに追加します。

次のステップは、QSYSでシステムを作成することです。 念のために、私は何が起こっているかの本質を簡単に説明します。 Cyclone V SoCは単なるFPGAではなく、その構造内に、USBポート、イーサネット、SPI、SD / MMCなどのさまざまなモジュールを備えたデュアルコアCortex-A9プロセッサがあります。 簡単な方法で、これはFPGA内のマイクロコントローラーとして想像できます。 QSYSでシステムを作成し、HPS(ハードプロセッサシステム)システムを既製のカーネル(IPコア)を使用してFPGAで合成された要素に接続します。 QSYSでは、不必要な心配なしにAvalon-MMまたはAMBA AXIバスを介して異なるコアを接続できます。手動でコードを記述する必要はなく、QSYSが生成します。 QSYSに移動し、[IPコア]タブでHPSシステムを選択します。 システム設定では、FPGAインターフェイスタブにあるLightweight H2F Bridgeのみが必要です。

[Peripheral Pins]タブで、SD / MMC(プログラムから読み込むカードから)およびUARTを選択します。 これについては後で詳しく説明します。

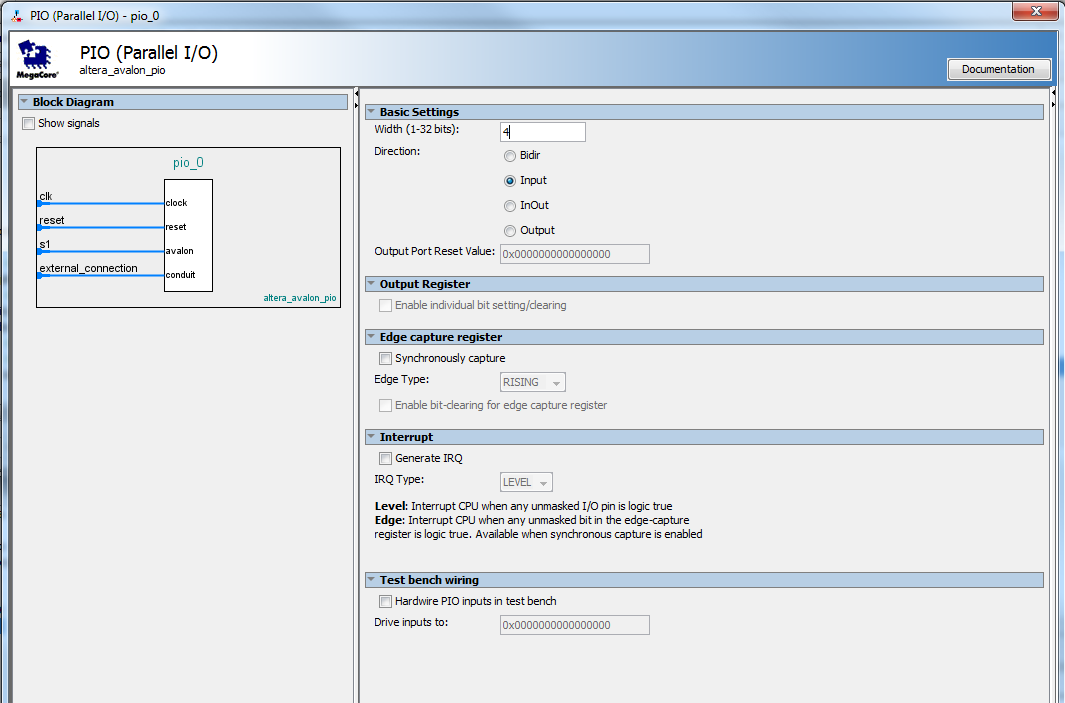

[HPSクロック]タブでは、デフォルトですべてを残しています。 [SDRAM]タブで、すべてのフィールドにスキュー値などを入力する必要があります。 私の知る限り、それらはマイクロサーキットからSDRAMまでの線のトレースに依存しています。 DE1-SoCのこのデータを含むドキュメントを見つけることができなかったため、ボードの完成したプロジェクトから取得しました(アルテラ大学プログラムの例ではSOC-Computerでした)。 これらの設定をパーセットとして保存したので、もう入力する必要はありません。右の列で確認できます。 次にIPコアでPIOを見つけます。これらはLEDとボタンになります。

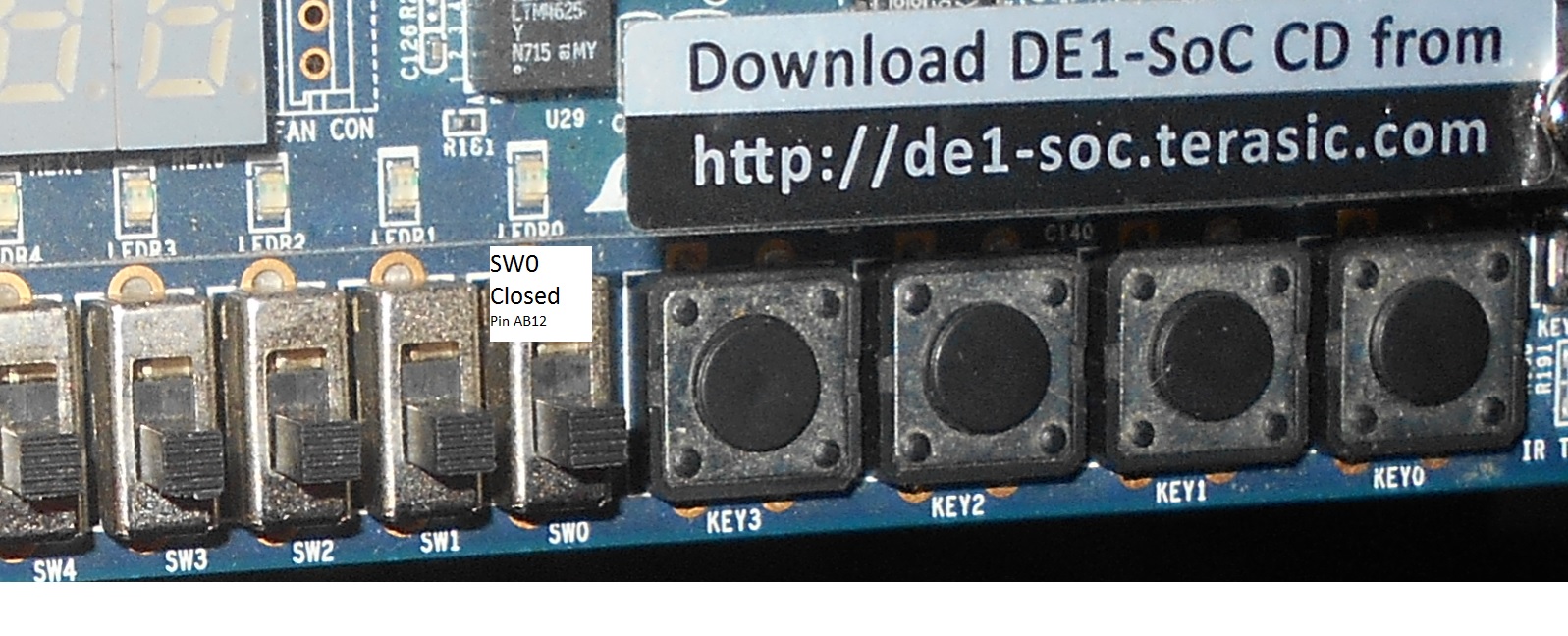

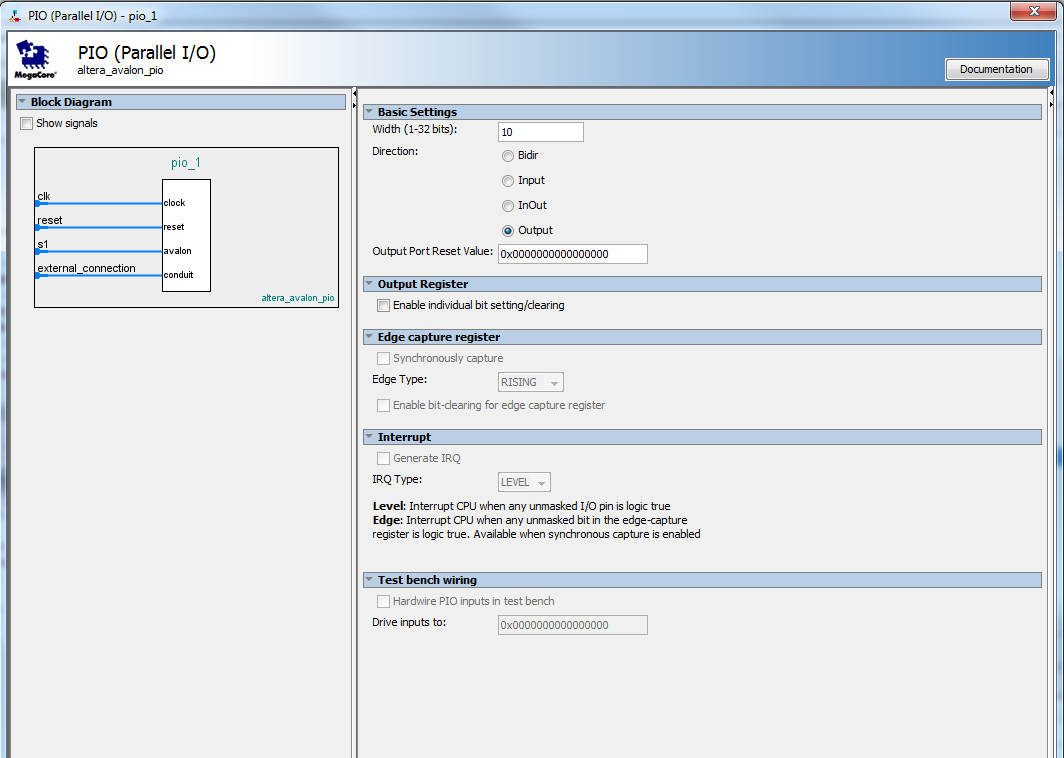

ボタンの設定には、[入力]を選択し、合計4つのボタンがあるため、幅を4ビットにします

LEDの場合、それぞれ出力と幅10。

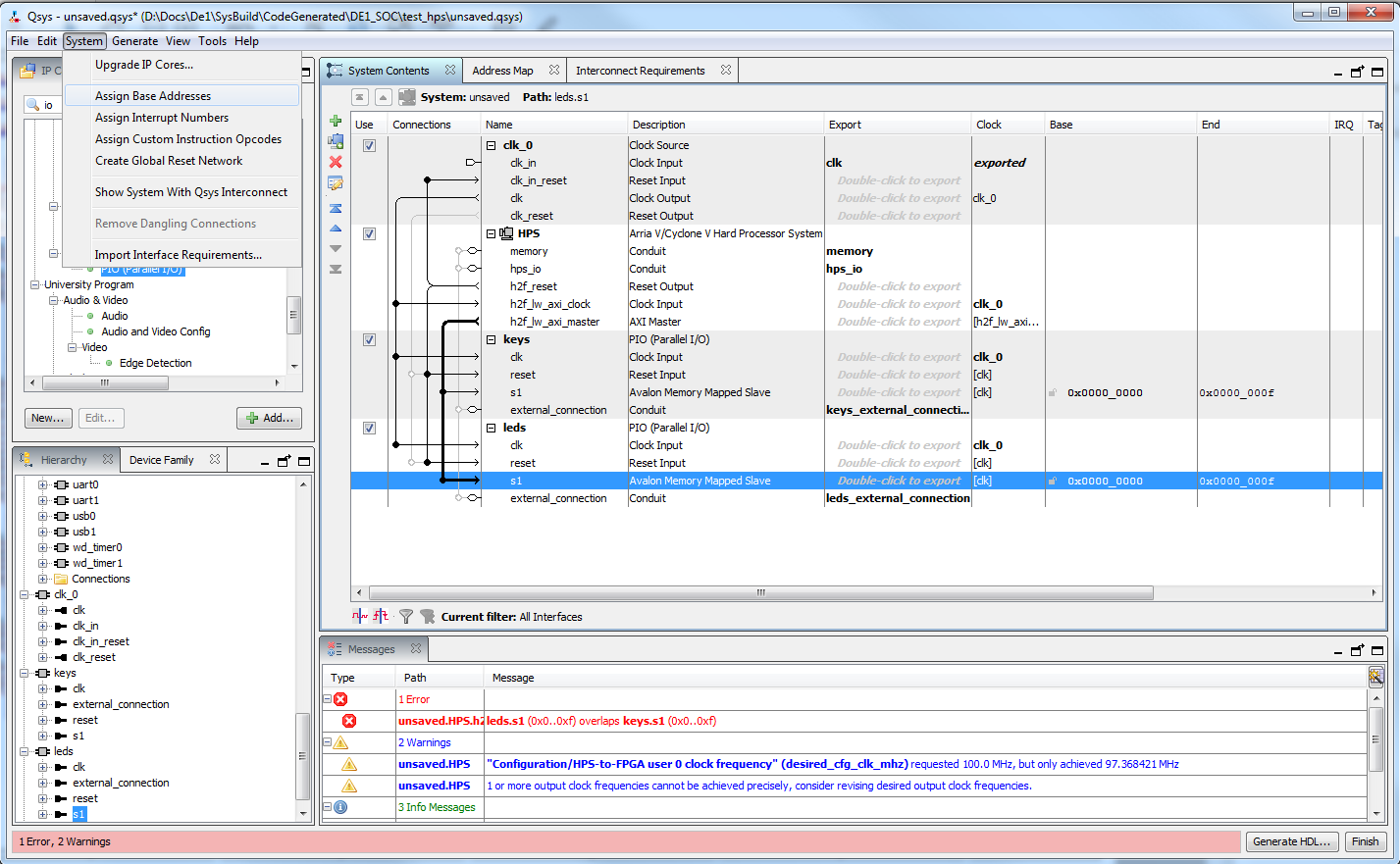

結果のシステムを図に示すように接続します。 PIOの名前を変更して、よりわかりやすく美しいものにすることができます。 PIOはFPGAファブリックで実行される要素であるため、LWH2FブリッジはHPSとFPGA(HPSマスターとも呼ばれる)間のリンクです。 システムからPIO LEDとボタンを出力するために、外部接続の反対側の碑文「エクスポート用のダブルクリック」をダブルクリックします。 後で、生成されたシステムファイルの最上位コードにこれらの結果が表示されます。 HPSのPIOおよび他のすべてのコアへのアクセスはアドレスで行われるため、それらを割り当てる必要があります。 これは、[ベースアドレスの割り当て]をクリックして自動的に実行できます。

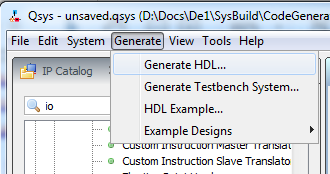

その後、システムコードを生成できます。

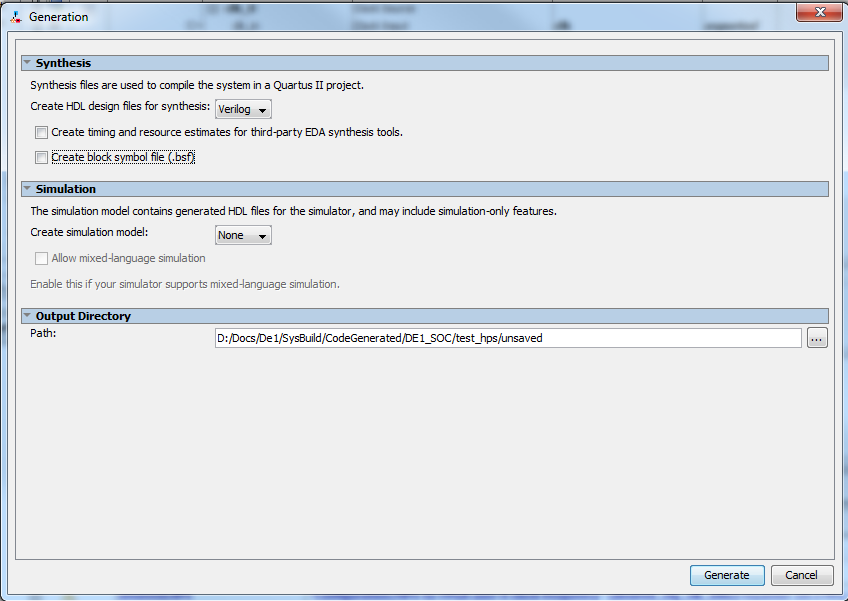

パスと目的のコード言語を指定します。 Verilogが好きです。 その後、QSYSを閉じることができます。 Quartusウィンドウに次のメッセージが表示されます。

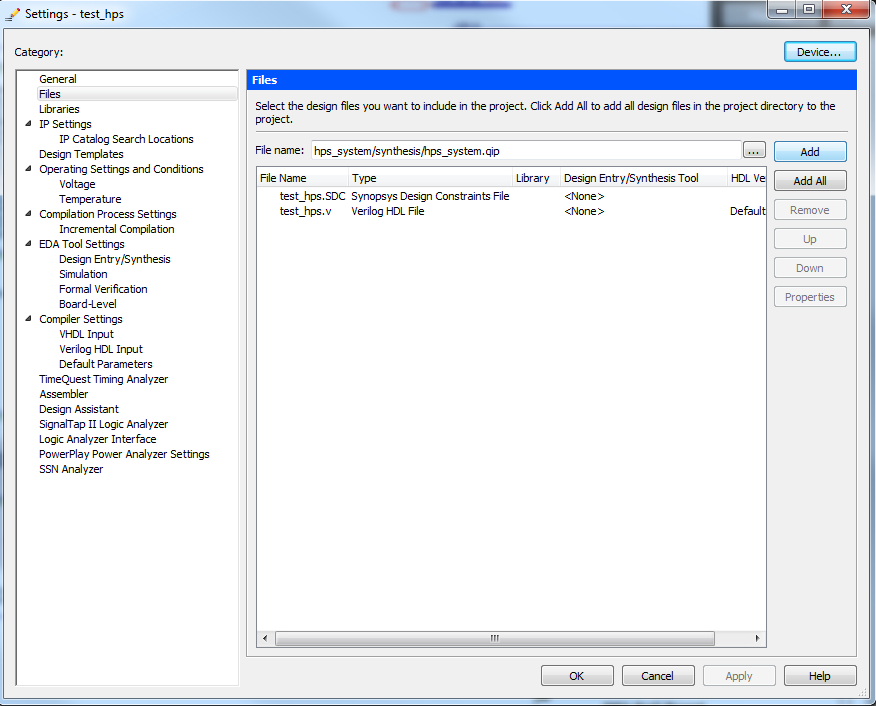

求められていることをしましょう。

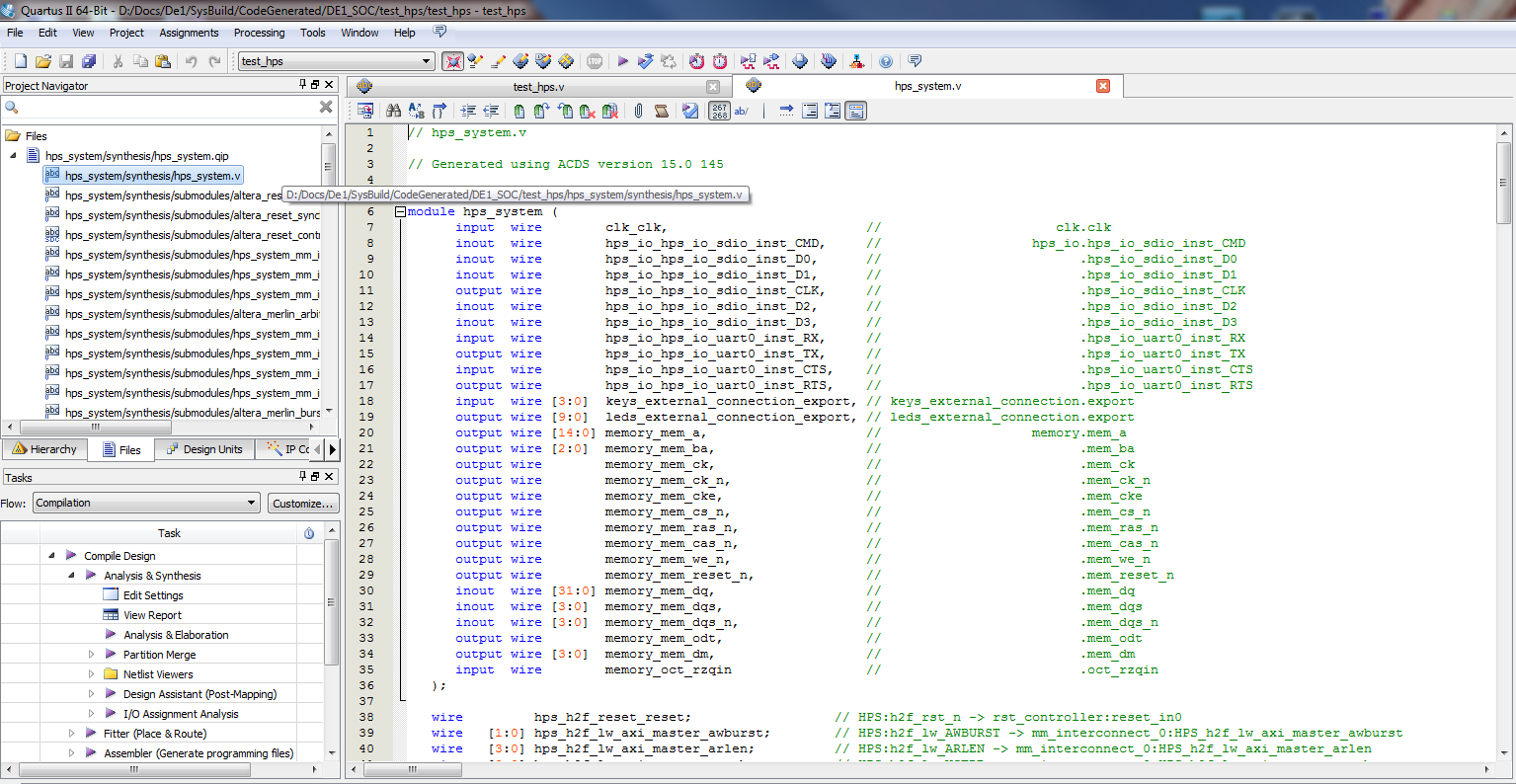

[ファイル]ウィンドウに、hps_system.qipが表示されます。 開いて、システムの最上位ファイルを確認します。

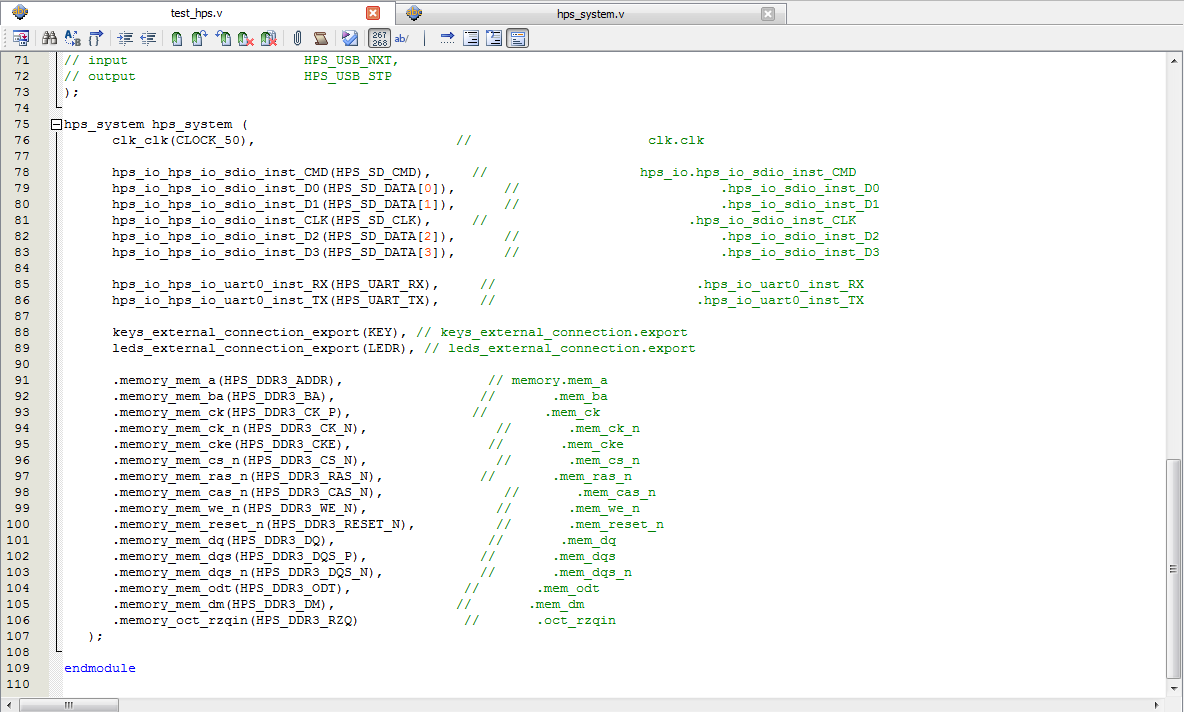

QSYSシステムで選択したものはすべてこのファイルに含まれています。 このモジュールを元のファイルに挿入するだけです。 これがFPGAファームウェアの最上位ファイルになります。

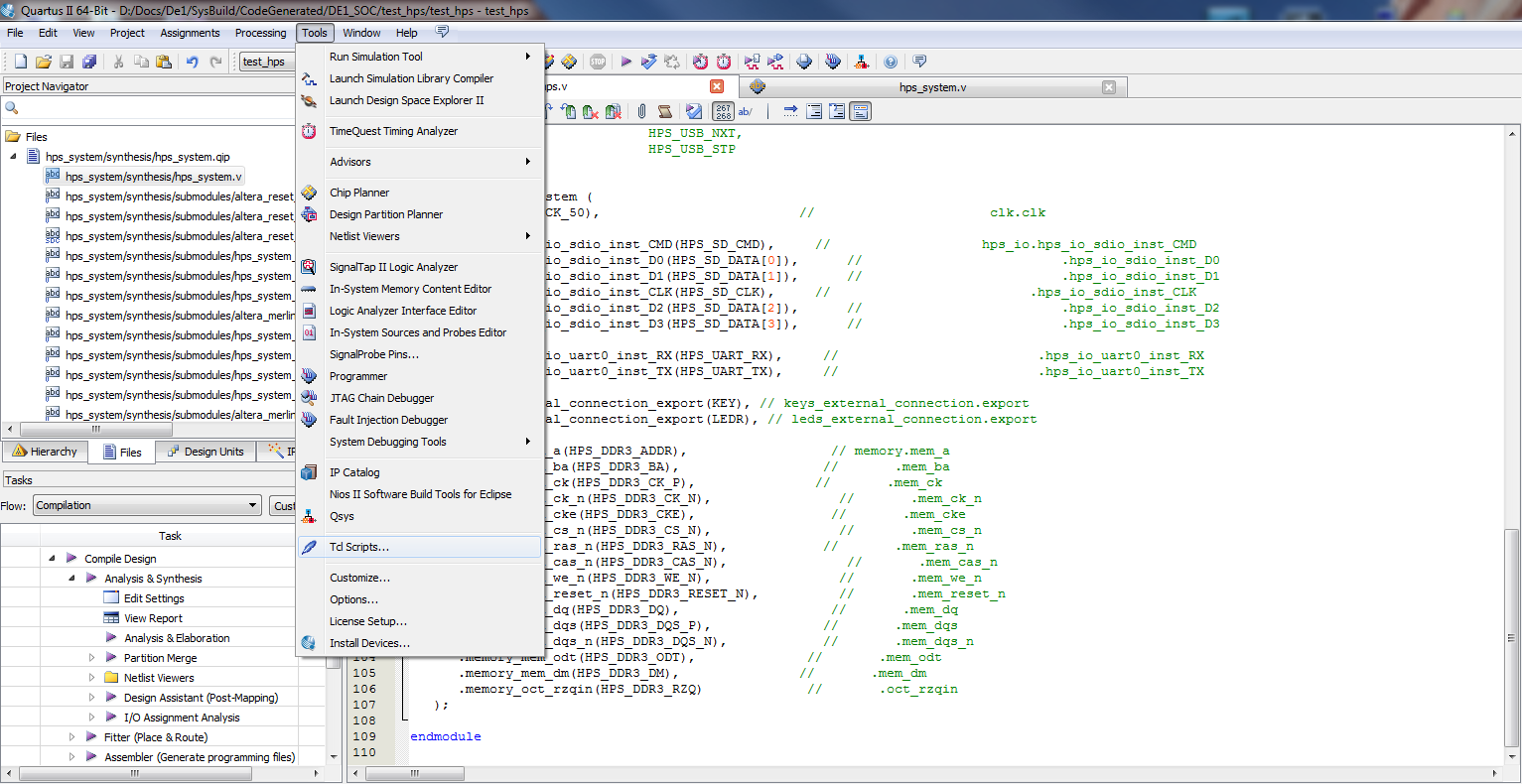

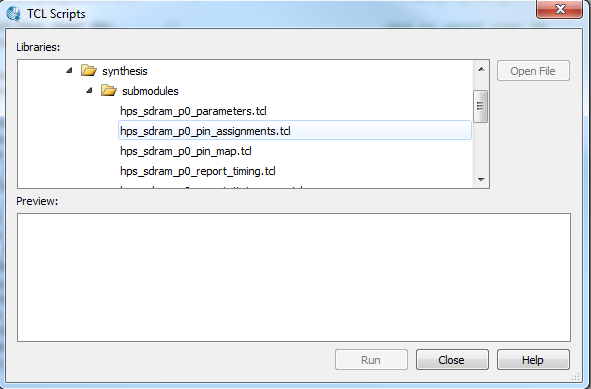

その中で、HPSシステムの結論は、このファイルの初期I / Oピンに起因します。 Pin Plannerに何も割り当てる必要はないことを思い出してください。ユーティリティを使用してプロジェクトを作成するときにすべてがすでに行われています。 ただし、HPSピンを割り当てる必要があります。これは次のように行われます。

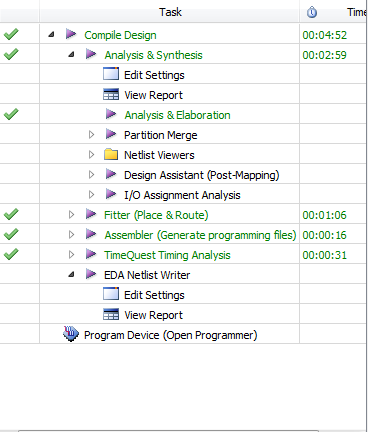

これが完了したら、ファームウェアをコンパイルできます。 エラーが発生した場合(たとえば、clk_clkおよびhps_io_hps_io_の隣にあるhps_system宣言を終了するのを忘れた場合...)、tclスクリプトを再度実行する必要があることに注意することが重要です。 すべてが正しく記述されていて、tclスクリプトを実行しても、コンパイルを開始するとエラーが発生する場合でも、コードを変更せずにスクリプトを再実行する価値があります。 助けてくれました。この機能の説明方法がわかりません。

そして、ファームウェアが完成しました! それでは、プリローダーの作成を始めましょう。

プリローダーを作成する

HPSブートプロセスにはいくつかの段階があります。それらを理解してみましょう。 Cortex-A9はアプリケーション用のプロセッサであり、名前の文字「A」はアプリケーションを意味し、主にLinuxなどのOSを使用して動作するように設計されていることに注意してください。 したがって、厳密に言えば、ベアメタルプログラムを起動するという考え方は奇妙に思えるかもしれませんが、場合によっては必要になります。 さらに、もちろん、このような機会がありますが、開発者は少なくとも基本的なレベルで読み込みプロセスを理解する必要があります。

スイッチをオンにした直後に、BootRomと呼ばれるCortex-A9フラッシュメモリに直接配置されたコードが実行されます。 変更したり、その内容を見ることもできません。 これは一次初期化に使用され、次のステップでブートプロセスをSSBL(Second Stage Boot Loader、略称Preloader)に転送します。 このプロセスを理解するために知っておく必要があるのは、まずBootRomコードがPreloaderダウンロードソースを選択し、外部の物理BSELピンに焦点を当てることです。 DE1-SoCでは、SDカードからロードするためのピンの初期設定が最初に選択されました。追加のスイッチと抵抗のペアをはんだ付けせずに、たとえばQSPIまたはNANDフラッシュに変更することはできません。 したがって、QSYSでは、[Peripheral Pins]タブでSDカードのピンを選択しました。 また、外部ソースからではなく、FPGAで作成されたメモリからのブートオプションがあり、そこにコードがプリロードされています。

したがって、BootRomコードが実行された後、クロック、SDRAMなどの設定に必要なプリローダーがロードを開始します。 プログラムが実行を開始した後。

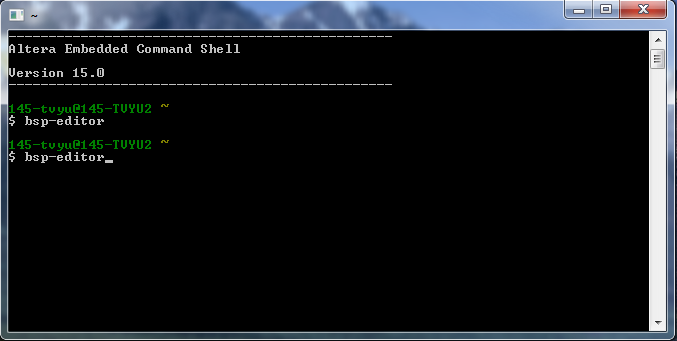

プリローダーを作成するには、SoC EDSが必要です。IntelFPGA Webサイトから既にダウンロードされているはずです。

プログラムはコマンドラインから機能します。 まず、適切な「bsp-editor」コマンドを作成してBSPを作成します。

このウィンドウで、[新規HPS BSP]をクリックします。

{Project directory} / hps_isw_handoff /へのパスを指定し、[OK]をクリックする必要があります。他のパラメーターを変更する必要はありません。

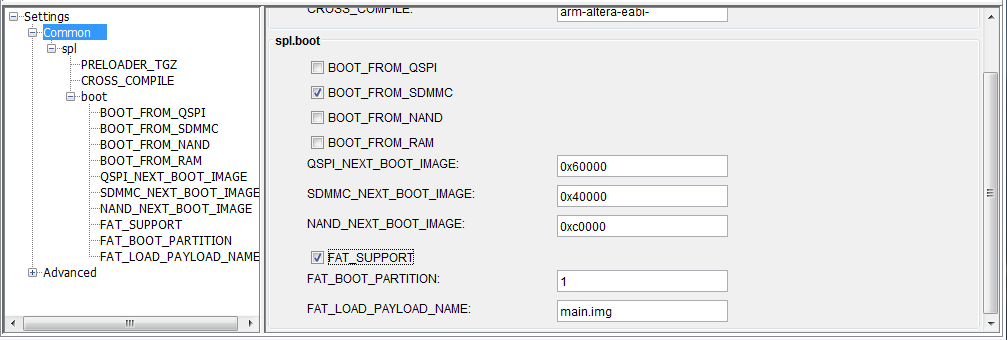

プリローダーのロード元のソースを指定するspl.boot設定を選択します。 私たちの場合、これはSDカードなので、BOOT_FROM_SDMMCを選択します。 Preloaderと、フラッシュドライブに少なくとも2つのパーティションがあるプログラムのダウンロードオプションを使用します。パーティションは、Preloaderのid = A2、およびプログラムのFAT32システムのパーティションでフォーマットされていません。 フラッシュドライブをパーティションに分割しない別のオプション、いわゆるRAW形式がありますが、私見では、このオプションの方が簡単です。 この方法で、任意のプログラムでUSBフラッシュドライブをフォーマットできます(ミニパーティションツール9.2を使用しました)。 または、... \ embedded \ embeddedsw \ socfpga \ prebuilt_images \ sd_card_linux_boot_image.tar.gzフォルダーで既にアセンブルされたイメージを使用し、Win32DiskImagerを介してUSBフラッシュドライブに書き込むことができます。

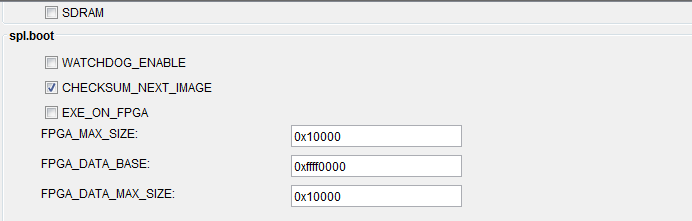

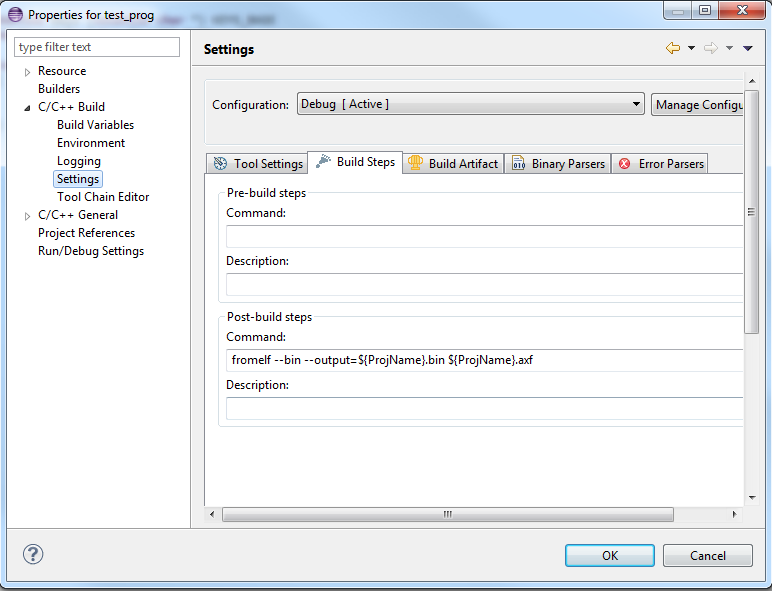

FAT_SUPPORT、FAT_BOOT_PARTITION 1、FAT_LOAD_PAYLOAD_NAME .imgを選択します。 WATCHDOG_ENABLEとEXE_ON_FPGAは使用しません(FPGAからPreloaderをダウンロードしません)。

SoCに精通していたときに問題を探して1か月間落ちた非常に繊細な瞬間です。 シリアルサポートとは、すでにPreloaderがUARTモジュールを使用して、起動時に診断メッセージを表示することを意味します。 セミホスティングとは、これらの診断メッセージの出力中に、デバッグ中にデバッガウィンドウに自動的に表示されることを意味します。 プログラム自体でこの関数を使用することは非常に便利です。これにより、printf関数で記述されたすべてを、追加のコードを記述せずにデバッガーウィンドウに表示できます。 HPSのQSYS設定でUARTの使用を指定せず、BSPの[シリアルサポート]チェックボックスをオンにすると、このプリローダーは機能しません。 セミホスティングを終了している間にシリアルサポートを削除すると、何も機能しなくなります。少なくとも私はそれを持っていました。 すべてを機能させるには、実験するか、チェックボックスをオンにします。 [生成]、[終了]の順にクリックします。

cdコマンドでSoC EDSの作業フォルダーを変更します。「<生成されたBSPファイルへのフルパスを指定します(デフォルトでは... software / spl-bsp)>」Preloaderをビルドするには、makeコマンドを実行します。 待っています。 パッケージのプロセスの最後に、目的のファイルpreloader-mkpimage.binを取得します。

これは、4つの同一のプリローダーイメージがあるコンパイル済みファイルです。 SoC EDSで実行されたmkpimageコマンドを使用して、このファイルをそのコンポーネント(個別のイメージ)に解析し、他の構成(異なるプリローダーイメージ)からアセンブルできます。 他の構成は完全に異なる場合があります(QSYSの異なるシステム)。つまり、4つの同一のイメージ(それぞれ64kb)を持つ個別のpreloader-mkpimage.binファイルを取得し、それらをコンポーネントに分解します。 (たとえば、異なるダウンロードソースを使用)。 これは信頼性のために行われます。 ある種の力が最初の試行から、最初のイメージからの起動を許可しなかったと仮定します。 次に、2番目の画像の読み込みが開始されます。たとえば、緊急事態の場合、それはわずかに異なります。 これがロードに失敗した場合、3番目などに進みます。 しかし、これはもはや私たちの仕事の主題ではなく、話題からの叙情的な余談なので、続けてください!

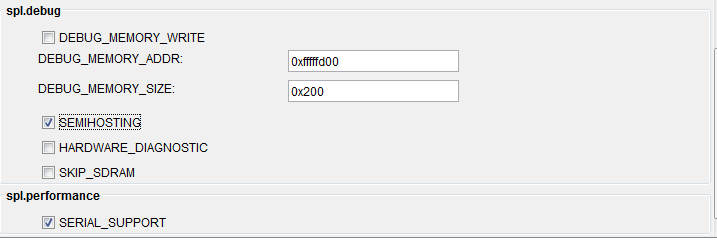

準備済みのセクションA2を備えたUSBフラッシュドライブを挿入し、「alt-boot-disk-util -p -a write -d」コマンドを使用してpreloader-mkpimage.binに書き込みます。 SoC EDSは、プリローダーファイルがあるフォルダーへのパスを指す必要があります。 プログラムを作成する準備がほぼすべて整いました! 便宜上、QSYS要素定義でヘッダーファイルを作成するだけです。 ファームウェアファイルを指すSoC EDSのパスを変更し、コマンドsopc-create-header-files .sopcinfoを実行します。 出力では、いくつかのファイルを取得し、その内容を調べて、それらのファイルの理由を明らかにします。

プログラム

プログラムを作成してデバッグするには、メーカーはDS-5 Eclipse環境の使用を推奨します。 「eclipse&」コマンドを使用して、SoC EDSを介してEclipseを起動することをお勧めします(Eclipseを開いた後、SoC EDSウィンドウがアクティブになるように、コマンドの最後に「&」記号を配置します)。

すでにARMに精通しており、そのようなアーキテクチャ用のプログラムを作成したことがある人にとっては、困難は終わります。 ARMに不慣れな人にとっては、困難が続きます。

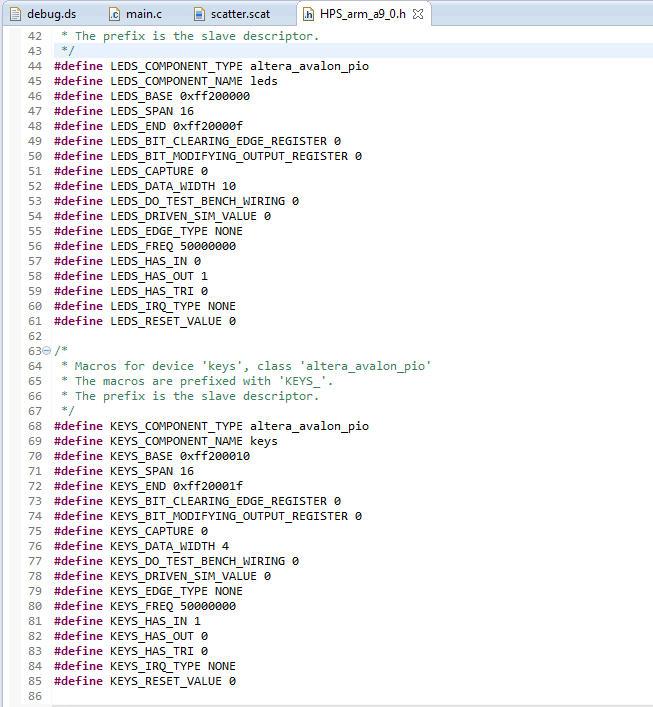

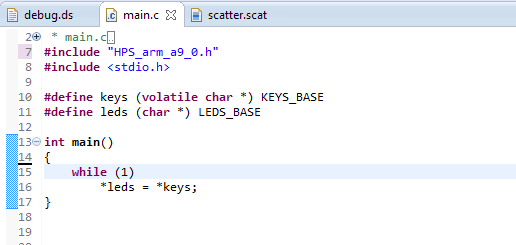

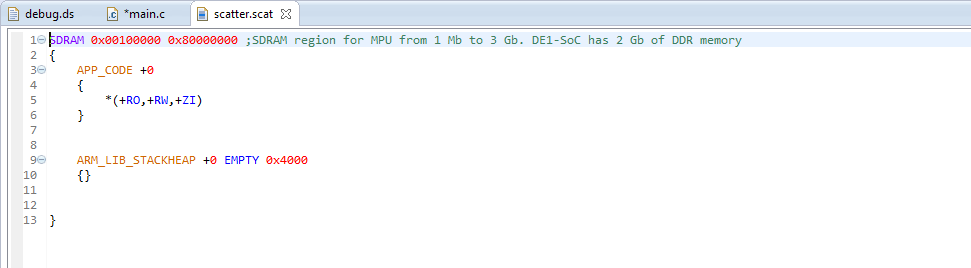

空の「C」プロジェクトを作成します。 コンパイラ選択ウィンドウが表示されます。ここでは、誰もが自分に最適なものを自由に選択して理解できます。 ARMの新人として、主にプログラムのさまざまな部分に記述されたプログラムを配置するために使用されるスキャッタファイルの比較的単純な構文のために、Arm Compiler 5が好きでした(GCCリンカスクリプト構文の単なる外観は私を怖がらせます)。 プロジェクトの設定では、すべてが簡単に見えます。 このコマンドのみを指摘します。

同じことをします。 これにより、axf形式がbin形式に変換されます。 後でプログラムをUSBフラッシュドライブに記録するために必要になります。 最終的にそれを書きます。

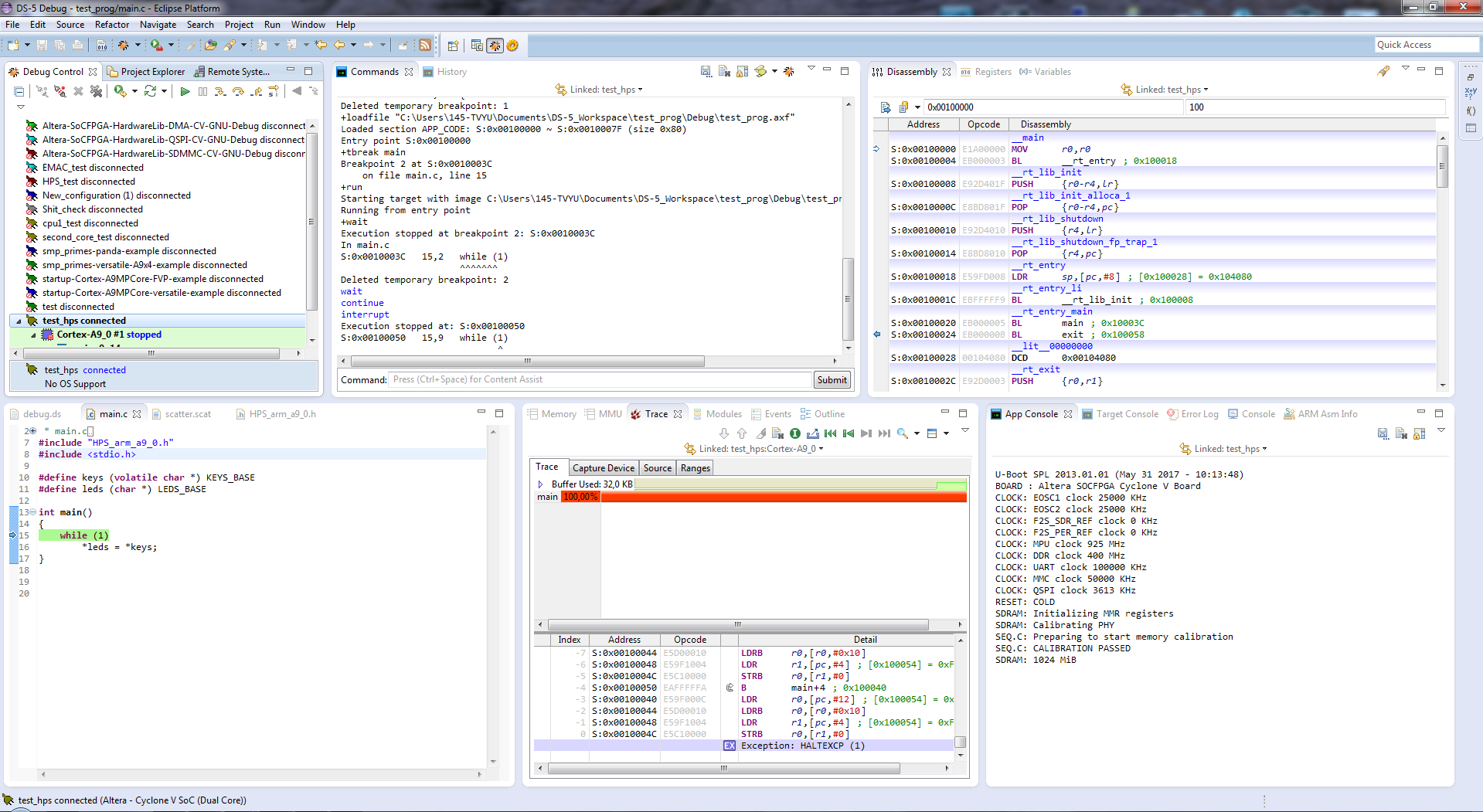

ここでは、stdio.hさえ必要ありません。 このプログラムは、メモリ内の内容をアドレスLEDS_BASEのアドレスKEYS_BASEに割り当てるだけです。 ボード上のボタンを押すと、その時間にLEDが消灯します。

スキャッタファイルの内容。

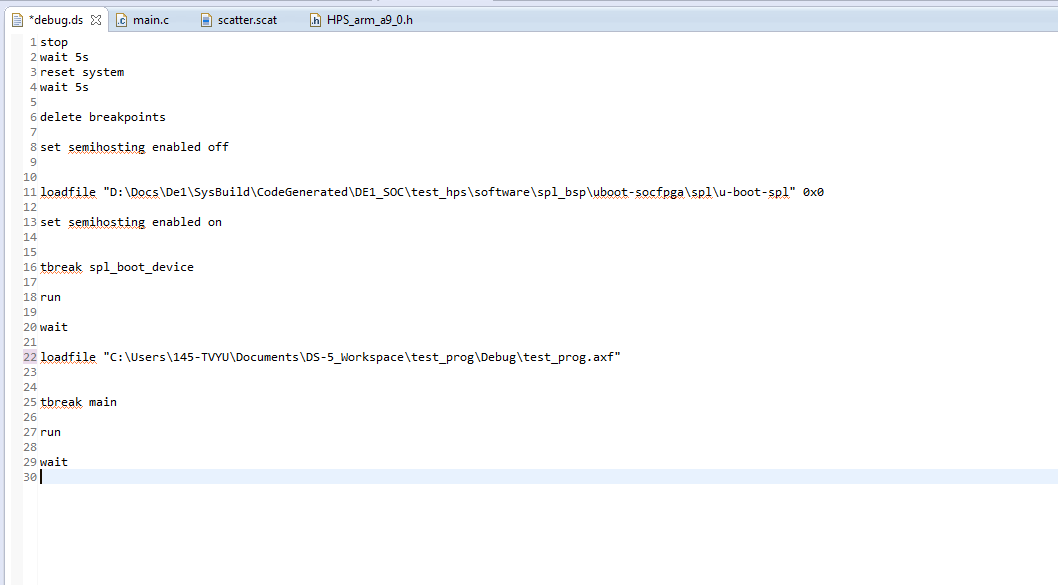

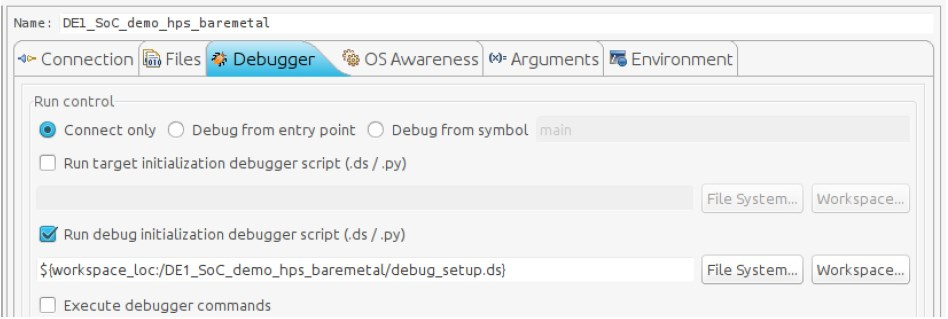

デバッグするには、デバッガーでスクリプトを作成する必要があります。 あなたが思い出すように、ダウンロードプロセスは簡単ではありません。 スクリプトは、ソースからアプリケーションをダウンロードする段階でプリローダーの実行を停止し、このタスクをコンピューターに転送します。

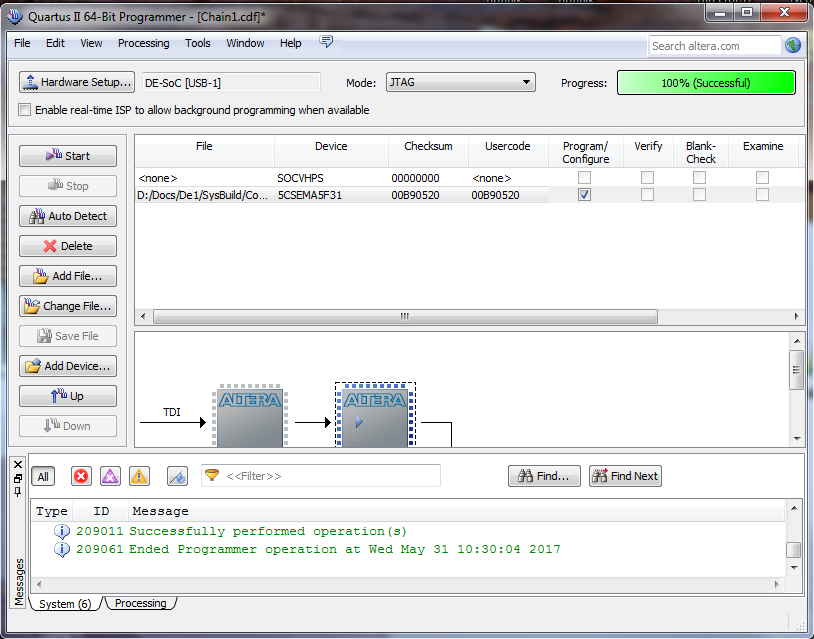

プログラムをダウンロードしてデバッグする前に、ボードをフラッシュすることを忘れないでください!

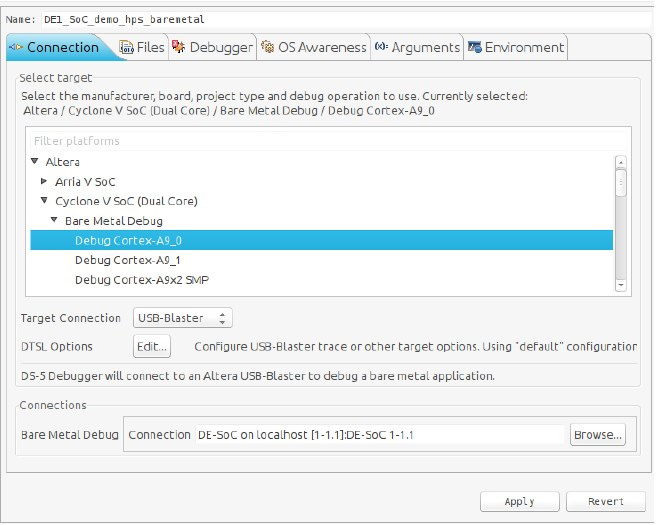

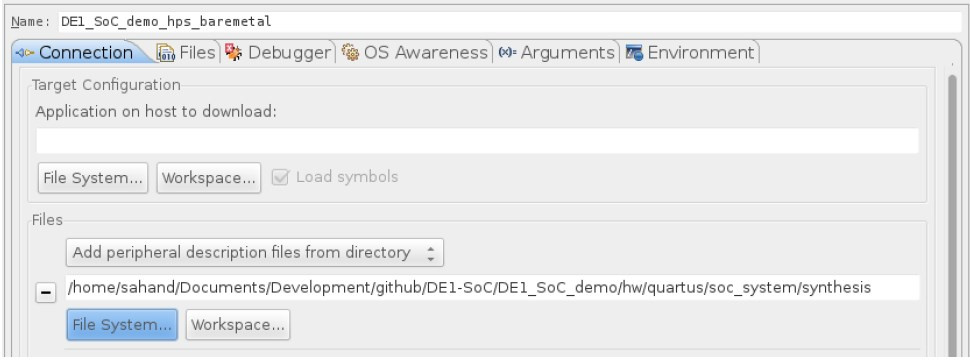

デバッグウィンドウで、新しいタスクを作成する必要があります。これは、デバッグコントロールで行います。 この段階でスクリーンショットを撮るのを忘れていたので、借りました。 以下の写真の設定と同様の設定を適用します。

コンパイル後、プログラムをデバッグし、レジスタの内容を見て、多くの興味深いことを行うことができます。

プログラムが正常に動作していることを確認したら、セルフローディング用のプログラムのイメージを作成できます。 これを行うには、DS-5プロジェクトのDebugフォルダーから<prj_name> .binファイルを取得し、SoC EDSを介して.img形式に変換します。 これは、コマンド「mkimage -A arm -O u-boot -T standalone -C none -a 0x00100000 -e 0x00100000 -n„ baremetal image「-d .bin .img」で実行されます。「-a」はロード先のアドレス、 -e "プログラムのエントリポイント。

エントリポイントはプロジェクト自体で設定することもできます。割り込みベクターが使用されている場合、割り込みベクターは使用されないため、設定しません。 スキャッタファイルに設定したアドレスにガイドされ、このコマンドに同じアドレスを記述します。 実行する前に、cdコマンド「<file folder>」でSoC EDSのbinファイルへのパスを指定することを忘れないでください。 imgファイルの名前は、FAT_LOAD_PAYLOAD_NAMEのBSPエディターで指定した名前と一致する必要があります。

通常のファイルのように、ファットセクションのUSBフラッシュドライブにファイルをコピーします。 DE1-SoCにUSBフラッシュドライブを挿入すると、プログラムの実行を確認できます。

おわりに

この記事では、説明されているプロセスには多くの段階があり、それぞれに実装の代替オプションと独自の特性があるため、多くのポイントをより詳細に検討できます。 しかし、他のすべての質問については、参考文献のリストが完全に答えると思います。 次の記事をご覧くださいCyclone V SoCでのAMPアプリケーションの起動