最初にいくつかの紹介的な言葉があります。 セットアップやホールドなどのセットアップやホールドなどのトリガーパラメータについては、 ここで詳しく説明します 。 一言で言えば、クロック信号がトリガー入力に到着する瞬間に、情報入力の信号が安定している必要がある一定の最小時間間隔があります。 信号の変化がこの間隔外で発生した場合、トリガーは正しく作動します。 これらは、開発者が単一のクロックで回路を設計する際に従う必要のある最小要件です。 また、プロジェクトが1つのリファレンスから取得した複数の周波数を使用する場合でも、回路は同期と見なされ、設計中に注意すべき最大値はセットアップとホールドの遵守です。

ここで、プロジェクトで2つの独立したクロックソースを使用するとします。 回路内のすべてのトリガーは、いずれかの基準周波数からの制御原理に従って、2つのドメインに分割されます。 互いに非同期のこれらのドメイン間では、境界は1つの基準周波数で生成された信号の形で通過し、異なる周波数で動作するトリガーの情報入力に進みます。 実際、トリガー入力の信号はクロックパルスと非同期であることが判明しているため、必要なセットアップ時間とホールド時間を維持できません。 その結果、2つのドメインの境界でトリガーの動作に異常(実際には誤動作)が発生することがあります。これは通常、一時モデリングでトリガーXの不確定状態として指定され、波形に赤でペイントされます。 実際の回路では、トリガーのこの異常な状態は、応答が長期化することがあります。トリガーが準安定領域に入るためには、入力信号がts + thよりもはるかに狭い時間間隔で変化する必要があるためです。

この図は、tc-クロックパルスの前部の絶対到着時間です。これは、ホールド軸(ゼロから右に向けられた)とセットアップ軸のゼロサンプルです。 セットアップ時間はブロックの前面が到着した瞬間から負の方向にカウントされるため、セットアップ軸は左に向けられます。 次に、tsとthはトリガーのセットアップおよびホールドパラメーターです。マークtsとthの間では、トリガー情報入力の信号が安定している必要があります(図の赤い領域)。 ts + thウィンドウの外側では、信号は任意に変更できます(図の青い領域)。 ts + thウィンドウ内で信号が変化すると、トリガーの切り替えが非常に遅れることがあります。 写真の最後の要素-準安定領域はオレンジ色で強調表示されています。 これは、トリガー出力の動作が予測不能になる特定の時間間隔であり、これについては以下で詳細に説明します。 実際には、時間thは多くの場合負であり(ts + thウィンドウは何らかの理由でゼロマークに対して左にシフトします)、メタスタビリティ領域の幅は、トリガー回路とトランジスタパラメーターごとに個別に決定する必要があります-実験的に、またはスパイスモデリングを使用して。

古典的なDフリップフロップ回路のデバイスとその構成要素であるRSラッチを考えてみましょう。

アクティブゼロの短いパルスがラッチの入力R(リセット)に到着し、パッシブ信号(ログ1)が入力S(セット)に到着すると想像してください。 インパルスが非常に短い場合、ラッチが切り替わらないことがあります。 そして、パルス幅を長くするとどうなりますか? さまざまな期間のパルスをラッチの入力に適用して、一連の実験を行います。 次の図は、L.R。の記事から引用したものです。 準安定操作のマリノ一般理論:

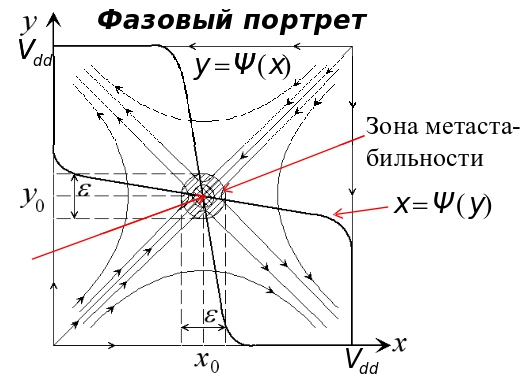

図は、RSラッチのXおよびY出力の電圧の2つの軸を示しています。 マークV0およびV1-電圧ログ。 1およびログ。 トリガーの0出力、Vmは½U供給に等しい電圧です。 この図は、初期状態(初期状態)が平面{X = V1、Y = V0}のポイントにあることも示しています。トリガー{X、Y}の出力は論理値{1,0}を取りました。 高電位(受動値)がラッチS(セット)の入力に適用され、異なる持続時間のアクティブゼロのパルスが入力R(リセット)に適用されます(6番目に短い、1番目に長い-図の下部に表示)。 入力Rでのパルス数に応じて、図は出力ペア{Y、X}の6つの潜在的なスイッチングパスを示しています。パルス1〜3ではトリガーが完全に切り替わり、パルス5〜6ではトリガーは切り替わりません。ログのしきい値の中間に位置する準安定ゾーン(ポイント{Vm、Vm})。 1およびログ。 0。

そのため、1つのラッチショルダーに持続時間が不十分なインパルスを適用すると、そのエネルギーは完全な切り替えには不十分である可能性があります。 パルス幅が長いと、ラッチを切り替える必要があります。 最後に、ラッチの出力が2つの安定状態の中間になるような期間の入力パルスを取得できます。 さらに、パルスエネルギーがラッチ出力を押す準安定領域に近いほど、これらの出力が安定状態を回復する時間は長くなります。

次に、ASICの設計で使用される65nmのライブラリの最新のDフリップフロップ図に移りましょう。

情報入力Dの図では、キーGDがあり、最初のラッチはオンスイッチI1とG1の2つのインバーターとして描かれ、パススイッチSWはラッチを分離し、2番目のラッチもオンスイッチI2とG2の2つのインバーターに構築されます。 速度を上げるための出力は、2番目のラッチの左肩から取得されます。 トリガーは次のように機能します。CK= 0で、入力キーはG1フィードバックが無効な状態で最初のラッチに信号を渡し、G2フィードバックがアクティブであるため、ラッチ間のキーが閉じられ、2番目のラッチが保存されます。 CK = 1の場合、最初のラッチは入力Dから遮断され、そのフィードバックG1がアクティブになり、ラッチ間のキーがロック解除され、2番目のラッチのフィードバックがオフになります-最初のラッチのデータは2番目に上書きされます。 リーディングエッジCKの到着前に信号Dが除去されると、最初のラッチの入力でアクティブゼロのパルスが得られます。その持続時間はフロントCKとDの比のみに依存します。したがって、状況はRSラッチで考慮される状況と同様です。ラッチを切り替える、切り替えない、または-ラッチを準安定状態にする。 L.R.の記事 マリノは、そのデザインに関係なく、絶対にあらゆるトリガーの出力が準安定状態をとることができることを数学的に証明しました。

ラッチの出力で考えられるすべての状態を考えてみましょう。 このために、出力の2つの軸電位で別のグラフを作成します。 このスケジュールは、論理設計に関する講義、技術科学博士、VB教授から借用しています。 マラホフスキー:

スケジュールはL.R.の記事とほぼ同じです。 Marino、ただし矢印はラッチ出力の可能な動作の軌跡を示しています。 軌跡に沿って移動すると、ラッチの出力は最終的に、入力の状態に対応する安定した論理状態{1,0}または{0,1}に切り替わります(入力状態をクリックします)。 しかし、出力の電位がグラフの中央の特定の領域に落ちた場合、出力の最終状態を予測することは不可能です。 これは不安定な平衡領域(準安定性)であり、その出力は熱雑音などのランダムな要因によってのみ影響を受ける可能性があります。 準安定状態の完了時のラッチ出力の最終状態は事前にはわかりません。任意の状態({1,0}または{0,1})になります。 準安定領域のサイズは実験的に測定されるか、スパイスモデリングを使用して計算されます。 実際には、準安定性は、食物の½Uに等しい静的電位の形だけでなく、この点の近くの弱い脈動の形でも現れることに注意すべきです。 準安定性のもう1つの重要な特性は、ラッチが安定するまでにかかる時間が予測できないことです。 知られているように、ラッチが準安定状態を離れる時間はポアソン分布によって記述され、理論的には無限に長くなる可能性があります。 したがって、準安定状態を抜けた後のトリガーの最終状態だけでなく、準安定状態の持続時間も事前に予測することは不可能です。 ただし、次のクロックサイクルでトリガー入力の信号が変化しない場合、2つのドメインの境界でのトリガー出力の準安定状態の最大持続時間はクロックパルスの持続時間を超えません。

準安定領域のサイズと障害の頻度を計算するための式と方法については、記事「Multistage Synchronizersの変動性」を参照してください。 この記事では、失敗の頻度を計算した結果のみを示します。 シンクロナイザーとして、周期800 ps、入力信号の周波数範囲600 ps〜2nsのパルスで動作する2x、3x、および4xトリガーのシリアル接続スキームを使用しました。

縦軸に沿ったグラフでは、MTBFは年単位で表示されます-800 psの周期のクロックサイクルで動作するドメインへの入り口で異なるシンクロナイザーを使用した場合の障害(メタステーブル状態に陥る-障害)の期間。 水平周期は、ドメインのクロックパルスの周期、つまり信号源です。 図からわかるように、シンクロナイザーチェーン内のトリガーが多いほど、障害が発生する頻度は少なくなります。

結論

1.トリガーの切り替え時間は、最初のラッチの入力での制御パルスの持続時間に完全に依存します。これは、トリガーの入力で信号の位相をクロックパルスにシフトすることによって取得されます。 間隔ts + thの制限を超えて信号を切り替えると、トリガーは正しく、所定の時間内に切り替わります。 ただし、この間隔内で入力信号が変化した場合、トリガーはより長く安定状態に達し、準安定ゾーンに近づきます。 トリガー出力が準安定ゾーン内にある場合、それらの最終的な論理状態と応答時間は予測できません。

2.オシロスコープのトリガー出力の準安定性は、1/2 U電源に等しい出力電位のレベル、またはこのレベルの近くの弱いリップルのように見えます。 トリガー回路のインバーターでは、貫通電流がグランドバスと電源バスの間に流れます。 しかし、nトランジスタとpトランジスタのオープンチャネルの抵抗はキロオームで測定されるため、貫通電流は、回路の一般的な消費、電力降下(IR降下)、エレクトロマイグレーションなどの現象に顕著な影響を与えません。

3.ギガヘルツに近い周波数では、2つのドメインの境界でのトリガーの障害(準安定性による)が数秒に1回発生します。 準安定性を使用すると、2つ以上のトリガーを連続してシンクロナイザーとして使用できます。 2つのトリガーを使用すると、シンクロナイザーの出力で障害が1年に1回発生します。 3つのトリガー-1000年に1回。 4つのトリガー-100億年に1回。 動作周波数を低下させると、障害の頻度に指数関数的に影響します。2つのトリガーのシンクロナイザーと約500 MHzの周波数を使用すると、障害の間隔は数桁増加します(100万年に1回の障害)。 したがって、ギガヘルツの周波数で回路を設計する場合は、できるだけ少ない非同期ドメインを使用するか、シンクロナイザーの直列トリガーの数を3つに増やしてください。

4.故障の頻度は、使用されるトランジスターのパラメーターとトリガー回路に依存する(トリガーを構成する)第1および第2ラッチの出力の寄生容量によって強く影響されます。 つまり、トランジスタとトリガー回路のパラメーターを変更すると、このトリガーの出力での準安定性の発生頻度に間接的に影響を与えることができます。 レシピは、独自の要素ライブラリを設計する場合にのみ適しています。

5.静的時間分析の観点から、非同期ドメイン間のすべてのパスは、sdc定数set_false_pathで記述される必要があります。

ロシアではトリガーの準安定性を研究した人はいません(正しくない場合でも正しい)が、実際には、開発者は上記の簡単な推奨事項に従うだけで十分です。 これが誰かに役立つことを願っています。