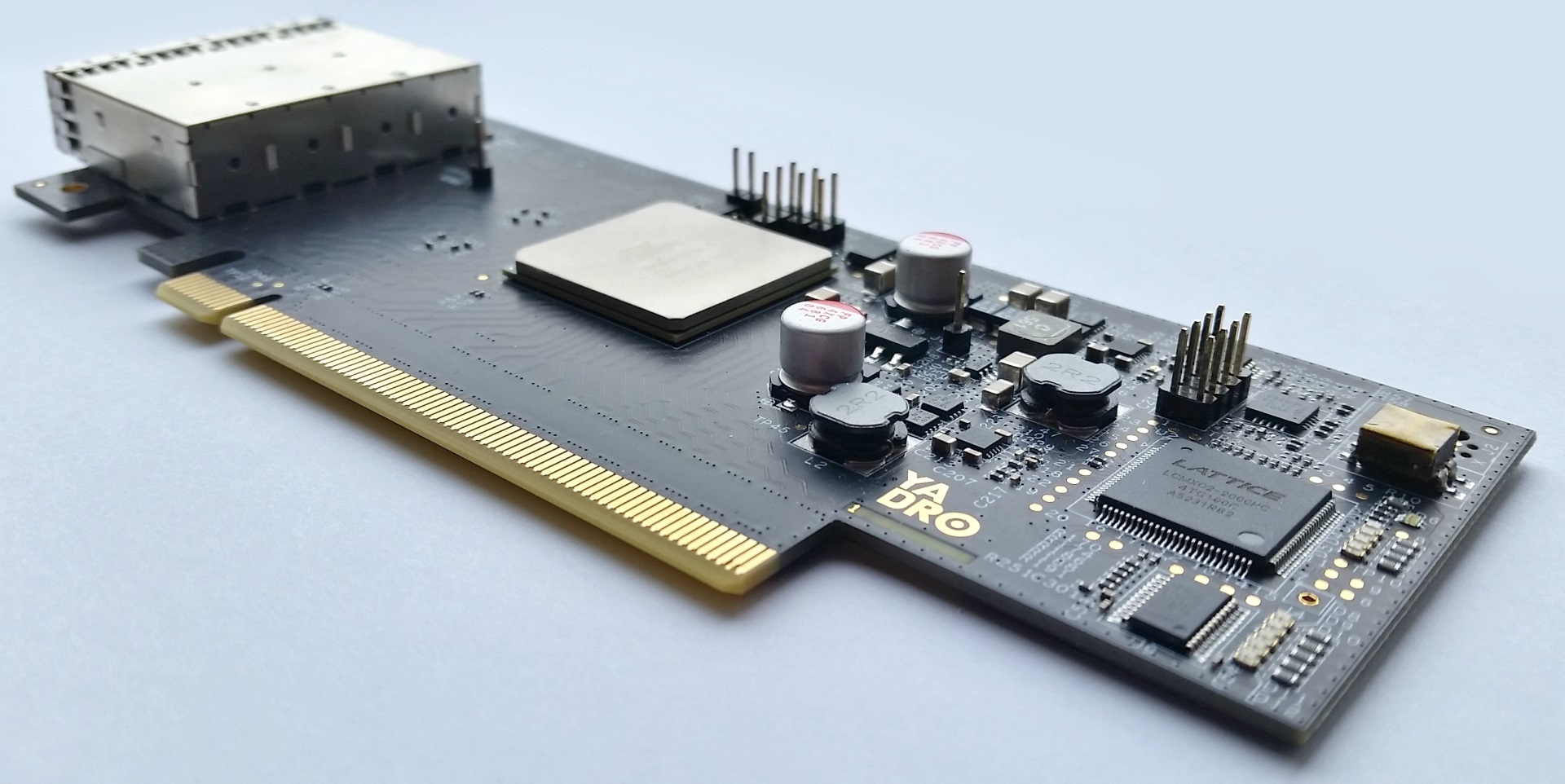

PCI Expressの歴史と開発に関するレビュー記事の最後に、 Alexeiはケーブルを介したPCI Express(以降、PCIeの略)デバイスの外部接続用の独自のアダプタについて言及しました。 今日は、さまざまなタイプと長さのケーブル接続で正しく動作するようにテストおよびデバッグした方法を説明します。

このアダプターは、ケーブルを介してPCIeバスを介してシステムのコンポーネントを相互に接続するように設計されています。 開発の時点では、このための既存の既製のソリューションは、いくつかの理由で私たちに適合しませんでした-一部はGen3速度をサポートしませんでした、一部は有望だと思われるケーブルを使用しました

次に、アダプターを操作する際に発生した(そしてまだ発生する)問題を説明します。 しかし、意味をよりよく理解するために、まずPCIeデバイスの相互作用の理論的な側面を掘り下げます。

予約します-以下の説明は一般的にPCIeに適用されますが、この記事の一部として、このメーカーのチップで動作するため、PLXのドキュメントの用語を使用しました。 他のメーカーでは、同様のメソッドとエンティティが異なる方法で呼び出されても、本質は変わりません。

チューニング

PCIeデバイスには、受信パスと送信パスにイコライザーがあります。 信頼性のある(BER <10 -12 )接続を得るために、イコライザーパラメーターを変更(調整)する必要があります。

送信機の調整

PCIeトランスミッターには、制御可能な次のイコライザーパラメーターがあります。

- ディエンファシスまたはポストカーソル

- プリシュートまたはプリカーソル

- メインまたはカーソル

「カーソル」という単語が絶えず点滅しないように、これらのパラメーターの名前の最初のバージョンを使用します。

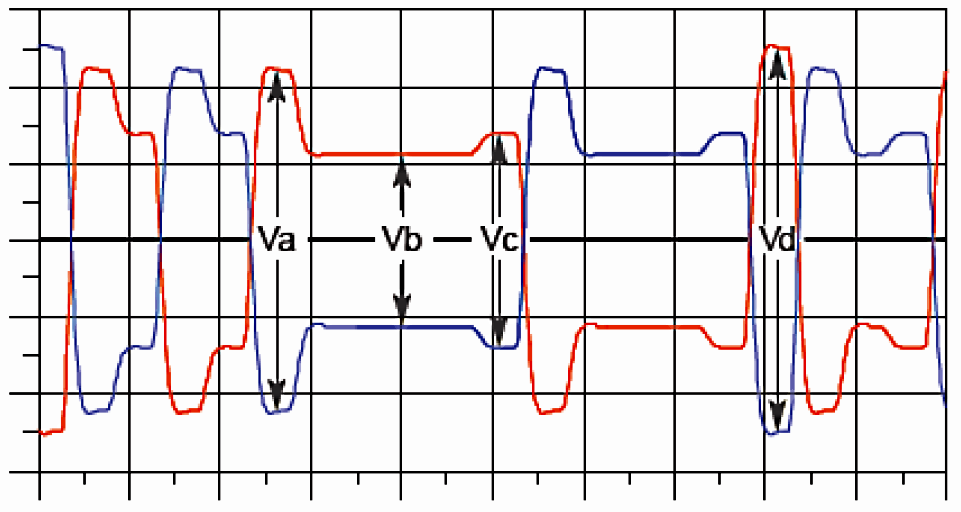

これらのパラメータは、時間領域での信号の振幅間の関係を決定します。

ディエンファシス係数はVb / Va比を決定し、 プリシュート係数はVc / Vb比を担当し、 メインは概して 、プリシュートを考慮した最大値とデエンファシスを考慮した最小値の間のスパン(ショート間のスパントップシェルフとロングボトム)またはその逆。

技術的な詳細に深く入り込まない場合、ディエンファシスは前のビットの値に応じて送信ビットの振幅を強化し、プリシュートは次のビットの値に応じて同じことを行います。 Mainは、全体として信号スイングを決定します。

Main、De-emphasis、およびPre-shootの値は、0〜63の係数によって設定されます。すべての係数の合計は63に等しくなければなりません。つまり、Pre-shoot = 6(3.5 dB)、およびDe-emphasis = 13(-6 dB )、メインに残るのは44のみであるため、信号エネルギーはHF(スイッチングビット)とLF(数個の連続した1または0)のコンポーネント間で再分配されます。

10メートルのケーブルの場合、最適な値はメインで63、プリシュートとディエンファシスでゼロ、またはプリシュート値が小さいメインで55-57です。 つまり、このようなケーブル長では、信号が減衰するため、レシーバーはエッジまで届かないため、ライン内の信号の存在を単に認識できません。

受信機のチューニング

信号が受信機に到着すると、次のツールが順番に使用されます。

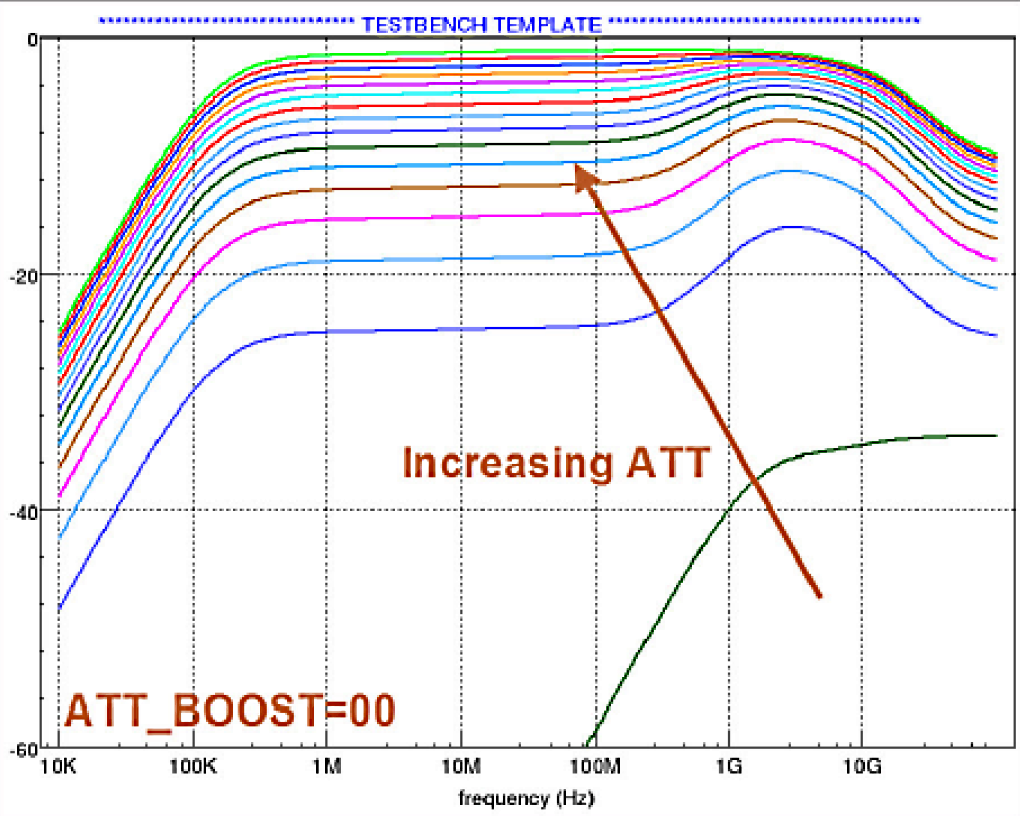

- ATT(減衰器);

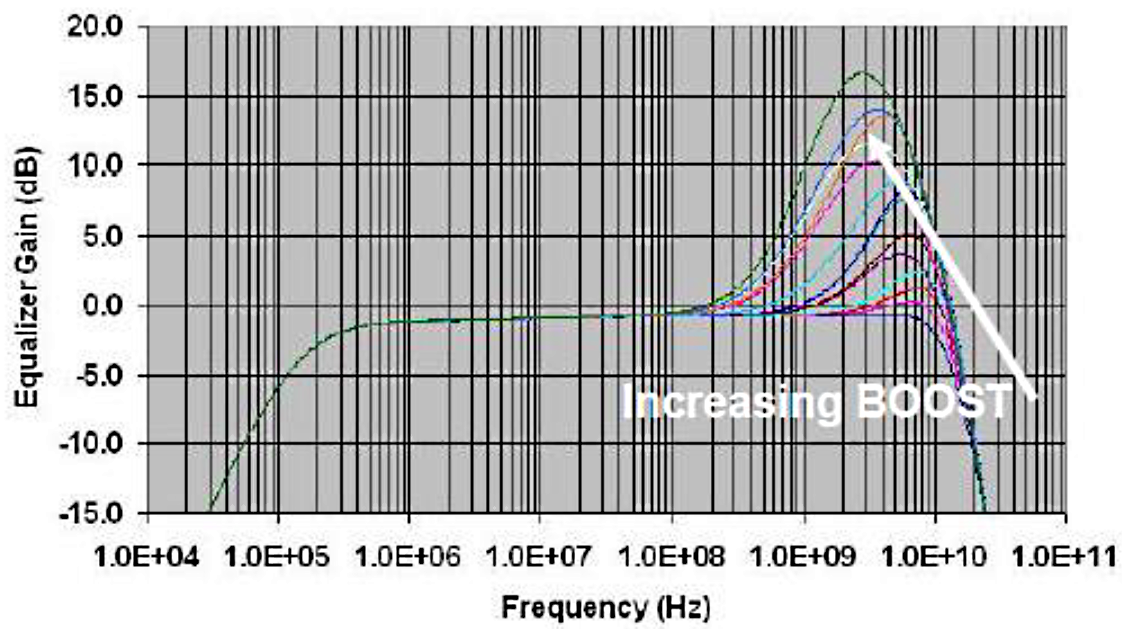

- BOOSTまたはCTLE-RFコンポーネントアンプ。

- DFE-送信機のディエンファシス/プリシュート段階と基本的に同様に機能するブロック(デフォルトでは無効)は、シンボル間干渉(ISI)を排除するように設計されています。

ATT伝達関数-全周波数範囲でほぼ均一な信号減衰:

CTLE伝達関数は、HF領域の大幅な向上です。

通常、ATTおよびCTLEは逆位相で動作します-低いATT値には高いCTLE値が伴います。 つまり、受信機は最初に入力信号を許容可能なレベルにスケーリングし、次にチャネルをたどるプロセスで最大の減衰を受けるRF成分をポンピングします。

係数を手で調整する必要がある場合、弱い減衰(およびその結果、過度に開いた「目」)が受信パスの過剰につながる可能性があることに留意する必要があります。 BOOSTの値が大きすぎると、たとえばクロストークによって引き起こされるRFノイズの増幅につながります。 一般的に、これらのハンドルを最大限にひねる必要はありません。

繰り返しになりますが、10メートルのケーブルの場合、ATTは0x0F(減衰なしを意味する最大値)で較正されます。 そして、0x09の領域のCTLE-高音域のかなり深刻な増加。 つまり、これらの距離では信号が減衰するため、ここではハンドルをほぼ最大までねじる必要があります。

PCIe Gen3ワークアウト

PCIe Gen3は、トレーニング中に反復フェーズが存在し、その間に受信パスと送信パスのパラメーターが調整されるという点で、Gen2およびGen1と根本的に異なります。 非常に拡大されたトレーニングプロセスは次のとおりです。

- それはすべてGen1から始まります。 この段階では、調整は行われず、全員が標準値で開始し、プロセスでそれらを変更しません。 特に、Gen1レシーバーの場合、これはATT = 0x09、CTLE = 0x05です。

- ダウンストリームポートは、Gen3のトランスミッタトリム(TX PRESETS)のアップストリームポート初期値を伝え、それ自体の開始値を設定します(通常は一致します)。

- アップストリームポートはトランスミッタを設定し、パートナーはGen3モードに入ります。 接続の品質が10 -4未満のBERを得ることができない場合、すべては機能しません。 つまり、多くの場合、開始パラメーター値が重要です。

- リンクアップが発生すると、ダウンストリームポートはレシーバーのキャリブレーションを開始し、BER

10 -12に達するまでアップストリームポートに新しいトランスミッター設定を通知します。 - この後、同じ手順が発生しますが、逆も同様です-アップストリームにアドバイスし、ダウンストリームが較正されます。 さて、リンクアップが起こります。

接続パートナーのこのような情報のやり取りのメカニズムは、バックチャネルチューニングと呼ばれます。

銅ケーブルを使用する場合のテストとデバッグ

最初のインクルードの時点では、もちろん、テストを実施しませんでした(誰がテストを実施しますか?)。 2つのアダプターを銅ケーブルでつなぎ、点滅する電球を見ました。 次に、lspciコマンドを使用して、リモート接続されたPCIeスイッチがシステムのPCIeツリーに表示されていることを確認し、確立された接続のパラメータが8 GT / sの速度で予想されるもの、すなわち構成に応じてx4 / x8 / x16に対応することを確認しました。

次に、接続の品質をさらに詳しく調査し始めました。 0.5 mおよび3 mのケーブルの場合、BERはゼロでした。 10メートルのケーブルには困難があり、それらを解決するために徹底的に解決する必要がありました。

10メートルでのリンクアップはすぐに発生しましたが、エラー率が大幅に増加しました。 データは送信できますが、非常に遅いです。 そして、TX PRESETSをどれだけ使っても、受信機をどのように調整しても、何も助けにはなりませんでした。 DFEを有効にすることにしました。 そして...何も起こりませんでした。

さらなる研究により、DFEには2つの動作モードがあるという事実に至りました。 信号の「目」を時間軸に沿って拡大することを目的とするEDFE(エッジDFE)、および振幅軸に沿って「目」の開口を増やすことを目的とするテストモードCDFE(中央DFE)。

EDFEは役に立ちませんでした。

Capella 1 PLXファミリのCDFEは、未知のレジスタの神秘的なペイントによってオンになります-ある種のコードシーケンスを入力することに非常に似ています。 メーカーの本質は明らかにされていません。 しかし、彼は私たちをかなり具体的に助けてくれました-120k x 10 -12からのBERは1.5kx 10 -12に落ちました。 しかし、これはまだ標準で必要とされるレベルを上回っており、さまざまなパラメーターを整理しながら、壁に頭をぶつけ続けました。

たとえば、受信機の感度、送信機の評価時間、反復回数など、さまざまなパラメーターを多数試しましたが、何も助けにはなりませんでした。 PLXスイッチのハードウェアと専用ソフトウェアを使用すると、各ラインのアイダイアグラムイメージを取得できると言わなければなりません。 しかし、アイダイアグラムを構築するために使用されるデータキャプチャポイントはDFEブロックの前にあるため、この関数は役に立たないことがわかりました。つまり、DFEが信号で何をするかがわかりません。 また、DFEの前には、閉じた「目」だけでなく、文字通り0があります(リンクアップは引き続き機能します)。

その結果、私たちは士気を失いました。 空母を止めることができないことに気付き、ボタンを探すことにしました。別の問題を取り上げ、それまで一時的に延期しました。 問題は、一般に、すべての回線でリンクアップが行われない場合があることでした。 これは、Gen1速度での初期接続に問題があったことを示しています-ラインが拒否されたのはこの段階だったからです。

Gen1キャリブレーションモードをオンにしました(テストを再度行いました)(標準作業では提供されていません)。 Gen1はまったく動作しなくなりました(明らかに、許容できるBERレベルに到達できませんでした)-しかし、レシーバーがリンクアップを試行しているパラメーター、照準を合わせて、突然、標準パラメーターとは別の宇宙にあることに気付きました。 興味を引くために、標準の0x09 / 0x05を0x09 / 0x0F(Gen1のアッテネーターをオフにした)で中断しました。

そして、安定したリンクアップGen1だけでなく、Gen3-0.3 x 10 -12のはるかに快適なBER値も取得しました。これはすでに標準フレームワークに適合しています。 Gen1受容体経路がGen3とどのように関連しているか-メーカーは言いません。 しかし、それは動作します。

光ケーブルで作業する

PCIeの機能のため、光ケーブルを個別に調整する必要がありましたが、10メートルの銅ケーブルをパンチングする作業と比較して、簡単でした。

簡単に言えば、状況は銅と光学素子では異なります。

銅との違いは何ですか

レシーバー検出

操作の開始後、PCIeトランスミッターは負荷のラインをチェックし始めます。 これは、回線の反対側の端から反射された信号を分析することにより行われます。 回線が受信機によって終端されていない場合、送信機はこの回線を認識して拒否します。

光レシーバの問題は、多くの場合、終端がPCIe仕様に適合していないこと、異なるインピーダンスに終端されていること、またはグランドに終端されていないことです。 これを見た送信機は、受信機がないと判断し、接続を確立する手順を開始しないことがあります。 光学系で正常に動作させるには、Receiver Detectブロックの信号をマスクすることをお勧めします。 言い換えれば、送信機に受信機を「見る」ように強制します。

電気的アイドル状態(以降-IDLE)

たとえば、低電力状態への移行によって引き起こされる非変調ラインのダウンタイムは、PINダイオードの過飽和につながり、この状態を抜けるときに問題を引き起こす可能性があります。 受信機は、光受信機の過渡状態に起因するノイズをIDLE状態から抜け出して誤った周波数にチューニングする可能性があります。 これにより、将来的に接続を確立する手順でこの回線が拒否されます。

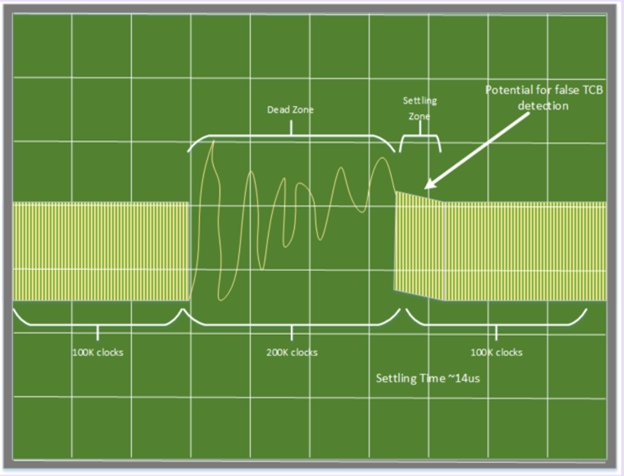

次の図は、IDLEが光学系に沿って発生したときにPCIeレシーバーが受信するものを示しています。

「デッドゾーン」がある場合-一定の信号レベルが必要です。 また、「整定時間」の値は、異なる行で異なる値を持つ場合があります。

推定アイドルモード

Inferred IDLEモードを使用する場合、受信機は送信されたデータのコンテキストを分析し、IDLE状態への入り口を決定するときに信号レベルに依存しません。 光ケーブルを使用する場合は、このモードを使用することをお勧めします。 彼なしで:

- 光レシーバーの過渡現象は、IDLE状態およびLTSSM状態マシンの後続の段階への誤ったエントリを開始する可能性があります。

- 1つのパートナーによるIDLE状態への移行は、2番目のパートナーによって認識されない場合があります。

PLXスイッチでは、これがデフォルトモードです。

ダウントレイン無効

接続を確立するプロセスで、レシーバーは最も古いまたは最も若い回線で接続をキャッチしようとします。 彼がこれを行うとすぐに、残りの行にはトレーニングを完了するための限られた時間があります。 上記の理由から、異なる回線の設定には非常に異なる時間がかかる可能性があるため、最後の回線で接続を確立した後、他の回線が間に合わない可能性があり、拒否されます。 すべてのポート回線を完全に構成しようとするために、レシーバーが指定されたチャネル幅以下で接続を確立しないようにすることをお勧めします。

チューニング

光デバイスは非線形であるため、受信機と送信機の校正係数を計算するときに信号の線形減衰に依存するため、バックチャネルチューニングメカニズムに依存することはできません。 場合によっては、それをオフにして、レシーバーとトランスミッターのパラメーターを手動で調整した方が良い場合があります。

一般に、光学を機能させるために制御できる多くのパラメーターがあります。 オンザフライでそれらにアクセスできるように、アダプターにCPLDチップをインストールしました。 スイッチメーカーが推奨するすべてのパラメーターを一度に使用することから始めましたが、何も起こりませんでした。 次に、1つのパラメーター、つまり、Receiver Detectブロックをオフにすることを忘れていることがわかりました。

彼らはそれをオンにし、光学が生き返った。

次に、Receiver Detectを除くすべてのパラメーターをデフォルト状態に戻しました。 光学は生き続けました。

マスキングレシーバー検出は、作業ケーブルおよびパッシブ銅ケーブルを妨害しません。 したがって、両方のタイプの接続で動作する構成を取得しました。

チャネルにエラーが表示されることもありますが、その発生頻度は標準の範囲内です。 そして、実際には光学系に関するチューニングにまだ取り組んでいないので、つまり、これらのエラーを無効にできるという強い信念です。

この問題に関する研究者は開発者を非常に怖がらせ、ケーブル間の生産ばらつきが大きいため、2本のx4ケーブルからx8接続を組み立てるのは非常に難しく、さらにx4-4 x4ケーブルからx16を組み立てることは非常に困難です。 したがって、これらのリスクを最小限に抑えることを目的として、ボード上のすべてのトラックを100 psに揃えました。 これに意味があるかどうかはわかりませんが、100メートルの光学系での4つのx4からx16のリンクの集約に問題はありませんでした。

一般的な問題

使用するケーブル接続(光ケーブルと銅線の両方)には、次の落とし穴があります。

- 基準クロック信号はラインで送信されません(以下、クロックと呼びます)。

- I2Cは回線で送信されません。

- PERST#、PRSNT#、および他の側波帯は回線で送信されません。

細断

通常、通常のチャネルのアップタイムにはPCIeブロッキングが必要です。 ただし、使用するスイッチはSRIS互換です。 SRIS-個別の参照非依存スプレッド。 簡単に言えば、それらは異なるシュレッドで機能するだけでなく、これらのシュレッドはSSCである可能性があります。

SSC

スペクトラム拡散クロッキングは、30〜33 kHzの周波数で0〜-5000 ppmの間隔でクロック周波数を変調します。 EMRを減らすために使用されます。 この場合、ブロック周波数は常にわずかに変動するため、放射パワーはスペクトル内で不鮮明になります。

この場合、2つのSRISデバイスを接続している場合にのみ通常の操作が可能です。 ホストプロセッサがロックなしで何かに直接接続されている場合、パフォーマンスは保証されません。 ホストプロセッサで使用されるクロックがSSCを使用しない場合、x86プロセッサがPLXデバイスとケーブルレス接続されているときに正常な動作を観察しましたが。 これはSRNS-個別参照拡散なしと呼ばれます。

アダプタには独自の細断処理サブシステムがあり、システムPCIe細断処理のすべてをクロックし、独自に動作させることができます。これは、SSCまたは非SSCのいずれかです。

テストの結果、システムシュレッドの作業は好きではありませんでしたが、システムのみで作業することを望み、シュレッドに関連する残りの回路図は削除しました。

非SSCとSSCの両方の細断処理は、最大4メートルのパッシブ銅ケーブルと光ケーブルを使用した場合に安定しており、信頼性があります。 10メートルの銅ケーブルの場合、通常のチャネル動作は現在、非SSCクロックでのみ実現されています。

I2C

これはオプションのインターフェイスであり、一般に、それを渡さなければ何も失われません。 転送していないことに注意する必要がありました。

その他の側波帯

その欠如は、例えば、そのような問題を伴います:

- すべてのPCIeデバイスが1つのボックスにある場合に発生するように、PCIeツリー全体を同期的にリセットできない。

- PCIeバス上のデバイスの突然の消失と追加に関する問題。

そして、一般的な言葉と呼ぶことができる他の同様のもの-同期。

これらの問題はよりグローバルなアプローチを必要とし、システム統合の段階で解決されます。 現時点では、ホストシステムが標準のブートプロセスでPCIeデバイスを通常列挙できるように、ターゲットの後にホストシステムの電源を入れるようにします。

また、NTBを使用する場合、この問題は関係ありません。

オプションとアナログ

実際、 前の記事でAlexeyが既に言及したように、2つのバージョンのアダプターがあります。 2番目のオプションにはPCIeスイッチが装備されていませんが、単純なリドライバーがあります。 これは安価なオプションであり、ポートの分岐が不要な場合に適しています。

また、使用する比較的安価なPCIeスイッチチップにはDMAコントローラーがないことも言う必要があります。したがって、これらの2つのアダプターを相互に接続すると、速度は遅くなり、プロセッサーに大きく依存します-動作するデータブロックとその方法によって異なります。 DMAコントローラーアダプターが少なくとも1つある場合、実際の速度は通常、物理的に使用可能な制限の約50〜60%です。つまり、一方向に約8〜9 GB /秒です。もちろん、1回のデータ転送操作は16 GB /秒の速度で発生する可能性があります。 PR-schikiは32 GB / sの書き込みを好みます-これは両側の物理的な制限です。ただし、PCIeバスでの情報のやり取りは通常双方向です。完了応答は各トランザクションのターゲットを送信します。したがって、32 GB / sのパフォーマンスでの作業は非常に疑わしいようです。

当然、このチップの選択は非常に合理的です。計画されたユースケースでは、少なくとも1つのアダプターに必然的にDMAコントローラーが搭載されます。したがって、このケースでは、DMAサポートが組み込まれたより高度なPCIeスイッチチップの半分を支払うことは意味がありません。

このアダプターを個別の製品として販売する予定はありません。これは当社の活動分野ではありません。当社独自の機器からの統合ソリューションにのみ搭載します。 DMAコントローラを備えた同様のアダプタが必要な場合、そのようなソリューションが市場に登場しています。Dolphin PXH830(HBA)またはPHX832(ホスト/ターゲット)を見ることができますが、これらのアダプターにはわずかに異なるパラメーターがあります。

モデル830には、ポートを2 x8または1 x16に分割する機能がありますが、4 x4モードにはありません。モデル832は4 x4モードで動作できますが、最大5 mのパッシブケーブルのみです。両方のモデルについて、最大100 mの長さの光ケーブルのサポートが発表されています。

次は?

その結果、アダプターは最大10メートルの銅線ケーブルと最大100メートルの光ケーブルで機能し、どちらの場合もBERは許容範囲内です。レイヤー数を減らした2番目のリビジョンをリリースし、レイアウトを改善し、結果をさらに洗練するために光学系のパラメーターを微調整してテストおよびプレイする予定です。

ご清聴ありがとうございました。