デジタル伝送システムを研究する過程で、またメンターの推薦で、研究されている資料をよりよく理解し、棚にすべてを置くために、私はこの資料をあなたに説明しようとします。成功したら、私はそれをよく学んだと仮定できます。 興味を持っていただければ幸いです。

この記事では、DSPとその構成、PDI(PDH)の機能について簡単に説明し、E1のフローとその構造について詳しく説明します。

デジタル伝送システム

デジタル伝送システム構築の特徴

世界中の電気通信の発展の主な傾向が通信ネットワークのデジタル化であり、これがデジタル伝送およびスイッチング方式に基づくネットワークの構築を提供することは誰にとってもニュースではありません。 これは、アナログよりもデジタル伝送方式の次の重要な利点によるものです。

高いノイズ耐性。

- 通信回線の長さに対する伝送品質の弱い依存。

- DSPチャネルのパラメーターの安定性。

- 離散信号の送信にチャネル帯域幅を使用する効率。

- デジタル通信ネットワークを構築する能力。

- 高度な技術的および経済的指標。

DSPの要件はITU-T Gシリーズの推奨事項で定義されており、この推奨事項は2つのタイプのDSP階層も示しています。プレシオクロナスデジタル階層(DSP)と同期デジタル階層(SDH)です。 すべてのタイプのDSPの主な信号は、メインデジタルチャネル(BCC) [外部ソース:Basic Digital Circuit(BDC)]と呼ばれる64 Kbpsの伝送速度のデジタルストリームです。Habréでは、 この記事でHFのチャネルのデジタル化がどのように行われるかについて既に説明しました。 チャネルの時分割(WRC)の原理[外部ソース:時分割乗算アクセス(TDMA)、または時分割多重化(TDM)]は 、BCC信号をグループ高速デジタル信号に結合するために使用されます。

プレシオクロナスデジタル階層

歴史的に最初に出現したプレシオクロナスデジタル階層(PDI) [外部資料:プレシオクロナスデジタル階層( PDH)]は、歴史的に出現しており、ヨーロッパ、北米、および日本の品種があります。

| 階層レベル

| ヨーロッパ

| 北アメリカ

| 日本

| |||

|

| Mbpsの速度

| 係数 多重化

| Mbpsの速度

| 係数 多重化

| Mbpsの速度

| 係数 多重化

|

| 0

| 0,064

| -

| 0,064

| -

| 0,064

| -

|

| 1

| 2,048

| 30

| 1,554

| 24

| 1,554

| 24

|

| 2

| 8,448

| 4

| 6,312

| 4

| 6,312

| 4

|

| 3

| 34,368

| 4

| 44,736

| 7

| 32,064

| 5

|

| 4

| 139,264

| 4

| -

| -

| 97,728

| 3

|

対応する表記は、北米-T、日本語-J(DS)、欧州-EのPDIのデジタルフローに使用されます。第1レベルのデジタルストリームは、T1、E1、2番目のT2、E2、J2などのT1と指定されます。

ロシア連邦の通信ネットワークで使用するために、欧州PDIを採用しました。

ロシア連邦の通信ネットワークでは、国内および海外生産のDSPPが運用されています。 国内のシステムは、PCM(パルス符号変調を備えたデジタル伝送システム)を備えたDSPと呼ばれます。 階層レベルの代わりに、システム指定はシステムの情報BCCの数を示します。 したがって、階層の最初のレベルのDSPはIKM-30、2番目のレベルはIKM-120などとして指定されます。

同期の基本原則

プレシオクロナス、「同期のように」DSP、SQFの原理が使用されるため、受信および受信ステーションでの発電設備の同期および共通モード動作でのみ、受信時の初期信号の正しい復元が可能です。 プレシオクロナスDSPの通常の動作では、次のタイプの同期を提供する必要があります。

クロック同期により、リニアおよびステーション再生器、コーデック、およびクロック周波数Fで信号を処理する他のDSPデバイスでのデジタル信号の処理速度が等しくなります。

クロック同期にはいくつかのオプションがあります。

- 双方向インターフェース:追加のクロック伝送は、個別の回線で実行されます。

- 逆方向インターフェース:1つのユニット(制御)が別の(従属)動作クロック周波数を設定します。

- 中央集中型マスター(マスターオシレーター)とのインターフェース:マスターオシレーターはすべての機器ノードのクロッキングを実行します。

ループ同期は次のとおりです。 送信局では、サイクルの開始時にグループデジタル信号にデジタルクロック信号(CC)が導入されます。 クロックレシーバー(MSS)が受信局に設置され、グループデジタル信号から周期的なクロック信号を抽出し、それによって送信サイクルの開始を決定します。

ストリームE1

ストリームE1の構造。

フローE1には3つのタイプがあります。

- 非構造化(KIチャネル間隔[外部ソース:タイムスロット]への分割はありません、論理構造は割り当てられません; 2048Kbit / sの速度のデータストリーム); データを送信するときに使用されます。

- 循環構造のフロー(チャネル間隔は割り当てられますが、制御および相互作用信号(SUV)は送信されません)-IKM-31;

- スーパーサイクル構造のストリーム(サイクリック構造とスーパーサイクリック構造の両方が区別されます)-PCM-30。

伝送フレームDSP IKM-30の構造を考慮してください。

E1ストリームの構造は、ITU-T G.704で定義されています。 このストリームはプライマリデジタルストリームと呼ばれ、30の情報BCCの連合によって編成されています。

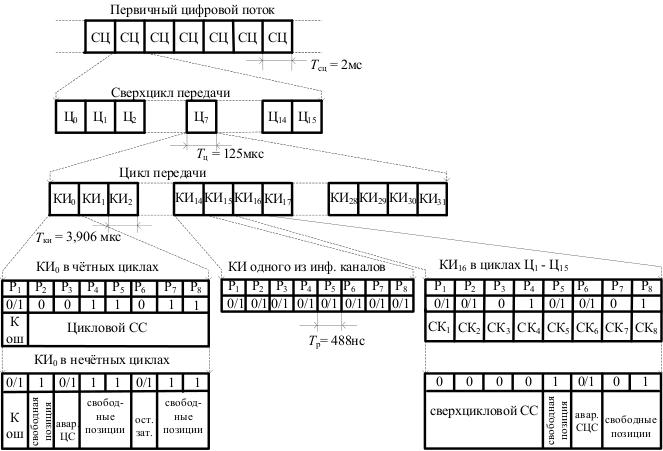

システムの線形信号は、上図に示すように、スーパーサイクル、サイクル、チャネル、およびクロック間隔に基づいて構築されます(指定0/1は、所定のクロック間隔でのランダム信号の送信に対応します)。 送信スーパーサイクル(SC)は、60の信号チャネル(SC)およびアラーム送信チャネル(スーパーサイクルまたはサイクル同期の喪失)の各カウントが送信される最小時間間隔に対応します。 SC TSCの期間= 2ミリ秒。 スーパーサイクルは、16の送信サイクル(Ts0からTs15)で構成されています。 サイクル期間はTC = 125μsで、8 kHzの周波数のPMチャネルのサンプリング間隔に対応します。 各サイクルは、Tk = 3.906μsの持続時間で32チャネル間隔(タイムスロット)に分割されます。 チャネル間隔KI1-KI15、KI17-KI31は、情報信号の送信用に予約されています。 KI0およびKI16-公式情報の送信用。 各チャネル間隔は、Tr = 488nsの持続時間を持つ8つの放電間隔(P1〜P8)で構成されます。 放電間隔の半分は、この放電でユニットを送信するとき、持続時間Ti = 244 nsの矩形パルスで占められます(ゼロを送信するとき、放電間隔にパルスはありません)。 偶数サイクルの間隔KI0は、形式0011011を持ち、間隔P2-P8を占める巡回クロック信号(DSS)を送信することを目的としています。 すべてのサイクルの間隔P1では、パーマネントデータ伝送チャネル(DI)の情報が送信されます。 奇数サイクルでは、周期P3およびP6 KI0を使用して、周期的同期の喪失(Avar。-LOF)およびチャネルの残留減衰の自己励起が発生する可能性のある値への減少(残存)に関する情報を送信します。 間隔P4、P5、P7、およびP8は自由であり、クロックアイソレータの動作を改善するために単一の信号で占有されています。 ゼロサイクル(Ts0)の間隔KI16では、フォーム0000(P1-P4)のスーパーサイクル同期信号と、スーパーサイクル同期の喪失に関する信号(P6-Avar。STsS-LOM)が送信されます。 残りの3ビット間隔は無料です。 残りのサイクル(Ts1-Ts15)のチャネル間隔KI16では、サービスチャネルSK1とSK2の信号が送信され、SKはTs1のPMの1番目と16番目のチャネルで送信され、2番目と17番目のTs2などで送信されます。 。 間隔P3、P4、P6、およびP7は無料です。 電話チャネル伝送の観点から:電話チャネルは8ビットカウントです。 ペイロードは、2人のサブスクライバー間の会話です。 さらに、サービス情報が送信されます(ダイヤル、電話の切断など)-制御および相互作用信号(SUV)。 このような信号を送信するには、15サイクルごとに1回繰り返すだけで十分ですが、各SUVは4ビット(特定のチャネルのSUV)を占有します。 これらの目的のために、16番目のチャネル間隔が選択されました。 1つのチャネルには、2つの電話チャネル用のSUVが配置されます。 なぜなら 1つの会話では30チャネルのみ、2チャネルが使用されるため、サイクルを15回繰り返す必要があります。したがって、Ts1からTs15まで、SUVに関するすべての情報を送信します。 したがって、サイクル数を決定する必要があります。 これらの目的のために、ゼロサイクルにはスーパーサイクルSS(1 4バイトの「0000」–MFAS)が含まれます。 6番目のビットでは、スーパーサイクルの損失(LOM)が送信されます。

E1ストリームの構造を説明しようとする人に出会わなければなりませんでした。E1ストリームをパイプとして提示し、その中に小さいサイズ(32タイムスロット)の32本のパイプが詰め込まれました。 PDIでは、データはビット単位で順番に送信され、並列ではありません。

伝送エラー制御

伝送エラーを制御するために、ゼロチャネル間隔の最初のビットが使用されます。

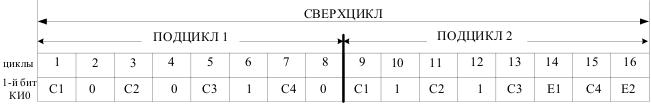

さまざまなサブサイクルの最初のビットKI0の内容。

多項式x4 + x + 1は、エラーの存在を決定します。 ビットC1、C2、C3、C4は、サブサイクル(8サイクル)を多項式x4 + x + 1で除算した余りです。 この場合、結果は次のサブサイクルに挿入されます。 1番目のサブサイクルの値を取得し、2番目のサブサイクルと比較します。不一致がある場合は、エラーメッセージが発行されます。 ビットE1およびE2は、1番目と2番目のサイクルでエラーメッセージを送信側に送信するように設計されています(E1-1番目、E2-2番目)。 偶数サイクル(14と16を除く)で正しく処理するために、エラーを制御するためにスーパーサイクルクロック信号(001011)が導入されています。

PDIの物理層OSIモデル

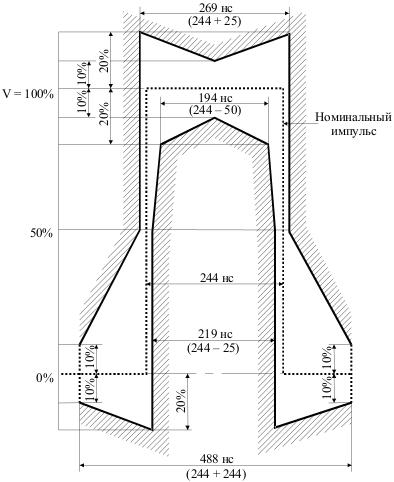

物理層には、線形コードの構造を含む、インターフェースの電気パラメーターと伝送信号のパラメーターの説明が含まれます。 これらのパラメータは、ITU-T勧告G.703で説明されています。

次の物理インターフェイスがPDIに対して定義されています。

- E0-対称ペア(120オーム);

- E1-同軸ケーブル(75オーム)または平衡ペア(120オーム)。

- E2、E3、E4-同軸ケーブル(75オーム)。

- E0-AMI;

- E1、E2、E3-HDB3;

- E4-CMI。

2048 Kbpsストリームの物理インターフェイスのパルスマスク。

これで、あなたはやめることができると思います。 ご清聴ありがとうございました、あなたが興味を持っていたことを願っています。

この記事が気に入ったら、同期デジタル階層(SDH) [外部ソース:同期デジタル階層(SDH)]および同期トランスポートモジュール(STM) [外部ソース:同期トランスポートモジュール(STM)] -STM- 1。

文学

プライマリネットワーク測定テクノロジー-I.G. mor;

最新の高速デジタル通信システム-V.N. ゴルディエンコ。

UPD:英語の用語と略語で記事を少し補足しました。