Political Correctness Penetrates Russia Through Books on Designing Chips on SystemVerilog for Non-Beginners

Finally, a textbook on SystemVerilog was released in Russia at a level higher than for beginners . The textbook describes the technologies and techniques that are asked for interviews at NVidia, Intel, AMD, Apple and other electronic companies: the use of concurrent assertions and functional coverage, which now require not only verification engineers, but also chip designers; the algorithm of the simulator with delta cycles; sane explanation of static timing analysis; communication diagrams of hardware units through hardware queues; the implementation of these communications using finite state machines with data paths, etc.

In the chapter on the latest, the Russian reader may be puzzled by the mention of a “politically correct system”. What would that mean? This is probably an allusion to the incident that occurred in Los Angeles County in 2003. Los Angeles officials asked manufacturers, suppliers, and contractors to stop using the terms “master / slave” for computer equipment, as one of the county’s employees was reminded of the slave past.

Now technical literature authors are avoiding the terms master / slave. African-American engineers also work in modern America (for example, Sofia Mvokani from Cameroon - on the photo on the left), and the use of old terms looks archaic, as for example the terms “pan / slave” in Ukrainian technical literature would look instead of the accepted “past / leading” ( Russian “leader / slave”).

This is not the first time that the theme of the struggle of African-Americans for civil rights appears in Russian e-education. For example, Tatyana Volkova, a well-known specialist in education in electronics, wears a T-shirt with the emblem of “Black Panthers”, the California movement, which at one time considered the peaceful protest insufficient, and engaged in armed protest.

The full image of the emblem under the skin of Tatyana Alexandrovna is under the cut, but mainly I will talk about delta cycles and state machines:

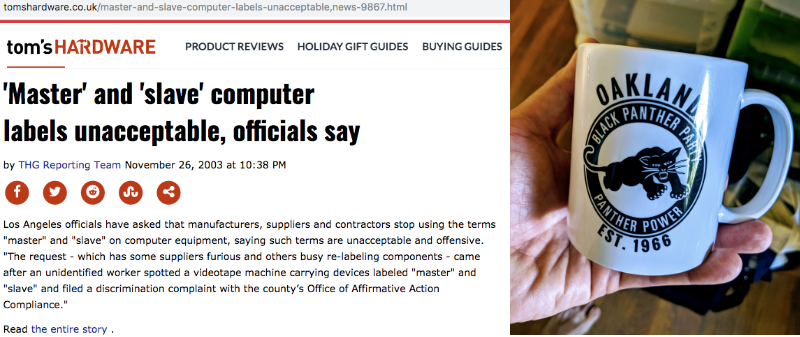

Below is a screenshot of the article about master / slave and the promised Black Panther emblem, after which we move on to the book as such.

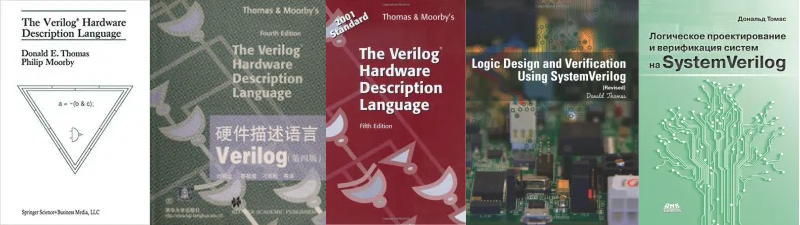

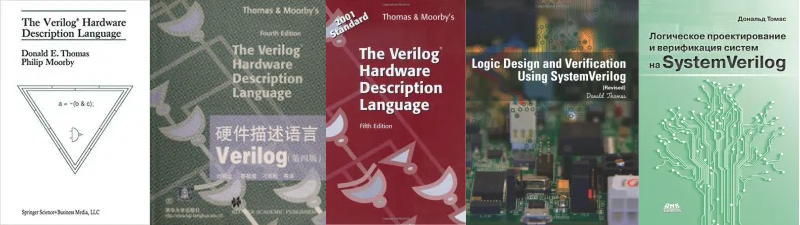

First of all, Donald Thomas, author of the book “Logical Design and Verification of Systems on SystemVerilog” (2019 in Russian from DMK-Press, 2016 in English) is the same Donald Thomas, who co-authored with Philip Murbi wrote a book 1991 The Verilog Hardware Description Language by Donald Thomas and Philip Moorby. Then, in 1991, many electronic companies still designed microchips in the old fashion, drawing them with the mouse on the screen; logical synthesis technologies have just left the laboratory for production; hardware description languages were considered intended for writing models and tests, and not source codes for creating final circuits; in addition to VHDL and Verilog closed at that time, there were many small and proprietary languages such as Abel, CUPL, PALASM; and Intel and MIPS had internal hardware description languages.

In this situation, the book of Thomas and Murbi came out, which became the same for the designers of digital circuits of the 1990s as the book for Kernigan-Richie for the programmers for C, and the books of Bjarni Straustrup for the C ++ programmers. The book withstood five editions - from 1991 to 2002, but for the era of iPhones was clearly insufficient. And in 2016, Donald Thomas decided to catch up and released a new book in which he described the key innovations in the language and methodology over 25 years. The very 25 years during which Verilog became a common base for the entire industry, schemes for everything are written on it - from the notorious iPhones and control computers in Tesla to Russian military helicopters.

Next, I will highlight my comments with blue text to separate them from the pictures from the book.

Even before the main text of the book, there is the pre-chapter “Context: Design at the Level of Register Transfers”, so that a programmer, schoolchild, or, say, a lover of exercise with prototyping boards, taking this book from the shelf, immediately understands what is being said and how they can use the book. It says:

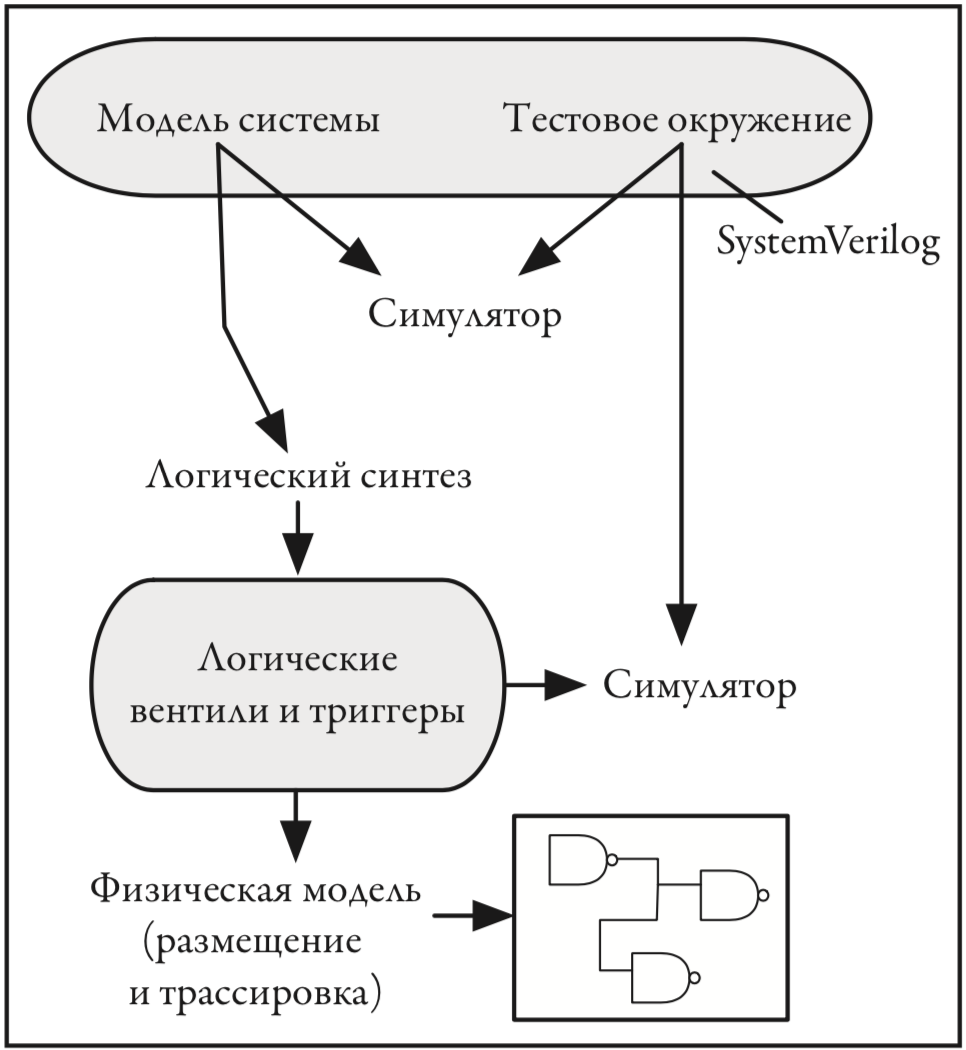

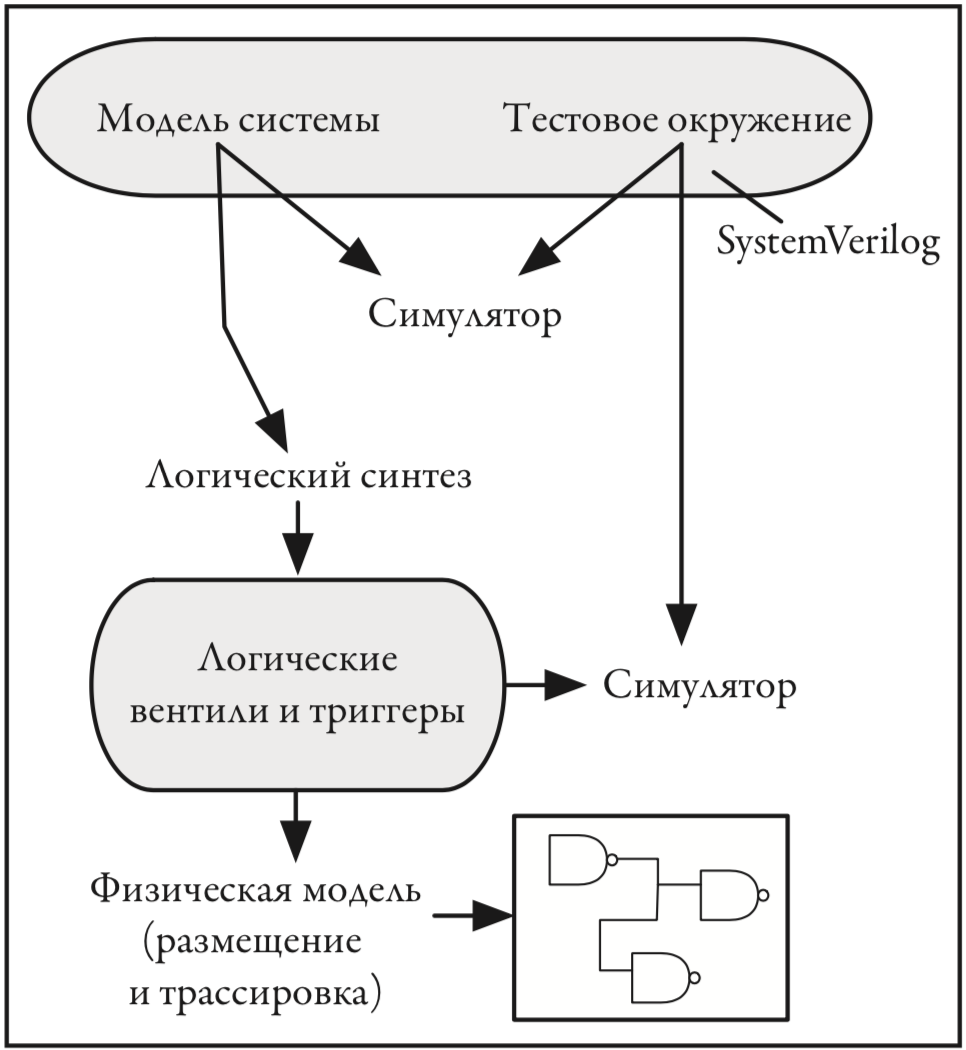

In this case, here is such a simplified picture to illustrate how the text on the veril turns into tracks and transistors of the microcircuit in the factory:

The first word in the book after the preface is “simulator”. To understand the hardware description languages, you need to be clearly aware that the synthesized subset of the verilogue is not a programming language, but a language for describing electrical circuits. Like let's say HTML is not a programming language, but a language for describing web pages. While the programming language is intended to be compiled into a chain of processor instructions, the hardware description language is intended to be converted (in particular) into processor iron as such. In this case, before casting into iron, the code in the hardware description language needs to be checked, for which purpose a specialized interpreter, called a simulator, serves.

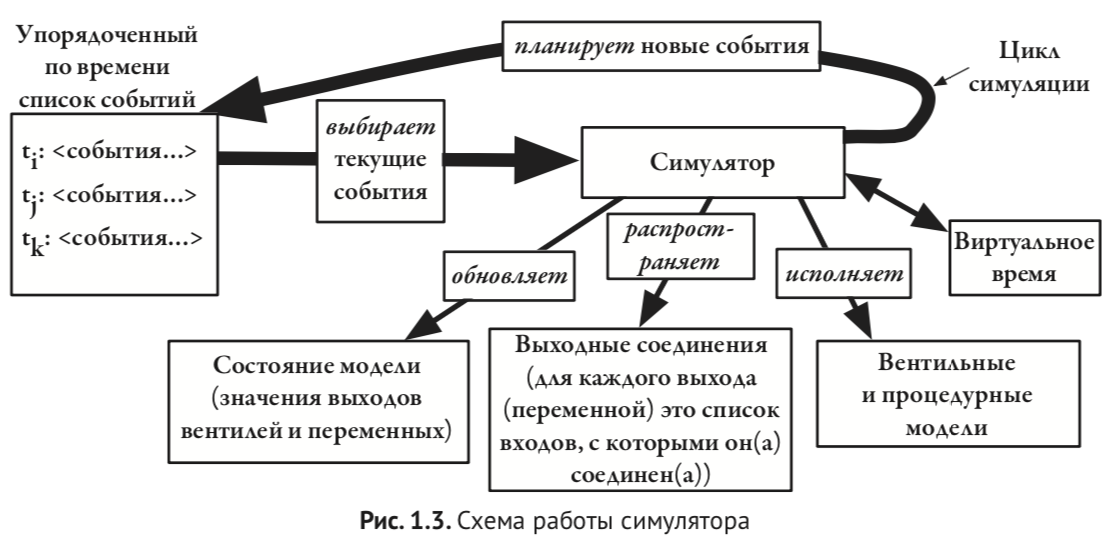

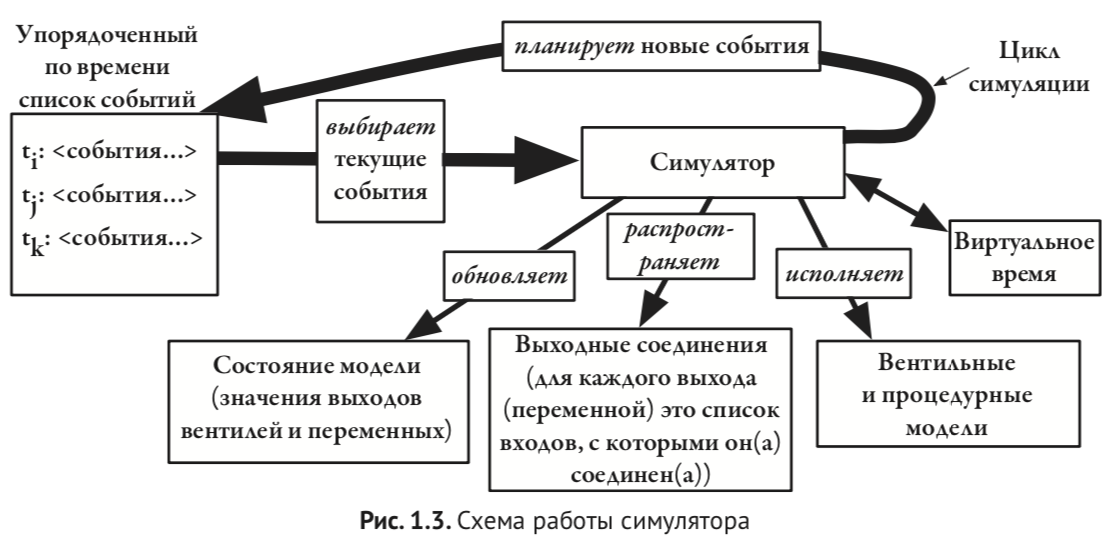

At the beginning of the book, Donald Thomas shows a simplified picture of the simulator, and at the end of the book he clarifies and supplements it:

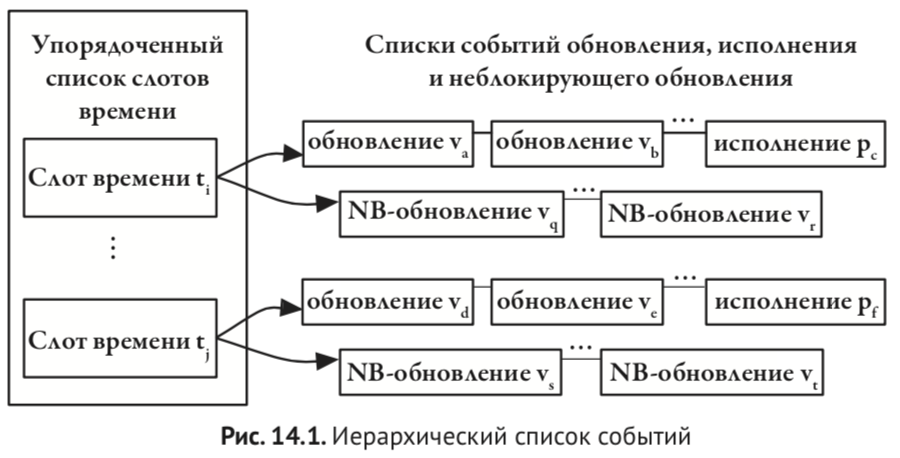

The simulator has event queues and simulated time:

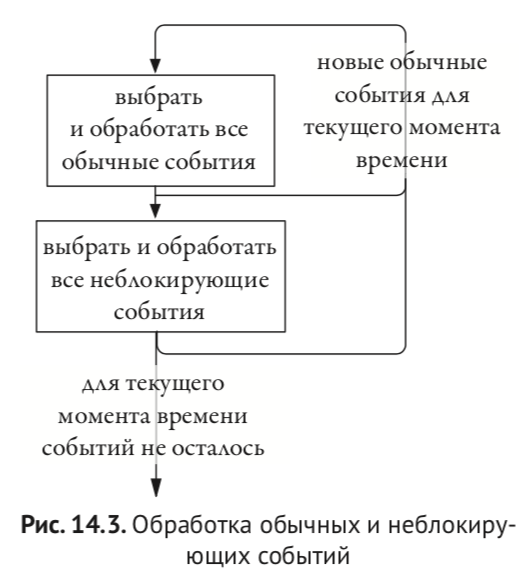

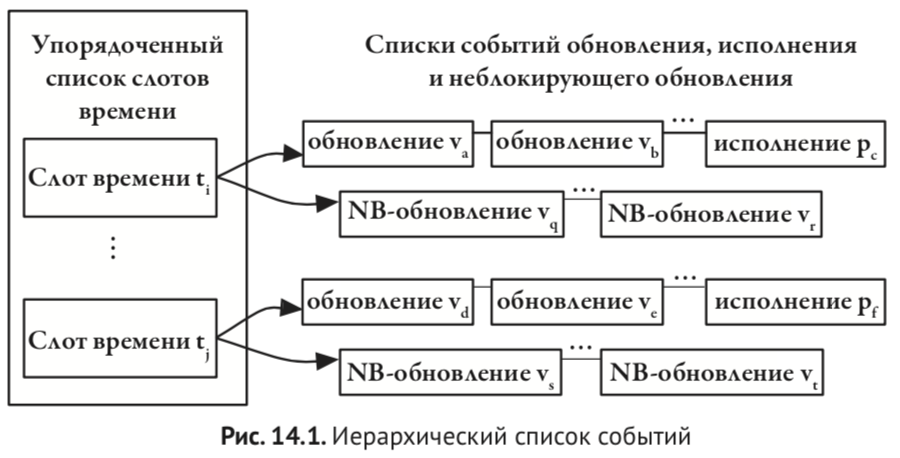

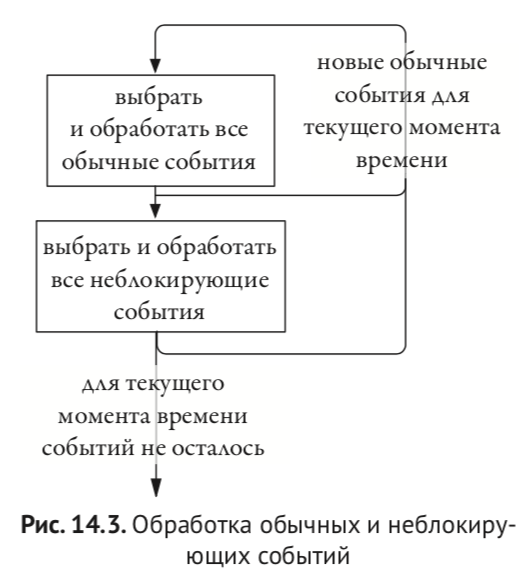

An event can give rise to a new event, both at the current moment of simulation (in the current delta cycle) and in the future tense. In the current delta cycle, all events generated by the so-called blocking assignments are processed first, and then events generated by non-blocking assignments are processed. This is necessary for the correct simulation of parallel semantics of the propagation of electrical signals in iron:

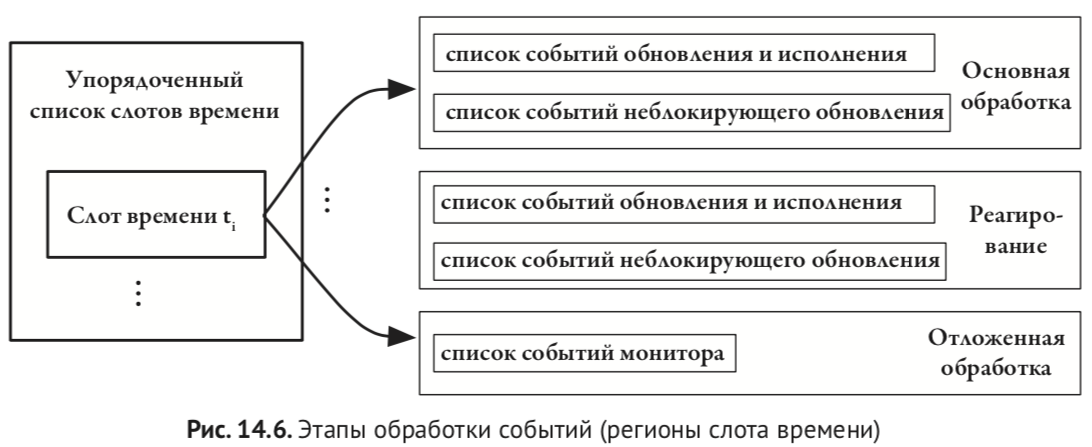

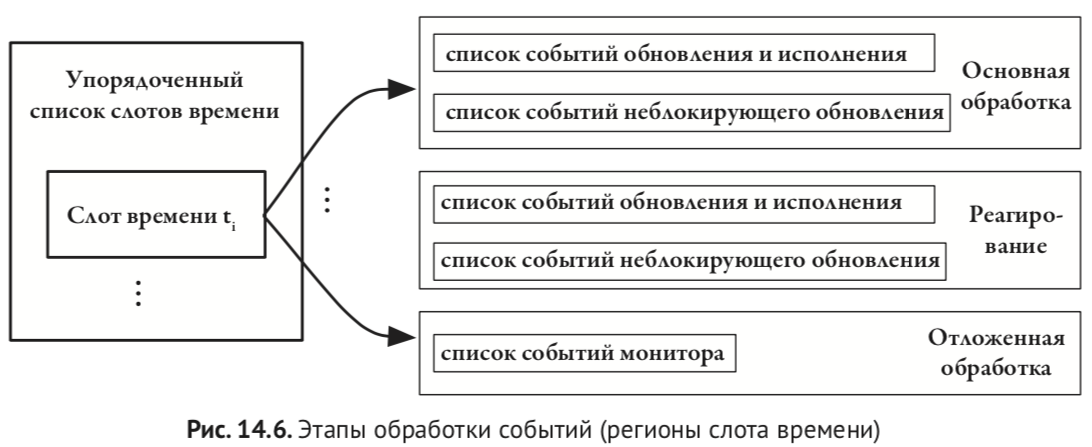

In addition to the synthesized subset of the verilog, there is also a non-synthesized subset. It is intended to describe the test environment and tests, and now it can be considered as a kind of programming language. For test environment events and monitors, additional simulator steps are introduced:

Accurate knowledge of the algorithm of the simulator is very useful to avoid a variety of bugs associated with the so-called race (race condition). When I intervene engineers, I always ask them to give an example of race condition in Verilog. Moreover, if for young RTL Design and Design Verification Engineers such knowledge is very desirable, but not in all aspects 100% necessary, that is, professions in which money is paid directly for this knowledge. I am talking about programmers who work in the Synopsys VCS, Cadence IES, and Mentor ModelSim teams.

Synopsys and Cadence are two companies located in California within a 15-minute drive of each other. They employ only a few thousand people, but they control the development of microcircuits around the world - in Intel, Apple, Samsung, Huawei, even in secret Russian institutes that make chips for military equipment.

If comrades Putin, Rogozin and Vekselberg really want to introduce import substitution in Russia, then they could finance the development of the Russian analogue Synopsys VCS (for simulating a verilogue), Synopsys Design Compiler (for logical synthesis of a verilogue) and Synopsys IC Compiler (for physically posting the results of logical synthesis ) There are probably several thousand mathematically savvy programmers in Russia.

Although licenses for these software products are fairly easy to break, using them without a support is difficult. If Huawei is disconnected from Synopsys and Cadence, they will have in some sense worse than disconnecting from Android and even ARM cores.

Yes, so here is the refined algorithm at the end of Donald Thomas’s book. If you don’t learn it by heart, it is useless to intervene in the simulation groups in Synopsys, Cadence, Siemens / Mentor, Xilinx, and there they will ask you to draw it on the board and suggest how to optimize some particular case:

After clarifying the simulation at the beginning of the book, Donald Thomas describes SystemVerilog as such. This language emerged as a Verilog superset in 2002, as a result of the merger of the Verilog-2001, Vera and Superlog languages, and with the addition of ideas from the Property Specification Language (PSL), which were transformed into SystemVerilog Assertions (SVA).

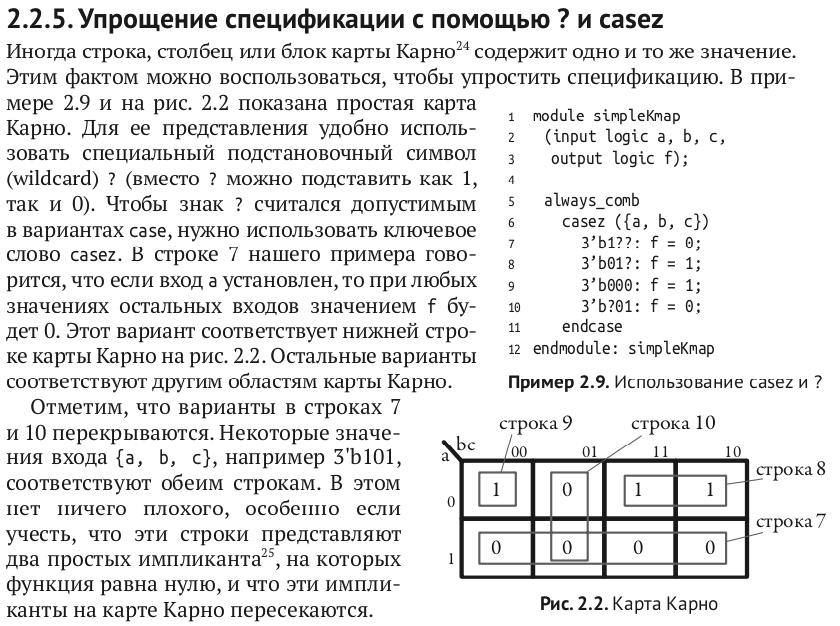

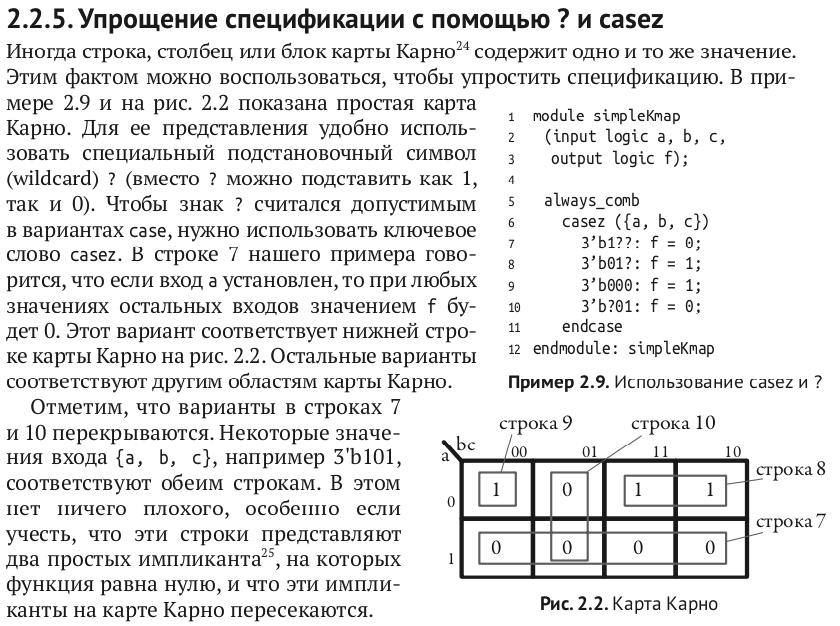

Donald Thomas believes that you have already learned the basics of digital design somewhere, and therefore weaves into the narrative fabric various well-known pieces such as Carnot cards. Carnot maps were used for manual design of circuits in the 1960s, after which this method was replaced by automatic optimization of logic using the Quine - McCluskey algorithm and automatic logic optimizer Espresso. Therefore, Carnot cards are present in all university textbooks on the design of digital logic, but they seem to hang in the air. And here Donald Thomas attaches Carnot maps to the life of a designer on a 21st century verilo:

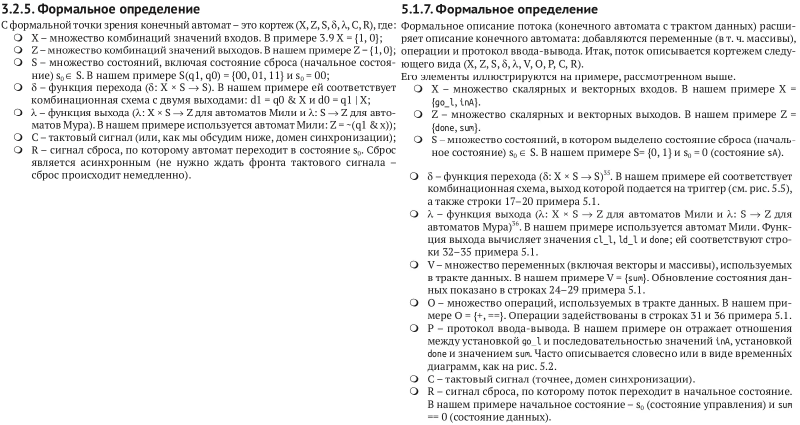

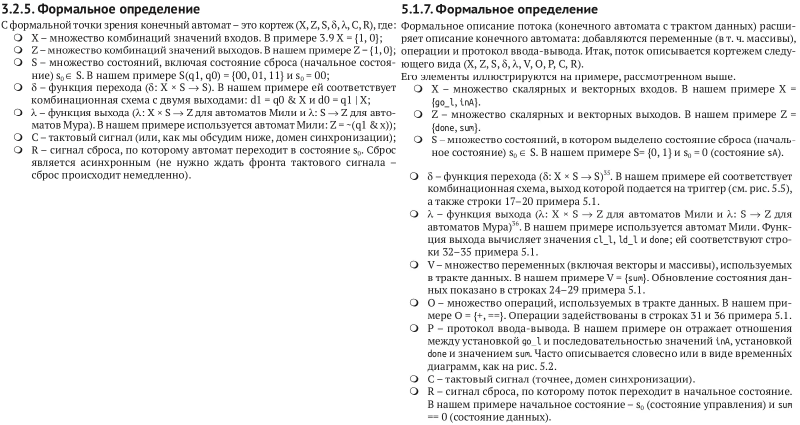

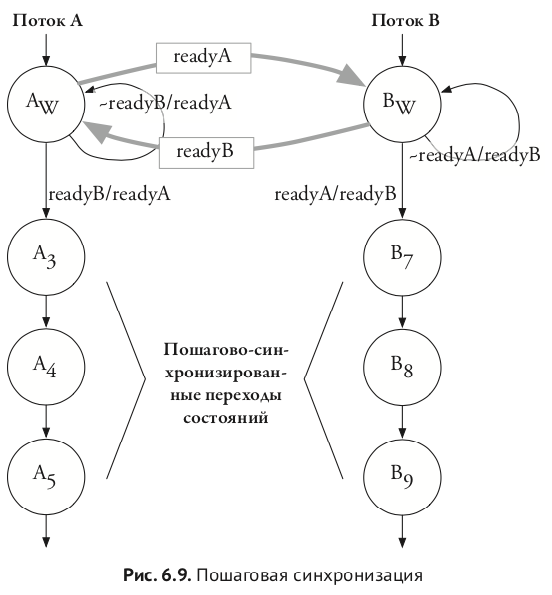

Further, Donald Thomas writes about finite state machines, and he gives 1) a rigorous mathematical definition; 2) diagrams; 3) code; 4) after which it begins to expand them to finite state machines with a data path - hardware flows; 5) after which these flows begin to interact with him, both according to simple “politically correct” (see above) protocols, and using hardware queues.

Here is the code for a simple automaton with a data path that Thomas cites as a first example:

Next, Thomas has a chapter on static timing analysis. Nothing special, but cleaner than on many popular Indian sites, "How to get through a VLSI interview." And also more fully than in some books on veril, which tediously chew on the syntax of the language, but do not really show how to use it.

Why do we need static timing analysis? In real hardware, unlike the illusion that the processor shows the programmer, each calculation goes through a time interval when all the garbage is on the wires - not only clearly calculated zeros and ones, but also any random glitches, that is, glitch, and generally non-digital values in the forbidden zone. For example, if you have all voltages above 0.7 volts considered as a digital unit, and all voltages below 0.3 volts as a digital zero, then 0.4 volts may appear on the wire.

In the end, all the signals in the circuit go their own way and the situation settles down, but this “in the end” should be less than the cycle of the clock signal (clock). This cycle is inversely proportional to the frequency at which the circuit operates (gigahertz, megahertz).

If the settled result of calculations or logical operations does not fall into the D-trigger (minimum memory element) at the moment of the aperture (interval around the change of such a signal), the state of the circuit will become garbage - the satellite or reactor will explode, the iPhone will stop answering calls. The entire equipment designer needs to know no less ironically than logic.

Why is the analysis static? In the 1980s, it was dynamic - delays were clarified through simulation. This turned out to be unreliable for circuits with hundreds of thousands, millions and billions of transistors, and now all delays are calculated statically, based on the analysis of signal paths after synthesis.

The clock signal can also come to different parts of the chip with some delay, which adds another uncertainty to this kitchen that needs to be eliminated (fortunately, not manually, but with the help of clock synthesis tree programs and other methods):

In the chapter on flows, Thomas discusses several basic options for how parallel operating state machines with data paths can exchange information, including using buffers and queues. As in the design / circuit itself, at the level of register transfers, so in the behavioral model or test environment of the circuit. When reading Thomas, it’s nice to write and debug examples yourself for all cases of the protocols described by him. The fact is that they like to write code on such topics (a small controlling state machine, a data flow between two modules, pipelined data paths or just a code for a hardware queue) during a second-level interview in electronic companies. If you can write an example for any of the combinations described by Thomas in 20 minutes with a code of 30-50 lines, then you will make a good impression. Hard to learn - easy in battle.

The test environment for routers (Fig. 8.3) with queues for several ports is a popular example that is used to explain verification methodologies. Probably because some of these methodologies were invented by Cisco and other companies designing chips for network hardware.

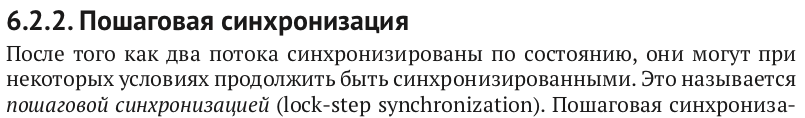

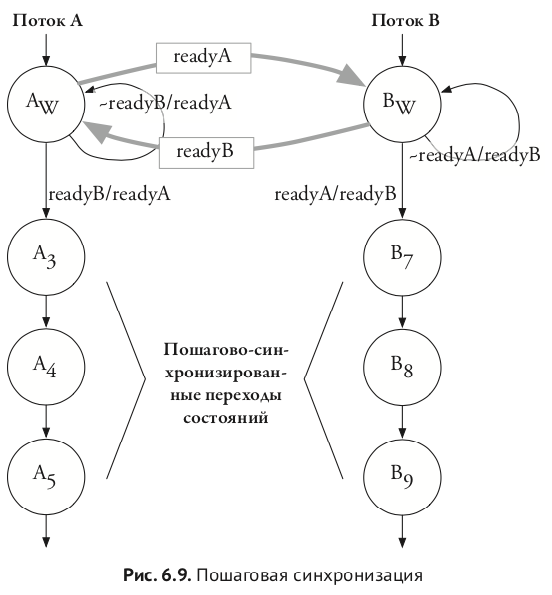

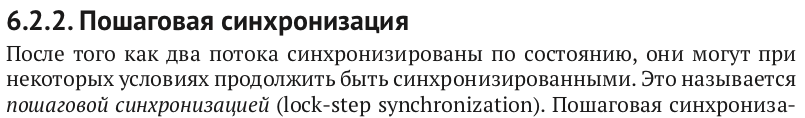

In chapter 6.2.2. Thomas describes one of the options for the interaction of flows - step-by-step synchronization (Lock-step). One of the lock-step applications is high-reliability systems, for example, in automotive electronics. A special case: two processors can execute the same program with a delay of several cycles, and during this execution a special circuit can check that they have the same results.

Thomas was clearly concerned with reliability, since in addition to the lock-step, he cites the use of CRC, cyclically redundant code to detect errors in data transfer. At the same time, Thomas talks about how to calculate CRC using LFSR, a linear feedback shift register. Both that, and another need to be able to a young engineer. This is the advantage of Thomas’s book - although it doesn’t always dig deep, it touches on many topics and shows where to dig:

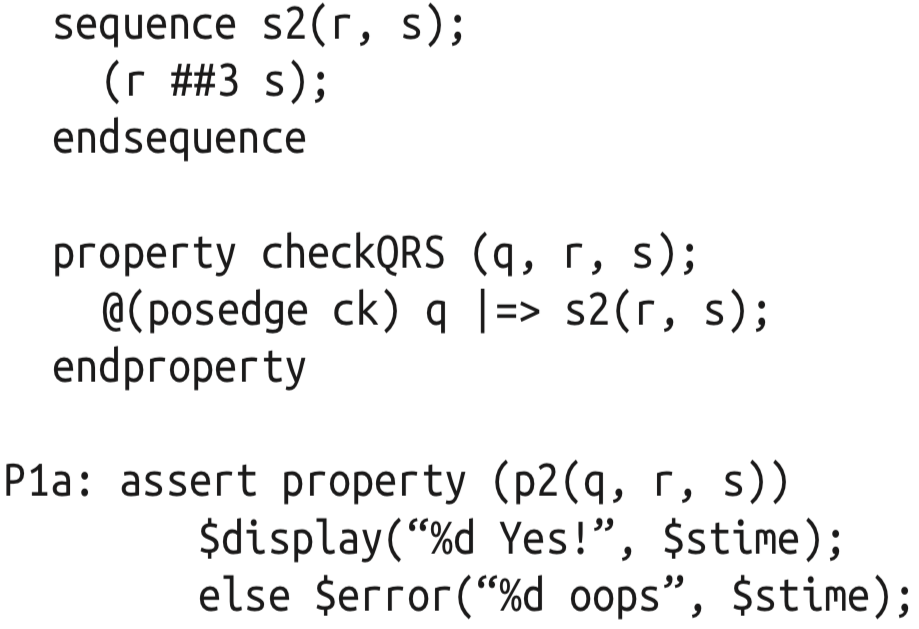

In describing CRC, Thomas refers to a very interesting and misunderstood book in Russia by Hacker's Delight :

Donald Thomas in his new book touches upon three technologies that were not in the old book at all:

These three technologies entered the industry in a good way only in the 21st century, but they entered quite firmly. At first, they were all used to create testing environments by verification engineers, but now knowledge of the functional coverage and the Temporal Assertion Language (SystemVerilog Assertions - SVA) also require designers. Thomas has a certain minimum that will help you not to be cut off in a telephone interview, but for real work you need to know much more. Moreover, not only the language of temporal statements as such, but also the practice of debugging with its help the parallel finite state machines generated by the simulator for each statement, as well as the use of formal verification programs. Assertion-based formal verification in recent years has been heavily implemented within Apple, AMD and other such companies.

I have a friend who downloaded this book on the language of temporal statements and studied it all the New Year holidays instead of a trip to Hawaii with girls. From here you can understand how important SystemVerilog Assertions (SVA) are for career and industry. True, for the sake of completeness, I should mention that he is the son of emigrants from Taiwan, and they have a more severe attitude to such things than Russians.

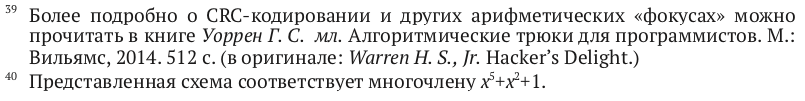

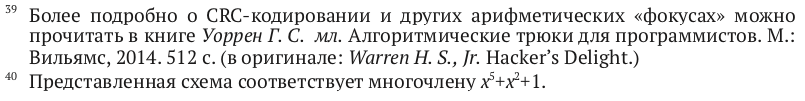

Here's how Thomas deals with generating pseudo-random transactions (transaction with rand fields and restricting them using the constraint construct):

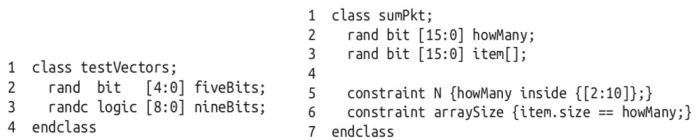

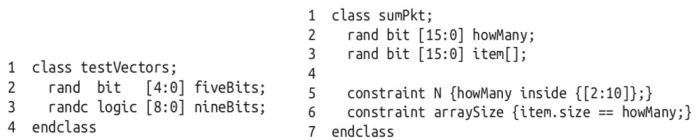

And here is how Thomas relates to functional coverage - covergroup / coverpoint / bins, taking into account combinations of coverings of several variables (cross), the use of wildcard bins, ranges of values, as well as coverage of transitions in state machines:

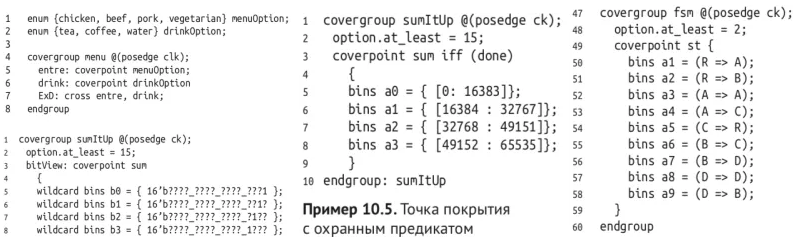

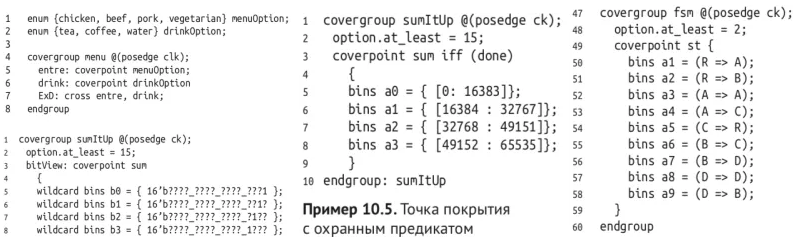

Here is an example of the simplest temporal statement “if q is true on the positive edge of the clock signal, then the sequence s2 must be executed through the loop, in which r is true first, and s after three cycles”:

What to read before and after the book “Logical Design and Verification of Systems on SystemVerilog” by Donald Thomas?

If you do not understand anything at all in my post, then you can try reading the book “Digital Circuitry and Computer Architecture” by David Harris and Sarah Harris . The book Harris & Harris can be understood by all who can read and count, provided that the reader has motivation. The book starts at the high school level - voltages, binary numbers - and ends with the design of its own processor on the veril.

Spoiler: David Harris and Sarah Harris are not husband and wife and not even brother and sister. They are just namesakes who accidentally began to work as teachers at the same university, during which they wrote a book.

Here on the left in the photo is the girl Irina from the Novosibirsk Academgorodok holding the English edition of Harris & Harris, and on the right is her Russian edition.

After the book by Donald Thomas, I recommend downloading articles by Cliff Cummings. He is the most famous veril trainer for both synthesis and verification. When reading the book of Donald Thomas, I had the idea “many times it would be nice to insert such and such a piece from Cliff Cummings” for completeness. Cliff takes $ 1,000- $ 3,000 for each student at the seminars, depending on the length of the seminar (from day to week), and electronic companies pay to improve the quality of their engineers who are not well-trained in universities. Even at Stanford, alas, not everyone learns this - I had an intern from Stanford, I know that from him. If you download all the free articles by Cliff Cummings after reading Donald Thomas, then you will save all this money.

These two articles are required - they like to ask everywhere in the interview:

Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog

Simulation and Synthesis Techniques for Asynchronous FIFO Design with Asynchronous Pointer Comparisons

It’s advisable to read these three articles, especially about removing an asynchronous reset, recoding FSM states and the FSM style “case (1'b1) // synopsys parallel_case ... state [STATE_N]: ...”, which has long been used in high-speed chips, back in Sun Microsystems, and continues to be used now:

Asynchronous & Synchronous Reset Design Techniques - Part Deux

Coding And Scripting Techniques For FSM Designs With Synthesis-Optimized, Glitch-Free Outputs

Synthesizable Finite State Machine Design Techniques Using the New SystemVerilog 3.0 Enhancements

And here is a curious article where you will see the lack of thought of the verilogue, which has remained since the 1980s. Although now, in the era of static timing analysis, this is not so relevant, inertial and transport delays are sometimes mentioned in the literature and code, and you should know how to model them:

Correct Methods For Adding Delays To Verilog Behavioral Models

This is me and Cliff Cummings:

In the chapter on the latest, the Russian reader may be puzzled by the mention of a “politically correct system”. What would that mean? This is probably an allusion to the incident that occurred in Los Angeles County in 2003. Los Angeles officials asked manufacturers, suppliers, and contractors to stop using the terms “master / slave” for computer equipment, as one of the county’s employees was reminded of the slave past.

Now technical literature authors are avoiding the terms master / slave. African-American engineers also work in modern America (for example, Sofia Mvokani from Cameroon - on the photo on the left), and the use of old terms looks archaic, as for example the terms “pan / slave” in Ukrainian technical literature would look instead of the accepted “past / leading” ( Russian “leader / slave”).

This is not the first time that the theme of the struggle of African-Americans for civil rights appears in Russian e-education. For example, Tatyana Volkova, a well-known specialist in education in electronics, wears a T-shirt with the emblem of “Black Panthers”, the California movement, which at one time considered the peaceful protest insufficient, and engaged in armed protest.

The full image of the emblem under the skin of Tatyana Alexandrovna is under the cut, but mainly I will talk about delta cycles and state machines:

Below is a screenshot of the article about master / slave and the promised Black Panther emblem, after which we move on to the book as such.

First of all, Donald Thomas, author of the book “Logical Design and Verification of Systems on SystemVerilog” (2019 in Russian from DMK-Press, 2016 in English) is the same Donald Thomas, who co-authored with Philip Murbi wrote a book 1991 The Verilog Hardware Description Language by Donald Thomas and Philip Moorby. Then, in 1991, many electronic companies still designed microchips in the old fashion, drawing them with the mouse on the screen; logical synthesis technologies have just left the laboratory for production; hardware description languages were considered intended for writing models and tests, and not source codes for creating final circuits; in addition to VHDL and Verilog closed at that time, there were many small and proprietary languages such as Abel, CUPL, PALASM; and Intel and MIPS had internal hardware description languages.

In this situation, the book of Thomas and Murbi came out, which became the same for the designers of digital circuits of the 1990s as the book for Kernigan-Richie for the programmers for C, and the books of Bjarni Straustrup for the C ++ programmers. The book withstood five editions - from 1991 to 2002, but for the era of iPhones was clearly insufficient. And in 2016, Donald Thomas decided to catch up and released a new book in which he described the key innovations in the language and methodology over 25 years. The very 25 years during which Verilog became a common base for the entire industry, schemes for everything are written on it - from the notorious iPhones and control computers in Tesla to Russian military helicopters.

Next, I will highlight my comments with blue text to separate them from the pictures from the book.

Even before the main text of the book, there is the pre-chapter “Context: Design at the Level of Register Transfers”, so that a programmer, schoolchild, or, say, a lover of exercise with prototyping boards, taking this book from the shelf, immediately understands what is being said and how they can use the book. It says:

Digital systems are being produced with billions of transistors on a chip. An amateur, of course, can draw several logic gates and connect them with wires as a specification (for implementation on a breadboard), but for commercial projects this is an ancient story ... Modern systems are specified in hardware description languages such as SystemVerilog.

In this case, here is such a simplified picture to illustrate how the text on the veril turns into tracks and transistors of the microcircuit in the factory:

The first word in the book after the preface is “simulator”. To understand the hardware description languages, you need to be clearly aware that the synthesized subset of the verilogue is not a programming language, but a language for describing electrical circuits. Like let's say HTML is not a programming language, but a language for describing web pages. While the programming language is intended to be compiled into a chain of processor instructions, the hardware description language is intended to be converted (in particular) into processor iron as such. In this case, before casting into iron, the code in the hardware description language needs to be checked, for which purpose a specialized interpreter, called a simulator, serves.

At the beginning of the book, Donald Thomas shows a simplified picture of the simulator, and at the end of the book he clarifies and supplements it:

The simulator has event queues and simulated time:

An event can give rise to a new event, both at the current moment of simulation (in the current delta cycle) and in the future tense. In the current delta cycle, all events generated by the so-called blocking assignments are processed first, and then events generated by non-blocking assignments are processed. This is necessary for the correct simulation of parallel semantics of the propagation of electrical signals in iron:

In addition to the synthesized subset of the verilog, there is also a non-synthesized subset. It is intended to describe the test environment and tests, and now it can be considered as a kind of programming language. For test environment events and monitors, additional simulator steps are introduced:

Accurate knowledge of the algorithm of the simulator is very useful to avoid a variety of bugs associated with the so-called race (race condition). When I intervene engineers, I always ask them to give an example of race condition in Verilog. Moreover, if for young RTL Design and Design Verification Engineers such knowledge is very desirable, but not in all aspects 100% necessary, that is, professions in which money is paid directly for this knowledge. I am talking about programmers who work in the Synopsys VCS, Cadence IES, and Mentor ModelSim teams.

Synopsys and Cadence are two companies located in California within a 15-minute drive of each other. They employ only a few thousand people, but they control the development of microcircuits around the world - in Intel, Apple, Samsung, Huawei, even in secret Russian institutes that make chips for military equipment.

If comrades Putin, Rogozin and Vekselberg really want to introduce import substitution in Russia, then they could finance the development of the Russian analogue Synopsys VCS (for simulating a verilogue), Synopsys Design Compiler (for logical synthesis of a verilogue) and Synopsys IC Compiler (for physically posting the results of logical synthesis ) There are probably several thousand mathematically savvy programmers in Russia.

Although licenses for these software products are fairly easy to break, using them without a support is difficult. If Huawei is disconnected from Synopsys and Cadence, they will have in some sense worse than disconnecting from Android and even ARM cores.

Yes, so here is the refined algorithm at the end of Donald Thomas’s book. If you don’t learn it by heart, it is useless to intervene in the simulation groups in Synopsys, Cadence, Siemens / Mentor, Xilinx, and there they will ask you to draw it on the board and suggest how to optimize some particular case:

After clarifying the simulation at the beginning of the book, Donald Thomas describes SystemVerilog as such. This language emerged as a Verilog superset in 2002, as a result of the merger of the Verilog-2001, Vera and Superlog languages, and with the addition of ideas from the Property Specification Language (PSL), which were transformed into SystemVerilog Assertions (SVA).

Donald Thomas believes that you have already learned the basics of digital design somewhere, and therefore weaves into the narrative fabric various well-known pieces such as Carnot cards. Carnot maps were used for manual design of circuits in the 1960s, after which this method was replaced by automatic optimization of logic using the Quine - McCluskey algorithm and automatic logic optimizer Espresso. Therefore, Carnot cards are present in all university textbooks on the design of digital logic, but they seem to hang in the air. And here Donald Thomas attaches Carnot maps to the life of a designer on a 21st century verilo:

Further, Donald Thomas writes about finite state machines, and he gives 1) a rigorous mathematical definition; 2) diagrams; 3) code; 4) after which it begins to expand them to finite state machines with a data path - hardware flows; 5) after which these flows begin to interact with him, both according to simple “politically correct” (see above) protocols, and using hardware queues.

Here is the code for a simple automaton with a data path that Thomas cites as a first example:

Next, Thomas has a chapter on static timing analysis. Nothing special, but cleaner than on many popular Indian sites, "How to get through a VLSI interview." And also more fully than in some books on veril, which tediously chew on the syntax of the language, but do not really show how to use it.

Why do we need static timing analysis? In real hardware, unlike the illusion that the processor shows the programmer, each calculation goes through a time interval when all the garbage is on the wires - not only clearly calculated zeros and ones, but also any random glitches, that is, glitch, and generally non-digital values in the forbidden zone. For example, if you have all voltages above 0.7 volts considered as a digital unit, and all voltages below 0.3 volts as a digital zero, then 0.4 volts may appear on the wire.

In the end, all the signals in the circuit go their own way and the situation settles down, but this “in the end” should be less than the cycle of the clock signal (clock). This cycle is inversely proportional to the frequency at which the circuit operates (gigahertz, megahertz).

If the settled result of calculations or logical operations does not fall into the D-trigger (minimum memory element) at the moment of the aperture (interval around the change of such a signal), the state of the circuit will become garbage - the satellite or reactor will explode, the iPhone will stop answering calls. The entire equipment designer needs to know no less ironically than logic.

Why is the analysis static? In the 1980s, it was dynamic - delays were clarified through simulation. This turned out to be unreliable for circuits with hundreds of thousands, millions and billions of transistors, and now all delays are calculated statically, based on the analysis of signal paths after synthesis.

The clock signal can also come to different parts of the chip with some delay, which adds another uncertainty to this kitchen that needs to be eliminated (fortunately, not manually, but with the help of clock synthesis tree programs and other methods):

In the chapter on flows, Thomas discusses several basic options for how parallel operating state machines with data paths can exchange information, including using buffers and queues. As in the design / circuit itself, at the level of register transfers, so in the behavioral model or test environment of the circuit. When reading Thomas, it’s nice to write and debug examples yourself for all cases of the protocols described by him. The fact is that they like to write code on such topics (a small controlling state machine, a data flow between two modules, pipelined data paths or just a code for a hardware queue) during a second-level interview in electronic companies. If you can write an example for any of the combinations described by Thomas in 20 minutes with a code of 30-50 lines, then you will make a good impression. Hard to learn - easy in battle.

The test environment for routers (Fig. 8.3) with queues for several ports is a popular example that is used to explain verification methodologies. Probably because some of these methodologies were invented by Cisco and other companies designing chips for network hardware.

In chapter 6.2.2. Thomas describes one of the options for the interaction of flows - step-by-step synchronization (Lock-step). One of the lock-step applications is high-reliability systems, for example, in automotive electronics. A special case: two processors can execute the same program with a delay of several cycles, and during this execution a special circuit can check that they have the same results.

Thomas was clearly concerned with reliability, since in addition to the lock-step, he cites the use of CRC, cyclically redundant code to detect errors in data transfer. At the same time, Thomas talks about how to calculate CRC using LFSR, a linear feedback shift register. Both that, and another need to be able to a young engineer. This is the advantage of Thomas’s book - although it doesn’t always dig deep, it touches on many topics and shows where to dig:

In describing CRC, Thomas refers to a very interesting and misunderstood book in Russia by Hacker's Delight :

Donald Thomas in his new book touches upon three technologies that were not in the old book at all:

- Automatic generation of pseudo-random transactions with constrained rules (constrained random transactions / constraint solvers).

- Accounting for coverage of interesting scenarios arising during the bombing of a design by limited-random transactions, functional coverage (functional coverage).

- The language of statements of temporal logic (concurrent assertions) and its use both in simulation and in automatic proof of design properties using formal verification programs.

These three technologies entered the industry in a good way only in the 21st century, but they entered quite firmly. At first, they were all used to create testing environments by verification engineers, but now knowledge of the functional coverage and the Temporal Assertion Language (SystemVerilog Assertions - SVA) also require designers. Thomas has a certain minimum that will help you not to be cut off in a telephone interview, but for real work you need to know much more. Moreover, not only the language of temporal statements as such, but also the practice of debugging with its help the parallel finite state machines generated by the simulator for each statement, as well as the use of formal verification programs. Assertion-based formal verification in recent years has been heavily implemented within Apple, AMD and other such companies.

I have a friend who downloaded this book on the language of temporal statements and studied it all the New Year holidays instead of a trip to Hawaii with girls. From here you can understand how important SystemVerilog Assertions (SVA) are for career and industry. True, for the sake of completeness, I should mention that he is the son of emigrants from Taiwan, and they have a more severe attitude to such things than Russians.

Here's how Thomas deals with generating pseudo-random transactions (transaction with rand fields and restricting them using the constraint construct):

And here is how Thomas relates to functional coverage - covergroup / coverpoint / bins, taking into account combinations of coverings of several variables (cross), the use of wildcard bins, ranges of values, as well as coverage of transitions in state machines:

Here is an example of the simplest temporal statement “if q is true on the positive edge of the clock signal, then the sequence s2 must be executed through the loop, in which r is true first, and s after three cycles”:

What to read before and after the book “Logical Design and Verification of Systems on SystemVerilog” by Donald Thomas?

If you do not understand anything at all in my post, then you can try reading the book “Digital Circuitry and Computer Architecture” by David Harris and Sarah Harris . The book Harris & Harris can be understood by all who can read and count, provided that the reader has motivation. The book starts at the high school level - voltages, binary numbers - and ends with the design of its own processor on the veril.

Spoiler: David Harris and Sarah Harris are not husband and wife and not even brother and sister. They are just namesakes who accidentally began to work as teachers at the same university, during which they wrote a book.

Here on the left in the photo is the girl Irina from the Novosibirsk Academgorodok holding the English edition of Harris & Harris, and on the right is her Russian edition.

After the book by Donald Thomas, I recommend downloading articles by Cliff Cummings. He is the most famous veril trainer for both synthesis and verification. When reading the book of Donald Thomas, I had the idea “many times it would be nice to insert such and such a piece from Cliff Cummings” for completeness. Cliff takes $ 1,000- $ 3,000 for each student at the seminars, depending on the length of the seminar (from day to week), and electronic companies pay to improve the quality of their engineers who are not well-trained in universities. Even at Stanford, alas, not everyone learns this - I had an intern from Stanford, I know that from him. If you download all the free articles by Cliff Cummings after reading Donald Thomas, then you will save all this money.

These two articles are required - they like to ask everywhere in the interview:

Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog

Simulation and Synthesis Techniques for Asynchronous FIFO Design with Asynchronous Pointer Comparisons

It’s advisable to read these three articles, especially about removing an asynchronous reset, recoding FSM states and the FSM style “case (1'b1) // synopsys parallel_case ... state [STATE_N]: ...”, which has long been used in high-speed chips, back in Sun Microsystems, and continues to be used now:

Asynchronous & Synchronous Reset Design Techniques - Part Deux

Coding And Scripting Techniques For FSM Designs With Synthesis-Optimized, Glitch-Free Outputs

Synthesizable Finite State Machine Design Techniques Using the New SystemVerilog 3.0 Enhancements

And here is a curious article where you will see the lack of thought of the verilogue, which has remained since the 1980s. Although now, in the era of static timing analysis, this is not so relevant, inertial and transport delays are sometimes mentioned in the literature and code, and you should know how to model them:

Correct Methods For Adding Delays To Verilog Behavioral Models

This is me and Cliff Cummings:

All Articles