シンプルエグゼキューターのジャンクション-シンプルターゲットインターフェイス(以降-STI)は、1つのFPGA構成プロジェクトまたはVLSIチップ(以下-プロジェクト)の範囲内でいくつかの機能ブロックの接続を提供する論理信号と対話プロトコルのセットです。 STIバージョン1.0インターフェース仕様は[1]で公開されました。

以下で使用される用語が仕様に導入され、STIアーティストを1つのセグメント内のイニシエーターに接続するための基本原則が決定されました。

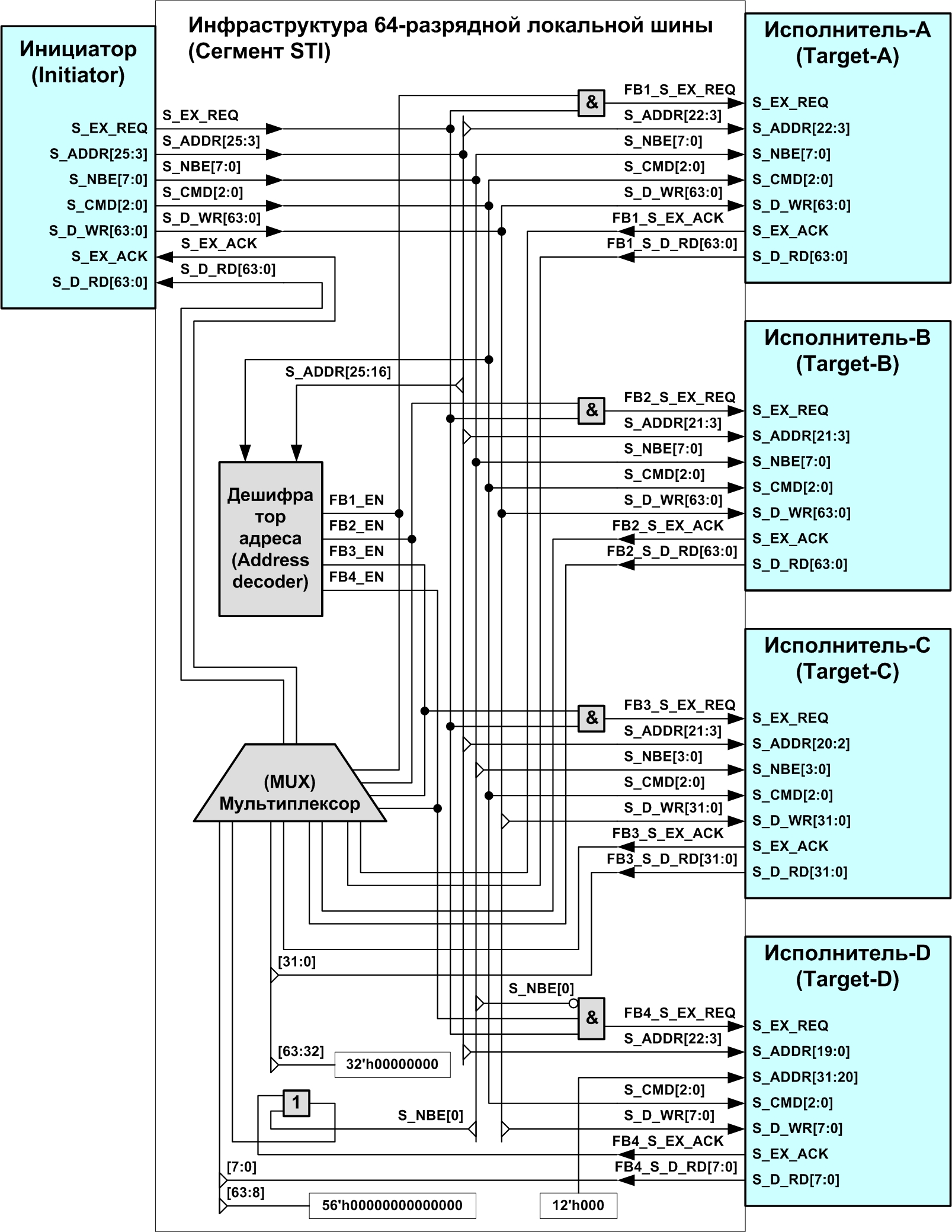

例として、イニシエーターと4人のパフォーマーを組み合わせたセグメント64-pバスSTIを考慮することが提案されています。 同時に、2つのパフォーマーのデータ容量は32ビットと8ビットです。 このようなSTIセグメントのブロック図を図6に示します。 1。

図 1. STIセグメントのブロック図

各アーティストには、書き込み時にデータを受信し、読み取り時にデータを生成するために利用可能なリソースが含まれています。 これらのリソースは、レジスタ、メモリブロック、インターフェイスブリッジで表すことができます。 そのような各リソースは、対応するアドレス空間に独自のアドレスを持っています。 メモリブロック、レジスタファイル、およびインターフェイスブリッジは、アドレス空間から連続したアドレスの範囲を占有できます。

4人のアーティストがI / Oアドレスとメモリのスペースにリソースを持っている例を考えてみましょう。 アーティストごとのアドレス範囲の分布を表1に示します。

表1

| 出演者 | アドレス空間 | ADDR [25] | ADDR [24] | ADDR [23] | ADDR [22] | ADDR [21] | ADDR [20] | ADDR [19] | ADDR [18] | ADDR [17] | ADDR [16] | 容量、バイト | DC_1 | DC_2 | DC_3 | DC_4 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Target_a | 記憶 | 1 | 0 | 0 | X | X | X | X | X | X | X | 800万 | 1 | 0 | 0 | 0 |

| Target_b | 記憶 | 0 | 0 | 0 | 0 | X | X | X | X | X | X | 4M | 0 | 1 | 0 | 0 |

| Target_c | 記憶 | 1 | 0 | 1 | 1 | X | X | X | X | X | X | 4M | 0 | 0 | 1 | 0 |

| Target_d | 記憶 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 64K | 0 | 0 | 0 | 1 |

| Target_d | I / O | 1 | 0 | 0 | X | X | X | X | X | X | X | 800万 | 0 | 0 | 0 | 1 |

| Target_c | I / O | 0 | 0 | 0 | 0 | X | X | X | X | X | X | 4M | 0 | 0 | 1 | 0 |

| Target_b | I / O | 1 | 0 | 1 | 1 | X | X | X | X | X | X | 4M | 0 | 1 | 0 | 0 |

| Target_a | I / O | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 64K | 1 | 0 | 0 | 0 |

STIセグメントのバスインフラストラクチャの構成の機能図を図に示します。 2。

現在のアドレスとコマンドコード(コマンドがアドレス空間を決定する)に応じたエグゼキュータの選択は、アドレスデコーダ-アドレスデコーダによって実行されます。 アドレスデコーダーの最初の出力のユニットは、エグゼキューターAへの呼び出し、2番目の出力のユニット-エグゼキューターBへの呼び出しなどを通知します。 デコーダー出力のバイナリコードを表1に示します。

アドレスデコーダーのアドレスは、サンプラーの信号を制御します。ターゲットA、ターゲットB、ターゲットC、ターゲットDのFB1_EN、FB2_EN、FB3_EN、FB4_ENはそれぞれ。 これらの信号はそれぞれ論理ゲートIに供給され、要求信号S_EX_REQが選択されたエグゼキューターに渡されることを許可し、スイッチングノードマルチプレクサー(MUX)にも供給されます。

マルチプレクサは、パフォーマーの出力信号(S_EX_ACKおよびS_D_RD)をイニシエーターの入力に切り替えます。 さらに、各時点で、イニシエーターは1つのエグゼキューター(デコーダーによって選択された)のみから信号を受信する必要があります。そうでない場合は、すべてのユニットを供給する必要があります。 最後の要件は、エグゼキューターに属さないアドレスへのイニシエーターのアドレスが、入力S_EX_ACKにゼロが存在するためにシステムをフリーズさせないという事実によるものです。 ほとんどのシステムに存在しないリソースからデータを読み取ると、すべてのユニットの組み合わせが返されます。

デコーダとマルチプレクサは、同じクロックサイクル内(隣接する立ち上がりエッジ間)で動作する組み合わせ論理回路です。

図 2. STIセグメントのバスインフラストラクチャの組織の機能図

executor-Dには8ビットSTIインターフェイスが装備されているため、S_NBEバイト選択入力がないことに注意してください。 その結果、パフォーマーDは、このパフォーマーが接続されているデータバスバイトのアクティビティを考慮して選択されます。 機能図から、データバスの最小バイトが使用されていることがわかります。したがって、executor-Dは、データの最下位バイトがアクティブな場合にのみ使用できます。S_NBE[0] = "0"。 このエグゼキュータの出力S_EX_ACKの論理ゲートORは、S_NBE [0] = "0"の条件でもレディ信号をマルチプレクサに渡します。 そうでない場合、マルチプレクサは「凍結」を防ぐ高レベルを受け取ります。

32ビットのArtist-Cを64ビットのSTIセグメントに接続するには、データバスの下半分[31:0]を使用します。 これらのデータラインを介して送信されるアドレスオフセット0、1、2、および3のバイトは、イネーブル信号S_NBE [3:0]に対応します。 この場合、バイトイネーブル信号はFB3_S_EX_REQエグゼキューターアクティベーション信号の形成に関与しません。これは、データバスの上半分にアクセスするサイクル(アドレスオフセット4、5、6、および7を持つバイト)が32ビットエグゼキューターCインターフェイスで空のサイクルを引き起こすためです。 4つの下位バイトすべてが非アクティブ化されます。 STI請負業者は、このようなサイクルに正しく対応する必要があります。

a

b

で

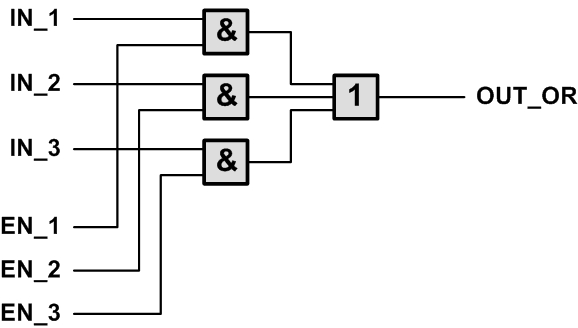

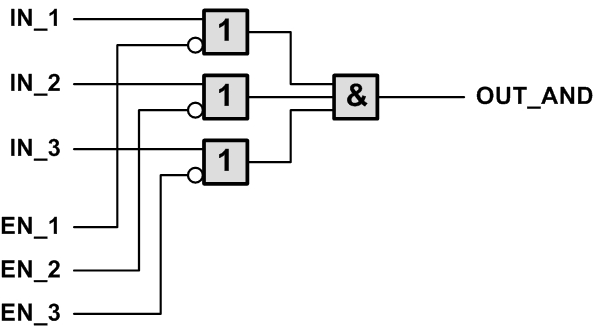

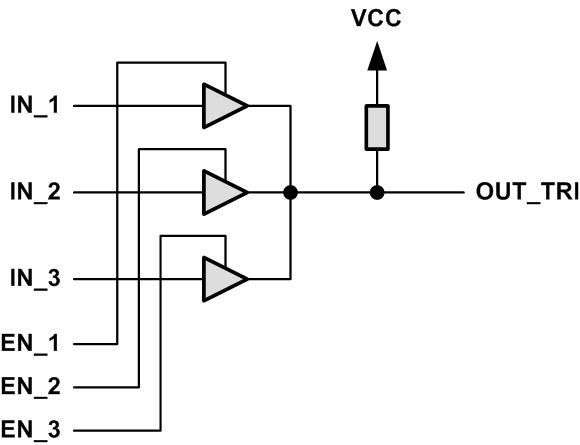

図 3.マルチプレクサーの論理構成

パフォーマーの出力信号をイニシエーターの入力に切り替えるマルチプレクサーの構成を検討してください。 正規マルチプレクサスキームは、DNF(二項代数の関数表現の選言的標準形式)の原理に基づいて構築されています。 DNFベースの回路は、2つのカスケードで構成されています。 最初のカスケードにはANDゲート(DNF式の論理積)が含まれ、2番目のカスケードにはOR結合要素(DNFの論理和)が含まれます。 3入力マルチプレクサのこのような回路を図6に示します。 3 a。 DNFに基づくマルチプレクサーの動作原理は、選択された入力からのみ最初のステージのユニットを渡すことです。 マルチプレクサの入力がどれも選択されていない場合、そのような回路は出力で低レベルを与え、S_EX_ACK信号スイッチに関する上記の要件を満たしません。

マルチプレクサを編成するための2番目のオプションは、図2に示されています。 3、b。 このスキームは、CNF(接続標準形)の原理に基づいて構築され、2つのステージで構成されます。最初のステージには、選択された入力からのみ論理ゼロを渡すORゲートが含まれ、2番目のステージには、原則に従って動作する統一AND要素が含まれます:少なくとも1つのゼロ出力ゼロ。 許可入力にすべてゼロが存在する場合、エグゼキューターが選択されていない場合、このようなマルチプレクサーは出力で1つを生成し、イニシエーター入力でのS_EX_ACK信号の要件を満たすことがわかります。

単純な請負業者-STIのバスインターフェイスのインフラストラクチャを記述するときに使用することが推奨されるのは、CNFベースのマルチプレクサです。

一部のVLSI要素ベースおよび初期のFPGAアーキテクチャでは、I / Oブロックだけでなくコアでも3つの出力状態(3安定バッファ)を持つ要素を使用できます。 図3の例のtristableバッファー 図3に示されるように、制御入力EN_xにユニットがある場合、信号IN_xを出力に送信し、そうでない場合、出力は第3の状態「Z」にある。 tristableバッファによって制御されるS_EX_ACK共有通信リンクに基づくスイッチを図3に示します。 3、c。 プルアップ抵抗は、すべてのバッファがオフになっている(エグゼキュータが選択されていない)場合に、共有通信ラインの信号の値を設定します。 プルアップ抵抗は、正論理の論理ユニットを形成します。 したがって、スイッチ信号S_EX_ACKの要件。

図2の回路のバイナリロジックの観点から注意してください。 3bおよび図 3、イネーブル入力EN_xのユニットが1つ以下の位置にある場合、その入力の組み合わせのセットで同一です。 STIアーティストスイッチで選択できるアーティストは1人だけです。または、どれも選択できません。これは、図1の回路の要件に対応しています。 3、c。 図に似たスキーム 3bは、図3cと同様のRTLモデルから多くのHDLシンセサイザーによって自動的に形成されます。

64ビットまでのビット容量を補うパフォーマーCおよびDを読み取るためのバスライン上の未使用の高位ビットデータは、デジタルアース回路(GND)への永続的な接続によってゼロに設定されます。

図2の機能図のもう1つの興味深い点は、アーティストDのバスアドレスに関連しています。 場合によっては、以前に開発されたライブラリユニットと汎用性をローカルシステムバスに接続する必要があります。 たとえば、適切なアドレス範囲を必要とする特定の容量のメモリブロック、または完全なアドレス形式用に設計されたインターフェイスブリッジは32ビットです。 現在のシステム構成のこのブロックがアドレスの全範囲を使用しない場合、S_ADDR入力の最上位のアイドルビットに定数を適用する必要があります。 この例では、executor -Dの未使用の入力S_ADDR [31:20]にはゼロがあります。

ビット容量の小さいアーティストがビット容量の大きいセグメントに接続されている場合、このアーティストのリソースのアドレスと未使用のアドレスを交互に使用する効果が現れます。 これは、バイトアドレッシングの特性によるものです。 アドレスが「000」で終わるバイトは、常に「001」ビット[15:8]で終わるアドレスのバイトが使用されるなど、64ビットデータバスのビット[7:0]で送信されます。下位ビット「111」データ行にアドレスが含まれるバイトが使用されます[63:56]。 したがって、未使用のデータバスラインに対応するアドレスは、残りのラインで使用可能なアーティストリソースのアドレスと交互になります。

前述に基づいて、executor-Cリソースは、16進表現が0〜3および8..Bの数字で終わるアドレスに配置され、「隣接」executor-Cリソースの間には、データライン経由でアクセスされる4つの未使用バイト[63 :32]。

同様に、アーティストDリソースは、0hと8hで終わるアドレスで、+ 8ずつ増加します。

アーティストCとDの接続は、アドレスバスをそれぞれ1ビットと3ビットシフトすることで実装されることに注意してください。 つまり、アーティストCの32ビットデータワードのアドレスはSTIセグメントの64ビットデータワードのアドレスになり、アーティストDのボリュームのバイトアドレスもSTIセグメントの64ビットワードのアドレスになります。

STIセグメントにデータバスの容量が小さいエグゼキューターに接続し、そのリソースがシステム(プロセッサ)のアドレス空間に連続的かつ連続的に配置されるようにするには、追加の機能ユニットを使用する必要があります-より大きなデータ容量のアクセスサイクルを2つ以上に分割するブリッジ交換請負業者のデータの容量で循環します。 このようなブリッジの構成は、この記事の範囲外です。

以下は、図に示すSTIセグメントインフラストラクチャの記述例です。 2、Verilogで:

`timescale 1ns / 1ps //////////////////////////////////////////////////////////////////////// // Engineer: FPGA-Mechanic // // Create Date: 09:38:35 03/03/2017 // Design Name: Argon SoC Proto // Module Name: STI_EXAMPLE // Project Name: Argon Otd.23 Projects // Target Devices: Any FPGA or ASIC // Tool versions: Xilinx 14.7 // Description: Test-purpose synthesizable STI module // //////////////////////////////////////////////////////////////////////// module STI_EXAMPLE( input CLK, input RST ); // Internal signals declaration: // STI-64: wire S_EX_REQ, wire [25:3] S_ADDR, wire [7:0] S_NBE, wire [2:0] S_CMD, wire [63:0] S_D_WR, wire S_EX_ACK, wire [63:0] S_D_RD, //------------------------------------------ // Initiator: STI_64b_Initiator INITR( .CLK(CLK), .RST(RST), .S_EX_REQ(S_EX_REQ), .S_ADDR(S_ADDR), .S_NBE(S_NBE), .S_CMD(S_CMD), .S_D_WR(S_D_WR), .S_EX_ACK(S_EX_ACK), .S_D_RD(S_D_RD) ); //------------------------------------------ // STI Bus Infrastructure: reg FB1_EN, FB2_EN, FB3_EN, FB4_EN; wire FB1_S_EX_REQ, FB2_S_EX_REQ, FB3_S_EX_REQ, FB4_S_EX_REQ; wire [63:0] FB1_S_D_RD, FB2_S_D_RD, FB3_S_D_RD, FB4_S_D_RD; wire FB1_S_EX_ACK, FB2_S_EX_ACK, FB3_S_EX_ACK, FB4_S_EX_ACK; always @ (S_ADDR[25:16], S_CMD) if((~S_CMD[2] & S_CMD[0]) | (S_CMD[2] & ~S_CMD[1] & S_CMD[0]) | &(S_CMD[2:1])) // Memory CMD: 0X1,101,11X case(S_ADDR[25:23]) 3'b100 : // 100XXXXXXX begin FB1_EN <= 1'b1; FB2_EN <= 1'b0; FB3_EN <= 1'b0; FB4_EN <= 1'b0; end 3'b000 : // 000XXXXXXX if(S_ADDR[22] == 1'b0) // 0000XXXXXX begin FB1_EN <= 1'b0; FB2_EN <= 1'b1; FB3_EN <= 1'b0; FB4_EN <= 1'b0; end else // No Resource begin FB1_EN <= 1'b0; FB2_EN <= 1'b0; FB3_EN <= 1'b0; FB4_EN <= 1'b0; end 3'b101 : // 101XXXXXXX if(S_ADDR[22]) // 1011XXXXXX begin FB1_EN <= 1'b0; FB2_EN <= 1'b0; FB3_EN <= 1'b1; FB4_EN <= 1'b0; end else if(S_ADDR[21:16] == 6'b001011) // 1010001011 begin FB1_EN <= 1'b0; FB2_EN <= 1'b0; FB3_EN <= 1'b0; FB4_EN <= 1'b1; end else // No Resource begin FB1_EN <= 1'b0; FB2_EN <= 1'b0; FB3_EN <= 1'b0; FB4_EN <= 1'b0; end default : // No Resource begin FB1_EN <= 1'b0; FB2_EN <= 1'b0; FB3_EN <= 1'b0; FB4_EN <= 1'b0; end endcase else // IO CMD: 0X0,100 case(S_ADDR[25:23]) 3'b100 : // 100XXXXXXX begin FB1_EN <= 1'b0; FB2_EN <= 1'b0; FB3_EN <= 1'b0; FB4_EN <= 1'b1; end 3'b000 : // 000XXXXXXX if(S_ADDR[22] == 1'b0) // 0000XXXXXX begin FB1_EN <= 1'b0; FB2_EN <= 1'b0; FB3_EN <= 1'b1; FB4_EN <= 1'b0; end else // No Resource begin FB1_EN <= 1'b0; FB2_EN <= 1'b0; FB3_EN <= 1'b0; FB4_EN <= 1'b0; end 3'b101 : // 101XXXXXXX if(S_ADDR[22]) // 1011XXXXXX begin FB1_EN <= 1'b0; FB2_EN <= 1'b1; FB3_EN <= 1'b0; FB4_EN <= 1'b0; end else if(S_ADDR[21:16] == 6'b001011) // 1010001011 begin FB1_EN <= 1'b1; FB2_EN <= 1'b0; FB3_EN <= 1'b0; FB4_EN <= 1'b0; end else // No Resource begin FB1_EN <= 1'b0; FB2_EN <= 1'b0; FB3_EN <= 1'b0; FB4_EN <= 1'b0; end default : // No Resource begin FB1_EN <= 1'b0; FB2_EN <= 1'b0; FB3_EN <= 1'b0; FB4_EN <= 1'b0; end endcase and (FB1_S_EX_REQ, FB1_EN, S_EX_REQ); and (FB2_S_EX_REQ, FB2_EN, S_EX_REQ); and (FB3_S_EX_REQ, FB3_EN, S_EX_REQ); and (FB4_S_EX_REQ, FB4_EN, S_EX_REQ, ~S_NBE[0]); // Acknowledge MUX: assign S_EX_ACK = (~FB1_EN | FB1_S_EX_ACK) & (~FB2_EN | FB2_S_EX_ACK) & (~FB3_EN | FB3_S_EX_ACK) & (~(FB4_EN) | S_NBE[0] | FB4_S_EX_ACK); // Read Data MUX: assign S_D_RD = (~{64{FB1_EN}} | FB1_S_D_RD) & (~{64{FB2_EN}} | FB2_S_D_RD) & (~{64{FB3_EN}} | FB3_S_D_RD) & (~{64{FB4_EN}} | FB4_S_D_RD); //------------------------------------------ // Target-A: STI_64b_Target_A TARGET_A( .CLK(CLK), .RST(RST), .S_EX_REQ(FB1_S_EX_REQ), .S_ADDR(S_ADDR[22:3]), .S_NBE(S_NBE), .S_CMD(S_CMD), .S_D_WR(S_D_WR), .S_EX_ACK(FB1_S_EX_ACK), .S_D_RD(FB1_S_D_RD) ); //------------------------------------------ // Target-B: STI_64b_Target_B TARGET_B( .CLK(CLK), .RST(RST), .S_EX_REQ(FB2_S_EX_REQ), .S_ADDR(S_ADDR[21:3]), .S_NBE(S_NBE), .S_CMD(S_CMD), .S_D_WR(S_D_WR), .S_EX_ACK(FB2_S_EX_ACK), .S_D_RD(FB2_S_D_RD) ); //------------------------------------------ // Target-C: STI_32b_Target_C TARGET_C( .CLK(CLK), .RST(RST), .S_EX_REQ(FB3_S_EX_REQ), .S_ADDR(S_ADDR[21:3]), .S_NBE(S_NBE[3:0]), .S_CMD(S_CMD), .S_D_WR(S_D_WR[31:0]), .S_EX_ACK(FB3_S_EX_ACK), .S_D_RD(FB3_S_D_RD[31:0]) ); assign FB3_S_D_RD[63:32] = {32{1'b0}}; //------------------------------------------ // Target-D: STI_8b_Target_D TARGET_D( .CLK(CLK), .RST(RST), .S_EX_REQ(FB4_S_EX_REQ), .S_ADDR({12'h000, S_ADDR[22:3]}), .S_CMD(S_CMD), .S_D_WR(S_D_WR[7:0]), .S_EX_ACK(FB4_S_EX_ACK), .S_D_RD(FB4_S_D_RD[7:0]) ); assign FB4_S_D_RD[63:8] = {56{1'b0}}; //------------------------------------------ //------------------------------------------ //------------------------------------------ //------------------------------------------ //------------------------------------------ endmodule

STIセグメントインフラストラクチャ自体は、「STIバスインフラストラクチャ」というコメントで制限されたコードブロックで説明されています。

STIインターフェイスを使用すると、データバス幅の広いアーティストをビット深度の低いセグメントに接続できます。 64ビットのエグゼキューターを16ビットのデータバスを持つセグメントに接続する例を考えてみましょう。 そのような接続の機能図を図に示します。 4。

図 4. 64ビットアーティストを16ビットSTIセグメントに接続します

より高いビット深度のエグゼキュータを接続する場合、アドレスバスのビットをシフトする必要はありません。 代わりに、エグゼキュータが使用しない下位アドレスビットは、現在のアドレスが交換されるデータバスの一部を選択するスイッチングノードを制御します。 同時に、エグゼキューターのリソースは、同じデータ幅のセグメントに接続するときと同じ順序でアドレス空間に配置されます。

スイッチングノードは、デマルチプレクサ(DMX)、S_D_WRセグメントのデータバスをアーティスト書き込みバスの対応する等しいビットグループに複製するバッファ、およびデータ読み取りバスのマルチプレクサ(MX)で表されます。

デマルチプレクサは、STIセグメントのS_NBEバイトのイネーブル信号を、アドレスの最下位ビットに基づいてパフォーマの対応するイネーブルバイト入力に渡します。 この例では、スイッチングを制御する最下位アドレスビットはS_ADDR [2:1]です。 現在のS_ADDR [2:1]の組み合わせで選択されていないデマルチプレクサの出力では、16ビットバス上のアドレスが現在のアドレスと一致しないバイトへのアクセスを禁止する論理ユニットが形成されます。

図の構成に対応するデマルチプレクサの機能図 図4 5。

図 5.デマルチプレクサの機能図

マルチプレクサは、制御の組み合わせ(アドレスの最下位ビット)に応じて、入力信号の1つを出力に切り替える標準的な論理組み合わせノードです。 したがって、S_ADDR [2:1] = 0hの場合、信号S_D_RD [15:0]はアーティストの出力S_D_RD [15:0]に送信され、S_ADDR [2:1] = 1hの場合、信号S_D_RD [31:16]、S_ADDR [2:2]の場合:1] = 2h-S_D_RD [47:32]、S_ADDR [2:1] = 3h-S_D_RD [63:48]。

16.32および64ビットパフォーマーの8ビットSTIセグメントへの接続は、このセグメントにはS_NBEバイト選択信号がないため、わずかに異なります。 特定のバイトがアクセスされない場合、対応する交換サイクルは8ビットセグメントで形成されません。

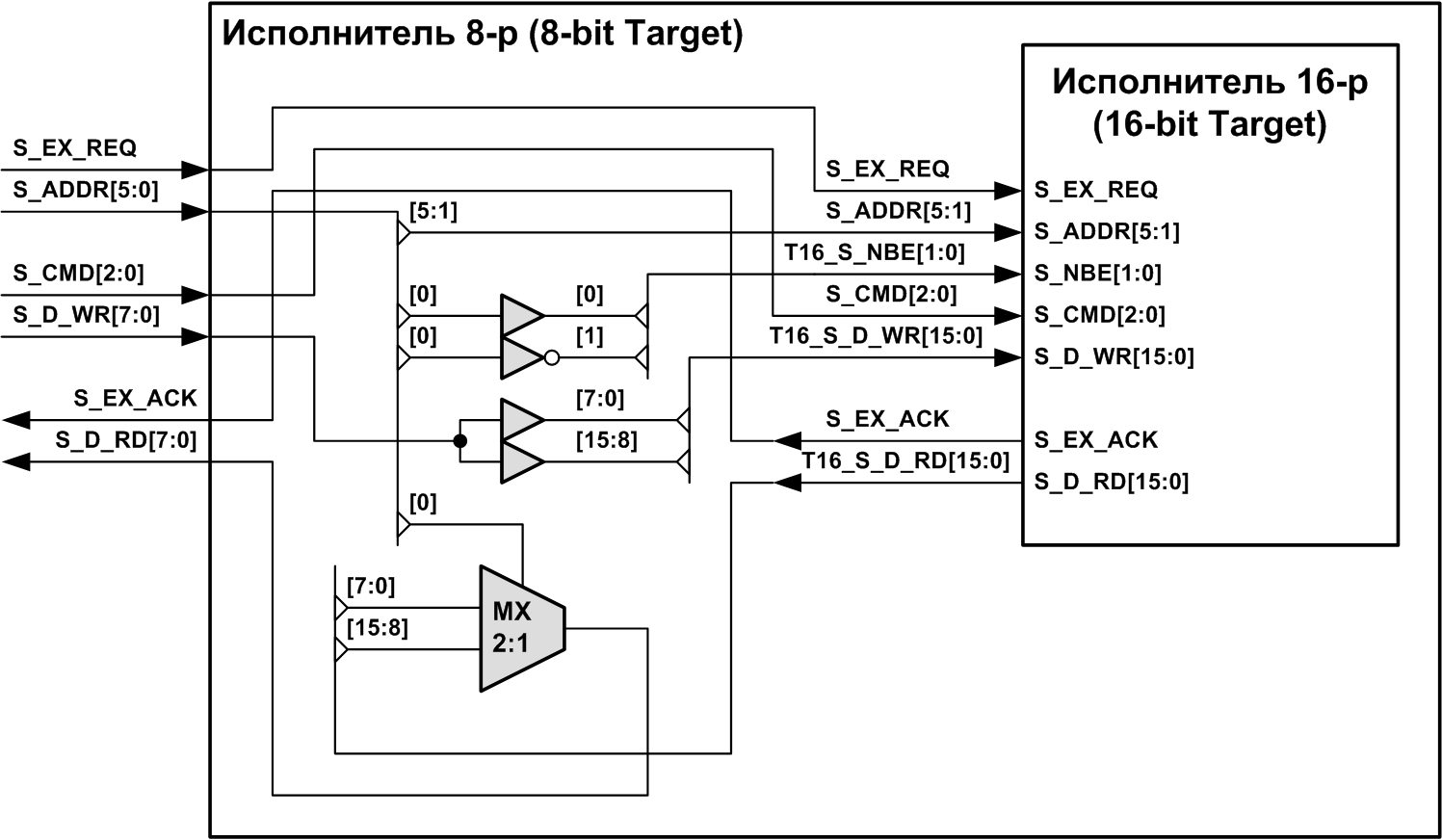

16ビットアーティストを8ビットセグメントに接続する例を図1に示します。 6。

図 6. 16ビットアーティストを8ビットSTIセグメントに接続する

16ビットエグゼキューターのS_NBEバイトイネーブル信号は、バッファーとインバーター上に構築された1:2アドレスデコーダーによって生成されます。 最小(偶数)バイトにアクセスする場合、アドレスビットS_ADDR [0]には、バッファを通過してエグゼキュータS_NBE [0]の入力に達するゼロが含まれます。 したがって、行[7:0]でのデータ交換は許可されます。 同時に、データライン[15:8]の交換を禁止するユニットが入力S_NBE [1]に形成されます。 エグゼキュータのシニア(奇数)バイトにアクセスするとき、アドレスビットS_ADDR [0]には1が含まれます。これは、ライン[15:8]に沿って交換が実行されると反対の状況になります。

マルチプレクサー-MXは、アーティストリード出力の2バイトのいずれかを8ビットデータバスS_D_RDに切り替えます。アドレスビットS_ADDR [0]がゼロの場合、アーティストの出力からのデータ[7:0]は出力S_D_RDに送信され、ユニットが1の場合、データ[15:8]。

記録用のデータは、executorのS_D_WR入力の両方のバイトに複製されますが、S_ADDR [0]とS_NBE [1:0]に応じて1バイトのみが書き込まれます。

32ビットのエグゼキューターが8ビットのSTIセグメントに接続されている場合、アドレスデコーダーは2:4形式(逆出力)であり、アドレスビットS_ADDR [1:0]をS_NBE [3:0]に変換します。 この場合のマルチプレクサは4:1フォーマットで、アドレスビットS_ADDR [1:0]によっても制御されます。 64ビットエグゼキューターが接続されている場合、3:8デコーダー(反転出力付き)は、S_ADDR [2:0]アドレスのビットをS_NBE [7:0]バイトイネーブル信号に変換します。 8:1マルチプレクサーは、アドレスの最下位3ビットの組み合わせに従ってデータ読み取りバス上のバイトを切り替えます。

結論

シンプルなSTIエグゼキューターのインターフェイスインターフェースは、VerilogおよびVHDL言語で簡単に記述できるバスインフラストラクチャを使用し、1つのセグメントでイニシエーターとSTIエグゼキューターを組み合わせます。

条件付きif / case演算子を使用した抽象化の動作レベルでのアドレスデコーダーの説明は、ブール代数法を使用した組み合わせ回路の時間のかかる合成を回避します。

STI Agent Interaction Protocolを使用すると、1つのバスセグメントでアドレスとデータバスのビット幅が異なるパフォーマーを使用できます。

参照資料

1. Borisenko N.V.コンピューティングコアとVLSIチップの周辺ブロックとの相互作用のための同期システムインターフェイス。 「コンポーネントとテクノロジー」No. 10.2016。

2. VHDLを使用したRTLハードウェア設計:効率、移植性、およびスケーラビリティのためのコーディング。 ポンP.Chu。 ジョン・ワイリー・アンド・サンズ 2006年。

3. Borisenko N.V.さまざまなプログラマブルロジックファミリに実装された統合された一連の合成FIFOバッファモデルを編成するアプローチ。 パート1.「コンポーネントとテクノロジー」第12.2012。

4. Borisenko N. V.情報のソースとレシーバーの間のデータパスに統一されたインターフェイスを持つFIFOバッファーを含めるためのスキーム。 「コンポーネントとテクノロジー」No. 2.2013。

5. Borisenko N.V.プログラマブルロジックチップの量の汎用レジスター上に構築された、統合インターフェースを備えた同期FIFOバッファーの構成。 「コンポーネントとテクノロジー」No. 8.2016。