はじめに

間違いなく、デジタル信号処理の主な分析ツールは高速フーリエ変換(FFT)です。 このアルゴリズムは、科学技術のほぼすべての分野で使用されています。 フーリエ変換の最も単純な物理的な例は、人間による音の知覚です。 私たちが音を聞くたびに、耳介は自動的に複雑な計算を実行します。これは、数年の数学の学習後に初めて実行できます。 この現象の本質は、聴覚器官がさまざまな高さの音の連続するラウドネス値のスペクトルの形で音を表し、脳が受け取った情報を知覚音に変えることです。

無線工学の問題では、FFTアルゴリズムは畳み込みおよびデジタル相関器の設計で使用され、画像処理、オーディオおよびビデオ機器(イコライザー、スペクトルアナライザー、ボコーダー)で使用されます。 さらに、FFTメソッドは、すべての種類の暗号化およびデータ圧縮アルゴリズム(jpeg、mpeg4、mp3)の根底にあり、長い数字を扱う場合にも役立ちます。 FFTはソナーシステムで水上艦艇や潜水艦を検出するために使用され、レーダーシステムでは速度、飛行方向、ターゲットまでの距離に関する情報を取得するために使用されます。

Maple、MATLAB、GNU Octave、MathCAD、Mathematicaなど、科学研究用に設計されたほぼすべてのアプリケーションパッケージで、さまざまなFFTモジュールが利用できます。 専門家は、フーリエ変換のプロセスを理解し、必要に応じて問題を解決するためにそれを適切に適用できる必要があります。

FFTアルゴリズムの最初のソフトウェア実装は、20世紀初頭のIBMコンピューターセンターで、ジョンチューキーの指揮の下、ジョンクーリーによって行われました。 1965年には、高速フーリエ変換アルゴリズムに関する記事も公開しました。 この方法は多くのFFTアルゴリズムの基礎を形成し、開発者の名前Cooley-Tukeyにちなんで命名されました。 それ以来、実行される操作の数を減らし、エネルギーコストとリソースを削減するなど、さまざまなFFTメソッドとアルゴリズムが開発および記述された非常に多くの異なる出版物とモノグラフが発行されました。 今日、FFTは1つの名前ではなく、フーリエ変換をすばやく計算するために設計された多数の異なるアルゴリズムの名前です。

理論

「デジタル信号処理」など、無線工学部のコースの理論については詳しく説明しません。 代わりに、理論的な研究と、特定のFFTアルゴリズムの実装の実用的な計算と機能の両方に精通できる、最も有用なソースの選択を提供します。

Habréに関する記事:

書籍:

- E.S. Eificher、Barry W. Dervis、デジタル信号処理。 実践的アプローチ

- Rabiner L.、Gold B.、デジタル信号処理の理論と応用

DSPLIBウェブサイト:

アルゴリズム

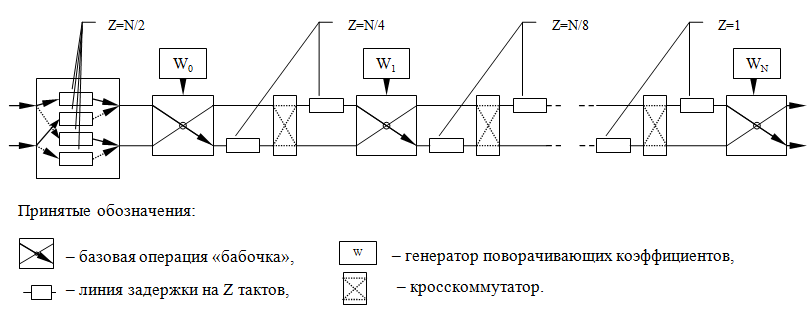

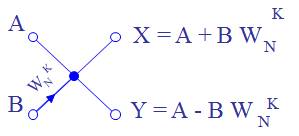

FFTノードは、ベース2のKyuli-Tukiアルゴリズムに従って作成されました。このような実装のすべての計算は、基本的なバタフライ演算の繰り返し実行に削減されます。 変換方法は、周波数デシメーション(FFTの場合)および一時デシメーション(IFFTの場合)を使用したコンベアスキームに基づいています。 アルゴリズムは二重並列化スキームを使用します。 このアプローチにより、ADCからの複雑なサンプルの連続ストリームを処理でき、そのサンプリング周波数は処理のクロック周波数の2倍です。 つまり、1クロックサイクルの「バタフライ」FFTは、2つの複雑なサンプルの計算を一度に実行します。 4倍または8倍の並列処理を使用する場合、処理周波数の4〜8倍の周波数でADCまたは他のソースからのデータストリームを処理できます。 このようなスキームは、多相フーリエ変換(多相FFT)の問題でよく使用され、特に興味深いものです。

FPGAチップにRAMBメモリを保存するには、FFTの特定の段階(NFFT> 4096ポイント)から開始し、回転係数の線形補間を使用します(テイラー級数の1次導関数への拡張)。 これにより、係数のセット全体を保存する代わりに、係数の一部のみを使用し、元のセットから近似計算によって残りを取得できます。 DSP48プリミティブのリソースを犠牲にすることで、RAMBブロックメモリのリソースが節約されます。これは、FFTノードにとって、FPGAのハードウェア実装において重要な場所です。 これについては、以下で詳しく説明します。

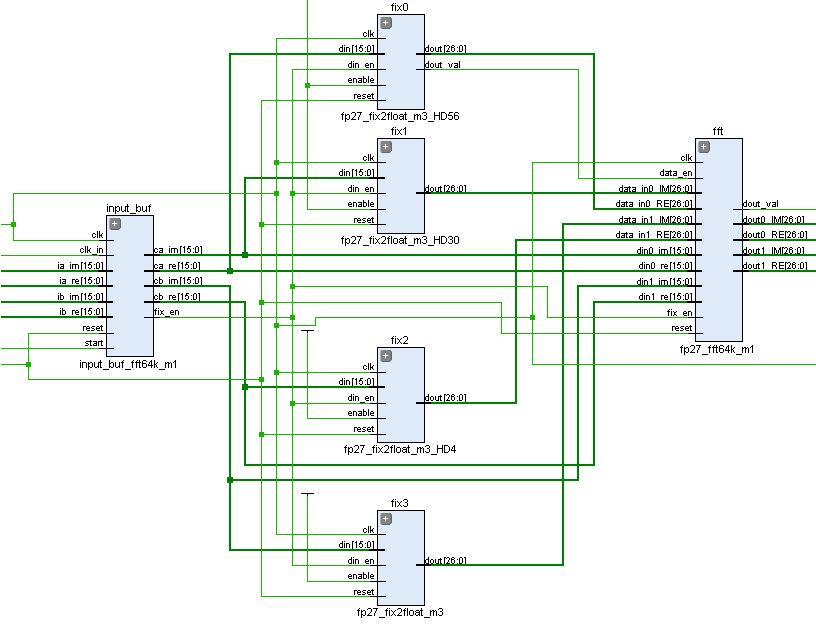

ブロック図

実現されたFFTノードの構造では、3つの機能ノードを区別できます:整数型から浮動小数点付きの特別な形式へのデータ変換、信号サンプルを記録するための入力バッファー、およびさまざまな完成した専用ノードを含むFFTコア。

合成プロジェクトの概略図: 入力バッファー+ FPコンバーター+ FFTコア

効率を高めるため、すべての計算は特別な23ビット浮動小数点形式FP23で実行されます。 これは、FP18およびFP27アルゴリズムの進歩的な実装であり、それに基づいてすべてのロジックが構築されます。 FP23形式の特徴は、ワード長-23ビット、仮数-16、指数-6、および符号-1です。FP23形式は、FPGAアーキテクチャに特に適合しており、ユニバーサルデジタル処理ユニットDSP48やメモリブロックなどの水晶ブロックの動作の内部機能を考慮していますRAMB18。 浮動小数点形式を使用すると、振幅に関係なくADCからの信号を処理するための高精度が提供され、計算のビット深度に制限のある整数ハードウェアコンピューティングを備えたシステムに典型的なデータのスケーリングにおける計算エラーが回避されます。 私の前の記事でそれについて読むことができます。

次の図は、長さN = 2 ^ nのシーケンスのパイプラインFFT計算スキームを示しています。 次のものが含まれます。

- 入力バッファ-FFTの入力での初期データ準備を提供します(実装と使用されるADC回路に応じてサンプルの再配置)、

- 回転係数のジェネレータ -正弦波と余弦波のサンプルを保存する分散メモリとブロックメモリのノード、

- バタフライ -FFTコアの基本操作(周波数と時間の間引き)

- 遅延線とクロス - スイッチ -処理された配列の要素の「蝶」の入力を目的のインデックスで提供します。

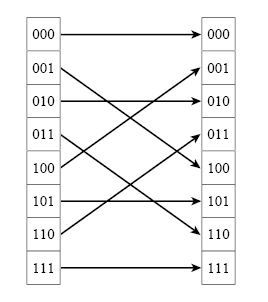

FFTコアコンベヤーは、その入力のデータが自然な順序で到着するように構築され、FFTの出力では、データストリームが放電逆順で形成されます。 OBPFの場合、反対は真です。入力データはバイナリ逆順で、出力は自然順または同種順です。 これは、入力データが厳密に自然な順序である必要があり、出力データが有効なオプションに依存するザイリンクスの既製カーネルと比較して、このFFTとOBPFのバンドルの主な利点です。

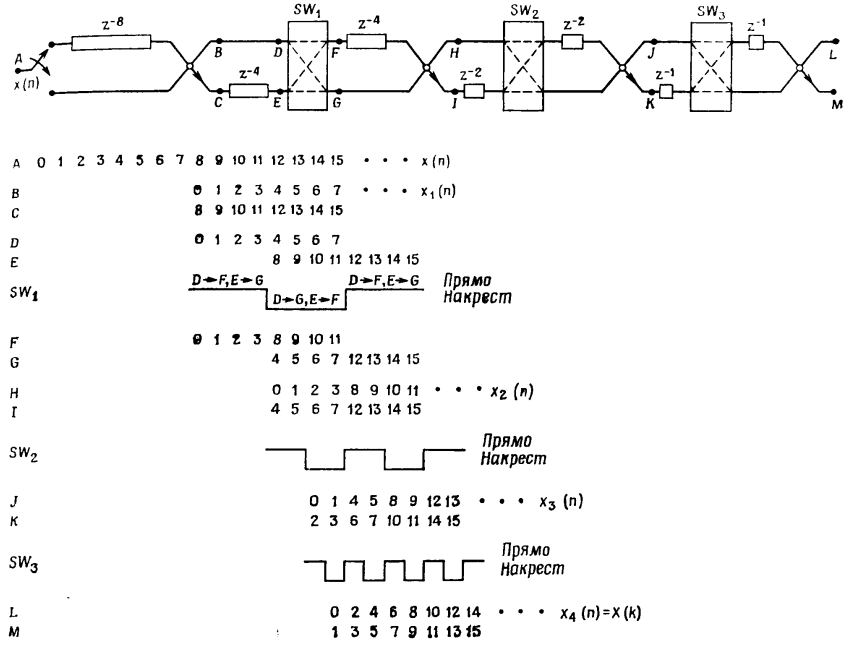

バイナリ逆順とは何であり、自然順からどのように変化するかは、次の図で明確に示されています(N = 8サンプルのシーケンスの場合)。

入力バッファ

FPGAチップの分散メモリまたは内部メモリ上に構築されます。 最新の実装では、入力でN個の複素数サンプルが到着し、出力でN / 2個のサンプルの2つのパケットが形成され、最初のパケットにはサンプル[0; N / 2 -1]、および2番目のパケット[N / 2; N-1]。 実際、入力バッファーはFFTノードのゼロ遅延ラインであり、その中でプライマリデータの並べ替えが発生します。

バッファメモリまたは遅延ラインを実装するためのVHDLのソースコードは非常に単純で、本質的にデュアルポートメモリを実行します。

PR_RAMB: process(clk) is begin if (clk'event and clk = '1') then if (enb = '1') then ram_dout <= ram(conv_integer(addrb)); end if; if (ena = '1') then if (wea = '1') then ram(conv_integer(addra)) <= ram_din; end if; end if; end if; end process;

回転係数ジェネレーター

バタフライ計算の各段階では、異なる数の係数が必要です。 たとえば、最初のステージでは1つの係数のみが必要であり、2番目のステージ2では3番目の係数が4などです。 2の累乗に比例します。 この点に関して、回転係数は、正弦波と余弦波のサンプルを保存するROMメモリ形式の分散型(SLICEM)および内部(RAMB)FPGAメモリに基づいて実装されます。 経済的なストレージのために、メモリリソースを削減する手法が使用されます。 これは、サインおよびコサイン周期の4分の1の助けを借りて、メモリアドレスのカウントの符号と方向を使用した演算のみを使用して、高調波信号の全周期を構築できるという事実にあります。 必要に応じて、係数の8分の1のみを保存でき、残りのセクションは、高調波信号のデータソースを切り替えて、カウンターの方向を変更することで取得できます。 現在の実装では、これによりパフォーマンスは向上せず、ブロックメモリのリソースがわずかに節約され、クリスタルの占有論理リソースの量が大幅に増加します。

コサインのシェーピングの例:

- 第1四半期:アドレスカウンター+ 1、cosカウント、

- 第2四半期:+1アドレスカウンター、-sinカウント、

- 第3四半期:アドレスカウンター-1、サンプル-sin、

- 第4四半期:アドレスカウンター-1、cosサンプル、

アドレスおよびデータカウンターのマルチプレクサーの単純なロジックにより、FPGAメモリを4回節約できます。

係数は16ビットの容量を持つ整数形式で保存され、メモリから抽出された後、FP23形式に変換されます。 整数形式と浮動小数点形式の回路のパフォーマンス評価を実施しました。 実践により、最初のオプションはクリスタルメモリを1.5倍節約しますが、コア全体のパフォーマンスはまったく低下せず、一部の段階でのフォーマット変換の遅延の追加により、いくつかの利点(周波数のデシメーションを伴うバタフライの係数の調整)がもたらされることも示されています。

FFTの長さが短い場合の回転係数は、SLICEMセルの分散FPGAメモリに、総容量32ビットの512個の複雑なサンプルを保存する必要がある段階まで保存されます。 FFTの長さが長い場合、RAMB18クリスタルブロックメモリが使用され、1024ペアのサンプルを保存するには、RAMB18ブロックを2つだけ使用する必要があります。これは36 * 1K = 16 * 2 * 1K = 18K * 2に相当します部分的なデータストレージの以前の方法、およびRadix-2の二重並列性を考慮して、これによりFFT長NFFT = 4096サンプルを提供できます。

NFFT> 4096サンプルのFFT長の場合、係数は1次導関数へのテイラー級数に拡張され、かなり高い精度で回転係数を計算し、FPGAメモリをさらに節約できます。 一部の理論計算を省略し、計算の実際の機能に直接進みます。

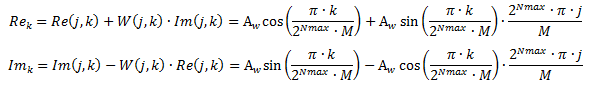

大きなNFFT値の場合、回転係数はFPGAブロックメモリに直接保存されませんが、テイラー法を使用した計算によって取得されます。 単純化された形式の回転係数の実数部と虚数部の計算式を以下に示します。

これらの式では:

A wは回転係数の振幅です(原則として、A w = 2 16 )。

2 Nmax -FPGAブロックメモリの使用を制限する回転係数の最大数(現在の実装では、2 Nmax = 2048、つまりNmax = 12)、

kは、現在のFFTステージでのすべての係数値のカウンターです。k= 0 ... 2 Nmax ∙M-1

jは、FFTの現在のステージでの係数の中間値のカウンターです。j= 0 ... M-1

M-計算の段階に依存する数は、M = 2 stageとして定義されます。ここで、stageはFFTステージの番号です。

Re k 、Im kは回転係数の計算値です。

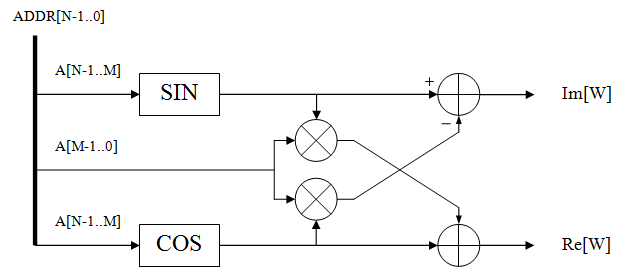

この図は、テイラー方式による係数計算の実装の簡略図を示しています(メモリから係数を抽出するためにアドレスカウンターが使用され、データを使用した数学的操作が行われます)

回転係数の計算は数学演算を使用して実行され、ブロックメモリからデータを抽出するため、係数を保存する各段階ではリソースDSP48およびRAMB18を使用します。 提示された計算式では、2つの高調波関数の乗算演算と1つのDSP48のブロックに相当するカウンター値による乗算演算を使用して、アルゴリズムが記述されました。

カーネルでTaylorスキームが使用されていない場合、次の各ステージでブロックメモリのリソースは次数2に比例して増加します。4096サンプルでは、4 RAMBプリミティブ、8192サンプル-8プリミティブなどに費やされます。 Taylorアルゴリズムを使用する場合、ブロックメモリプリミティブの数は常に2に固定されたままです。

サイン係数およびコサイン係数を作成するためのコードは、VHDL関数に基づいて構築されます(MATHパッケージを使用する必要があります)。 関数が合成され、データが整数形式の32ビットデータベクトルに正常に変換されます。

function rom_twiddle(xx : integer) return std_array_32xN is variable pi_new : real:=0.0; variable re_int : integer:=0; variable im_int : integer:=0; variable sc_int : std_array_32xN; begin for ii in 0 to 2**(xx-1)-1 loop pi_new := (real(ii) * MATH_PI)/(2.0**xx); re_int := INTEGER(32768.0*COS( pi_new)); im_int := INTEGER(32768.0*SIN(-pi_new)); sc_int(ii)(31 downto 16) := STD_LOGIC_VECTOR(CONV_SIGNED(im_int, 16)); sc_int(ii)(15 downto 00) := STD_LOGIC_VECTOR(CONV_SIGNED(re_int, 16)); end loop; return sc_int; end rom_twiddle;

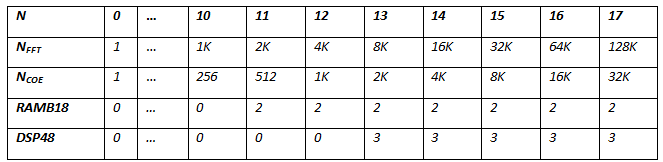

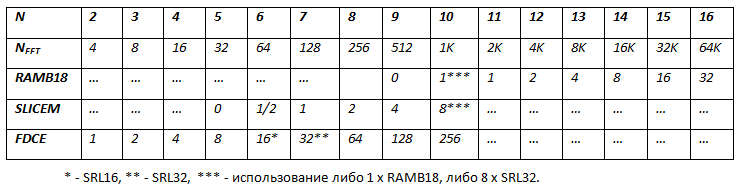

旋削比の実装のためのリソースの表:

バタフライ

FFTおよびIFFTの各バタフライは、4つの乗算器と6つの加減算器を使用し、複雑な乗算と加算/減算の機能を実現します。 提示された機能ブロックのうち、乗算器のみがDSP48セルを1つずつ使用します。 したがって、FFTバタフライごとにDSP48プリミティブは4つしかありません。 周波数と時間の間引きを伴うバタフライの計算式は、上記のソースに記載されています。 蝶は非常に簡単に実現されます。 バタフライはブロックメモリのリソースを消費しません。 ここでの落とし穴はシンプルで管理が簡単です。データを計算し、回転係数Wnをアンロードするプロセスで、計算の遅延を考慮する必要があります。 FFTとIFFTの場合、これらの遅延は異なります!

遅延線

クロススイッチと遅延線は、各FFTステージに必要な順序でデータ置換を実装します。 順列アルゴリズムの最も詳細な説明は、 Rabiner and Goldの本に記載されています。 分散またはブロックFPGAメモリを使用します。 残念ながら、ここにはメモリを節約するためのトリックはありません。 これは最も最適化できないブロックであり、そのまま実装されます。

一般的な遅延線の実装のためのリソースの表:

NFFT = 16の場合のさまざまな段階での遅延線でのバイナリ順列のプロセスを示す本から写真を削除できるようにします。

C ++では、このアルゴリズムは次のように実装されます。

for (int cnt=1; cnt<stages+1; cnt++) { int CNT_ii = pow(2.0,(stFFT-cnt)); int CNT_jj = pow(2.0,(cnt-1)); for (int jj=0; jj<CNT_jj; jj++) { for (int ii=0; ii<CNT_ii; ii++) { int jN = ii+jj*(N_FFT/pow(2.0,cnt-1)); int iN = N_FFT/(pow(2.0,cnt)); int xx = jj*N_FFT/pow(2.0,cnt); // mix data // -------- A, B, WW, IND[A], IND[B], IND[W] -------- // ButterflyFP(Ax, Bx, CFW, jN, jN+iN, ii*CNT_jj); } } }

バタフライは、番号jNおよびjN + iNのサンプルAおよびBを受信し、 WW係数は番号ii * CNT_jjになります。 プロセスを完全に理解するには、本のバイナリ順列スキームと例を見てください。

総リソース

さらなるアクションは非常に簡単です-すべてのノードは、さまざまな操作(蝶の数学、さまざまな段階の係数のアンロード)の実行の遅延を考慮して、互いに正しく接続する必要があります。 すべてが正しく行われた場合、最終結果では、作業コアが完成します。

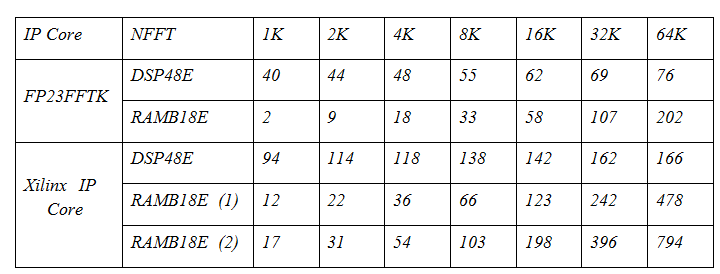

次の表は、FP23FFTK FFTコアとザイリンクスFFTコア(オプションの浮動小数点、Radix-2、パイプラインストリーミングI / O)のリソース計算を示しています。 ザイリンクスカーネルの表には、ブロックメモリのリソースの2つの列が示されています: (1) -バイナリ逆から自然( ビット反転出力データ )に順序を変換せず、 (2) -変換あり( 自然出力データ )。

表からわかるように、FP23FFTKコアは、NFFT = 64Kで2.5倍少ないDSP48プリミティブを占有します。これは、主に、切り捨てられた仮数と指数を持つデータ形式(FP23対FP32)によるものです。 さらに、カーネルは、 ビットリバースオプションのブロックメモリコンポーネントを2.5倍 、ザイリンクスカーネルのナチュラルオプションの4分の1しか消費しません。 これは、切り捨てられたデータ形式で正当化できますが、1.5倍しか得られません。 残りの改善は、回転係数のストレージ機能とテイラーアルゴリズムの使用に関連しています。

例:ザイリンクスFFTコアは入力データを自然な順序で受信する必要があります( カーネル機能! )、したがって、NFFT = 64KのザイリンクスコアのFFT + IFFTバンドルの場合、〜1600ブロックメモリセルが必要で、FP23FFTK形式の同じバンドルの場合のみ、〜 400個のRAMBセル。OBPFの場合、データを自然な形に変換する必要はなく、出力ではデータはすでに自然な順序になっています。 この機能により、パフォーマンスを損なうことなく、小さなFPGAクリスタルの高速畳み込みにコンパクトな圧縮フィルター(FFT + OBPFバンドル)を構築できます!

以下は、NFFT = 65536ポイントのFFTコア合成ログです。

カーネルパフォーマンス

ハードウェアの制限があるため、Virtex-6(XC6VSX315T)とKintex-7(XC7K325T)の2つのクリスタルでのみFFTコアをテストしました。

ザイリンクスFPGA Virtex-6 SX315TのNFFT = 64KサンプルでのFFT + IFFTの束では、F dsp = 333 MHzの周波数で安定したフィルター動作を実現できました。 ザイリンクスFFTコアもこの周波数で動作しましたが、使用されるリソースの量は大幅に増加しました。

Kintex-7 FPGAの場合、NFFT = 8Kで独立したフィルターを備えた安定したマルチチャネル回路が実装され、処理周波数もF dsp = 333 MHzに等しくなります 。

残念ながら、333 MHzを超える周波数および他のファミリのFPGAでは、ノードの動作は確認されませんでした。

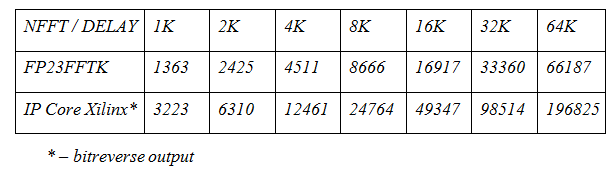

次の表は、さまざまなFFT長について、カーネルの入力から出力までの遅延時間(NFFTサンプルの長さでバーストを完全に計算)を示しています。 表からわかるように、ザイリンクスの結果は残念です。 FP23FFTKカーネルを使用すると、完全なFFT計算の時間を約2.5倍短縮できました 。 また、IPザイリンクスで自然順序での変換も有効にすると、値はさらに大きくなります。

FPGA実装例

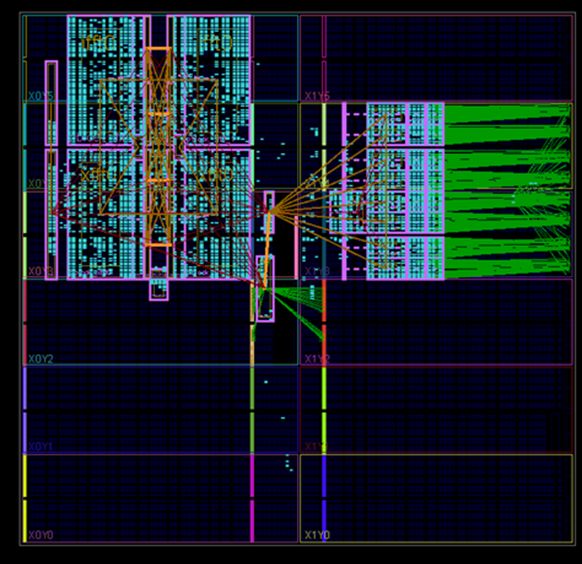

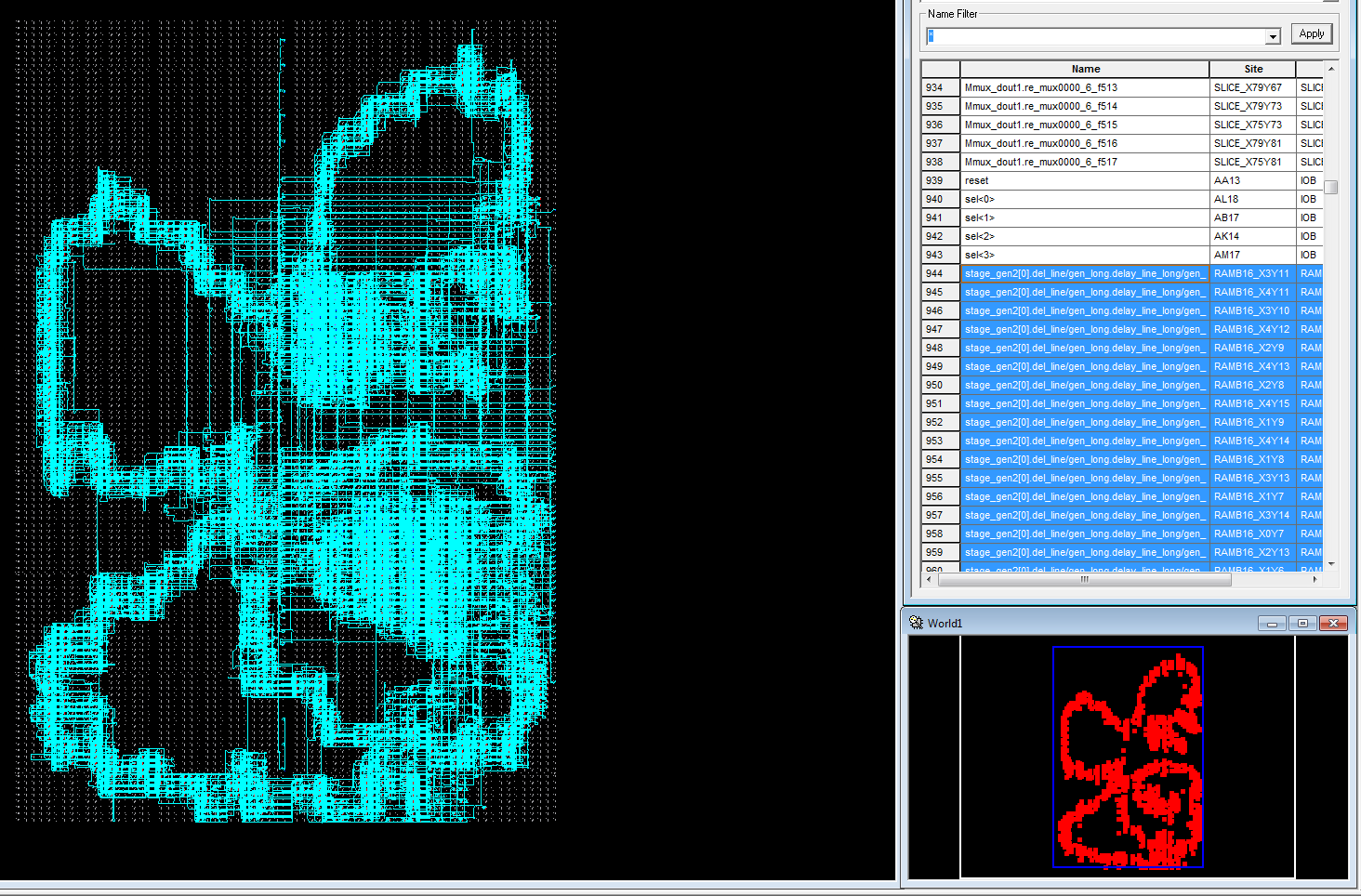

1. 4チャネルのダイレクトFFT。 FPGA:Virtex-6 SX315T(〜1300 RAMB、〜1400 DSP48)。 4x FP23FFTK、NFFT = 16K

その他の例...

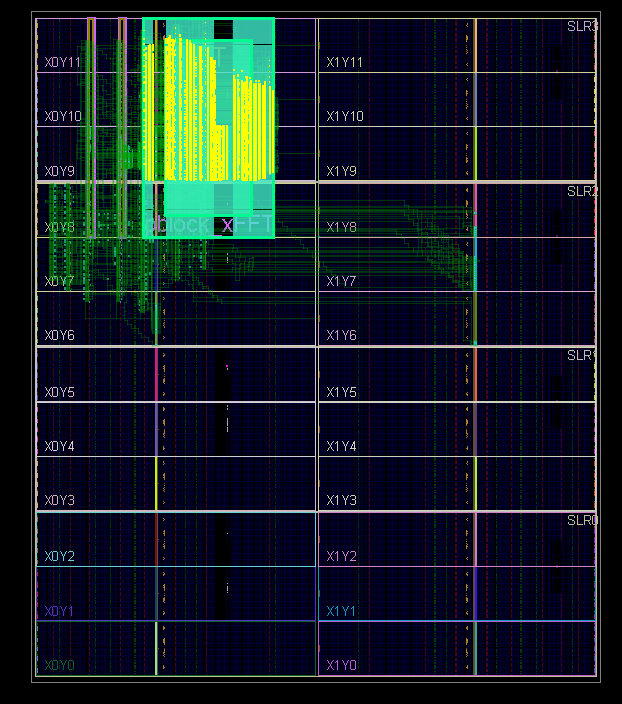

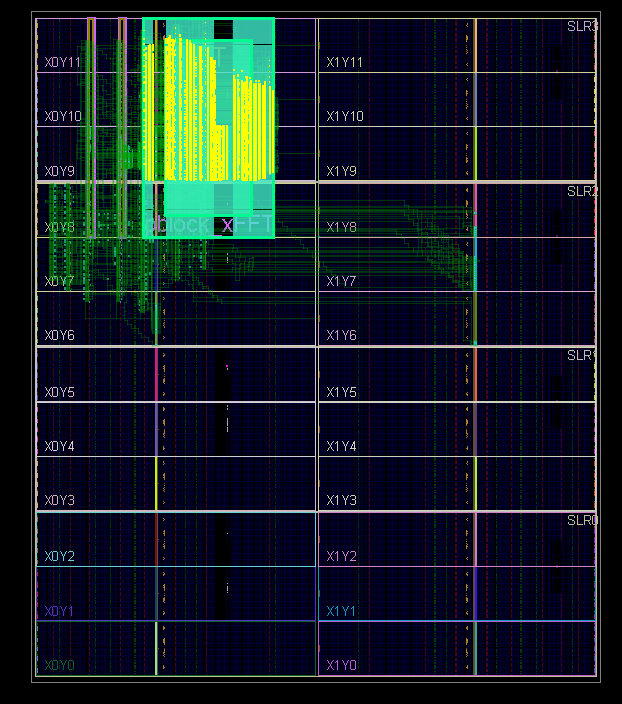

2. 8つの圧縮チャネル(FFT + OBPF)。 FPGA:Virtex-6 SX315T(〜1300 RAMB、〜1400 DSP48)。 16x FP23FFTK、NFFT = 16K

3. FFT + OBPF 64K(大きな圧縮フィルター)。 FPGA:XC7VX1140TFLG-2(〜3700 RAMB、〜3600 DSP48)。

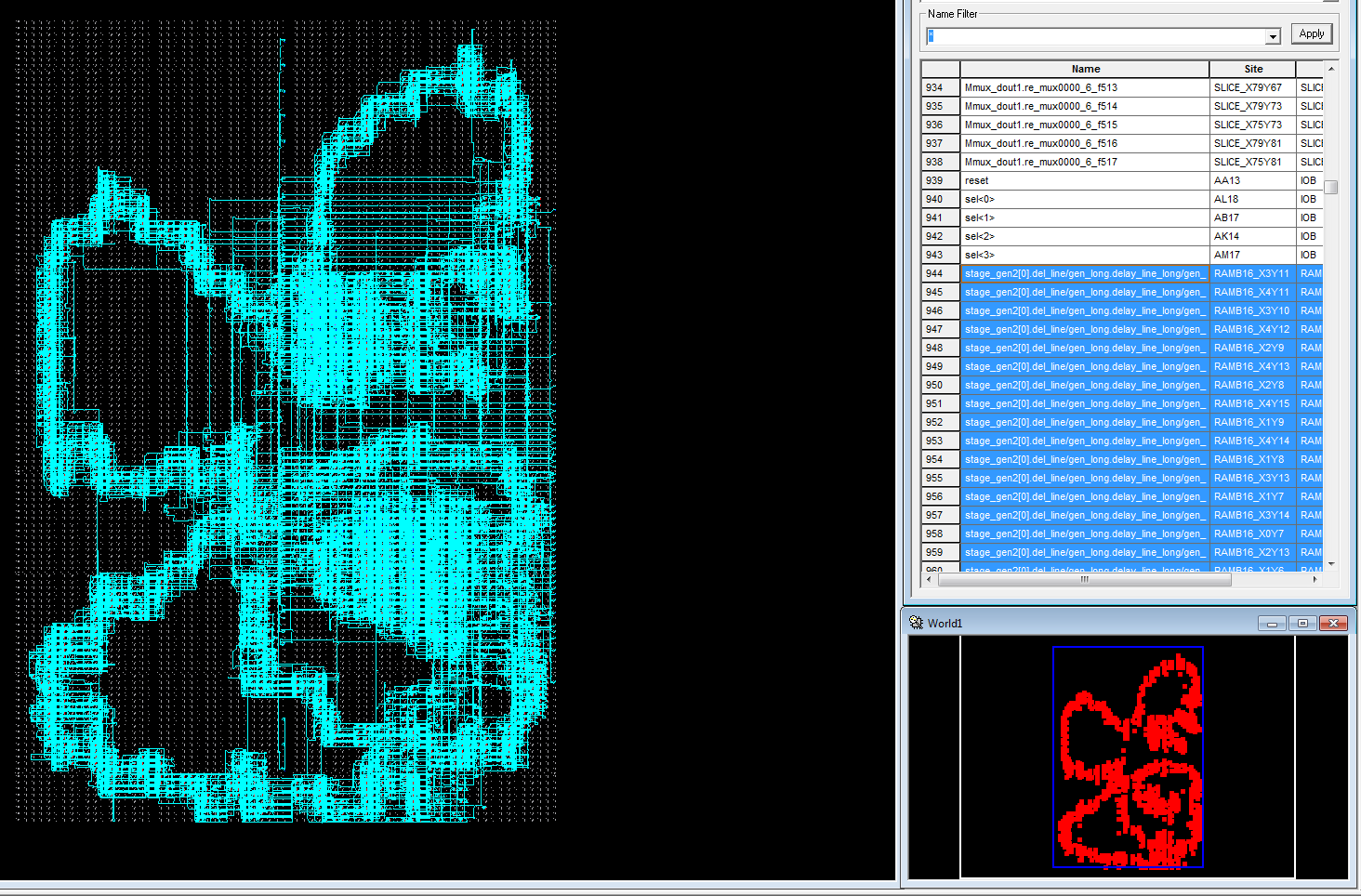

4. ランダムFFT配線の図 (蝶に似ています):

3. FFT + OBPF 64K(大きな圧縮フィルター)。 FPGA:XC7VX1140TFLG-2(〜3700 RAMB、〜3600 DSP48)。

4. ランダムFFT配線の図 (蝶に似ています):

カーネルチェック

FPGAでの浮動小数点形式のFFTカーネルの開発とデバッグには、さまざまな開発ツールが使用されました。

A) FFTコアのRTLモデルのテストは、Xilinx Vivado CADおよびAldec Active-HDL CADを使用して実行されました。 Vivadoの高いパフォーマンスにもかかわらず、いくつかの欠点があり、その1つはコード編集ツールの低さです。 製品は絶えず進化しているようですが、いくつかの便利なガジェットがまだプログラムにないため、ソースコードはメモ帳++で記述され、VHDL / Verilogファイルで動作するように構成されています。 Vivadoとは異なり、Active-HDLモデルははるかに高速であり、アプリケーションの終了後にタイムチャートを保存することもできます。 Modelsimは、ライセンスがないため作業中に使用されませんでした:)

B) FFTカーネルのプログラムモデルのテストは、Microsoft Visual Studioで実行され、RTLモデルを繰り返すC ++で記述されたアプリケーションが遅延とクロック周波数を使用せず、設計のさまざまな段階(回転係数のジェネレーター)で迅速かつ効率的にデバッグできるようになりました、順列切り替えノード、数学演算、Taylorアルゴリズムの実装、完全な完全なFFTコア)。

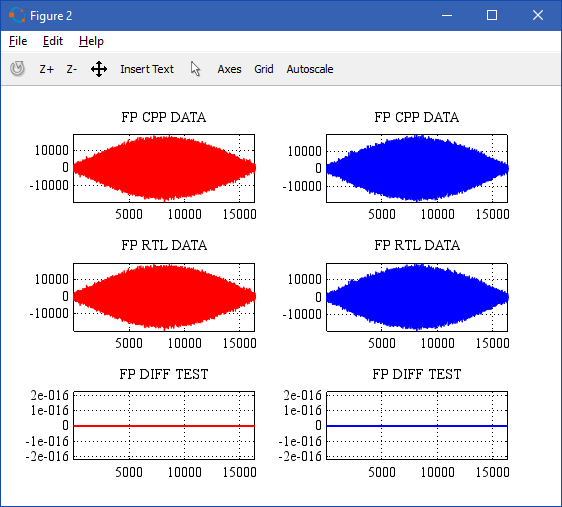

C) Matlab / GNU Octaveで完全なテストが実施されました。 デバッグ用にさまざまなテスト信号を含むスクリプトが作成されましたが、偏差、振幅、オフセット、およびその他のパラメーターのさまざまな設定を持つ最も単純なLFM信号は、視覚モデリングに最適であることがわかりました。 高調波信号とは対照的に、スペクトル全体でFFTの動作を確認できます。 正弦波信号でテストすると、トラップに何度か落ちてしまい、チャープ信号を使用できなくなりました。 特定の周波数の正弦波信号をFFTの入力に適用すると、出力では目的の周波数で良好な高調波が得られますが、入力正弦波の周期を変更するとすぐにエラーが発生しました。 RTLコードのデバッグ中にこれらのエラーの性質を追跡することは容易ではありませんでしたが、答えを見つけました:計算のいくつかの段階での蝶と回転係数のノードの不正確な遅延。 LFM信号を使用することでこの問題が解消され、FFT計算の各段階で正しい遅延を選択できるようになりました。 また、mスクリプトを使用して、C ++モデルとRTLモデルの動作を比較し、FP23浮動小数点形式とfloat / double形式の計算の違いも確認しました。

テストアルゴリズム

このプロセスはやや日常的に思えるかもしれませんが、すべてのFFTノードの正しい動作を実現することができたのは、この順序でした。 おそらくプロジェクトでカーネルを使用する場合に役立ちます。

1. Matlab / Octaveスクリプトを実行して、基準信号を作成します。 次の変数を制御できます。

- NFFT-FFT / OBPFの長さ、変換ポイントの数、

- Asig-入力信号の振幅(0-32767)、

- Fsig-入力信号周波数、

- F0-チャープの初期周波数(信号位相)、

- Fm-LFM信号のエンベロープ周波数(非矩形エンベロープの場合)、

その結果、C ++およびRTLモデルで使用される2つのファイルが(実コンポーネントと虚コンポーネント用に)作成されます。

2. Microsoft Visual Studioでプロジェクトを作成し、適切なディレクトリでC ++のソースコードを取得します。

3.プロジェクトをビルドして実行します。 hファイルで次の変数を設定できます。

- NFFT-FFT / IFFTの長さ(パラグラフ1の選択に依存)、

- SCALEは、FP23形式からINT16形式にデータを変換した後の数値の範囲を決定するスケーリング係数です。 値の範囲は0〜0x3Fです。

- _TAY(0/1)-テイラーアルゴリズムによる係数計算の使用(NFFT> 4096の場合)。

4. VivadoまたはActive-HDL環境でHDLプロジェクトを作成し、VHDLでソースファイルを取得します。

5.テストベンチディレクトリのファイルを使用してシミュレーションを実行します。 このファイルで次のオプションを設定できます。

- NFFT-FFT / IFFTの長さ(パラグラフ1の選択に依存)、

- SCALEは、FP23形式からINT16形式にデータを変換した後の数値の範囲を決定するスケーリング係数です。 値の範囲は0〜0x3Fです。

- USE_SCALE(TRUE / FALSE)-テイラーアルゴリズムによる係数の計算または係数の計算を直接使用します(NFFT> 4096の場合)。 句3からの_TAY変数の戻り値。

- USE_FLY_FFT(TRUE / FALSE)-FFTコアでの蝶の使用。 デバッグのために、このオプションはそのままで、実際的な利点はありません。

- USE_FLY_IFFT(TRUE / FALSE)-OBPFのコアでの蝶の使用。

6. mスクリプト(項目1から)を再実行して、FFTおよびOBPFのC ++ / RTLカーネルの動作を確認します。

これらの魔法のアクションを実行すると、入力信号のグラフと、FFTおよびOBPFノードを通過する信号のグラフが画面に反映されます。 1つのFFTノードのみをテストするには、mathディレクトリから別のmスクリプトを取得して、ソースファイルにいくつかの変更を加える必要があります。

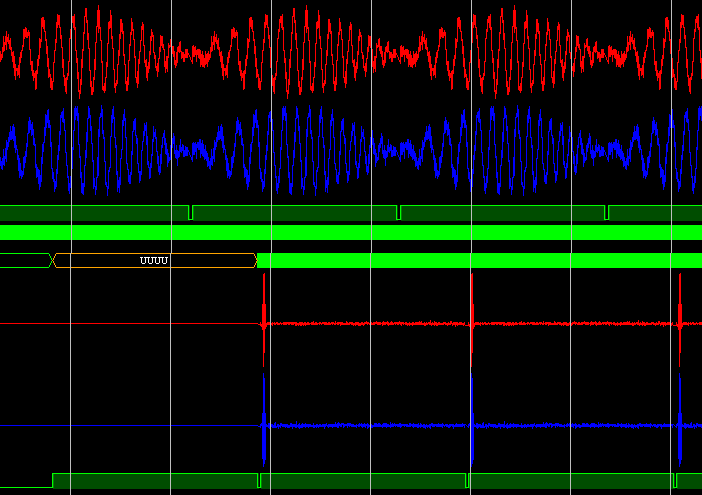

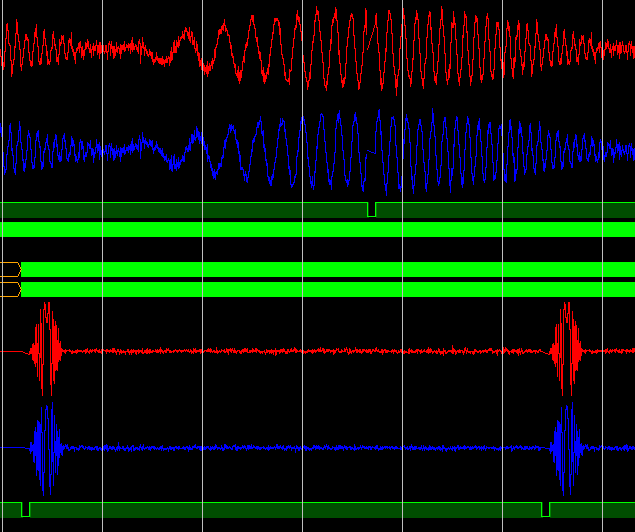

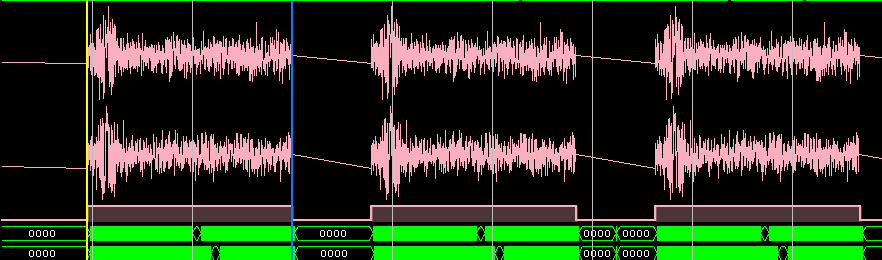

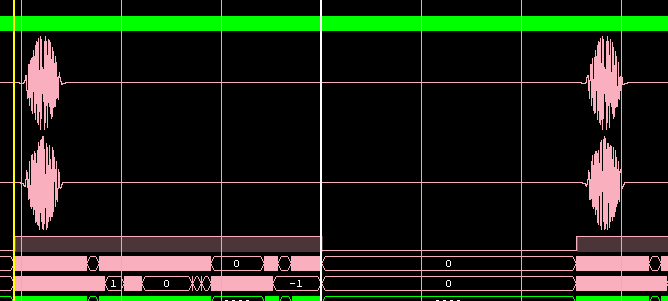

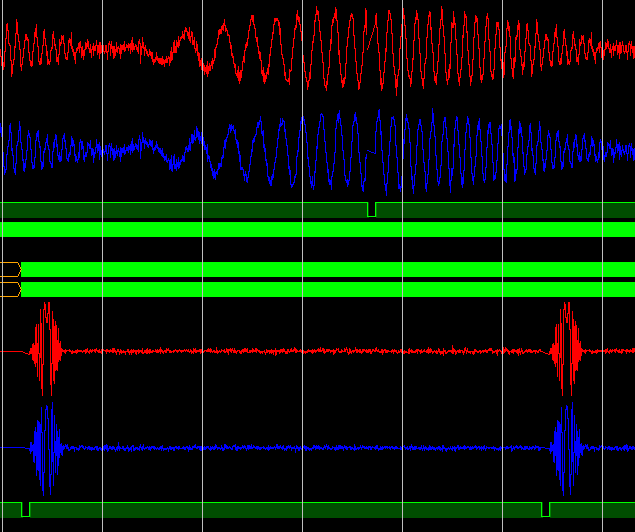

C ++およびRTLモデルの視覚的検証(FFT + OBPFバンドル):

FFTコアのテスト結果

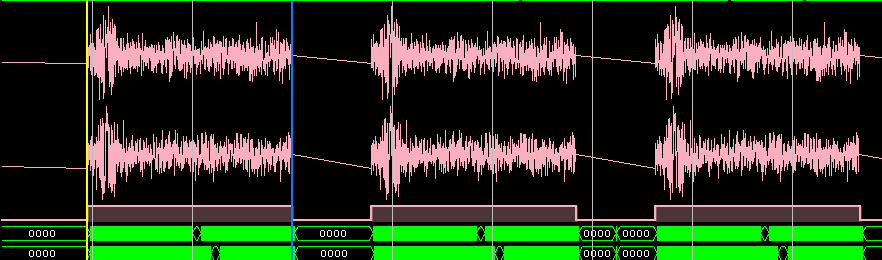

ホワイトノイズを含むノイズ信号のテスト(Vivadoのモデル)

FFT入力:

別のテスト例(入力およびFFT結果):

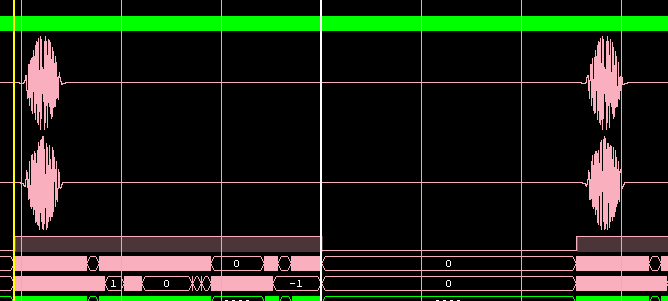

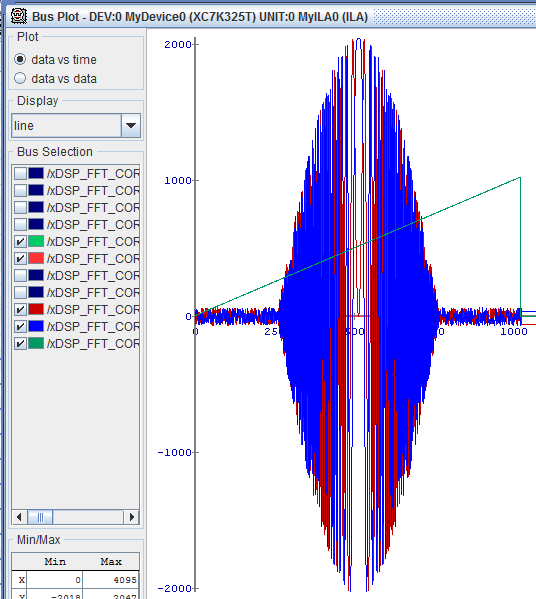

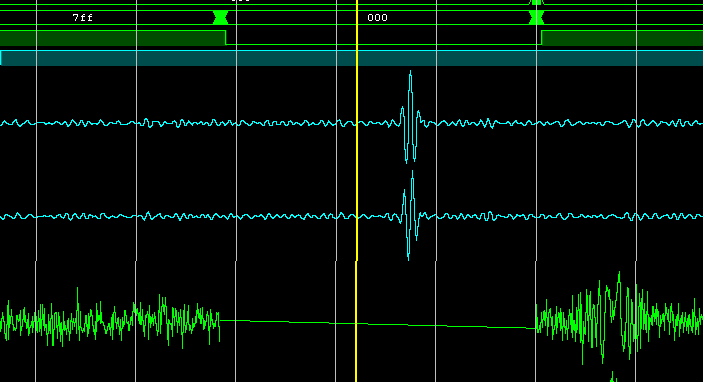

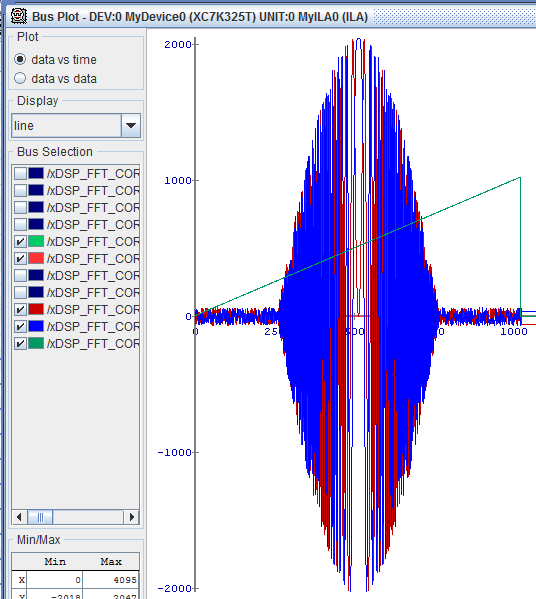

Kintex-7 FPGAでのハードウェアでのテスト(ChipScopeでのデバッグ):

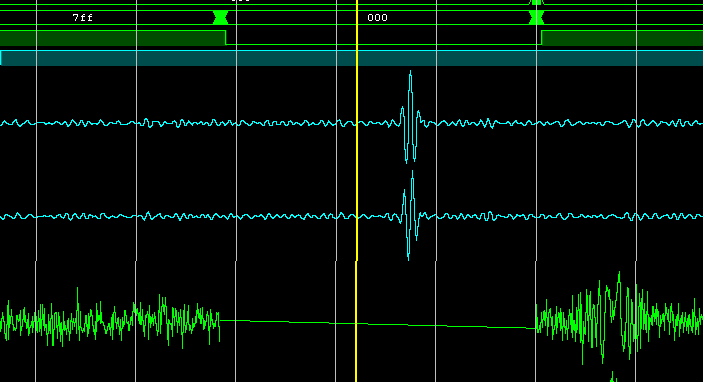

フィルター操作-圧縮LFMインパルス(ソースコードに圧縮フィルターの実装はありません):

FFT入力:

別のテスト例(入力およびFFT結果):

Kintex-7 FPGAでのハードウェアでのテスト(ChipScopeでのデバッグ):

フィルター操作-圧縮LFMインパルス(ソースコードに圧縮フィルターの実装はありません):

FFT FP23FFTKコア機能

- ザイリンクスのゲートおよびプリミティブのレベルでの実装。

- 記述言語-VHDL。

- NFFT変換長= 8-256Kポイント。

- NFFT変換長の柔軟な調整。

- 特殊な浮動小数点数形式FP23(16ビット仮数)。

- 固定小数点形式に変換するときの出力のスケーリング。

- テイラー級数の1次導関数への展開による回転係数のコンパクトなストレージ。

- 分散メモリおよびブロックメモリでの係数の期間の1/4のストレージ。

- FFTのバタフライ-時間のデシメーション、IFFTのバタフライ。

- FFT:入力のデータ-直接順、出力のバイナリ逆順。

- OBPF:入力でのデータをバイナリ逆順で、出力で-直接。

- 二重並列処理を備えたコンベア処理回路。 基数2

- データの最小バーストは、連続モードまたはブロックモードのNFFTサンプルに等しくなります。

- 高速コンピューティングと少量のリソース。

- 既存のコアと比較して、完全な計算の大幅に短い遅延時間。

- 最新のFPGA(Virtex-6、7シリーズ、Ultrascale)での実装

- FFT + OBPFバンドルの高価なビットリバース操作は不要

- オープンソース。

ソースコード

VHDL上のFFT FP23FFTK FHDカーネルのすべてのソース(FP23形式の基本操作を含む)、C ++でのチェック用モデル、およびMatlab / Octaveのmスクリプトは、githubのプロファイルで利用できます。

今後の計画

もちろん、プロジェクトの開発はそこで終わりではありません。 私の計画では、すでに作成されたモデルに基づいて、次のような多くの興味深い新しいことを実行できます。

- 大きなFFT長の計算の精度を高めるには、FPGA機能を考慮してFP32形式(IEEE-754と同様)を実装します。仮数長は25ビットです。

- FP32形式のFFTおよびIFFTノード、NFFT長= 256K以上、例として圧縮フィルターを使用。

- Radix-4、Radix-8スキームによる多相FFT。これにより、パイプラインモードでADCからのデータストリームを非常に高い周波数で処理できます。

- NFFT = 1M-256Mポイントの外部メモリを使用した超長FFTスキーム(2D-FFTに基づく)。

-

SystemVerilogのソースを書き換えます。必要ですか?

おわりに

実装プロセスでは、非常に少ないリソースで高いパフォーマンスを提供する高性能コアを取得できました。ザイリンクスコアと比較して、FP23FFTK はリソース、全体的なレイテンシ、およびおそらく最大データ処理頻度の点で勝ちます。さらに、FP23FFTKプロジェクトのFFTコアとOBPFコアのバンドルは自然な順序での変換を必要とせず、最大変換長はFPGAリソースによってのみ制限されます!

私は、ハードウェアとこのプロジェクトの完全な実装で安定した結果を得るために数年を費やしました。(残念ながら、純粋な時間はカウントしませんでした)。このプロジェクトは、フィット、スタート、夕方、週末に作成され、定期的に放棄され、さまざまなノードへのアプローチが部分的または完全に変更されました。多くの場合、一部のアイデアは捨てられたり、強く投げ出されたり、時には純粋に偶然に過ぎたりします。この仕事の過程で私がした主な結論の1つは、独立した手段による設計の各段階の徹底的なチェックの必要性です。たとえば、C ++モデルがないと、実装をまったく進めることができない場合があったため、ノードの一般的なテストの前に、多くの小さなテストを作成し、各部分を個別にデバッグする必要がありました。

このカーネルがDSPのタスクで誰かを助け、プロジェクトでアプリケーションを見つけることを願っています。私は微妙にいくつかの点を省略し、それらに焦点を合わせませんでした(積分変換誤差の計算、FP23形式での量子化ノイズなど)。私は常にdsmv2014に感謝します。dsmv2014は、私のアイデアを常に歓迎し、FPGAでのデジタル信号処理のさまざまなタスクの実装に対する冒険的な取り組みを積極的に受け入れました。

ご清聴ありがとうございました!