まえがき

Tetrisや無線送信機など、興味深いFPGA開発に関する多くの興味深い記事を読んだ後、魂のために何かをするというアイデアも得ました。 このために、 OV7670カメラと、Altera Cyclone IIチップを搭載したTerasic DE-1デバッグボードを購入しました。 タスクは次のとおりでした。カメラからの画像をVGAモニターに表示します。 FPGAの使用を正当化するために、カメラの最大速度でそれを行います。 エレクトロニクスの分野の知識は、この作業をより簡単に理解するのに役立つことに注意してください:VGAおよびI2Cインターフェイスの知識、SDRAMメモリの理解など。

はじめに

この記事は研究ではなく、主なアイデアと私の意見で最も興味深く、複雑な場所を示した進捗報告書です。 複雑さの点では、このプロジェクトは「点滅LED」に従いますが、拡張の可能性が非常に大きくなります。 このプロジェクトは元々手書きのものとして計画されていたため、このプロジェクトは既製のIPカーネルと標準インターフェースを意図的に使用していません。 また、リソースと速度の面で少し勝つのに役立ちます。 この記事が読者の興味を引くことを願っています。また、「自家製カメラ」を通してスクリーン上で自分自身を見たいという願望がFPGAの研究を促進することを願っています。

免責事項

プロジェクトの一部の場所では、コードのアーキテクチャと構文が最適でない場合があります。 これは、私が暇なときにプロジェクトの実施に携わったという事実によるものであり、時には数か月間アプローチの間に中断がありました。古い考えは忘れられましたが、新しい考えが現れました。 そのため、たとえば、中央のオートマトンは大幅に簡素化されました。「グローバル」という名前だけが元のモンスターから残っていました。 投稿する前に、コードをリファクタリングしましたが、欠陥が見つかった場合は、コメントでそれらを示してください。

問題と解決策

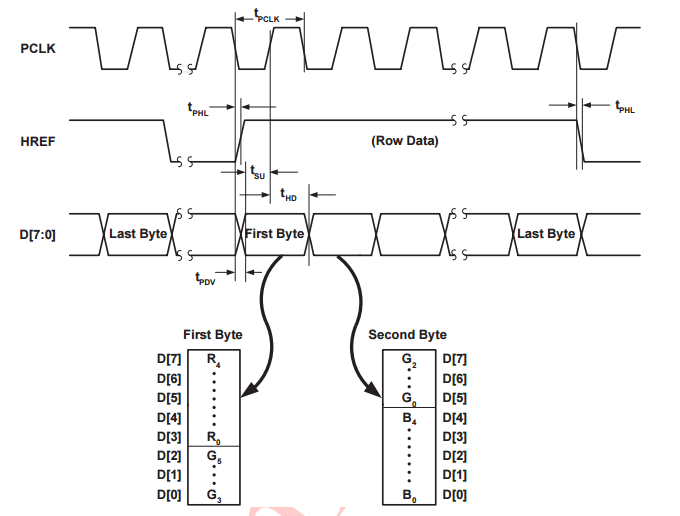

待っていることを理解するために、ハードウェアを見て、直面している問題を評価してください。 カメラOV7670。 このカメラは、RGB565形式で毎秒30フレームの頻度で640x480ピクセルの解像度の画像を生成できます。 カメラが機能するには、24 MHzクロックを適用する必要があります。 カメラは、同期ゲートVSYNCおよびHSYNCと同様に、8ビットバスを介してユーザーにデータを送信します。 カメラのタイミング図を図1に示します。

図1

色情報は、バイト単位で2メジャーで送信されます。 データをバイトにパックする様子を図2に示します。

図2

VGAモニター。 VGAはアナログ信号であるため、入力にデジタルデータを供給することはできません。 しかし、DE-1には4ビットDACがあり、それらを使用してデジタル信号をアナログ信号に変換します。 解像度が640x480のVGAのリフレッシュレートは60フレーム/秒です。 25.175 MHzの周波数でDACにデータを公開し、同期ゲートVSYNCおよびHSYNCを形成する必要があります。 VGAのタイミングについては、 こちらをご覧ください 。

カメラからのデータの頻度とモニターへのデータ出力の頻度が異なることが明らかになり、直接接続の可能性が排除されます。 この状況から抜け出す方法は、 フレームバッファの使用です。 メモリ内の2つの等しい領域を選択します。カメラの現在のフレームが1つに記録され、記録されたフレームの終了後、前のフレームが2つ目から抽出され、バッファが交換されます。 1フレームの保存には640 * 480 * 16 = 4.915 * 10 ^ 6ビットが必要です。これは、Cyclone IIで使用可能なオンチップメモリよりもはるかに多くなります。 したがって、フレームを保存するために、DE-1ボード上の別のチップにあるSDRAMを使用します 。 これにより、技術的な問題を解決するためのフレームバッファーを整理し、SDRAMコントローラーの作成を練習する機会が与えられます。

次の問題は、前の問題の解決策から発生します。 プロジェクトでSDRAMを使用する場合、2つの重要な点を考慮する必要があります。まず、設計のためにメモリが120 MHzの高周波数で動作し、新しい問題に直面しています。カメラのドメインからSDRAMドメインにデータを転送します。 第二に、最大のパフォーマンスを達成するには、SDRAMへの書き込みは、バーストと呼ばれるトランザクション全体で行う必要があります。 これらの問題を解決するには、オンチップFPGAメモリに編成されたFIFOが最適です。 基本的な考え方は次のとおりです。低周波数のカメラがFIFOを満たし、その後、SDRAMコントローラーが高周波数でデータを読み取り、1回のトランザクションですぐにメモリに書き込みます。

モニターへのデータ出力は、同じ原理で構成されています。 SDRAMからのデータはFIFOに書き込まれ、25 MHzの周波数で抽出されてDACに供給されます。 FIFOを空にした後、操作が繰り返されます。

最小の問題は、「箱から出してすぐ」のカメラ設定が私たちに合わないことであり、それらを変更する必要があります。 最も重要なポイントは、カメラがデータをYUV422形式で出力するため、RGB444に変更する必要があることです。 OV7670の内部レジスタにアクセスするには、I2Cトランスミッタモジュールを記述する必要があります。

これで、どのモジュールを実装し、どのタスクを解決するかを指定できます。

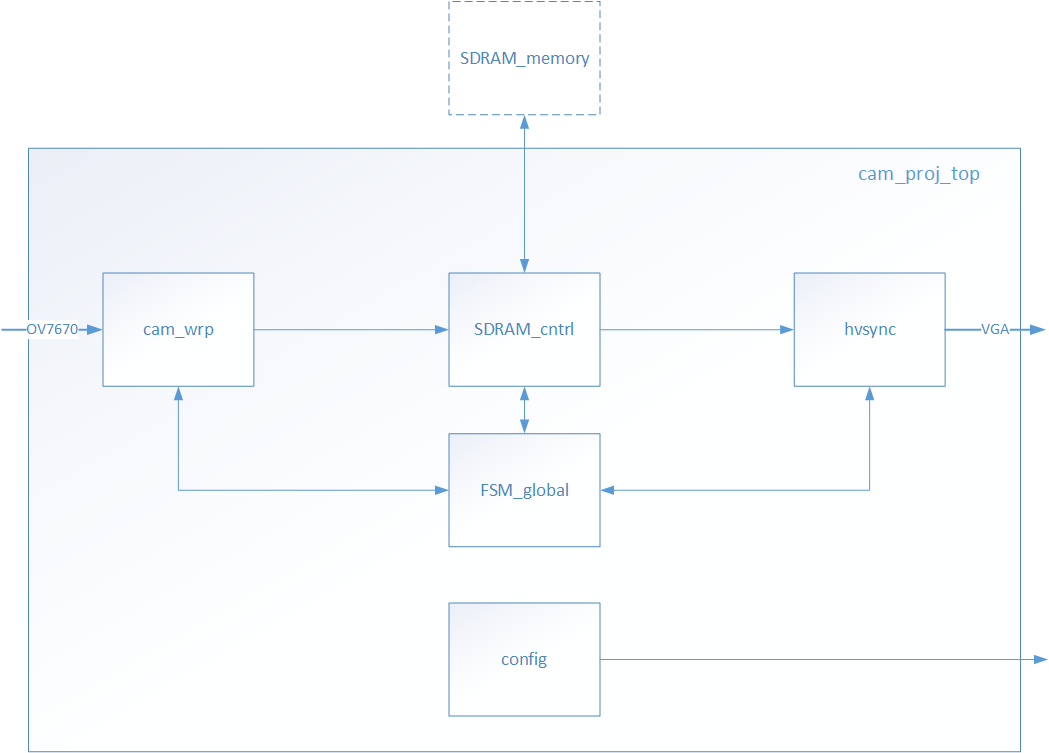

- cam_wrp-モジュールはカメラからデータを受信し、入力FIFOに書き込みます。

- hvsync-モジュールはVGAのストローブを生成し、SDRAMからデータを受信し、入力FIFOに書き込み、ストローブに沿ってDACに送ります。

- sdram_cntr-SDRAMコントローラ。

- FSM_global-自動制御。

- camera_configure-設定およびカメラ制御用のモジュール。

図3に、設計の機能図を示します。

図3

各モジュールをさらに詳しく検討してみましょう。

cam_wrpモジュール

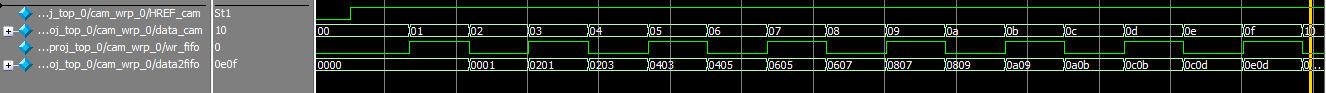

最も簡単なモジュールの1つ。 カメラのhsyncストロボの動作時のタスクは、2バイトを連続して取得し、それらから1つのダブルバイトワードを形成し、FIFOに書き込むことです。 コントローラのSDRAMからの信号により、FIFOのすべての内容をコントローラに転送します。

2連続バイトを1ワードに「パック」するには、wr_fifo信号を使用します。これはクロックで反転します(周波数を2で除算します)。 この信号が論理1の場合、データを下位バイトに書き込み、論理0の場合は上位バイトにデータを書き込みます。 FIFOの書き込み信号としてwr_fifoも使用します。 データバスに加えて、FIFOからバスが表示され、そこに書き込まれたデータの数が設定されます。 このバスはコントロールユニットに接続されています。 図4は、バイトをダブルバイトワードに「パック」するタイミング図を示しています。

図4

FSM_globalモジュール

モジュールには非常に哀れな名前があり、実際には4つの状態のみを持つ単純なオートマトンですが、非常に重要な機能を実行します。 コントローラの準備信号sd_ready SDRAM、入力および出力FIFOのフルネスを追跡し、マシンはコントローラにSDRAMコマンドを発行して、入力FIFOからデータを収集するか、出力FIFOに書き込みます。 読み取りと書き込みは、FIFOが完全にいっぱいまたは空になるよりも少し早く発生します。 高い周波数のFIFOでの操作が低い周波数よりも早く終了しないように、正しいFIFO充填レベルを選択する必要があります。これにより、エラーが発生することが保証されます。 SDRAMコントローラの一部では、この機能を説明する図を示します。

SDRAM_contrモジュール

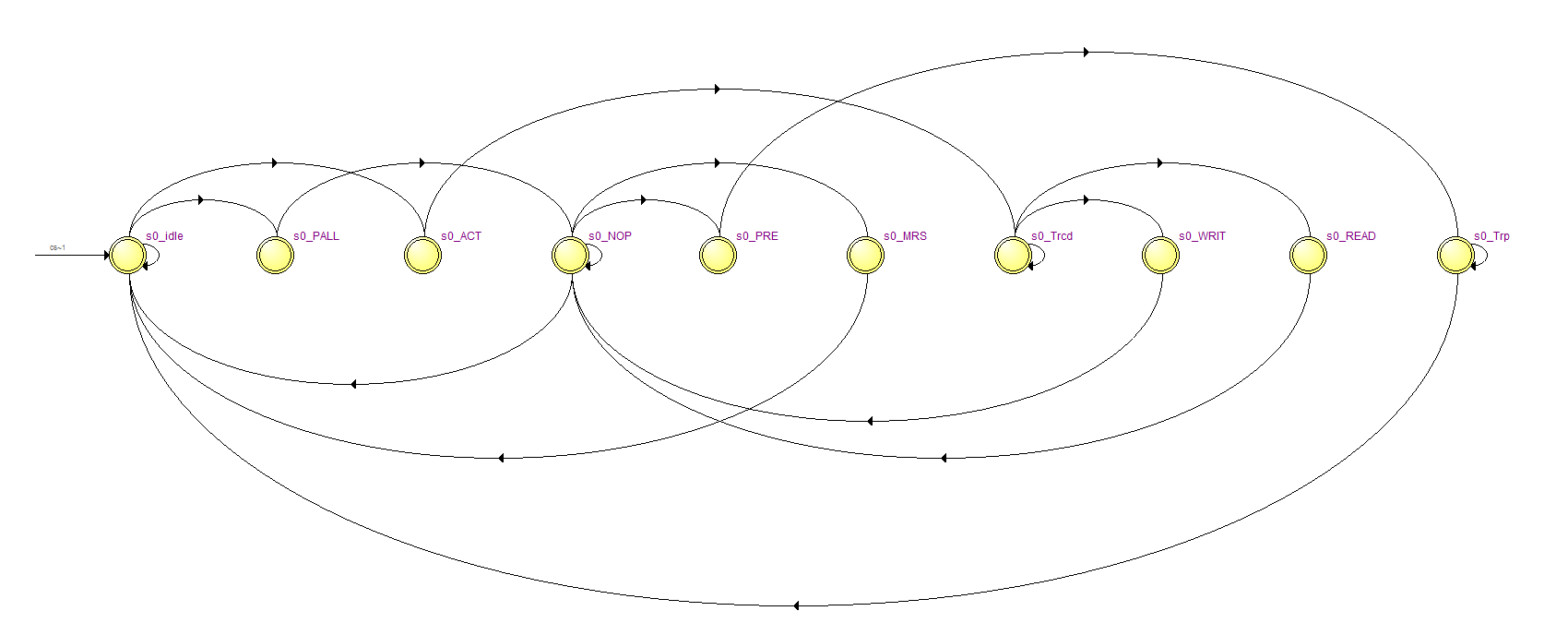

多くのSDRAMコントローラがすでに記述されているため、車輪の再発明を望まなかったため、キャタピラーバイクを発明することにしました。 つまり、SDRAMコントローラーは、この特定のプロジェクトのために研ぎ澄まされました。 これにより、管理が簡単になり、速度が少し向上します。 本格的なSDRAMコントローラーのオートマトン遷移グラフを図5に示します。

図5

除外できると考えてみましょう。

まず、データを更新しません。 この仮定は、汎用コントローラーには絶対に適していませんが、今回のケースでは、同じメモリー領域を使用し、常にそれを参照しています。 データには劣化する時間がありません。

第二に、長さ640のベクトルでデータを常に読み書きするため、個々の数値を扱う可能性を拒否でき、バーストのみを書き込みます。

第三に、アドレスについて考える必要はありません。各バースト後にアドレスをインクリメントし、各フレームの終わりにゼロにします。 結果の遷移グラフを図6に示します。

図6

コントローラはアイドル状態で起動します。 通常の動作を開始する前に、メモリチップ(マシンs0_MRSの状態)を初期化する必要があります。その後、mode_flagフラグが設定され、コントローラーがスタンバイ状態になり、データの書き込みと読み取りが可能になります。 これを行うには、fsm_globalモジュールから読み取りまたは書き込みを開始するコマンドを受け取り、選択したバンクで必要な列を開いて(状態s0_ACT)、読み取りまたは書き込み(状態s0_WRIT、s0_READ)を実行する必要があります。 残念ながら、1つのバーストは機能せず、メモリチップの列の深さは256 16ビットワードのみであり、640のベクトル長を書き込む必要があります。3バースト、256のうち2つ、128のうち1つを書き込む必要があります。行は空のままです。つまり、リソースを不合理に使用していますが、リソースが不足していないため、マシンを複雑にせずに我慢することにしました。

アドレスに関しては、読み取りと書き込み用の異なるレジスタが割り当てられ、各バストの前にインクリメントされます。 したがって、長さ640のベクトルを書き込むには、640 * 4 = 1440アドレスを使用します。 カメラの垂直同期ゲートまたはVGAアドレスは、それぞれ書き込みと読み取りのためにゼロにリセットされます。

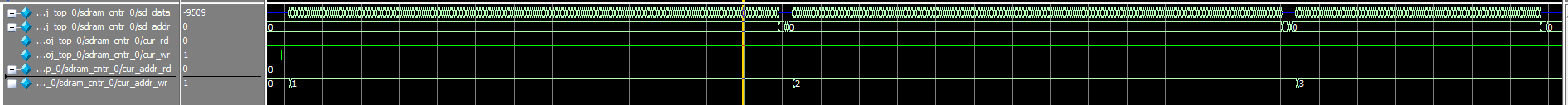

ダブルバッファリングを使用します。あるバッファに書き込み、別のバッファから読み取ります。 単純化するために、SDRAMチップのバンク0に1つ、バンク1に2つ目のバッファーを配置しました。 読み取りおよび書き込み用のバンクは、カメラからのフレームの終了後に場所を変更します。 図7は、単一のベクトルを記録するタイミング図を示しています。 レコードが3つの部分に分割されていることがわかります。各アドレスがインクリメントされた後、転送全体がストロボcur_wrの下で行われます。 読むために、図は似ています。

図7

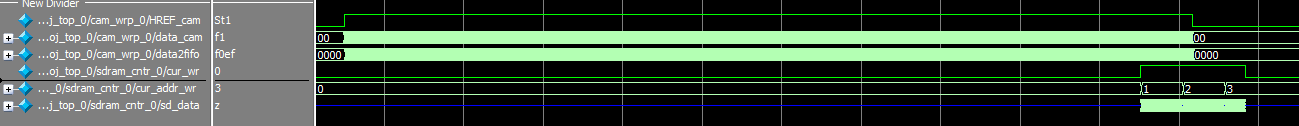

図8は、FIFOの充填時間と比較して、カメラからのデータがどのようにSDRAMに記録されるかを示しています。 最終FIFOがいっぱいになるのを待たずにSDRAMに書き込みを開始することに注意してください。

図8

Hvsyncモジュール

これは、このプロジェクトの2つのモジュールのうちの1つであり、私が作成したものではありません。 一度同様のモジュールを実装したら、繰り返すことに興味がなかったので、サイトmarsohod.orgの作者が書いた優れたモジュールを使用しました。 このモジュールには余分なものはありません。パラメータ化されており、任意の画面解像度に簡単に構成できます。 実質的には変更せず、FIFOのみを追加し、SDRAMコントローラーに接続し、信号をバインドしました。 バスはFIFOで表示され、そこに記録されるデータ量が設定されます。このバスは、入力FIFOとの類推によってコントロールユニットに接続されます。 FIFO出力は、DACに向かうワイヤに接続されます。

Camera_configureモジュール

最初は、ホームプロジェクトの自由を取り、ドキュメントを不注意に読んで、カメラを「デフォルト」設定で起動したかったのですが、OV7670なしではRGB565形式ではなく、YUV422で情報を送信することがわかりました。 何も書き直したくなかったので、すべてを賢明に行い、カメラを適切に初期化することを決めました。 カメラはI2Cによって制御されるため、NIOSを使用するというアイデアが思いつきました。 オープンコアでI2Cピールを使用してNIOSを半分のキックから取得することはできませんでしたが、誤ってVerilogの初期化モジュールを見つけました。 コードに非常に簡単に統合できたため、何も変更する必要はなく、1行だけ変更しました。ボードには正確に4ビットDACがあるため、RGB565ではなくRGB444モードを有効にしました。 図9は、0x80を0x12で記録することによるカメラのソフトウェアリセットのタイムダイアグラムを示しています。

図9

結果のデモンストレーション

すべてのモジュールを作成したら、トップモジュールでそれらを接続し、Quartusでアセンブルすると、テストできます。 ビデオは結果を示しています。

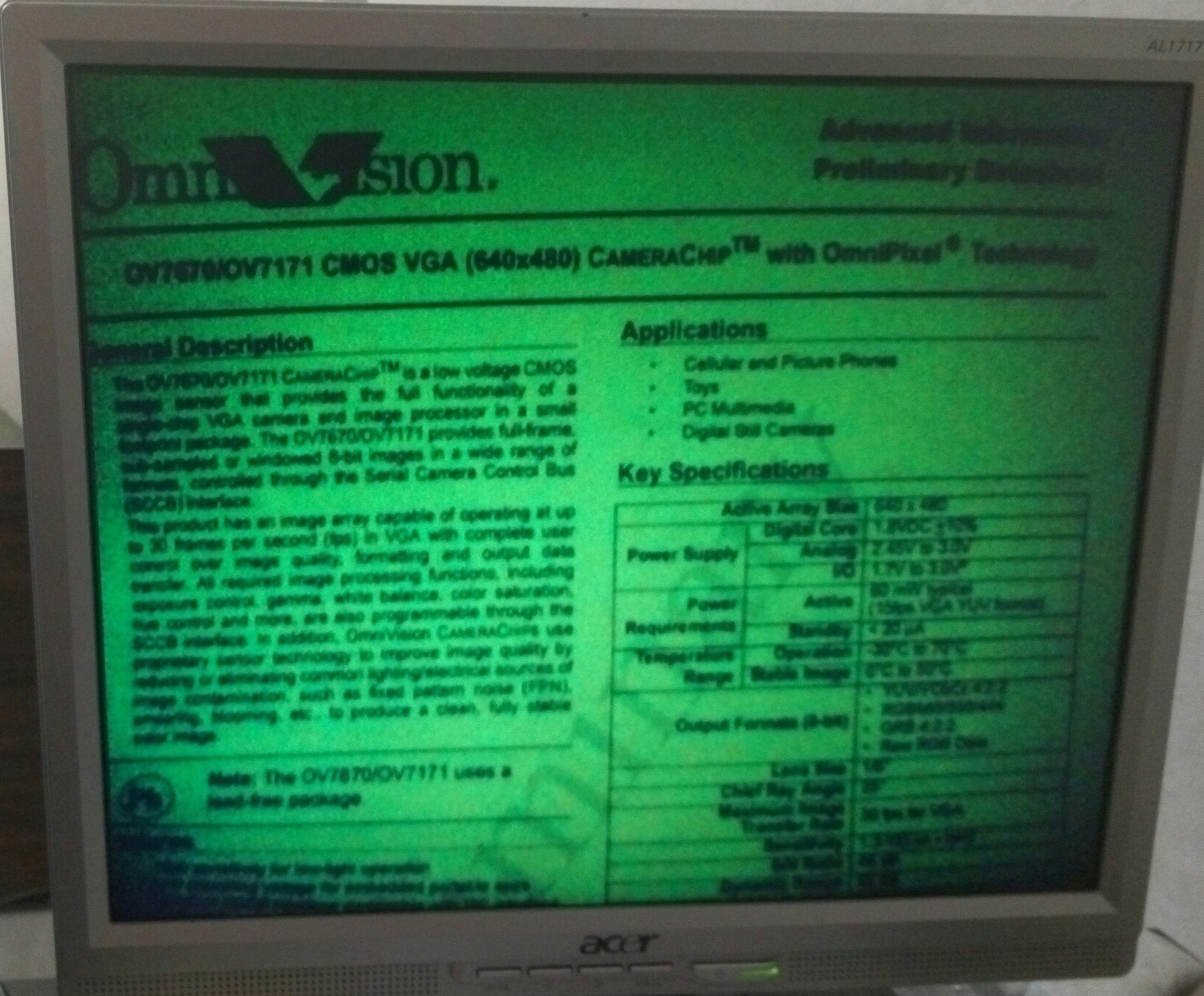

私は撮影にあまり良くない時間を選択しました-日没と非常に明るい太陽-カメラは明るすぎる太陽のまぶしさに十分に反応しません。 動いているオブジェクトが正しく表示されており、けいれんやループがないことがわかります。 これは、FPGAを使用して実現したものであり、わずか30のすべて(およびカメラの機能)fpsを少ない血液で処理できます。 画像の鮮明さについて話すと、A4シートのテキストは問題なく読み取られますが、残念ながら、モニターの写真は実際よりも悪いと言えます。 図10に、カメラのドキュメントを含むシートA4の断片を示します。

」

」

提示されたビデオと写真にはいくつかの欠陥があります。最初の欠陥はシャープで、2番目は色付きです。

私は不完全に焦点を合わせて、ビデオのシャープネスと問題を結び付けます。 スレッド上にあるレンズをねじ込むことにより、カメラの焦点を機械的に調整します。 糸はプラスチックであり、わずかな揺れからでもかなり大きなバックラッシュがあり、シャープネスが低下する可能性があります。

私には、白いシートの過剰な緑黄色の問題は、ホワイトバランスの問題と関係しているようです。撮影は、自然から遠く離れた部屋で行われました。 また、カメラの設定は色の状況に影響する場合があります。 私は実際にそれを脱ぐ実験をせず、マジックナンバーとして使用しました。

おわりに

タスク-OV7670カメラからVGAモニターへのリアルタイムの画像出力-は解決されました。 このプロジェクトで得られた結果を、マイクロコントローラーまたはArduinoを使用する他の開発者によって得られた結果と比較すると、移動オブジェクトの表示速度が劣ることがわかります。 このプロジェクトの複雑さは、マイクロコントローラーを使用して作成された同様のものを超えません。 FPGAデザインの初期知識を持っている人は、数日でそれを実装できます。 このプロジェクトは拡張の大きな可能性を秘めています。結果の画像やオブジェクト認識などをフィルタリングできます。 Cyclone IIチップの設計は、LE-745(4%)、メモリビット-32768(14%)、PLL-1(25%)、Embedded Multiplier-0(0%)のリソースを使用します。アイデアを実装するのに十分なリソース。

あとがき

次は? 将来的には、 マトリックスフィルターを使用したリアルタイムの画像処理を追加して、プロジェクトを拡大する予定です。

記事の内容とデザインに関するアドバイスをしてくれたishevchukと、綴りについて彼女に感謝します。

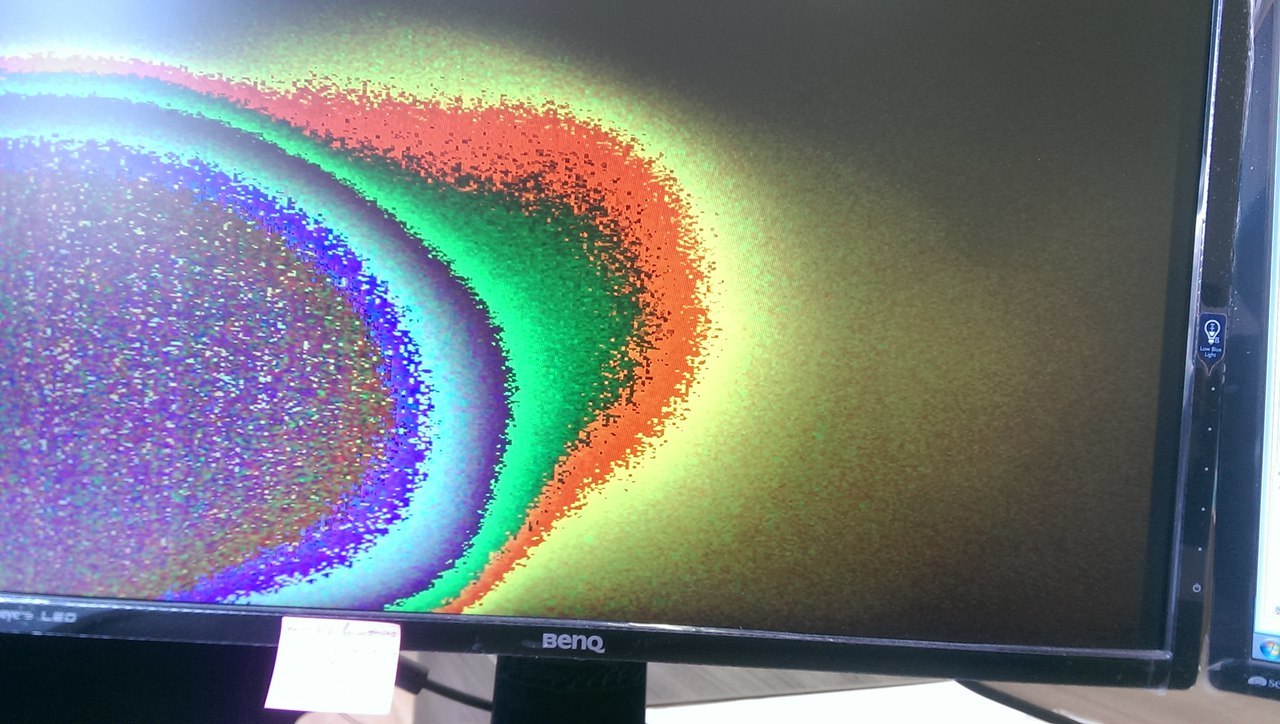

悪い重複

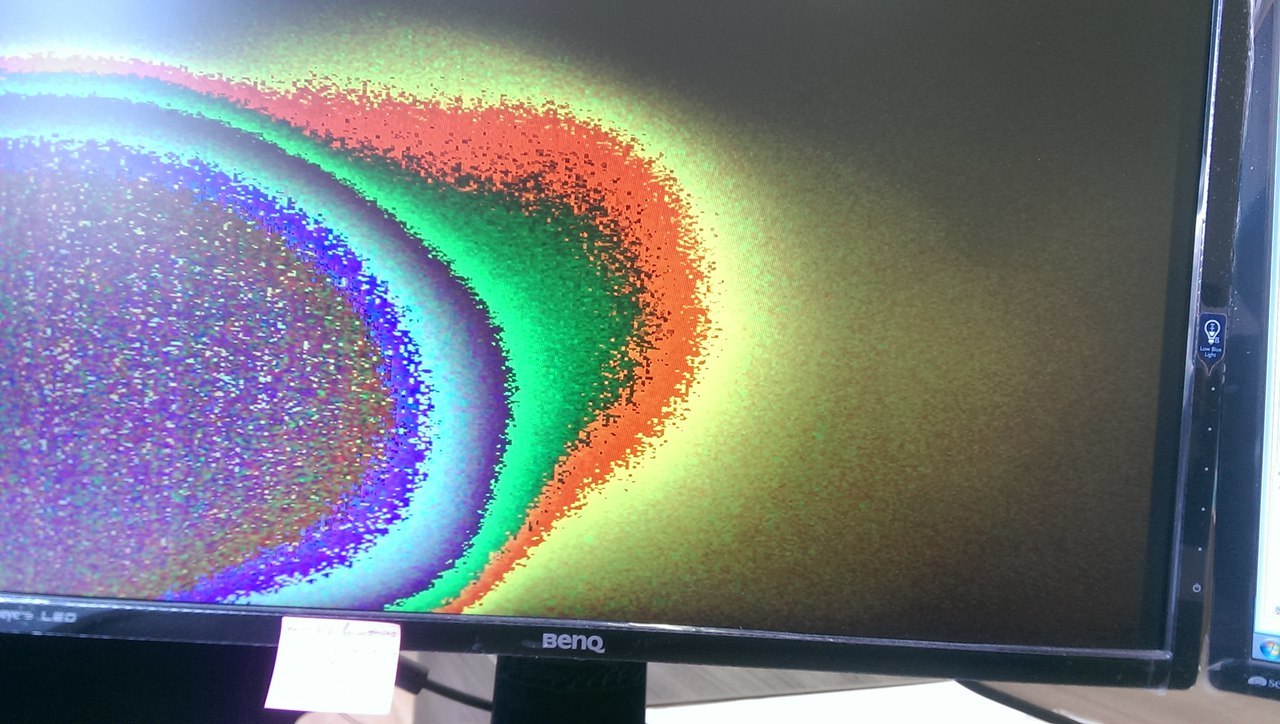

最初に画面をオンにすると、神秘的なパターンが現れました。 私はそれが何であるかを長い間考えていました。 その結果、カメラにフォーカスが設定されていないことが判明しました。 レンズのレンズをねじった後、すべてが所定の位置に収まりました。

「alt = "画像" />

「alt = "画像" />

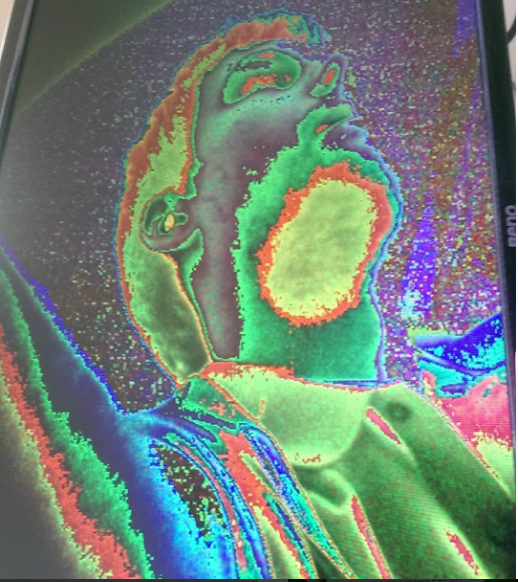

2度目にカメラの電源を入れたときに、カメラが誤って初期化され、予期しないセルフィーが発生しました。

」

」

「alt = "画像" />

「alt = "画像" />

2度目にカメラの電源を入れたときに、カメラが誤って初期化され、予期しないセルフィーが発生しました。

アーカイブのソースはこちら(Ya.Disk)からダウンロードできます。