「Making Tetris for FPGA」という記事を読んだ後、私はかつて彼女に「手と心」を提供するために使用していた類似のプロジェクトがあったことを思い出しました。

そして、あなたに似たようなことをしてみませんか?

ソースを掘り下げて、彼は失われた知識を更新し、古いプロジェクトに基づいて、古いバージョンのSpartan3Eでゲーム「Minesweeper」の簡単なバージョンを作成することを決めました。 実際、論理ゲートのレベルでのマインスイーパゲームの実装とザイリンクスFPGAの開発の主な機能については、この記事で説明します。

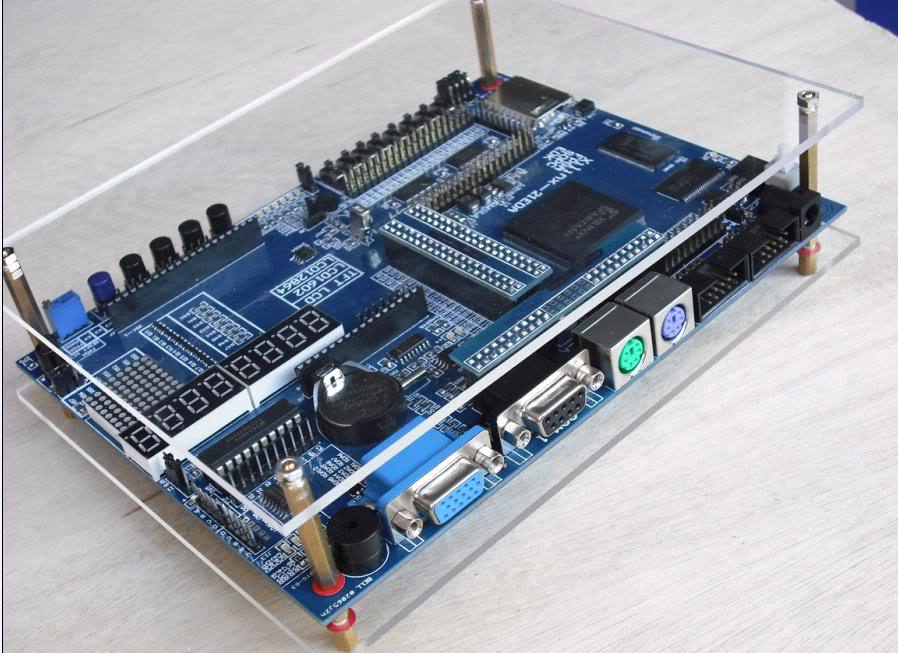

デバッグボード

数年前、FPGAとVGA、PS / 2、LEDとLEDディスプレイの存在、トリガースイッチなどの異なるインターフェースへの最もシンプルなバインディングを備えたデバッグボードの予算オプションを探していました。 それから私は最も簡単な中国のクジラに落ち着きました。これは配達を考慮に入れて135.00ドルでebayで注文するのが最も簡単でした。 ちなみに、キットは不完全でしたので、私は怒ったレビューを残しました、それに対して売り手は20ドルを返しました。 そのため、ボードの価格は旧価格で約4000rでした。

クジラの製造業者の公式ウェブサイト 。

devkitaの主な機能:

- FPGA Spartan3E( XC3S500E-4PQ208C ) -50万論理ゲート、

- クロックソースCLK = 50 MHz、

- 外部メモリ64M SDRAM、

- FPGAファームウェアを保存するためのSPIフラッシュ(M25P80)、

- LEDマトリックス8x8、LEDライン8個、

- 8つのスイッチと5つのボタン、

- LEDディスプレイ用コネクタ、

- ディスプレイ用VGAコネクタ

- PS / 2コネクタなど

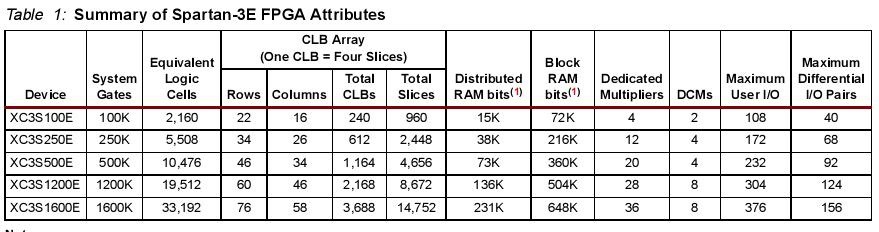

Spartan3E XC3S500Eクリスタルのリソースを表に示します。

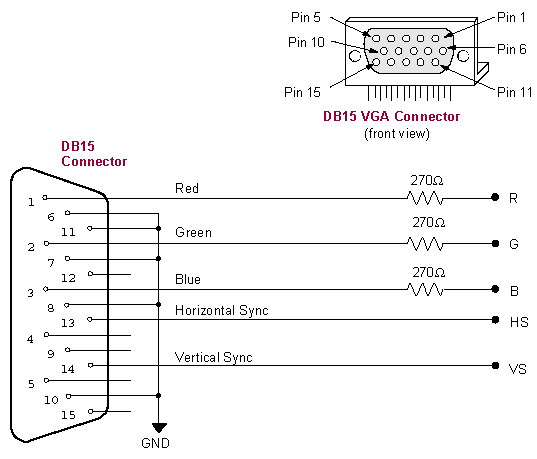

マインスイーパゲームを実装するには、すべての種類のうち、 VGAおよびPS / 2コネクタが必要です。 それらに加えて、FPGA内のロジックのグローバルリセットにスイッチを使用しました。

ゲームの基本概念

どうした?

古いプロジェクトでは、次のものが実装されています。

-キーボードからのコマンド入力(制御PWM変調器とディスプレイ);

-解像度640x480の自己記述VGAインターフェイス。

-PWMに基づく8x8 LEDのマトリックス上の点滅するハート。

最初の2点はゲームの開発時間を大幅に短縮したため、自転車を発明しませんでした。

ゲームのルール:

- キーボード制御:

「 WSAD 」-画面内を移動する矢印ボタン。

「 Enter 」-地雷の有無をフィールドで確認します。

「 スペース 」-新しいゲームを開始します。

「 Esc 」-現在のゲームを完了します。

「 Y / N 」-新しいゲームを開始します。 - フィールド8x8、フィールドあたりわずか8分。

- 残りのルールは、通常のサッパーゲームと同じです。

FPGAプログラミング言語: VHDL

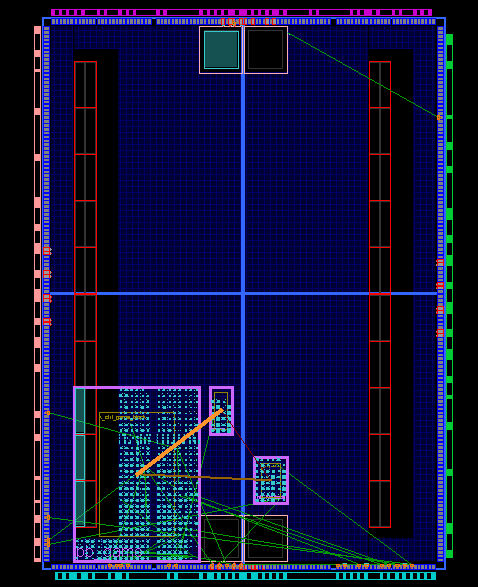

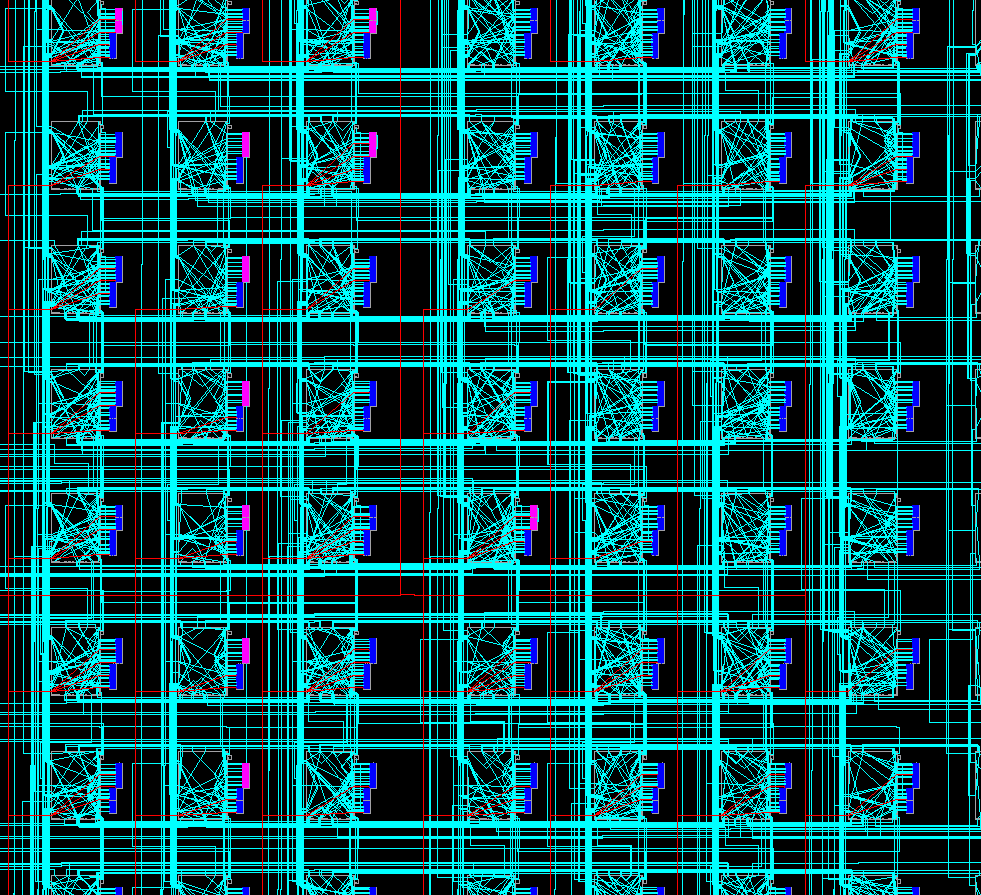

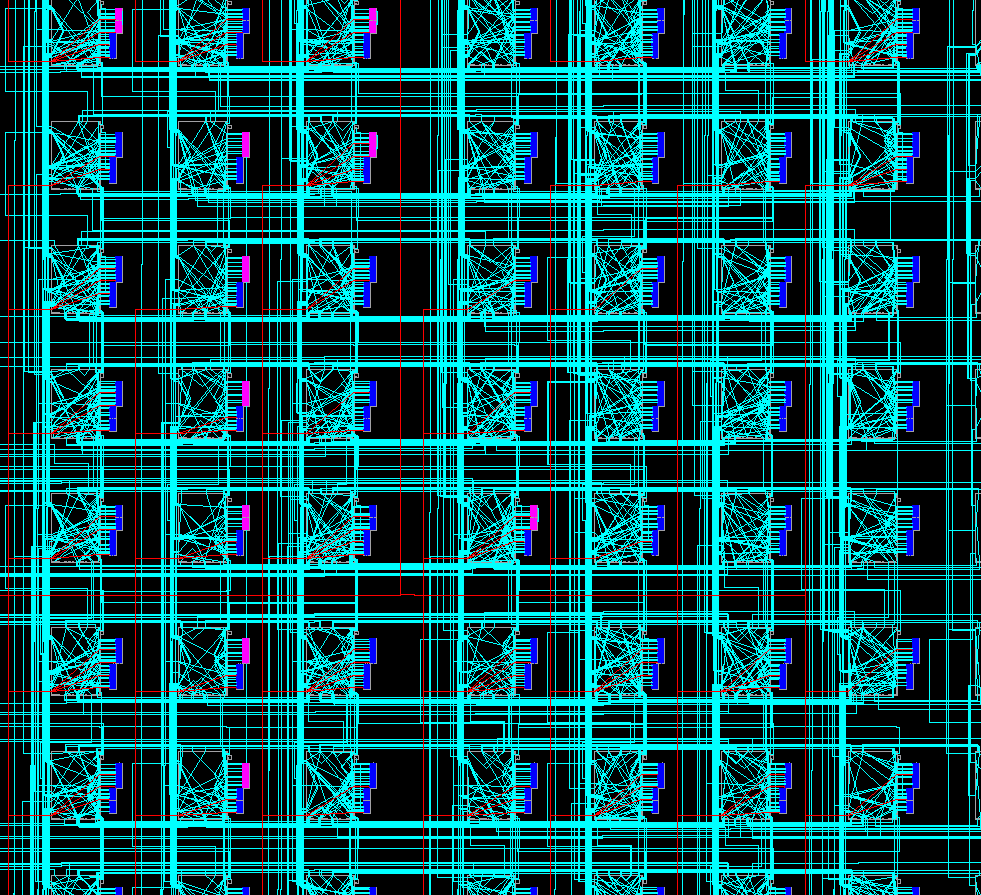

これは、PlanAheadプログラムの完成したプロジェクトが、合成およびトレースの段階をどのように処理するかを示しています。 紫色のフレーム内のブロックは、クリスタルの占有リソースです。

大きなブロック:ゲームのメインロジック。

中央ブロック:PS / 2キーボードコントローラー;

小ブロック:VGAディスプレイコントローラー。

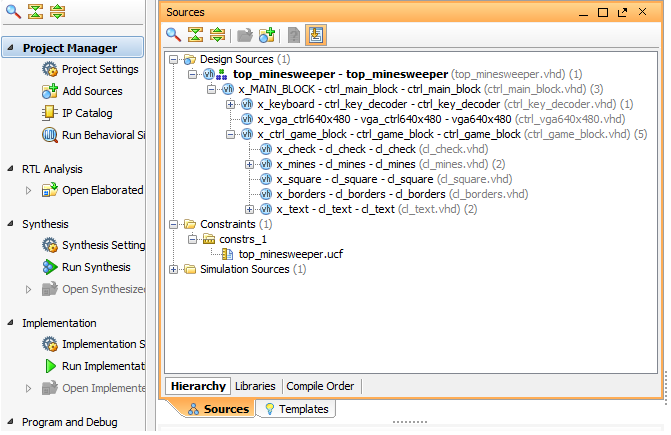

プロジェクト階層:

設計の最初の段階の1つでは、プロジェクトがどのように見えるか、および記述がより便利なコンポーネントの数を把握する必要があります。 私は次の構造を思いつきました:

->トップレベル

----> PS / 2コントローラー

----> VGA 640x480コントローラー

---->ゲームコントローラー

------->四角形の境界描画ブロック、

-------> 8x8の入力済みフィールドを描画するためのブロック

------->フィールドに地雷や数字を描くためのブロック

----------->地雷の配置のためのメモリ

----------->文字メモリ

------->テキストおよびダイアログメッセージのレンダリングをブロックする

----------->文字メモリ

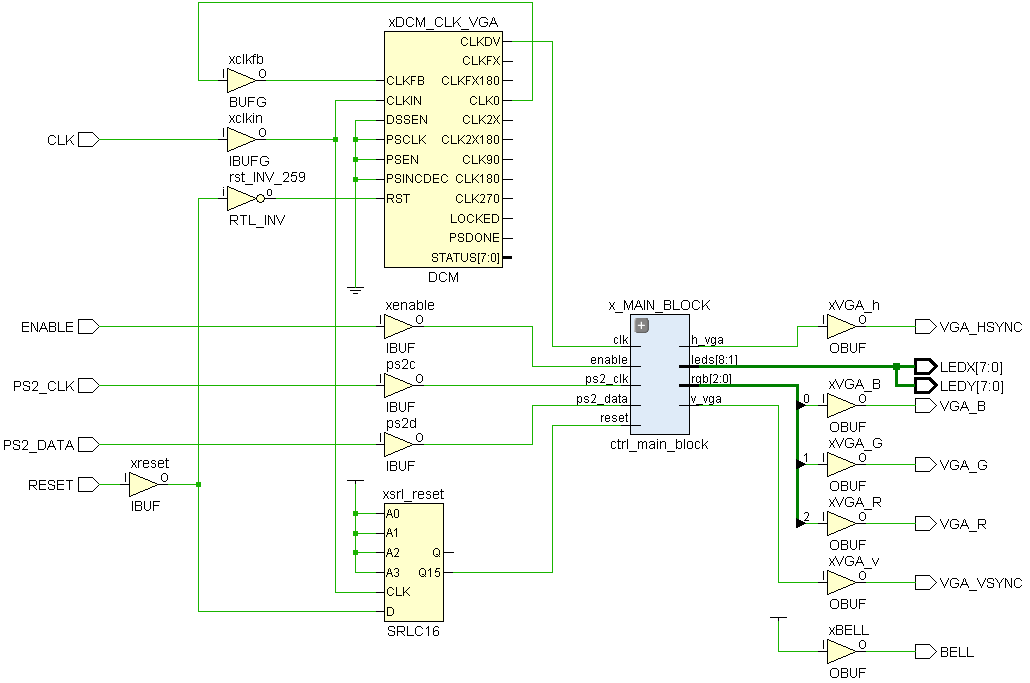

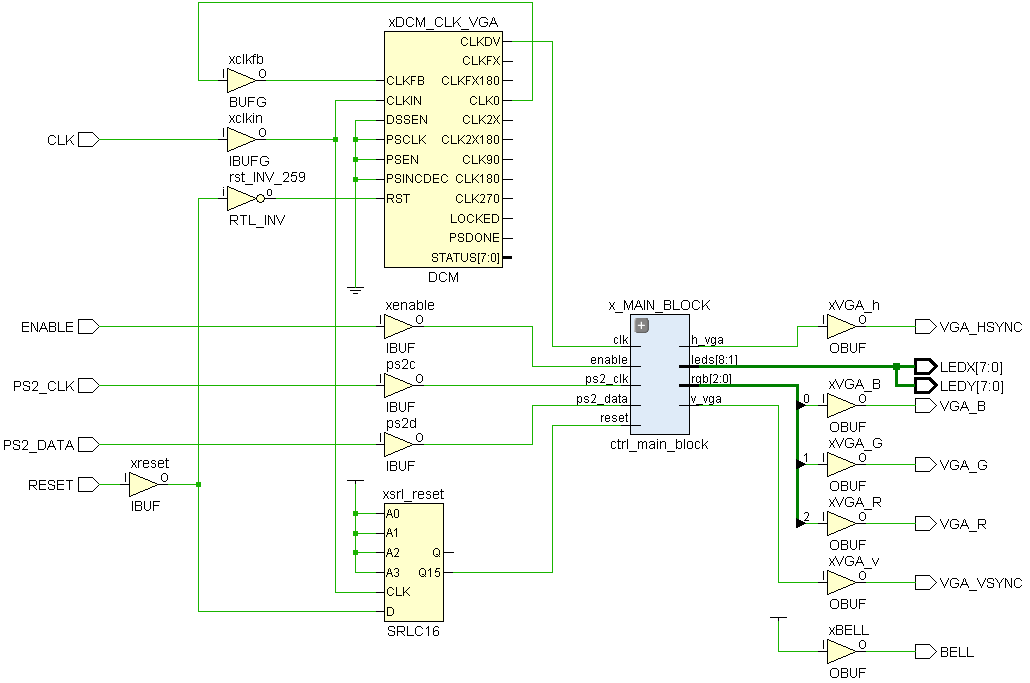

これは、ザイリンクスPlanAhead環境での外観です。

トップレベル

メインI / Oポートについて説明し、入力周波数を50 MHzから25 MHzに変換するためのDCM周波数合成ユニットが含まれています。 最上位コードは次のとおりです。

entity top_minesweeper is port( -- PS/2 IO -- PS2_CLK : in std_logic; -- CLK from PS/2 keyboard PS2_DATA : in std_logic; -- DATA from PS/2 keyboard -- CLOCK 50 MHz -- CLK : in std_logic; -- MAIN CLOCK 50 MHz -- VGA SYNC -- VGA_HSYNC : out std_logic; -- Horizontal sync VGA_VSYNC : out std_logic; -- Vertical sync VGA_R : out std_logic; -- RED VGA_G : out std_logic; -- GREEN VGA_B : out std_logic; -- BLUE -- SWITCHES -- RESET : in std_logic -- Asynchronous reset: SW(0) ); end top_minesweeper;

PS / 2コントローラー

このプロジェクトは基礎として採用されています。 すぐに獲得しました。 シリアル伝送インターフェイスは非常に原始的です。2行:キーボードコマンドであるPS2_CLKとPS2_DATAです。

落とし穴-最初は「Make」コードの助けを借りて、キーの「キーストローク」を知らせる単一のインパルス(エッジに沿って)を生成しました。 これにより、別のキーが押されたときにシミュレートされた再押下が行われました。 バイトの「Make」コードと「Break」コードは一致するため、「Break」コードを指定すると、条件をより明確にする必要がありました。

PS / 2コントローラーのコード表は、上記のリンクに記載されています。

VGAコントローラー

一度、トレーニングの目的で、私は自分で書きましたが、その操作のアルゴリズムはすべてのVGAコントローラーとまったく同じです。 Habréでも同様です 。

主な機能:

-コントローラー周波数:25.175 MHz

-画面解像度:640x480

-更新頻度:60Hz

-利用可能なパレット:RGB

残念ながら、デバッグボードには組み込みのカラーパレット復号化チップがないため、 3つの原色 (赤、緑、青)と5つの組み合わせ (黄色、マゼンタ、シアン、白、黒)しか使用できません。 しかし、これは配色を思い付くために止まらず、まばたき画像を表示することさえありません! (最後のビデオを参照)

ゲームコントローラー

Sapperゲームコントローラーを記述する最も簡単な方法は、ステートマシン( FSM )に基づいています。 特定のイベントが処理されるマシンの状態を考え出す必要があります。

私のプロジェクトでは、マシンの5つの基本的な組み合わせを使用しています。

- WAIT_START (すべての制御信号のリセット、最小カウンター、ランダムゲームジェネレーターの起動。

- PLAY (ゲームプロセス:キーボードからのボタンの制御、地雷検索);

- CHECK (地雷が見つかったかどうかを確認します-ゲームの最後に進みます);

- GAME_OVER (勝利または敗北のイベントを決定し、ディスプレイに追加のメッセージを表示します);

- RST (オプションのステージ-画面をクリアし、新しいゲームを開始する可能性なしにすべての制御信号をリセットします)。

キャラクターメモリー

インターネットで発見。 1文字の寸法は8x16です。 シンボル「1」の例:

"00000000", -- 0 "00000000", -- 1 "00011000", -- 2 "00111000", -- 3 "01111000", -- 4 ** "00011000", -- 5 *** "00011000", -- 6 **** "00011000", -- 7 ** "00011000", -- 8 ** "00011000", -- 9 ** "00011000", -- a ** "01111110", -- b ** "00000000", -- c ** "00000000", -- d ****** "00000000", -- e "00000000", -- f

すべてのキャラクターは、RAMB16クリスタルブロックメモリの単一ブロックに収まります。 メモリは、シンボルが容量8の16個のベクトルで構成されるように配置されます。シンボルを表示するには、アドレスバスの下位4ビットをY座標ベクトルに接続する必要があります。論理 '1'-シンボルの色、 '0'-背景色(黒)。

フィールドに地雷を配置するためのメモリ

プロジェクトのこの部分を最も長く修正し、さまざまな洗練されたソリューションを発明しました。 最終的に、ゲームを選択するROMメモリの形式で次のコンポーネントを作成することにしました。

コードの一部:

constant N8x8 : integer:=8; -- 88 constant Ngames : integer:=1; -- type round_array_3x64xN is array (Ngames*N8x8*N8x8-1 downto 0) of integer range 0 to 7; constant mem_init0: round_array_3x64xN:=( -- game 0: 1,1,1,0,0,0,0,0, 1,7,1,1,1,1,0,0, 1,1,1,1,7,2,1,0, 0,0,0,1,2,7,1,0, 0,1,1,1,1,1,1,0, 0,1,7,2,7,1,1,1, 0,1,1,2,2,2,2,7, 0,0,0,0,1,7,2,1);

定数N8x8およびNgamesは、フィールドのサイズとゲーム数を指定します。 フィールドの番号は、鉱山またはその周辺の鉱山の数に対応しています。 ルールは非常に簡単です。

- 0〜6の数字-鉱山の数を決定し、

- 番号7-フィールドで地雷を予約および定義します。

なぜそう

私は、7分または8分がポイントのすぐ近くにある状況を考えていませんでした。 8分間と8x8フィールドでは、これらはあまりにも面白くない決定です。 また、0〜7の数字は3ビットのみを占有しますが、鉱山の0〜8と9の組み合わせはすでに4ビットを占有しています。 この点で、私はクリスタルの内部ロジックとトレースリソースを節約することを大いに楽しんでいます。たとえこれらのリソースが5つのプロジェクトに十分であったとしてもです。

したがって、すべての数値は、ゲームで追加できる一種のROMアレイに収まります。 私のプロジェクトには32個のゲームがあり、RAMB16のメモリブロックは1個弱です。 数値は整数形式で指定されることに注意してください。 std_logic_vector(2:0)への変換とさらなる処理のために、特別な関数が作成されています。 整数形式は、新しいゲームの記録を簡素化し、時間を大幅に節約しました。 多くのVHDL FPGA開発者は、整数型の構造が常に合成されるとは限らないため、整数形式が使用される状況によって混乱に陥ることがあります。 実際のハードウェアではチェックできません。 しかし、ROMジェネレーターの場合、整数が最適です。

独自の鉱山のレイアウトを追加するには、8x8フィールドを配列に正しく入力する必要があります。 手で詰めたゲームのバリエーション。 私のプロジェクトでは、合計32の鉱山配置の組み合わせがあります。

境界線とフィールドを描画するためのブロック8x8

最初はシンボルジェネレーターに実装しましたが、クリスタルリソースを節約することにしました。 網掛けの正方形とフレームのために、RAMB16セル全体を使用するのは意味がないと思いました。 (リソースによる最適化!)したがって、すべてがマルチプレクサで実行されます。 これについては詳しく説明しません。

地雷と数字を描くためのブロック

一連のゲームのメモリのデータを、文字メモリを使用して画面上の数字と地雷に変換します。 最初は、8x8の正方形フィールドを表示したかったのですが、それからROMジェネレーターを書き換えるのが面倒になり、長方形のままにしました。

このブロックでは、特別な8x8マスクも作成する必要がありました。これを使用して、「Enter」を押すと、塗りつぶされたセルが数字または地雷に変わります。

テキストとメッセージ

テキストは1つの部分で書かれています。つまり、すべてが一度に画面に書き込まれますが、ゲームの段階によっては、一部の情報が見えないままになります(たとえば、敗北や勝利に関するメッセージ)。 同じ文字ジェネレーターが使用されます。 シンボルのサイズは8x16であるため、640x480の表示フィールドはセクション80x30に分割でき、そこにシンボルが表示されます。 これはどのように行われますか?

以下に簡単な例を示します。

addr_rom <= data_box(6 downto 0) & y_char(3 downto 0) when rising_edge(clk); x_char_rom: ctrl_8x16_rom -- port map ( clk => clk, addr => addr_rom, data => data_rom); pr_sel: process(clk, reset) is -- begin if reset = '0' then data <= '0'; elsif rising_edge(clk) then data <= data_rom(to_integer(unsigned(not x_char(2 downto 0)))); end if; end process; g_rgb: for ii in 0 to 2 generate -- begin rgb(ii) <= data and color(ii); end generate;

最初に、メモリアドレスを使用して1つまたは別の文字を選択する方法を理解する必要があります。 アドレスが2つのベクトル「y_char」と「data_box」で構成されていることがわかります。

y_char(3から0)は、Y軸に沿った座標ベクトルの最下位ビットであり、このデータは自動的に更新され、VGAコントローラーから取得されます。

data_box(6 downto 0)-信号は、フィールドで使用される文字を選択します。 このベクトルは自分で作成する必要があります。

data_box <= "000001"を書き込むと、ジェネレーターの最初の文字がベクター "data_rom"に書き込まれます。 pr_selプロセスは、データベクトルをシリアルコードに変換します。 X座標レジスタの最下位3ビットに応じて、data_romベクトルの特定のビットが選択されます。 最初は、画面上のデータをミラーリングする問題に遭遇しました。 解決策は簡単です-x_char信号の反転。

出力は、係数メモリからのデータを使用した論理変換後にVGAコネクタに供給されるRGB信号です。

鉄の実現

これはすべて1つの大きなプロジェクトになります。 美しさのために、シンプルなカウンターの助けを借りて、私は勝利/敗北のメッセージの点滅を台無しにし、ランダムゲームを選択するジェネレーターも追加しました。

FPGAポートとさまざまな属性の接続を記述する* .UCFファイルは、VHDLのソースに必ずねじ込まれます。 例:

## Switches NET "RESET" LOC = "P148" | IOSTANDARD = LVTTL | PULLUP ; ## SW<0> NET "ENABLE" LOC = "P142" | IOSTANDARD = LVTTL | PULLUP ; ## SW<1> ## VGA ports NET "VGA_R" LOC = "P96" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ; NET "VGA_G" LOC = "P97" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ; NET "VGA_B" LOC = "P93" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ; NET "VGA_HSYNC" LOC = "P90" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ; NET "VGA_VSYNC" LOC = "P94" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ; ## CLK 50 MHz NET "CLK" LOC = "P183" | IOSTANDARD = LVCMOS33 ; NET "CLK" TNM = "CLK_TN"; TIMESPEC TS_CLK = PERIOD "CLK_TN" 20 ns HIGH 50%; # PS/2 KEYBOARD NET "PS2_CLK" LOC = "P99" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ; NET "PS2_DATA" LOC = "P100" | IOSTANDARD = LVTTL | DRIVE = 8 | SLEW = FAST ;

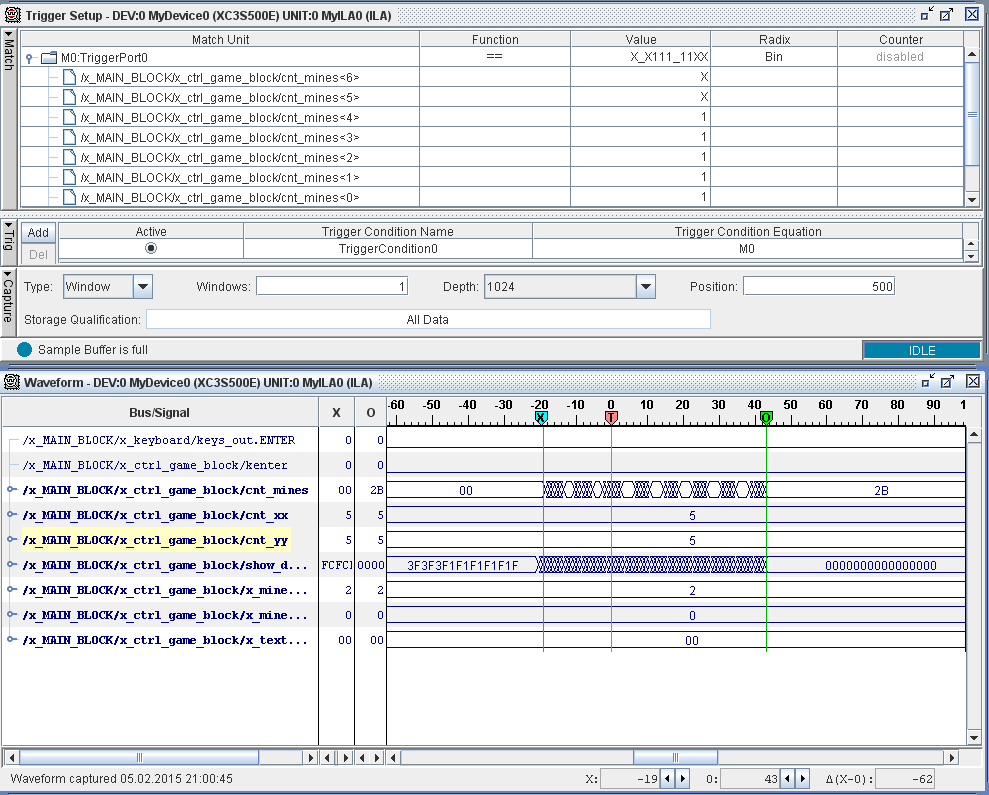

Aldec Active-HDL CADおよびXilinx ISE CADを使用して、FPGAデザインを合成およびトレースします。 イベント処理は複雑であるため、テストベンチを記述せずにデバッグを実行し、ファームウェアをFPGAに直接アップロードして、ディスプレイの出力を確認しました。 原則として、すべてが一度に機能しました。 主なエラーは、信号の同期でした。 たとえば、ラッチされたアドレスの同時操作とデータの読み取りの試行。 このようなエラーは、適切な場所でサイクルごとに追加の遅延を導入することで迅速に修正されます。 深刻な場合、 ChipScope Pro ( Core Inserter and Analyzer )が使用されました。

おわりに

マインスイーパミニゲームは、デバッグボードで正常に獲得しました。

フィールドのサイズは8x8、フィールドあたりの地雷の数は8です。

ゲーム数は32です。開始する前に、地雷の配置はフィールドのメモリからランダムに選択されます。

クリスタルの占有リソース(FPGAはほとんど空です):

写真

結果は次のようになります。

その他の写真...

ゲームコントローラーの分野でのFPGAエディターでのトレース:

RTL回路図のプロジェクトの回路図ビュー:

ChipScope Pro Analyzerでプロジェクトをデバッグ(開いている空のフィールドの数をカウント):

RTL回路図のプロジェクトの回路図ビュー:

ChipScope Pro Analyzerでプロジェクトをデバッグ(開いている空のフィールドの数をカウント):

Githubソースコード 。

ゲームデモ