過去3週間にわたって、MIPSfpga FPGAのプロセッサに関するセミナーがMIET、MSU、MEPhI、MIPT、およびその他のロシアの大学で開催されました。 セミナーの枠組みの中で、MIPSfpgaを実践する方法を実演する実験が行われました。

この出版物では、MIPSfpgaを使用した実験について説明します。これは、実験室での作業を超えており、MIPSfpgaプロセッサコアをopencores.org IPブロックと統合する可能性について検討します。 また、MIPSfpgaを一部のアルテラFPGAベースのボードに移植する方法についても説明します(Fmax値とFPGAリソース使用状況インジケータが示されています)。

私は、経験のあるFPGAハードウェア開発者ではないことを事前に予約したいのですが、MIPSfpgaを使用してFPGAを正確にマスターし始めました。 したがって、プレゼンテーションはややプログラマ中心の方法で実行されます。

背景:MIPSfpgaとは正確には何ですか

MIPSプロセッサアーキテクチャの開発者であるMIPS Technologies社は、困難な運命にあります。1984年に独立企業として活動を開始し、Silicon Graphics(SGI)の一部として残り、独立を取り戻し、2013年初頭にImagination Technologiesの一部となりました品質とこの出版物を書いている時点でです。

MIPSアーキテクチャを備えたプロセッサは、伝統的に学生にマイクロプロセッサのアーキテクチャを教えるために使用されます。たとえば、 MIPT-Intelラボのコースを参照してください。

MIPSfpgaは、教育目的のために特別に設計されたMIPS32 microAptivアーキテクチャを備えたプロセッサコアです。 MIPSfpgaはVerilogでソースコードとして提供されているため、FPGAでの合成に適しています。 この記事の執筆時点では、MIPSfpgaへのアクセスは学生と大学教授のみが取得できることに注意してください。

MIPSfpgaはおもちゃではありません。このプロセッサコアは、イマジネーションが商業的に提供するmicroAptivプロセッサコアと基本的に違いはありません。

MIPSfpgaが属するmicroAptiveファミリーのコアはエントリーレベルに起因する可能性があり、これらのコアは記録的なパフォーマンスを達成することを目的としていませんが、より高度なコアと完全にソフトウェア互換性があります。 MIPSfpgaコアはMIPS32リリース3アーキテクチャに準拠しており、MMU(TLB)とキャッシュメモリが組み込まれています。 必要に応じて、MIPSfpgaでLinuxを実行することもできます。

イマジネーションは、元のMIPSfpgaとともに、MIPSfpgaを使用する方法の例を示すトレーニングマニュアルを提供しています。

mipsfpga-plus:ラボオンチップシステム

ロシアのMIPSfpgaの実験室作業(または単に実験室)は、イマジネーションの従業員であるYuri Panchulによって行われました。 ユーリは、研究室が開催された大学の能力に適応しなければならなかったという事実に主に関連して、作品の元の材料に明確な変更を加えました。

作業のために、MIPSfpgaコアと小さなストラップを含むmipsfpga-plusシステムオンチップを組み立てることが提案されています。

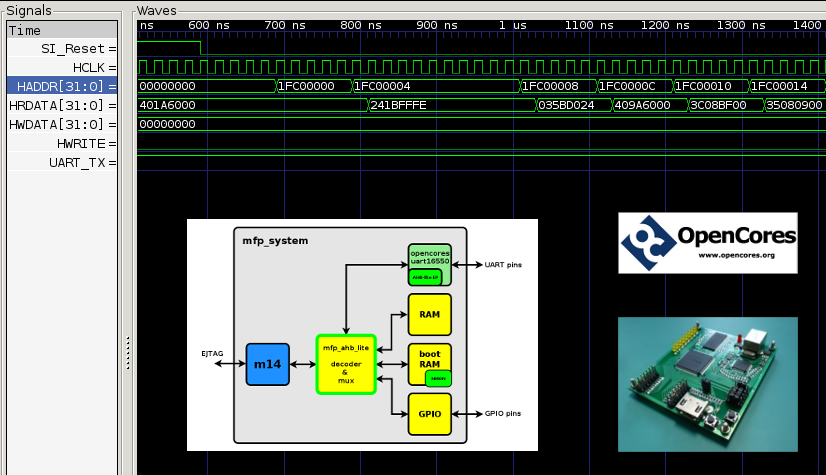

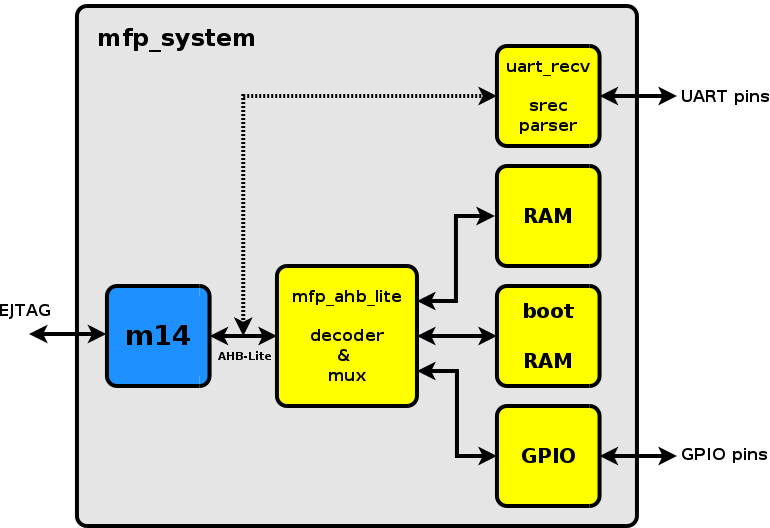

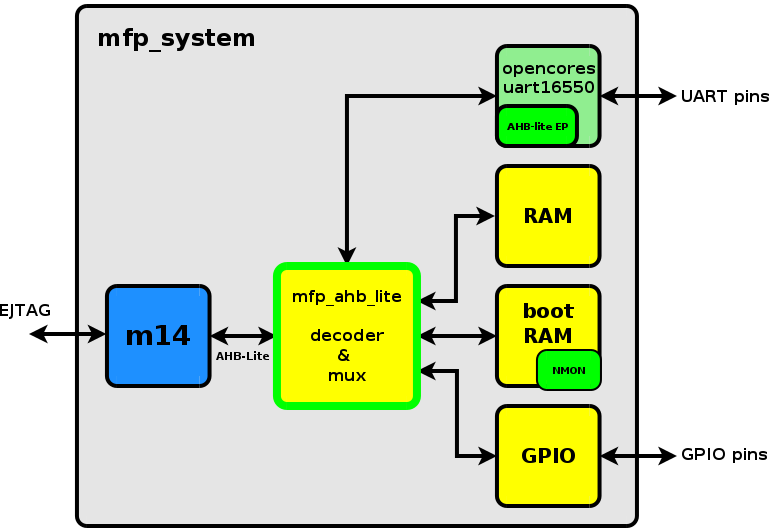

簡略化すると、mipsfpga-plus構造は次のようになります。

図では、m14はMIPSfpgaプロセッサコア( microAptivファミリのM14Kcコアとも呼ばれます)です。 実験室での作業では、コアが外部の世界に接続されるインターフェイスが重要です:EJTAGおよびAHB-Lite。

EJTAGインターフェースは技術的であり、プロセッサーで実行されるプログラムのデバッグを目的としています。詳細については、出版物EJTAG:魅力的なハッカーを参照してください 。

ただし、AHB-Liteインターフェイスは、プロセッサを外部と接続するための主要なインターフェイスです。 AHB-Liteバスは、AHBバスの簡易バージョンです。特に、AHB-Liteでは、バス上で要求イニシエーター(「マスター」)を1つだけ許可しています。 詳細については、AMBA 3 AHB-Liteプロトコルv1.0仕様(ARM IHI 0033A)を参照してください。

mfp_ahb-light decoder & mux

(以降、 デコーダー

mfp_ahb-light decoder & mux

)は、AHB-Liteバス上のプロセッサー要求をデコードし、プロセッサーの宛先アドレスに応じて、IPブロックの1つに要求を転送するブロックです。

- RAM

- ブートRAM。

- GPIO

RAMは、プログラムとデータを保存するためのメモリブロックです。

ブートRAM-RAMブロックと本質的に完全に類似したメモリブロック。 違いは、ブートRAMブロックには、RESET信号が削除された直後に実行されるプログラムが含まれていることです(このブロックはアドレス0x1fc00000にマップされているため)。

GPIOブロックは一連のレジスタで構成され、そのビットはボード上のLEDとボタン/スイッチに接続されています。 このようにプロセッサコアで実行されているプログラムは、外部の世界と対話できます。

実験室での作業のために、ユーリは個々のm14信号をボードのLEDに出力することを提案しています(このような接続は実際には状況に応じたものであり、図には反映されていません)。

これは、デコーダーがIPブロックをAHB-Liteバスの物理アドレスにマップする方法です。

| IPブロック | ベースアドレス | 長さ |

|---|---|---|

| RAM | 0x00000000

| 32K-256K |

| GPIO | 0x1f800000

| 0x14 |

| ブートRAM | 0x1fc00000

| 4K |

注意:AHB-Liteバスでは、プロセッサコアが物理アドレスを設定しますが 、これは原則として、プログラムが動作しているアドレス ( プログラムアドレスまたは仮想アドレス )と一致しません。 MIPSのアドレス指定の詳細については、 「MIPS実行 」の「基本アドレススペース」セクションを参照してください 。

ラボでの作業中、プロセッサはテストプログラムを実行します。テストプログラムは、いくつかの方法でブートRAMにロードできます。

最も簡単なオプションは、FPGAのビットストリームを作成する段階でブートRAMを初期化することです。 一方で、それは非常に簡単です-ビットストリームをFPGAにアップロードし、プログラムが実行を開始します。 しかし、一方で、プログラムに変更を加えたい場合は、ビットストリームを再生成する必要があり、非常に高価になる可能性があります。

より高度な方法は、EJTAGデバッグインターフェイスを使用してプログラムをダウンロードすることですが、この方法では追加のソフトウェアとハードウェアが必要です-JTAGアダプターとOpenocdソフトウェア(EJTAGを使用してBlack SwiftボードのRAMにデータをロードする例を参照: geektimes.ru/post/249184 )

YTAGアダプタはあまりにもエキゾチックであるように見えたため、特にVerilogのmipsfpga-plusの場合、彼はUARTインターフェース(図ではuart_recv srecパーサーとして示されている)を介してSレコード形式のデータロードを実装するIPブロックを作成しました。 この場合、ブートRAMにデータをロードするには、安価なUSB-UARTアダプターとLinuxまたはWindowsに含まれている標準プログラムを使用するだけで十分です。 スイッチをオンにした直後、uart_recvブロックはUARTインターフェイスを介してデータの受信を開始しますが、プロセッサコアは停止します(リセット信号がアクティブになります)。 データを受信した後、プロセッサコアのリセット信号は無効になり、uart_recvブロックは自己リセットします。

mipsfpga-plusの詳細については、 こちらを参照してください 。

MIPSfpgaの移植

MIPSfpgaの標準的なボードは、Terasic DE2-115およびDigilent Nexys4 DDRです。

ただし、MIPSfpgaを他のボードに移植する作業を促した理由があります。

たとえば、単にDigilent Nexys4 DDRボードを購入できませんでした。 Digilentサイトが発行したものは次のとおりです。

Terraelectronicsからボードを購入する可能性についてのリクエストに対して否定的な応答を受け取りました。

Terasic DE2-115ボードに関しては、私の意見では、MIPSfpgaのアプリケーションは銃からスズメを発射することに部分的に似ています:FPGAはMIPSfpgaのリソースを過剰に使用してボードにインストールされますが、同時にボードのコストは非常に高くなります。

しかし、最も重要なことは、プロジェクトを新しいボードに移植すると、FPGAの操作をよりよく理解し、実験室での作業に適したボードのリストを拡大できることです。

移植性の基準

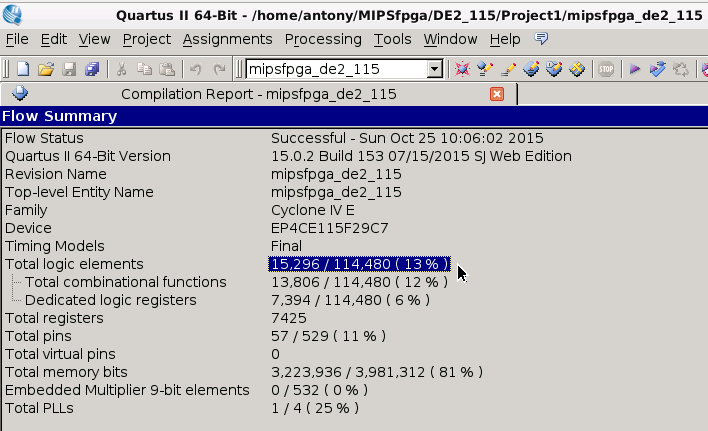

テストのために、DE2-115ボードのリファレンスプロジェクトを合成しました。

プロジェクトが3メガビットのクリスタルメモリを消費したことを気にしないでください-この値は簡単に減らすことができます。 RAMブロックとブートRAMのサイズを小さくするだけで十分です。 オンチップメモリを節約するために、FPGAにはキャッシュの一部を犠牲にする機会さえあります。

レポートからわかるように、FPGAには約15500の論理要素(LE)が必要です。 つまり、20,000以上のLEを搭載したFPGAに集中する必要があります。

そのようなボードを探してみましょう。

テラシックボード

台湾の会社Terasicは、アルテラのFPGAベースのボードを幅広く提供しており、トレーニング目的で購入した一部のボードは割引価格(アカデミック価格)で購入できます。

|  |  | |

|---|---|---|---|

| 料金 | DE0-Nano | DE0-CV | DE1-SoC |

| FPGA | EP4CE22 | 5CEBA4F23 | 5CSEMA5F31 |

| 家族 | サイクロンIV | サイクロンv | Cyclone V SoC |

| LEの数 | 22K | 49K | 85K |

| メモリ、kbps | 594 | 3080 | 4450 |

| 価格 | 79ドル | 150ドル | 249ドル |

| アカデミック価格 | 61ドル | 99ドル | 175ドル |

料金Mars rover3

TaganrogのInpro Plus LLCは、アルテラFPGAデバイスの開発に特化した興味深いサイトmarsohod.orgを維持しています。 このサイトでは、MIPSfpgaに非常に適したMars rover3ボードを購入できます。

Mars rover3ボードには、1600 Kbpsのメモリと50,000 LEのMAX10 FPGAが搭載されており、ボードの価格は8,000ルーブルです。

IPブロックをオープンコアに接続します

プロセッサコア内部で何が起こっているかを見ることが提案されているラボは、非常に有用で有益です。 ただし、MIPSの実際のプロセッサコアに基づいてシステムオンチップを組み立てることは、私にとってより興味深いことです。 これは、多くの周辺機器によってプロセッサコアに接続する必要があります。 ボタンを押してLEDを見てプロセッサと対話することは確かに良いことですが、もっと便利なインターフェイスが欲しいです。 ほぼすべての最新の組み込みシステムは技術的な目的でUARTインターフェースを使用しているため、mipsfpga-plusにUARTを追加することにしました。

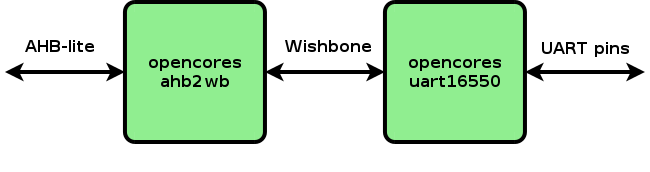

UARTを実装するIPブロックをゼロから書くことは私の目標ではなかったので、すぐに使えるものを使用することにしました。 opencores.orgが最も有名な無料のIPブロックサイトであることは周知の事実です。 そしてもちろん、興味のあるIPブロックがありました。 しかし問題は、無料のIPブロックの場合、標準バスがWishboneであり、AHB-Lite MIPSfpgaバスと互換性がないことです。

私は、opencores.orgにある「アダプター」AHB-Wishboneを介してUART IPブロックを接続しようとしました。 私はそのような接続に頼っていました:

実際には、予想どおりアダプターが機能しなかったことが判明したため、AHB-LiteバスをサポートするためにUART IPブロックのインターフェイス部分を簡単に変更できることがわかりました。

一部のソフトウェアはUART IPブロックで動作するはずなので、nbox nanomonitorをbareboxブートローダーから借りました。 nmonはUARTを介してユーザーと対話し、基本的な機能のみを備えています。アドレスでワードを記録/印刷したり、制御をアドレスに転送したりできます。

ただし、nmonはRAM(sic!)を必要としません。その動作のために必要なメモリは1200バイト未満で、メモリ内のどのアドレスからでも動作します。

サイズが小さいため、合成中にnmonをブートRAMにすぐに配置できます。 そのため、リセット信号を削除した直後に、nmonプロンプトがUARTインターフェイスに発行され、ユーザーはnmonを使用してプログラムをダウンロードして実行するか、プロセッサアドレス空間で手動で書き込み/読み取りを行うことができます。これは、ユーザーIPブロックの初期デバッグに役立ちます。 典型的なnmonセッション:

別のIPブロックをAHB-Liteに接続するには、デコーダーブロックを手動で編集する必要がありました。 最後に、接続されたUARTユニットを持つmipsfpga-plus構造体は次のようになります。

UART IPブロックのopencoresからmipsfpga-plusへの接続を示す最終プロジェクトは、myMIPSfpgaと呼ばれていました。 myMIPSfpgaは、Terasic DE0-Nano、DE0-CV、DE1-SoCボード、およびMars rover3ボードで動作します。

myMIPSfpgaプロジェクトはgithub: github.com/MIPSfpga/myMIPSfpgaで公開されています。

フリーソフトウェアの使用

アルテラは、独自のQuartusソフトウェアを使用してFPGAのビットストリームを生成する必要がありますが(これについては何もする必要はありません)、MIPSfpgaを使用する他の多くのタスクについては、自由に配布できるソフトウェアで取得できます。

MIPSでプログラムをコンパイルするには、gccおよびbinutilsソフトウェアを使用します(事前に構築されたツールチェーンSourcery CodeBench Lite 2015.05-18を使用するか、 crosstool-ngを使用して独自のツールをビルドできます)。

EJTAGでMIPSプロセッサを使用するには、openocdおよびgdbソフトウェアが使用されます。 openocdは、ビットストリームをFPGAにロードするためにも使用できます。

Icarus VerilogはmyMIPSfpgaのモデリングに非常に適しており、シミュレーション結果のタイミング図はGtkWaveの使用を検討するのに非常に便利です。

myMIPSfpga:FPGAリソースの使用

セミナーの参加者は、FPGAリソースの使用率インジケータとmyMIPSfpgaのFmax値について質問しました。 以下に、得られたスロー1200mV 85CモデルFmaxサマリーのMHz単位の値を示します。QuartusIIソフトウェアのさまざまなバージョンの値を示します。

| 料金 | FPGA | Quartus 13.1.4 | Quartus 15.0.2 |

|---|---|---|---|

| DE0-Nano | EP4CE22F17C6 | 31.66 | 31.22 |

| DE0-CV | 5CEBA4F23C7 | 31.24 | 34.06 |

| DE1-SoC | 5CSEMA5F31C6 | 28.24 | 37.17 |

| 火星探査機3 | 10M50SAE144C8GES | --- | 06/27 |

しかし、異なるFPGAのリソースの使用の指標:

| 特徴 | Quartus 13.1.4 | Quartus 15.0.2 |

|---|---|---|

| EP4CE22F17C6 | ||

| トータルロジックエレメント | 15.342 / 22.320(69%) | 15,660 / 22,320(70%) |

| 合計組み合わせ機能 | 14,161 / 22,320(63%) | 14,161 / 22,320(63%) |

| 専用論理レジスタ | 7.665 / 22.320(34%) | 7.665 / 22.320(34%) |

| 総レジスタ | 7665 | 7665 |

| 総メモリビット | 95.872 / 608.256(16%) | 95.872 / 608.256(16%) |

| 5CEBA4F23C7 | ||

| ロジック使用率(ALMで) | 7.283 / 18.480(39%) | 6.972 / 18.480(38%) |

| 総レジスタ | 7976 | 8127 |

| 合計ブロックメモリビット | 95.872 / 3,153,920(3%) | 95.872 / 3,153,920(3%) |

| 5CSEMA5F31C6 | ||

| ロジック使用率(ALMで) | 7.264 / 32.070(23%) | 6.978 / 32.070(22%) |

| 総レジスタ | 7951 | 8104 |

| 合計ブロックメモリビット | 95,616 / 4,065,280(2%) | 95,616 / 4,065,280(2%) |

| 10M50SAE144C8GES | ||

| トータルロジックエレメント | 37.206 / 49.760(75%) | |

| 合計組み合わせ機能 | 30,763 / 49,760(62%) | |

| 専用論理レジスタ | 25,165 / 49,760(51%) | |

| 総レジスタ | 25165 | |

| 総メモリビット | 78,464 / 1,677,312(5%) |

注:Quartus 13.1.4ソフトウェアはMAX10 FPGAをサポートしていません。

MIPSfpgaをOpencoreのIPブロックで使用する方法

opencores.orgのIPブロックを便利に使用するために、補助ツールが作成されました。

- fusesoc-個別のIPブロックからシステムオンチップのアセンブリを制御するためのツール。

- wb_intercon-ウィッシュボーンスイッチジェネレーター。

fusesocでは、高レベルの記述を使用してシステムオンチップを生成できます。一方、fusesocは、Verilogでソースコードを生成するだけでなく、CAD AlteraまたはXilinxの構成ファイルも生成します。

wb_interconを使用すると、VerilogでWishboneスイッチのコードを生成できます。 Wishboneポートとスイッチングルールのパラメーターを含む構成ファイルが入力として使用されます。

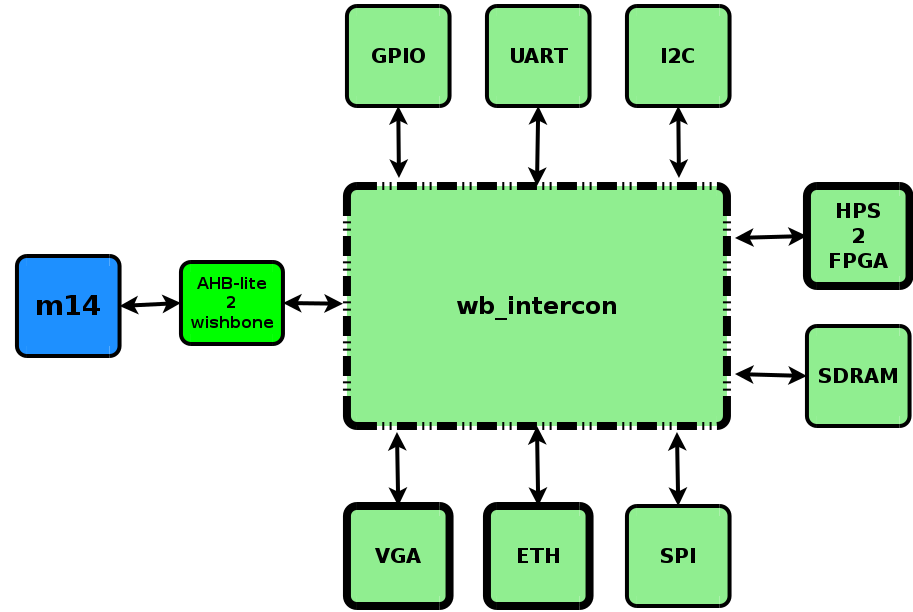

UARTをWishboneバスでmipsfpga-plusに接続することで得られた経験から、プロセッサコア自体がすぐにWishboneに接続されている場合、opencores.orgおよびMIPSfpgaのコアからシステムオンチップを組み立てるときの問題は最小限になると結論付けることができます。

AHB-LiteとWishboneの間に通常のアダプターを作成できたとします。 次に、システムオンチップは次のようになります。

図では、GPIO、UART、I2C、VGA、ETH、SPI、SDRAM5、HPC2FPGAブロックはopencores.orgからの実際のIPブロックであり、生成されたWishboneスイッチを使用してマイクロプロセッサコアに接続します。

注:もちろん、AHB-Lite-in-Wishboneアダプターでは追加の遅延が発生します。 MIPSfpgaにWishboneサポートが組み込まれていると、パフォーマンスが向上します。 さらに、OpenRISCコアの例に従って、コマンドおよびデータ用の個々のWishboneバスを導出できます。

あとがき

MIPSfpgaの経験から、FPGAベースのシステムオンチップ設計の初期開発は複雑で費用のかかるものではなく、多くの準備が必要であることが示唆されています。 FPGA、無料のCAD、自由に配布されるツールとマニュアル(特にmarsohod.orgのサイトに注目)を備えた利用可能なボードの可用性により、自宅でもFPGAの設計をマスターできます。

謝辞

著者は、イマジネーションの従業員であるRobert OwenとYuri Panchulに、MIPSfpgaと連携する機会を与えてくれたことに感謝します。

Nikolai Kovachおよびmarsohod.orgのサイト作成者であるMars rover3料金、Terasic DE1-SoC料金についてはETF会社、DE0-Nano料金についてはAlexei Zhukovに感謝します。

CAD Quartus IIの開発を支援するために、著者はNIISI RASのスタッフ、Sergey Aryashev、Andrey Shcherbakov、Alexander KornilenkoおよびAndrey Arakelovに感謝します。

著者は、将来MIPSfpgaライセンスが改訂され、このプロセッサコアがマイクロプロセッサのアーキテクチャに関心のあるすべての人に利用可能になることを望んでいます。