みなさんこんにちは!

これは、トピック「FPGAでのデジタルフィルタリング」に関する2番目の出版物です。 2番目の部分は、FPGAでのFIRフィルタの実用的な実装に専念します。 素材を準備する過程で、前例のないサイズに膨らむことに気づきましたが、いくつかの部分に分けたくありませんでした。 したがって、FIRフィルターの理論と合成の微妙な点はすべて1つの記事にまとめられ、相互に関連するセクションに分けられます。 特に理論的な部分からレビューを開始します。フィルター係数の計算の機能と方法について説明します。 MATLAB、CoreGENERATOR、Vivado HLSなど、さまざまな環境でのFIRフィルターの作成について詳しく検討します。 猫に興味がある人は誰でも聞いてください。

パート2. FIRフィルター

理論

FIRフィルターの簡単な実装例を考えてみましょう。 ご存知のように、フィルターには2つの大きなクラスがあります- 無限インパルス応答を持つ IIRと、 有限インパルス応答を持つFIRです。 2番目のタイプ、FIRフィルター(Eng。FIR-「有限インパルス応答」)について説明します。 FIRフィルターは線形デジタルフィルターであり、その主な特徴は、そのインパルス応答の限られた時間です。つまり、ある時点からゼロに等しくなります。 原則として、ほとんどのFIRフィルターはフィードバックなしで実行されるため、ほとんどすべてのFIRフィルターは非再帰的です。

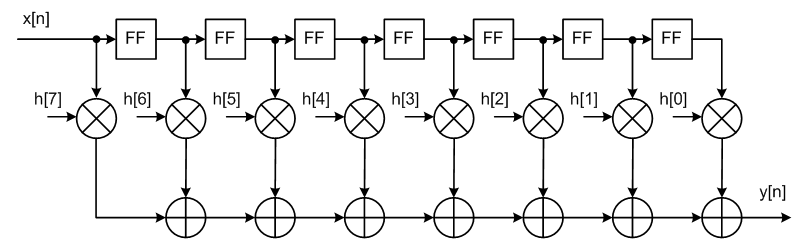

これは、FFPフィルターの実装が一般的な形式、特にFPGAでどのように見えるかです。

すべてのFIRフィルターは、次の方程式で記述されます。

ここで、 y(n)は出力信号(入力の現在および過去の値の関数)、 x(n)は入力アクション、 h(k)はインパルス応答係数、 Nはフィルター長(フィルター係数の数)、 H(z)はフィルターの伝達特性。

FIRフィルターの秘密は何ですか?

FIRフィルターの最も重要な機能は、正確な線形位相応答を取得できることです。 読者には自然な質問があります-「なぜこれが必要なのですか?」。 この瞬間について詳しく見ていきましょう。 信号は、フィルターを通過するときにさまざまな変換を受けます。 特に、信号の振幅と位相は、フィルターの周波数応答(振幅、周波数応答、位相、位相応答)に応じて変化します。 多周波信号の場合、処理ユニットを通過するときに信号の位相が歪むことは容認できません。 さらに、通過帯域の周波数応答がほぼ一定であれば、それは難しくありません。その場合、周波数応答に問題があります。 位相歪みを評価するには、位相および群遅延の概念を導入すると便利です。

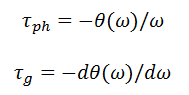

位相遅延は、信号の各周波数成分の遅延量です。 位相角を周波数で割ったものとして定義されます。 群遅延は、複数周波数信号全体の平均時間遅延です。 周波数の位相の導関数として定義されます。 数学的に位相および群遅延は次のように記録されます。

群遅延の式から、位相応答フィルターの線形性が明らかになります。 位相応答が線形の場合、導関数を取得した後の群遅延は一定です。つまり、すべての周波数成分に対して一定です。 非線形の位相応答を備えたフィルターが信号の位相を歪めることは論理的です。

したがって、位相特性の線形性は、FIRフィルターの最も重要な機能の1つです。 このクラスのフィルターの研究について説明します。

線形位相応答を備えたFIRフィルター

位相応答の線形性を確保するには、フィルターのインパルス応答(または係数)の対称条件を満たす必要があります。 簡単に言えば、線形位相応答を持つFIRフィルターは対称です。 フィルター次数Nのパリティと対称のタイプ(正または負)が異なる4種類のフィルターがあります。 例えば、負の対称性を持つフィルターの場合、90 °の位相シフトが得られます。 このようなフィルターは、微分器とヒルベルト変換の設計に使用されます。 FIRフィルターのインパルス応答のエンベロープは、フィルターの種類(ローパスフィルター、ハイパスフィルター、PF、RF、微分器) に関係なく、法則〜sin(x)/ xに従って構築されます。 実際的な問題を解決するために、多くの場合、どのタイプのフィルターが選択されるかを考える必要はありません。 係数の対称条件の証明はしませんが、好奇心の強い読者であれば、さまざまな文献でそれを見つけることができます。

FIRフィルターの設計

「FIRフィルターの計算」では、ほとんどの場合、周波数応答の値による係数の検索を意味します。 学術的な興味を除いて、逆問題が解決されるケースを思い出せません。

新しいデジタルFIRフィルターを作成するとき、エンジニアは開発の特定の段階を経ます*:

- フィルター仕様 。 フィルタータイプ(ローパスフィルター、ハイパスフィルター、通過帯域、ノッチ)、N係数の数、必要な周波数応答、減衰帯域と通過帯域の非線形性の許容範囲などが設定されます。

- 係数の計算 。 利用可能な方法と手段により、前段落の仕様を満たすフィルター係数が計算されます。

- 有限容量の結果の分析 。 この段階で、フィルター係数、中間データ、および出力データに対する量子化効果の影響が推定されます。

- 実装 。 この段階では、フィルターはアクセス可能なプログラミング言語で開発されるか、既成のIPコアを作成することでフィルターが実装されます。

*-開発の段階は多少異なる場合がありますが、本質は常に同じです。

フィルター仕様

この段階で、エンジニアは妥協ソリューションを検索して、目的のパラメーターで目的のフィルターを実装します。 それらは少数ですが、多くの場合、1つのパラメーターを犠牲にして他の値に必要な値を達成する必要があります。

- Apass-帯域幅の不均一性、

- Astop-抑制帯域の減衰レベル、

- Fpass-カットオフ周波数帯域幅、

- Fstop-カットオフ周波数カットオフ周波数、

- Nはフィルター次数(フィルター係数の数)です。

実際には、ApassおよびAstopパラメーターはデシベル(dB)で指定され、FpassとFstopの間の距離はフィルター遷移帯域幅を表します。 Apassの値は可能な限り小さく、Apassは可能な限り大きくし、Fpass / Fstop比は理想的には統一する傾向があります(完全に長方形の周波数応答)。 フィルター仕様に入力された係数の数は無駄ではありません。 以下に示すように、フィルターの周波数特性とFPGAリソースの占有量は、フィルターの次数Nと係数のビット深度に依存します。

フィルター係数の計算

このテーマについては、いくつかの書籍や科学記事を書くことができますが、この記事の枠組みのすべての方法を詳細に検討することはしません。 フィルター係数を計算する方法は多数あります。ウィンドウ関数による重み付け方法、周波数サンプリング方法、Remezアルゴリズムを使用したさまざまな最適な方法(チェビシェフによる)などです。 すべての方法は、その特性が独特であり、特定の結果をもたらします。 ウィンドウ重み付け法の場合、 ギブス効果は負の兆候になり、関数の計算されたポイント間のフィルターの周波数応答に不均一性と外れ値が導入されます。 無限に対処できますが、実際には、通過帯域と抑制帯域の不均一性に許容範囲が導入されます。

多くのフィルターの係数を計算する主な方法は、修正されたRemezアルゴリズムであるParks-McClellanアルゴリズムです。 本質的には、チェビシェフフィルター特性を使用して最適な値を見つけるための間接反復法です。 この方法の特徴は、インパルス応答のチェビシェフ近似により、減衰帯域と伝送帯域の誤差を最小限に抑えることです。 係数の数が多いほど、周波数応答の不均一性が少なくなり、より長方形になることは非常に論理的です。

最終結果は方法の選択に依存しますが、パスバンドでの放射を最小限に抑え、周波数応答の「角形性」を高めるという、すべて同じ目標に到達します。

有限容量の結果の分析

係数のビット深度は、周波数応答のタイプが依存する主な要因です。 最新のFPGAでは、係数のビット深度は任意に選択できますが、妥当な数値は16〜27ビットです。 フィルター次数が高い場合、放電グリッドの広いダイナミックレンジを提供する必要がしばしばありますが、これができない場合、遅かれ早かれ、量子化誤差が現れ始めます。 係数のビット深度が制限されているため、周波数応答が変更され、場合によっては歪みが大きくなり、許容可能な結果を得るために周波数仕様からパラメーターを犠牲にする必要があります。 いずれにせよ、係数の表現のビット深度は、Astopの最大可能減衰に直接影響します。 したがって、制限された係数の放電グリッドを使用すると、巨大なフィルター次数でも所望の抑制を達成できない場合があります!

中間データのビット深度と算術オーバーフローは、周波数応答のタイプとフィルター出力での結果も依存する要因です。 多くのFPGAでは、DSPユニットに大容量のバッテリーを使用することで問題を解決しています。 たとえば、ザイリンクス6および7シリーズFPGAは、DSP48E1セルで48ビットのバッテリーと乗算器を使用します。 次の図は、FIRフィルターを実装する標準ブロックDSP48E1を示しています。

最新のFPGAの組み込みDSPブロックは、DSPタスクを最も便利に実行できるように設計されています。 まず、FIRフィルターの実装用。

実装

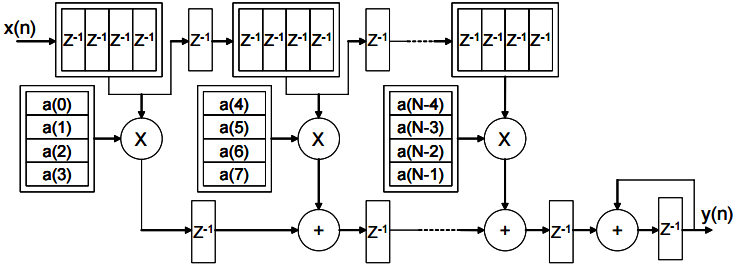

最も単純なフィルターを実装するために必要な論理演算はほとんどありません。 FIRフィルターを実装するメインノードは、DSP FPGAブロックです。 このブロックでは、すべての数学演算が行われます-入力サンプルとフィルター係数の乗算、入力信号の遅延、データの合計。 最新のDSPノードには予備加算器が含まれているため、対称THEMを使用したフィルターの加算操作もこのノード内で実行できます。 DSPブロックに加えて、フィルターには係数(分散またはブロック)を保存するためのメモリが必要です。 フィルターは他のものを使用しません。 この図は、乗算器、バッテリー、遅延ライン、および係数を保存するためのメモリを使用したFIRフィルターの実装を示しています。

MATLABでのフィルター計算

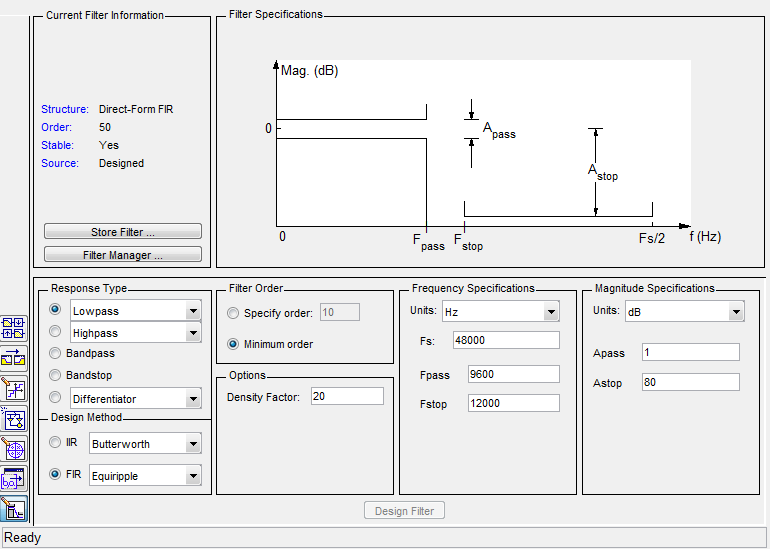

フィルタを計算し、その係数を検索できる多くのアプリケーションがあります。 たとえば、MATLABのLABView、Scope FIR、FDAToolまたはOctaveの無料のアナログ。 おそらく、FIRフィルターを計算する最も便利な手段はMATLABです。 フィルターを作成および分析するツールを実行するには、環境のコマンドウィンドウでキーワードfdatoolを入力します。 このようなウィンドウが表示されます(MATLABのバージョンによっては、外観が少し異なる場合があります)。

主なパラメーターは、 フィルター仕様ウィンドウで設定します。 フィルタ設定によっては、メインウィンドウ領域にいくつかのパラメータが表示される場合があります。

- フィルター次数 -フィルター次数を定義します(最小またはユーザー定義)**。

- 周波数仕様 -フィルター特性の周波数パラメーターを定義します。

- 振幅仕様 -フィルター特性の振幅パラメーターを定義します。

- 密度係数 -等リップルタイプの場合、フィルターを近似するポイントのグリッドを設定します。

**-FDAToolでは、フィルター次数Nは指定された次数より1つ大きくなります(N = 7に設定すると、ユーティリティは8つの係数を計算します)!!!

応答タイプ - 応答タイプをフィルタします。 このフィールドでは、たとえば次のような自然界に存在するフィルターが選択されます。

- ローパス -ローパスフィルター、

- レイズドコサイン -レイズドコサインフィルター、

- ハイパス - ハイパスフィルター、

- バンドパス -バンドパスフィルター、

- バンドストップ -ノッチ(弾幕)フィルター、

- 微分器 -微分器、

- ナイキスト - ナイキストフィルター、

- マルチバンド -マルチバンドフィルター、

- ヒルベルト変換器 -ヒルベルト変換器、

- 任意の大きさ -任意の周波数応答を持つフィルター。

さらに、フィルターのタイプに応じて、分析ツールはフィルターのタイプの制限を示し、Nの正しい値を入力するように提案します。

設計法 -フィルター設計法とそのタイプ(IIRまたはFIR)を選択します。 IIRフィルターでは、次のオプションを使用できます。

- バターワース - バターワースフィルター、

- チェビシェフタイプI、II-チェビシェフフィルター、

- 楕円 -楕円フィルター、

- 最大フラット -通過帯域で最もフラットな応答を持つフィルター、

*** FIRフィルターのオプションが利用可能です:

- 等リップル -均一に脈動する周波数応答を持つフィルター、

- 最小二乗 -最小二乗フィルター、

- ウィンドウ -さまざまな機能を持つウィンドウの重み付きフィルター****、

- Complex Equiripple-均一に脈動する周波数応答を持つ複雑なフィルター、

- 最大フラット -通過帯域で最もフラットな応答を持つフィルター、

***-タイプEquirippleおよびWindowのフィルターは、実用上の最大の関心事です。

****-このオプションを選択すると、ウィンドウ機能とそのパラメーターへのアクセスパネルが表示されます。

等リップル法の場合、修正されたRemezアルゴリズムを使用して、最も単純なFIRフィルター計算が実行されます。 ユーザーは、フィルターの仕様からパラメーターを設定し、すぐに結果を確認します。 満足のいく結果が得られない場合は、いつでも1つ以上のフィルターパラメーターを変更して、異なる周波数応答を取得できます。 計算は、必要な特性が得られるまで実行されます。 タスクの値を達成できなかった場合、遅かれ早かれ、仕様から1つまたは別の値を犠牲にするか、Nフィルターの次数を大幅に増やす必要があります。

Windowメソッドのウィンドウ関数には、ユーザー定義のウィンドウ関数(ユーザー定義)まで、 Bartlett、Blackman、Blackman-Harris、Chebyshev、Flat Top、Gaussian、Hamming、Hann、Kaiser、Rectangleなどのいくつかのオプションがあります。 これらの関数はすべて独自の特性を持ち、FIRフィルターの周波数応答のさまざまなパラメーターを提供できます。 ウィンドウ関数の一部はパラメーターなしで計算され、フィルターの一部はフィルターの周波数応答に影響する特定のパラメーターを介して指定されます。

私の意見では、表示されるすべてのウィンドウ関数の中で、 Kaiserウィンドウが最も便利です。 周波数応答を作成するには、1つのベータパラメーターのみが必要です。これは、減衰帯域の抑制レベルと周波数応答の角形性に影響します。

FDAToolには、メインワークスペースの左下に追加のタブがあり、フィルターのタイプ(デシメータまたはインターポレーター)、Simulinkに挿入されるモデルの名前、係数と入力データのタイプと解像度などを指定できます。 実用的な目的のために、最も基本的なタブは、 デザインフィルター -フィルターがその中で計算され、 量子化パラメーター -このタブでは、データのタイプと幅が設定されます。

上部パネルには、フィルターの周波数応答と位相応答、グループと位相遅延、パルスと遷移特性、フィルターの零点と極のマップ、計算された係数などを確認できるボタンがあります。

FDAToolワークスペースのスクリーンショット

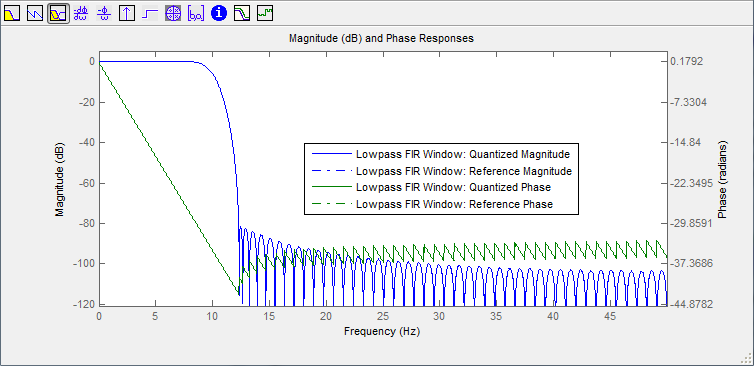

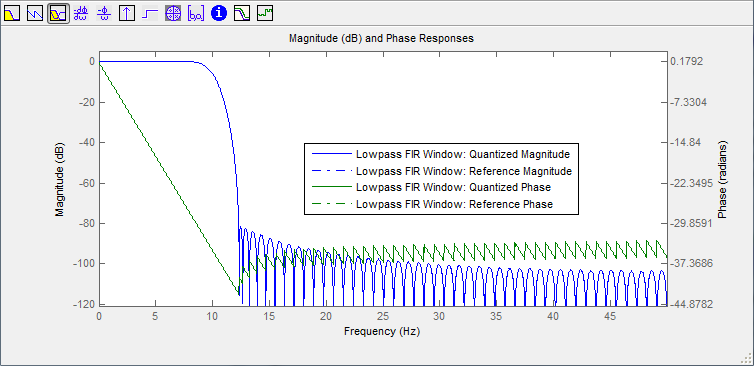

フィルターの周波数応答と位相応答のグラフ:

インパルス応答グラフのフィルター:

零点と極のグラフチャート:

インパルス応答グラフのフィルター:

零点と極のグラフチャート:

これに加えて、FDAToolではフィルターモデルと計算された係数をインポートおよびエクスポートできます。 たとえば、フィルターを計算し、そのモデルを標準プリミティブのモデルとしてSimulinkに送信できます。 係数を計算して、たとえば* .h(ヘッダー)という拡張子を持つファイルとして別のファイルに保存できます。

*フィルタ係数を含む.Hヘッダーファイル

/* * Discrete-Time FIR Filter (real) * ------------------------------- * Filter Structure : Direct-Form FIR * Filter Length : 128 * Stable : Yes * Linear Phase : Yes (Type 2) * Arithmetic : fixed * Numerator : s16,15 -> [-1 1) * Round Mode : convergent */ /* General type conversion for MATLAB generated C-code */ #include "tmwtypes.h" const int BL = 128; const int16_T B[128] = { -18, 0, 19, 39, 58, 75, 88, 97, 100, 96, 85, 68, 44, 16, -16, -50, -83, -113, -139, -157, -166, -164, -152, -128, -94, -51, 0, 55, 111, 164, 211, 248, 272, 280, 269, 240, 192, 126, 45, -47, -146, -245, -339, -421, -483, -521, -528, -501, -434, -329, -183, 0, 217, 462, 728, 1006, 1288, 1564, 1823, 2056, 2254, 2409, 2517, 2571, 2571, 2517, 2409, 2254, 2056, 1823, 1564, 1288, 1006, 728, 462, 217, 0, -183, -329, -434, -501, -528, -521, -483, -421, -339, -245, -146, -47, 45, 126, 192, 240, 269, 280, 272, 248, 211, 164, 111, 55, 0, -51, -94, -128, -152, -164, -166, -157, -139, -113, -83, -50, -16, 16, 44, 68, 85, 96, 100, 97, 88, 75, 58, 39, 19, 0, -18 };

さらに、ザイリンクス用の特別な形式で* .COE係数ファイルを作成できます。 これを行うには、固定小数点を持つ係数のタイプを選択し、ビット深度を設定します。 次に、[ ターゲット ] -> [ザイリンクス係数(.COE)ファイル ]をクリックします。その結果、ファイルの内容(グローバル設定とHEX形式の係数)がメインMATLABウィンドウに表示されます。

例* .coeファイル

; XILINX CORE Generator(tm)Distributed Arithmetic FIR filter coefficient (.COE) File ; Generated by MATLAB(R) 8.3 and the DSP System Toolbox 8.6. ; ; Generated on: 06-Dec-2015 15:35:35 ; Radix = 16; Coefficient_Width = 18; CoefData = 3ffeb, 00018, 00049, 00067, 0005f, 00029, 3ffd2, 3ff79, 3ff46, 3ff59, ...

単一のインパルスが入力に適用されると、フィルターのインパルス応答のみが出力で形成されることがわかります(Simulinkのグラフ)。

ザイリンクスFIRコンパイラ

CICフィルターの場合と同様に、ザイリンクスからFIRフィルターを作成する方法について詳しく説明します。 説明には、データシートからの翻訳だけでなく、個人的な経験や同僚の経験からのコメントや推奨事項が含まれていることに注意してください。

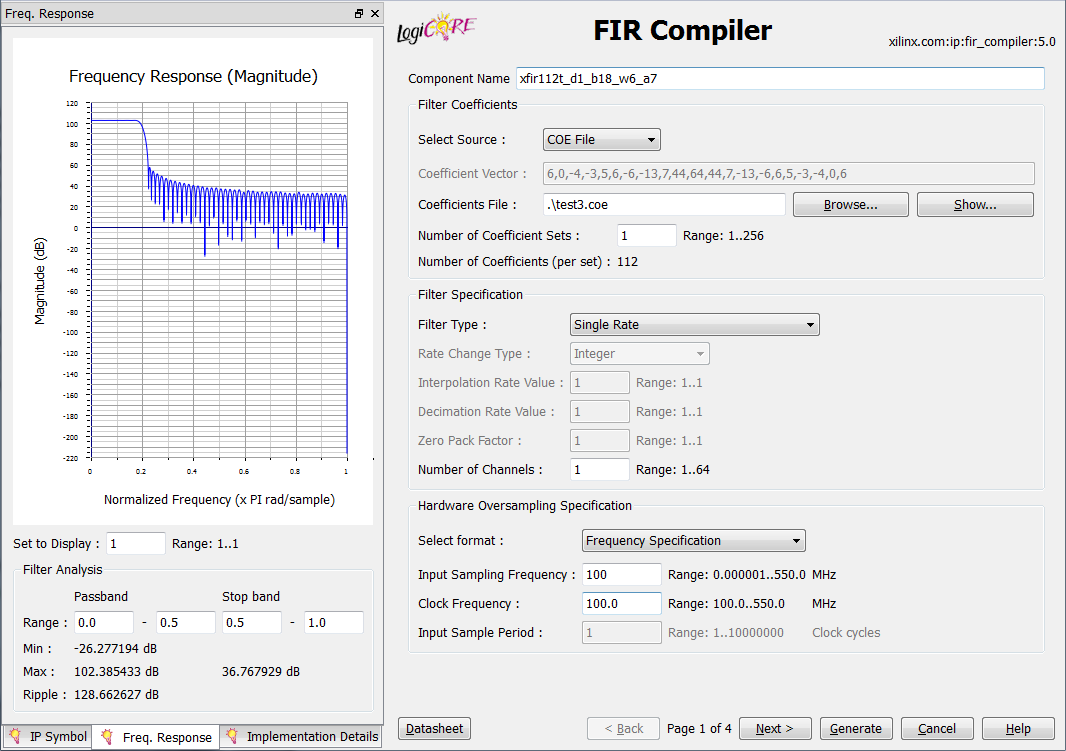

FIRコンパイラ-タブ1:

コンポーネント名 - コンポーネントの名前 (ラテン文字a〜z、数字0〜9、および記号「_」を使用)。

メインのフィルターパラメーターが暗号化されている意味のある名前を使用することをお勧めします。 たとえば、 xfir128t_d1_b18_4c_w6_a7はザイリンクス向けに作成されたフィルターで、N = 128(タップ)、デシメーションは使用されず、ビット深度は18、4チャネル、ベータ= 6のカイザーウィンドウ関数が適用され、FPGAチップはArtix-7です。

フィルター係数:

- ソースの選択 -係数のソースを選択します( ベクトル -手動で指定されたベクトルまたはCOEファイル -係数のセットを持つファイル)。 オーバーロードされた* .COEファイルを使用することをお勧めします。

- 係数ベクトル -手動で設定された係数のベクトル 。

- 係数ファイル -ファイルから読み取られた係数のベクトル。

- 係数セットの数-係数を処理するために実際に使用されるDSPブロックの数。 係数の数は、指定された値で完全に除算する必要があります。 サンプリング周波数に比べて高い周波数で作業する場合に便利なオプションは、FPGAリソースを大幅に節約できます。

- 係数の数(セットごと) -DSPブロックによって同時に処理される係数の数。 フィールドの値は、係数の数と前のパラメーターを読み取るときに自動的に設定されます。

フィルター仕様:

- フィルタータイプ -フィルタータイプ:単純/補間/間引き/多相。

- レート変更タイプ -処理速度の変更。 整数でも分数でもかまいません。

- 補間/間引き率値 -補間/間引き係数。

- ゼロパック係数 -フィルターを補間する場合、パラメーターは係数間に挿入されるゼロの数を決定します。

- チャネル数 -独立したフィルタリングチャネルの数:1〜64。

ハードウェアオーバーサンプリング仕様:これらのパラメーターは、出力サンプルレート、データの処理に必要なクロックサイクル数に影響します。 カーネル内の並列処理のレベルと占有されるリソースの量も、これらのパラメーターに依存します。

- 形式の選択 -フィルターの周波数比を選択します:周波数仕様/サンプル周期。

- 周波数の指定 :ユーザーは、サンプリングレートとデータ処理の頻度を設定します。

- サンプル周期 -クロック仕様:ユーザーは処理周波数とデータのクロック周波数の比率を設定します。

- 入力サンプリング周波数 -*。

- クロック周波数 -フィルター処理周波数:*****。

- 入力サンプリング期間 -入力クロック信号の周波数に対する処理周波数の比率:*****。

*****-範囲は一般設定とサンプリングレートRに依存します。

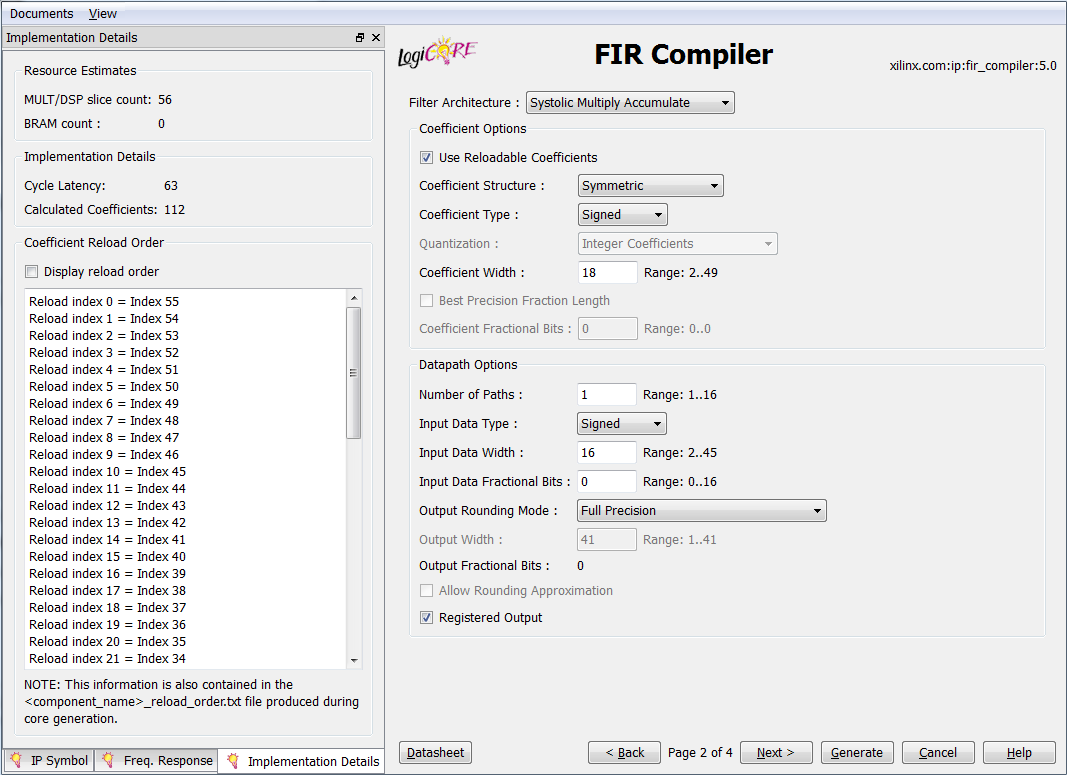

FIRコンパイラ-タブ2:

フィルタアーキテクチャ -実装されたフィルタアーキテクチャを定義します。

- Systolic Multiply Accumulate-累積を伴う収縮期フィルター、

- Transpose Multiply Accumulate-累積可能な調整可能なフィルター、

- 分散演算 -分散FPGAロジックに基づくフィルター。

係数オプション -係数のパラメーター

- リロード可能な係数を使用-オーバーロードされた係数を使用します。 1つのフィルターに過負荷の周波数応答を実装するための便利なオプション。

- 係数構造 -係数構造、5種類:非対称、対称、負対称、ハーフストリップ、ヒルベルト変換あり。 デフォルトでは、FIRコンパイラーは係数のタイプ(推定)自体を決定しようとします。

- 係数タイプ - 係数のタイプ :符号付きまたは符号なし。

- 量子化 -丸め方法を設定します:整数係数、最も近い整数への丸め、または最大ダイナミックレンジ(最大値に対して係数をスケーリングします)。

- 係数の幅 - 係数のビット深度。 このフィールドの値は、フィルターの周波数応答に影響します。これは、対応するウィンドウで確認できます(周波数応答)。

- 最高精度の小数部の長さ -ビットグリッドの全体および小数部に最適な比率を自動的に設定します。

- Coefficient Fractional Bits-ビットグリッド内の係数の小数表現から整数部分を分離する位置を決定します。

データパスオプション -入力オプション

- パスの数-処理する並列チャネルの数を決定します。 DSPコアの数は、このフィールドの値に比例します。 このオプションの場合、フィルター入力はいくつかの独立したデータストリームを受け取りますが、[チャンネル数]パラメーターの場合、データは1つの入力に送られ、順次処理されます。

- 入力データ型 -フィルターの入力でのデータ型(符号付きまたは符号なし)。

- 入力データ幅 - 入力データの幅 。

- 入力データの小数ビット -入力データ表現の小数部分ごとのビット数を決定します。 このフィールドの値は、フィルターの実装に影響しません! (固定小数点数は好きなように表現できます。小数部がある場合とない場合がありますが、結果は同じです)。

- 出力丸めモード -出力データの丸めモード:完全精度、最下位ビットの破棄、整数の切り上げ/切り上げ、偶数/奇数への切り上げ。 多くのタスクでは、このパラメーターを変更する必要はなく、完全精度-完全精度のままにしておくことができます。

- 出力幅 -フィルターの出力データの幅。

- 出力小数ビット - 出力の小数部を決定するビット数。 このフィールドは参考情報であり、フィルターの実装には影響しません。

- 丸め近似を許可 -対称丸めモードモードの場合、このオプションにより、追加のリソースコストなしで丸める際の近似が可能になります(単語の符号ビットの自動決定)。

- Registered Output-アクティブなオプションは、フィルター出力に追加のレジスターを追加して、フィルターのパフォーマンスを向上させます(最大処理周波数)。

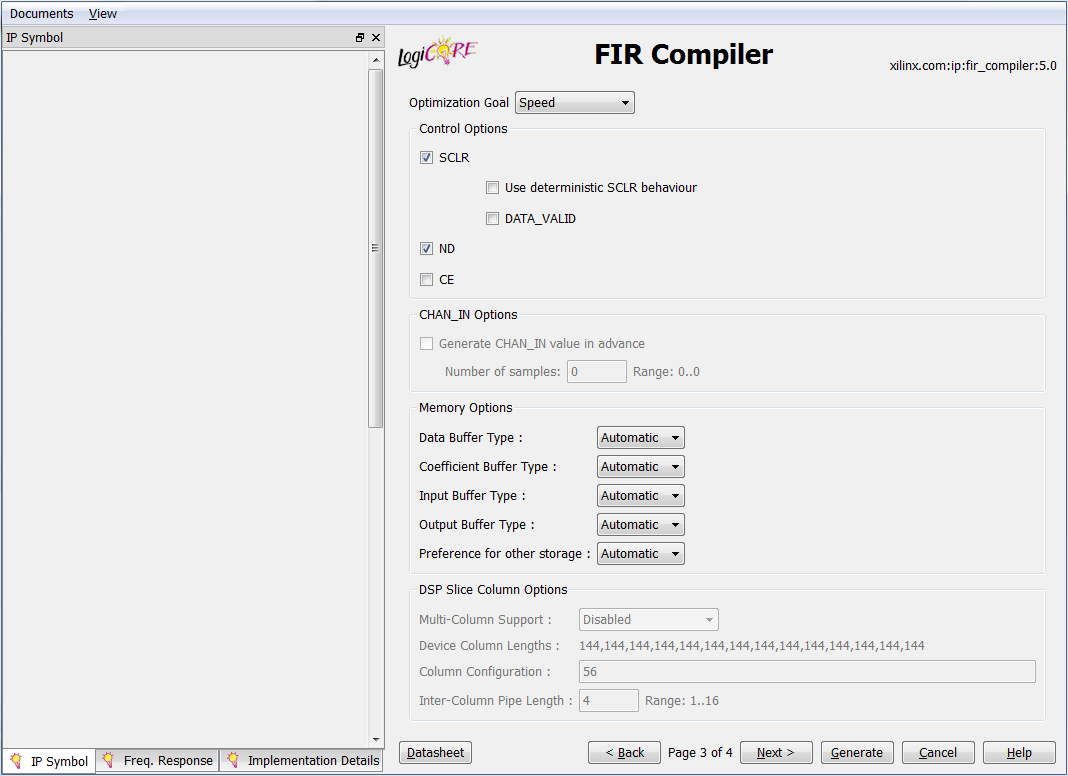

FIR Compiler-タブ3:

最適化の目標 -フィルターを作成するときの最適化の目標を定義します(面積-面積、速度-速度)。 ほとんどの場合、最大速度と最小リソース消費を同時に実現できますが、特定の場合、速度を指定すると、フィルターは論理関数間のクリティカルパスに内部レジスタを最適に配置します。

- SCLR-同期フィルターリセット(入力の論理ユニットがリセットを実行します)。

- 確定的なSCLR動作の使用 -リセットプロセス中の積和フィルターの内部データの動作を定義します。 アクティブオプションを使用すると、リセット信号は内部レジスタ、データメモリ、およびストレージ係数をクリアします。

- ND- 「新しいデータ」、フィルター入力へのデータ入力を決定する入力信号。 RFD信号と一緒に、データのバッチ処理を整理することができます。 通常、NDおよびRFD信号はFIFO制御信号に接続されます。

- CE- 「クロックイネーブル」、フィルタークロックイネーブル信号。 この信号の入力の低レベルでは、新しいデータが到着したかどうかに関係なく、フィルター内部の処理はすべて停止します。

- DATA_VALID-出力データの有効性のシグナル。 このオプションは、マルチチャネルモード(Number of Channels> 1)でのみ役立ちます。

メモリオプション -入力データ、フィルタ係数、中間データ、出力データを保存するメモリのタイプを選択するためのグローバル設定。 分散メモリではなくブロックメモリを選択すると、FPGA論理リソースを何百回も節約できる場合があります。

データ/係数/入力/出力バッファタイプの場合、 自動/ブロック/分散モードが可能です。

他のストレージの設定 -中間データ用のメモリのタイプを定義します。 自動/ブロック/分散モードも利用できます。

DSPスライス列オプション-FPGA列間のDSPブロックの分散の設定を定義します。 たとえば、対称係数を使用する一部のフィルターアーキテクチャでは、Multi-Colomn Supportモードを使用できないため、フィルターの実装の可能性を監視する必要があります。

- デバイス列の長さ -DSPブロックの列の長さを決定します。 フィルター次数の上限と実装されているフィルターの最大数を事前に定義できる便利な情報フィールド。

- 列構成 -列内のDSPブロックの構成と位置を決定します。 このパラメーターは慎重に処理する必要があります。フィルターが複数の列の間で破損すると、大きな遅延が発生する可能性があるため、最大クロック周波数が低下するためです。

- 列間パイプ長 -伝搬遅延の悪影響を除去するために、DSPブロックの列間の追加レジスタの数を決定します。

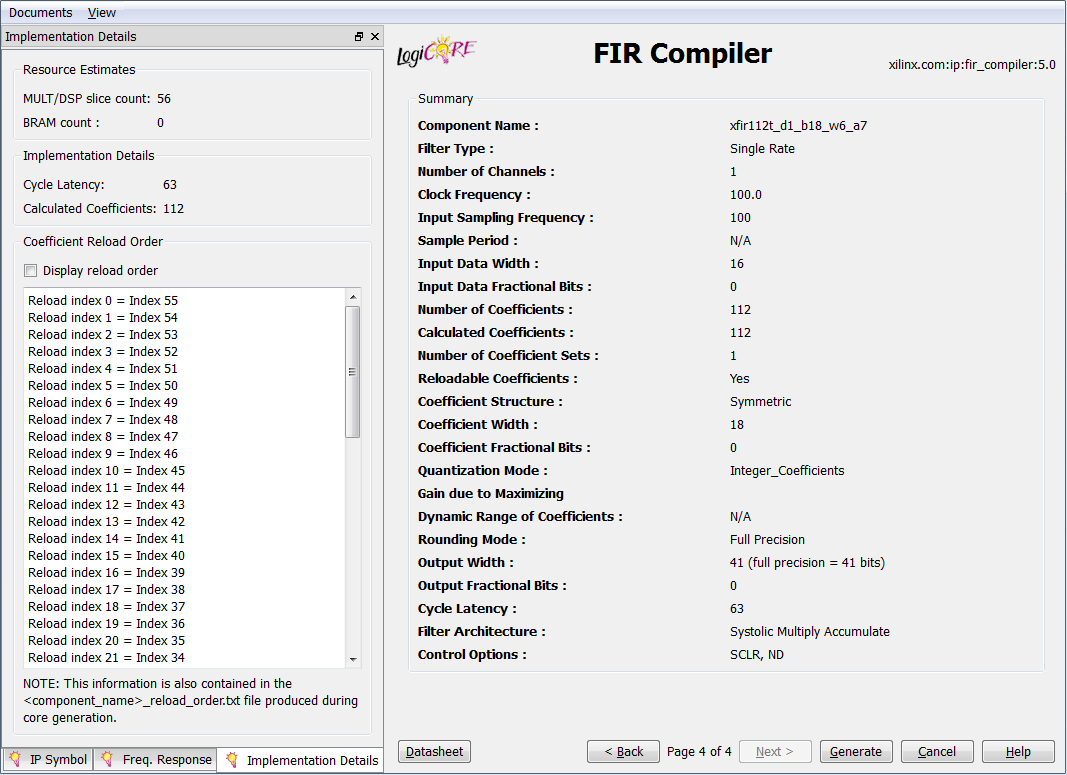

FIR Compiler-タブ4:

要約 -リスト形式のこのタブには、最終フィルター設定(チャネル数、フィルター次数、周波数パラメーター、入力のビット深度、出力および中間データ、係数のビット深度、フィルターの遅延、使用されるDSPブロックの数、制御信号の有無など)が反映されます。

FIR Compilerウィンドウの左側には、3つの便利な追加タブがあります。

- IPシンボルは、アクティブなI / Oポートを備えたIPブロックの概略図です。

- 頻度 response -FIRフィルターの周波数応答。

- 実装の詳細 -DSPおよびRAMBの占有リソースの推定、合計遅延、係数の数、およびそれらのロードの順序。

抽象例

状態

次のパラメーターを持つプライマリ処理のブロードバンドフィルターを計算します。

- Fsサンプリングレート:250 MHz、

- Fpassフィルターのカットオフ周波数:55 MHz

- 角形比:> 0.88(Fpass / Fstop)、

- 帯域幅抑制(Apass):<0.5 dB、

- 減衰抑制(Astop):> 50 dB。

解決策

ステップ1:FPGAリソースの見積もり

このようなフィルターを実装するために使用できる水晶リソースの量を理解する必要があります。 DS180では、チップに240個のDSP48E1ブロックが3列に配置されていることがわかります(これは重要です!)。 TKからTHEMは対称であることがわかっています。つまり、次数Nのフィルターでは、DSP48E1のN / 2ブロックが必要です。 したがって、選択した超小型回路では、特性長N = 240の2つのフィルター、または長さN = 80の6つのフィルターを実装できます。実際の目的では、信号を処理する場合、フィルターの長さは2のべき乗の倍数として選択されます。 たとえば、N = 64、128または256。または、N =(128 + 64)、(32 + 16 + 8)。 この場合、240個のDSPブロックに6個のフィルターを実装する必要があります。 各フィルターに対称性がある場合、係数の長さN <81を使用できます。 フィルターパラメーターを実現するには、N = 80 = 64 + 16の係数で十分であるとします。

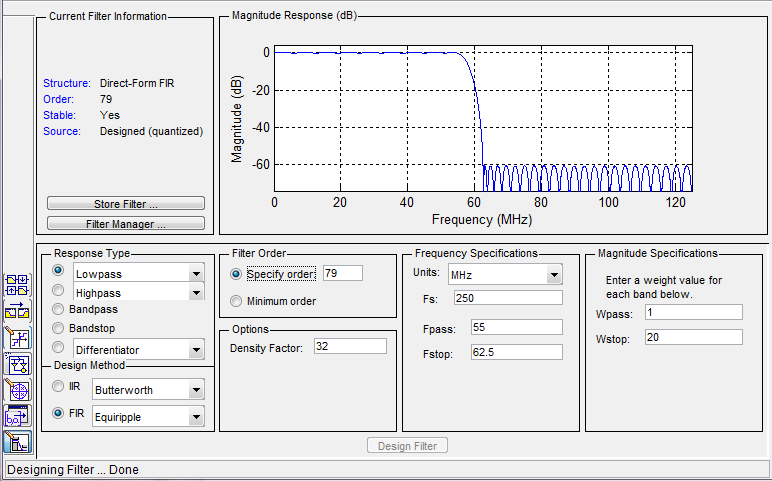

ステップ2:フィルター係数を見つける

FDAToolを実行し、仕様から必要なフィールドにフィルターパラメーターを追加します(次数Nは実際のフィルター次数より1少ない値に設定されていることに注意してください)。 モード1- 等リップル 。 Fpass = 55 MHzのカットオフ周波数と0.85を超える直角度係数の場合、バリア周波数Fstop <62.5 MHzが見つかります。 次の図は、必須パラメーターに応じたフィルターの計算を示しています。

ご覧のとおり、フィルターは上記の要件をすべて満たしています。

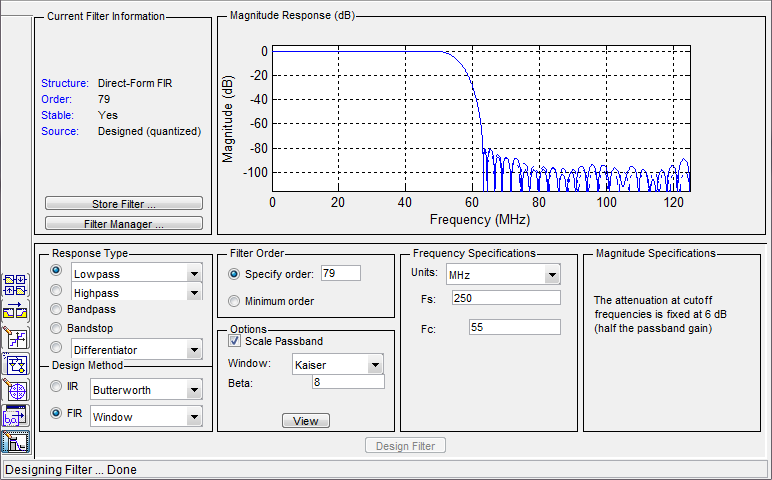

モード2-ウィンドウ 。 突然、プロジェクトを難解な顧客に引き渡す直前に、彼の頭に思いが浮かびました。 「70 dBの抑制が必要です。他の条件はすべて同じです!」 エレメンタルベースが選択され、ボードが配線およびマウントされ、FPGAがインストールされ、プロジェクトは数か月間デバッグされており、リメイクするものを置く方法はありません。 どうする プロジェクトが完了する1週間前に、独自のFIRフィルタを設計しますか? 周波数応答を抑制する他の方法をお探しですか? ボードをやり直し、FPGA fatterをインストールしますか? 非現実的! 主なことはパニックにならないことです。 Equirippleメソッドは保存しなくなりました。 ウィンドウモードWindowに渡します。 私のお気に入りのカイザーウィンドウを選択すると、最高のフィルター特性を実現できます。 たとえば、減衰帯域Astop = 80 dB(パラメーターBeta = 8)で必要な抑制を提供します。 ただし、ウィンドウ方式では、係数のビット深度が不十分であるため、減衰帯域で量子化効果が発生する可能性があることを考慮する必要があります。

次に、既知の方法で、計算した係数を* .COEファイルにアップロードして、さらに作業を進めます。

ステップ3:実装

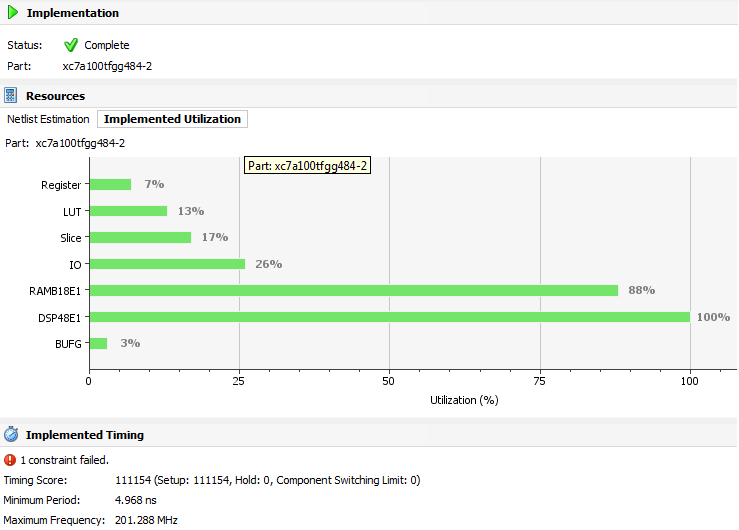

チャネルと係数の数は、FPGAのDSP48E1のリソースを100%占有するように選択されました。 次の図の6チャネルの占有リソースの数:

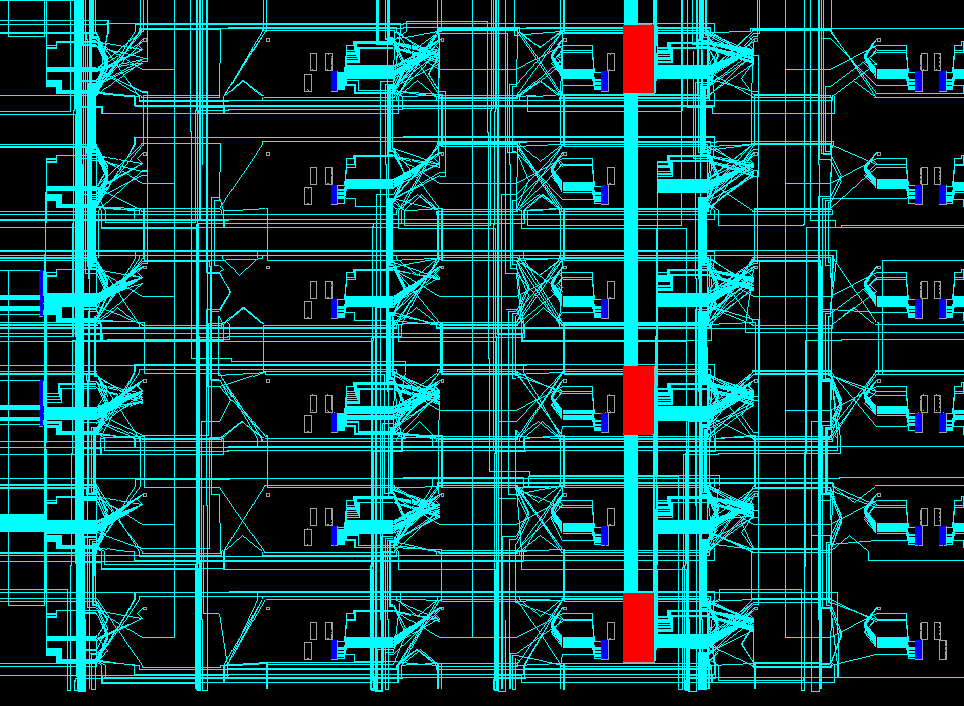

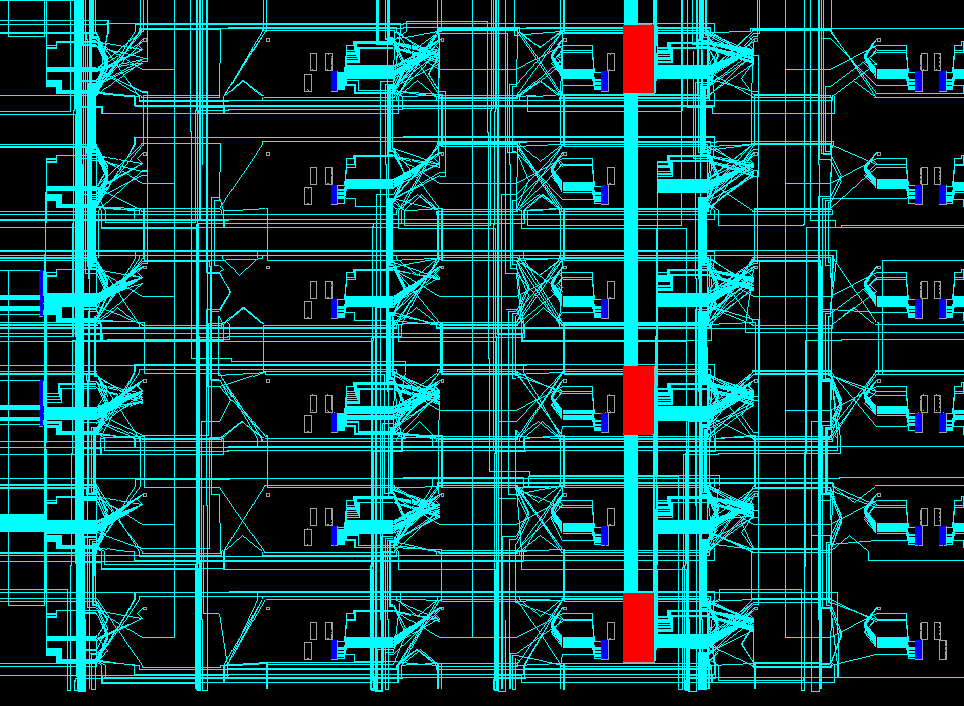

プロジェクトが250 MHzで動作しないことを恐れないでください。 仕組みも。 PlanAheadは安全にプレイすることを好み、実際よりも低い値を示します。 FIRフィルターの6つのチャネルの配線結果。

プロジェクトの配線の美しい図面

FIRフィルターのIPコアの一部の概略図:

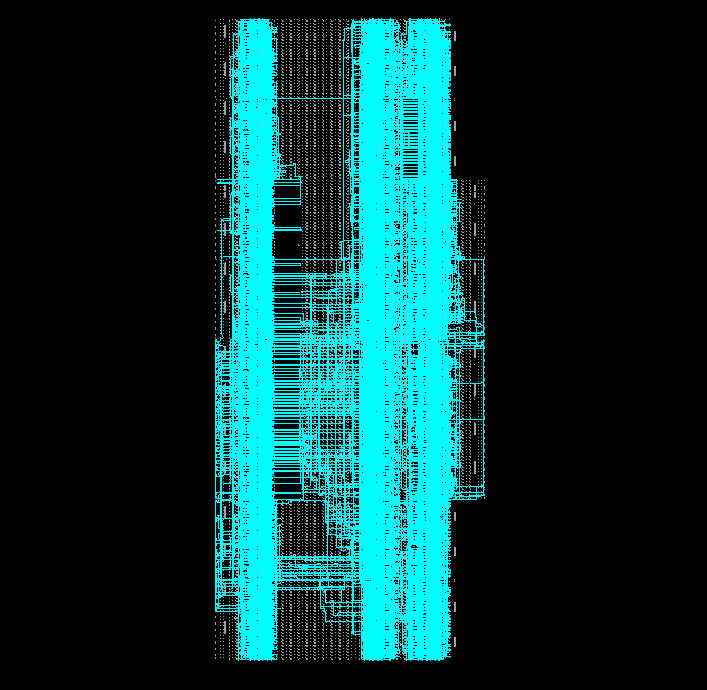

FPGA Editorのボードレイアウト(ズーム下部):

FPGA Editorのボードレイアウト:

FPGA Editorのボードレイアウト(ズーム下部):

FPGA Editorのボードレイアウト:

実用的なヒント

もちろん、Windowへの移行は常に保存されるとは限りません。実際には、開発者の生活を何らかの形で単純化する他の方法がいくつかあります。

- 信号の可能なデシメーションを事前に決定します(信号スペクトルのサンプリング周波数とカットオフ周波数の比によって)。 間引きには安価なCICフィルターを使用します。 間引きの後、使用されるDSPクリスタルブロックの数を減らすことができます。

- FPGAチップのサンプリング周波数と処理周波数の比率を決定します。 処理頻度がサンプリング頻度よりも数倍高い場合、FIRフィルターの実装に必要なリソースの量を何度でも節約できます。

- 分散FPGAロジックにフィルターを実装します(これが可能であり、処理周波数の点で重要でない場合)。 この方法は実装が非常に難しく、フィルターNの大きな次数では安定して機能しません。

- 対称THEMでフィルターを実装するには、最初にDSPブロックの列のサイズとFPGAのこれらの列の数を推定します。 対称THEMで長いフィルターを実装するには、DSPブロックのカスケード接続が必要であり、1列のFPGA内にフィルターを配置する場合、十分なDSPセルがない場合があります。 一方、独立したフィルターチャネルを実装する場合、各列にフィルターが1つしか収まらない場合、列だけでは不十分な場合があります。 特性の長さを短くするか、係数の少ない2つの小さなフィルターを作成する必要があります。

- 最新のFPGAクリスタル(AlteraおよびXilinx)の場合、対称THEMを使用してフィルターを実装する場合、分散ロジックではなくDSPノードで予備加算器を使用します。 内部の前置加算器は、論理セルだけでなく、水晶リソースのトレースも大幅に節約します! *******

*******-ザイリンクス7シリーズ以前のFPGAの場合、係数のビット深度が18を超えない場合にのみこの方法が保存されます。2015-2016年の超近代的なザイリンクスUltra-Scaleチップの場合、可能です。 24因子の容量を持つ予備加算器を実装します。

Vivado hls

FPGAでデジタル信号処理タスクのノードを作成する最新の方法は、2つの原則に基づいています。

- 設計時間の短縮(「 市場投入までの時間 」の概念)、

- エントリのしきい値の減少(C ++開発者の間でのFPGAの普及)。

両方の原則は偶然に生じたものではなく、主にFPGAの論理容量の絶え間ない増加に由来しています。 ザイリンクスは、(VHDLおよびVerilog言語の)古いプログラミング方法では現在のタスクに対応できなくなっていると主張しており、将来的にはFPGAプログラミングがCやC ++などの高級言語でのみ行われる可能性が高くなります。 ザイリンクスは、数年前にVivado HLSと呼ばれる新しいデザインツールを発表し、すべての大規模プロジェクトを部分的または完全に新しいレベルに引き上げました。 Vivado HLSでの開発は、「 クロック周波数 」の概念から離れて、FPGAを参照せずに複雑なアルゴリズムを開発できるという事実に帰着します。FPGAのすべての最適化は、プロジェクトの最終段階で既に行われている必要があります。 新しい環境を使用して何ができるかを見て、Vivado HLSで最も単純なFIRフィルターを開発してみましょう。

例として、ザイリンクスの実験室の作品の1つを取り上げました。最初の近似では、最新のツールの能力を最大限に発揮します。 Vivado HLSを使用した主な開発は、相互に関連するタスクに基づいています。コードを記述し、ディレクティブを使用して速度と占有領域(エリア)を最適化します。

ザイリンクスは、次のデザイン動作を提供します。

- -C検証/シミュレーション( プロジェクト-> Cシミュレーションの実行 ):アルゴリズムの作成、プロジェクトのデバッグ、コードのエラーの検出、標準とのデータの比較など。

- -C合成( ソリューション-> C合成の実行 ):CコードからRTL形式へのプロジェクトの合成と受信データの分析:パフォーマンス評価(レイテンシ、トリップカウント、速度など)、リソース推定、受信I / Oインターフェイス*

- -RTL検証( ソリューション-> Run C / RTL Cosimulation ):メイン()テストのCモデルを再利用して、RTLモデルを分析します(セルフチェック)。

- -IPの作成( ソリューション-> RTLのエクスポート ):メインプロジェクト(Xilinx ISE、Vivadoなど)でさらに使用するためのIPコアの作成

さまざまな決定を下す方法は? ディレクティブを使用-Vivado HLSでプロジェクトを最適化するツール。 ディレクティブは、ソースコード( ソースファイル )または別のディレクティブファイル( ディレクティブファイル )に追加できます 。

- ソースファイル -プロジェクトの作成中に変更されないディレクティブの設定に適しています。 たとえば、I / Oポートインターフェイスのディレクティブは変更されません。 プロジェクトでは、これらのディレクティブは#HLSというプレフィックスで示されます。

- ディレクティブファイル -速度と配置の最適化に影響する条件と制限の設定に適しています。 原則として、プロジェクトでは、さまざまなソリューションのいくつかの制限を比較し、最適な制限を選択できます。 プロジェクトでは、これらのディレクティブは接頭辞%HLSで示されます 。

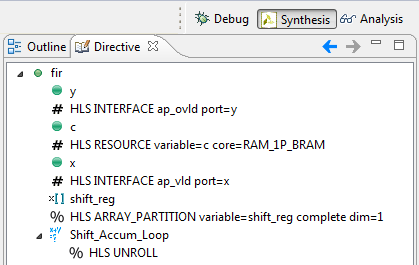

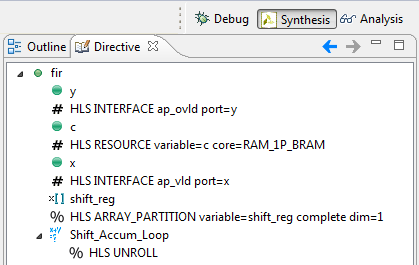

最も単純なFIRフィルターのソースコードの例を示します。 ソースコード内のディレクティブに注意してください。

Vivado HLS用FIRフィルターC ++

#include "fir.h" void fir ( data_t *y, coef_t c[N], data_t x ) { <b>#pragma HLS</b> INTERFACE ap_ovld port=y <b>#pragma HLS</b> INTERFACE ap_vld port=x <b>#pragma HLS</b> RESOURCE variable=c core=RAM_1P_BRAM static data_t shift_reg[N]; acc_t acc; data_t data; int i; acc=0; Shift_Accum_Loop: for (i=N-1;i>=0;i--) { if (i==0) { shift_reg[0]=x; data = x; } else { shift_reg[i]=shift_reg[i-1]; data = shift_reg[i]; } acc+=data*c[i];; } *y=acc; }

別のファイルのディレクティブは次のとおりです。

set_directive_unroll "fir/Shift_Accum_Loop" set_directive_array_partition -type complete -dim 1 "fir" shift_reg

注:最適化プロセス中に、開発者は多くの場合、パフォーマンスとリソースの観点から異なる結果を比較する必要があります。したがって、多くの場合、ディレクティブの大部分は別のファイルに書き込まれます。開発者がすべての決定に特定の最適化が必要であると確信している場合、ソースコードに入力できます!

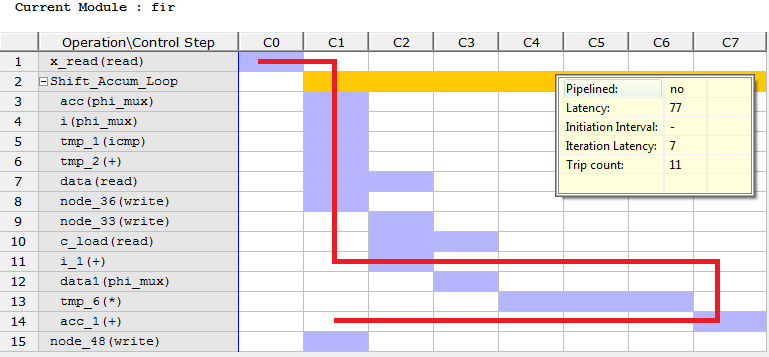

FIRプロジェクト用に3つの異なるソリューションを作成します。

- ディレクティブを使用しない(シンセサイザーは最小限のリソースを使用する-順次データ処理)

- ポートディレクティブを使用する(シンセサイザーが入力/出力インターフェイスを最適化する)、

- UNROLLディレクティブを使用します(FORループを展開し、ループの各反復を並列処理します)。

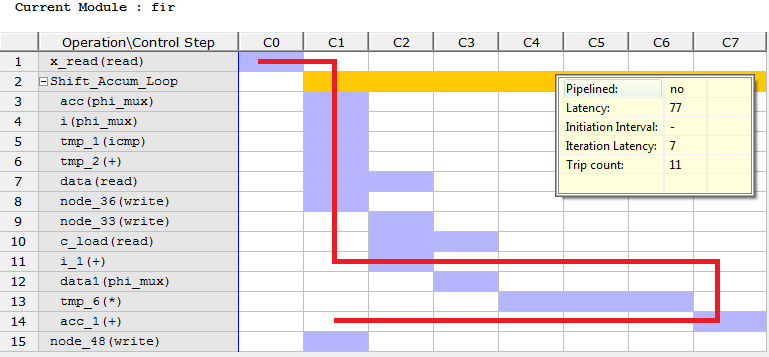

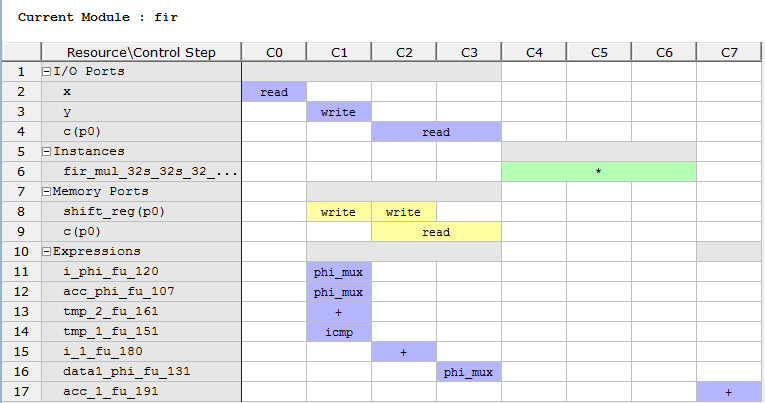

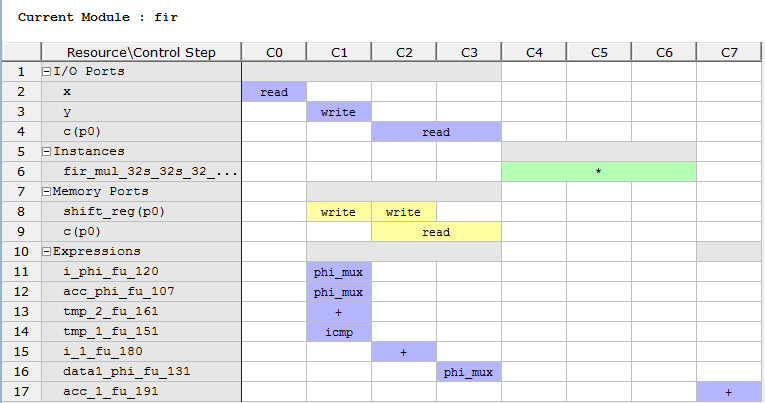

Vivadoでの合成の結果、使用されるリソースと最大パフォーマンスの完全な分析を実行できます。作成されるカーネルのI / Oポートインターフェイスを参照してください。さらに、特定の機能が実行される方法、それらが占有するリソースの数、および実行されるクロックサイクルの数を確認できます。

3つのソリューションの比較:

Vivado HLSでのプロジェクト合成結果

ディレクティブ:[

パフォーマンス

]タブ:[リソース]タブ:

クリスタルリソース:

パフォーマンス

]タブ:[リソース]タブ:

- ポートxの読み取りとポートyの書き込みは、1クロックサイクルで行われます。ポートcはRAMメモリインターフェイスとして記述されているため、2サイクルで読み取ります。

- 2つの乗算器が使用されます。

- シフトレジスタshift_regは、読み取りおよび書き込み操作に使用されます。

- 残りのリソースは、単一の形式(コード内の式)で存在するため、共有されません。

クリスタルリソース:

この記事は前例のないサイズに既に成長しているため、新しいプロジェクトの作成プロセスとすべての設計ステップについては説明しません。しかし、プロジェクトでVivado HLSを使用するトピックに興味がある場合は、喜んで私の経験を共有します。urockのヘルプも使用できます。この問題では、彼はマスターです!

おわりに

これを要約したいと思います。この記事では、FPGAでFIRフィルターを作成する基本原則について説明します。記事に関する一般的な結論:

- — , FPGA .

- = = = .

- , .

- .

- .

- N (, 512), .

- .

- .

- .

- , .

- . , .

アルテラFIR設計:

ザイリンクスHLS FIRデザイン1:

ザイリンクスHLS FIRデザイン2:

ザイリンクスHLS FIRデザイン1:

ザイリンクスHLS FIRデザイン2:

文学

- DSPLIB

- Altera FIR Compiler

- Xilinx FIR Compiler

- Xilinx DSP48E1 (7 Series)

- Xilinx DSP48E2 (Ultra-Scale)

- Wikipedia FIR

- Parks-McClellan algorithm

- MATLAB Tutorial 1

- MATLAB Tutorial 2

- OpenCores FIR 1

- OpenCores FIR 2

- OpenCores FIR 3

続行するには...