FPGAでのデジタル信号処理に関する記事を何度も始めたいと思っていましたが、さまざまな理由でこれを始めることができませんでした。 幸いなことに、自由な時間もありましたので、FPGA上のDSPに関連するさまざまな側面を反映した資料を定期的に公開します。

これらの記事では、これらのアルゴリズムまたはそれらのアルゴリズムの理論的な説明を最小限に抑え、私自身および同僚や友人がFPGA開発に何らかの形で遭遇した実用的な微妙さにほとんどの資料を捧げようとします。 この一連の記事が初心者エンジニアと経験豊富な開発者の両方に役立つことを願っています。

パート1:CICフィルター

最初の部分では、最も単純なCICフィルターを検討します 。 CIC-ロシア語の「カスケード積分櫛」-IIR型のカスケード積分櫛フィルター(無限インパルス応答)。 このようなフィルターのクラスは、複数のデータレートで作業が必要なタスクで広く使用されています。 CICフィルターは、間引きと補間、つまりサンプリング周波数を下げたり上げたりするために積極的に使用されます。 CICフィルター自体は、ローパスフィルター(ローパスフィルター)にすぎません。 つまり、このようなフィルターは、スペクトルの低周波数を通過させ、カットオフ周波数の背後の高周波数を遮断します。 フィルターの周波数応答は、法則〜sin(x)/ xに従って構築されます。 CICフィルターの主な利点は、乗算演算をまったく必要としないことです(他のタイプのフィルター、たとえばFIRとは異なります)。

はじめに

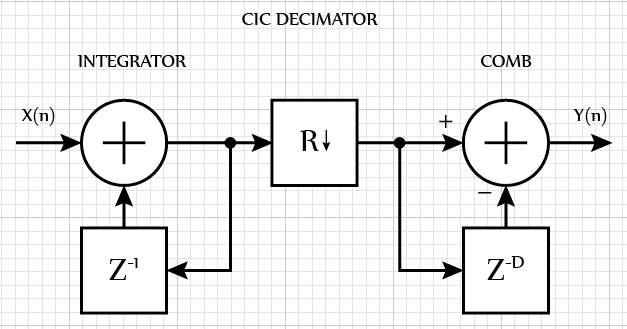

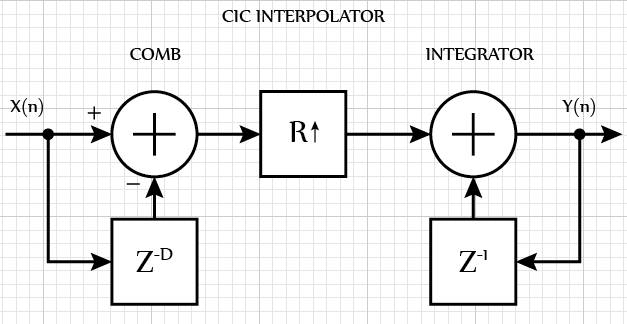

名前から、CICフィルターは2つの基本ブロックに基づいていると推測できます:積分器と櫛形フィルター(微分器)。 積分要素 (int)は、最も単純なバッテリーとして作られた通常の1次IIRフィルターです。 くし形フィルター (comb)は1次FIRフィルターです。

積分器とくし形フィルターの間には、サンプリング周波数を整数回( R)増減させるためにノードが配置されることがよくあります。

- 入力シーケンスからサンプリング周波数を下げる場合、各Rサンプルが選択され、間引きされた出力シーケンスが形成されます。

- 入力シーケンスのサンプル間のサンプリング周波数を増加させる場合、ゼロは単純に挿入され、その後、積分セクションで平滑化され、増加したサンプリング周波数でシーケンスを形成します。

伝達特性と振幅周波数特性の式は以下のとおりです。

間引きおよび補間のすべての側面に関するすべての数学的計算の詳細については、他のソースで見つけることができます。これについては、記事の最後にリンクを示します。

間引き

CICフィルターを使用してサンプリングレートを下げる場合、デシメーターと呼ばれます。 この場合、積分器が最初のリンクになり、サンプリングレートが低下し、最後に微分フィルターリンクが使用されます。

補間器

CICフィルターを使用してサンプリングレートを上げる場合、補間器と呼ばれます。 この場合、微分要素が最初にあり、サンプリング周波数が増加し、最後に積分フィルターリンクがあります。

微分要素での入力信号の遅延に応じて、フィルターのさまざまな周波数特性を取得することができます。 遅延パラメーターDが増加すると、フィルターの振幅周波数特性(AFC)の「ゼロ」の数が増加することが知られています。

微分セクションでパラメーターDが増加する積分器と櫛形フィルター(CICフィルター)の束では、周波数応答のゼロが中心にシフトすることに注意してください。フィルターカットオフ周波数Fc = 2 pi / Dが変化します。

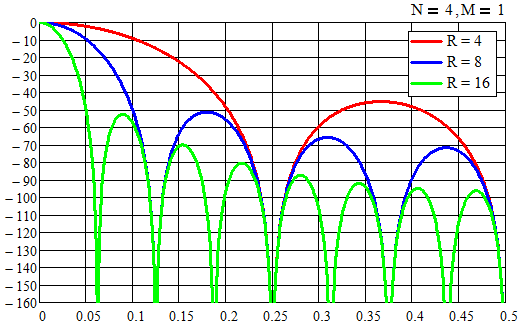

間引きおよび補間操作を行わない積分器と櫛形フィルターのカスケード接続は、移動平均フィルターと呼ばれます。 このようなフィルターの最初のサイドローブのレベルは-13 dBだけであり、深刻なDSPタスクに十分な大きさです。

CICフィルターで発生する数学演算の線形性により、複数のフィルターを連続してカスケード接続することが可能です。 これにより、サイドローブのレベルが比例して減少しますが、スペクトルのメインローブの妨害も増加します(スペクトルとは、フィルターの周波数応答を意味することがよくあります)。 したがって、同じタイプのCICフィルターのNカスケード接続では、同一の伝達特性が増加します。 原則として、インテグレーターと櫛形フィルターのセクションはタイプごとに結合されます。 たとえば、最初に同じタイプの積分器のNセクションが連続して配置され、次に同じタイプの微分フィルターのNセクションが配置されます。

次の図は、サンプリング係数Rのさまざまなパラメーターに対するフィルターの周波数応答を示しています(計算はMathCAD 14で行われました)。

CICフィルターの周波数応答は、矩形インパルス応答(TH)を備えたFIRフィルターの周波数応答と完全に同等です。 トータルフィルターICは、積分器のカスケードと櫛形フィルターカスケードのカスケードのすべてのインパルス特性の畳み込みとして定義されます。 CICフィルターの次数が大きくなると、ICは適切な回数だけ統合されます。 したがって、1次のCICフィルターではTHEMは長方形、2次のTHEMは二等辺三角形、3次ではTHEMは放物線などになります。

ビット深度の増加

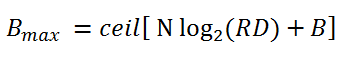

あいにく、くし形構造における遅延値Dの増加およびフィルタNの次数の増加は、透過係数の増加をもたらす。 これにより、フィルター出力のビット深度が増加します。 CICフィルターを使用するDSPタスクでは、これを常に覚えて、送信信号が使用済みビットグリッドを超えないようにする必要があります。 たとえば、ビット深度の増加による悪影響は、FPGAチップの使用済みリソースの大幅な増加に現れます。

補間器:限られた精度の使用はレジスタの内部ビット深度に影響せず、最後の出力ステージのみがスケーリングされます。 積分器セクションでビット深度が大幅に増加します。

間引き: CICフィルター間引きは、中間データと出力データのビット深度が依存するパラメーターD、R、およびNに非常に敏感です。 微分リンクと積分器の両方が、出力信号の最終ビット深度に影響します。

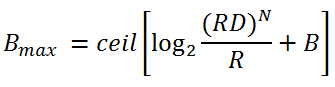

これらの式では、 Bは入力データのビット深度、 Bmaxは出力データのビット深度、 Rはサンプリングレート、 Dは遅延パラメーター、 Nはフィルター次数(カスケードの数)です。

注! Hogenauerの記事では、各デシメータステージのビット深度を選択するための原則について説明しています。 ザイリンクスとアルテラは、フィルタを実装する際に、フィルタ容量の増加による悪影響を考慮し、この記事で説明されている方法を使用してこの現象に対処しています。

ザイリンクスCICフィルター

私の仕事はザイリンクスのマイクロサーキットに99%関連しているため、このベンダーのIPフィルターカーネルの説明を提供します。 しかし、アルテラにとってすべてがほぼ同じであることを保証することを敢えてします。

CICフィルターを作成するには、 CORE Generatorアプリケーションに移動して、使用するFPGAの種類と、この場合は必須ではないその他のさまざまな設定を示す新しいプロジェクトを作成する必要があります。

CICコンパイラ-タブ1:

コンポーネントのコンポーネント名 (ラテン文字a〜z、数字0〜9、および記号「_」を使用)。

フィルター仕様:

- フィルタータイプ -フィルタータイプ:補間/間引き。

- ステージ数 -インテグレーターとくし形フィルターのカスケードの数:3-6。

- 微分遅延 -微分フィルターセルの遅延:1-2。

- チャネル数 -独立チャネルの数:1〜16。

サンプルレート変更仕様:

- 固定/プログラム可能 -サンプリング係数のタイプR:定数/プログラム可能。

- 固定または初期レート -サンプリング係数Rの値:4..8192。

- 最小レート -サンプリング係数Rの最小値:4..8。

- 最大レート -サンプリング係数Rの最大値:8..8192。

ハードウェアオーバーサンプリング仕様:これらのパラメーターは、出力サンプルレート、データの処理に必要なクロックサイクル数に影響します。 カーネル内の並列処理のレベルと占有されるリソースの量も、これらのパラメーターに依存します。

- 形式の選択 -フィルターの周波数比を選択します:周波数仕様/サンプル周期。

- 周波数の指定 :ユーザーは、サンプリングレートとデータ処理の頻度を設定します。

- サンプル周期 -クロック仕様:ユーザーは処理周波数とデータのクロック周波数の比率を設定します。

- 入力サンプリング周波数 - *

- クロック周波数 -フィルター処理周波数: *

- 入力サンプリング周期 -入力クロック信号の周波数に対する処理周波数の比率: * 。

* -範囲は一般設定とサンプリングレートRに依存します。

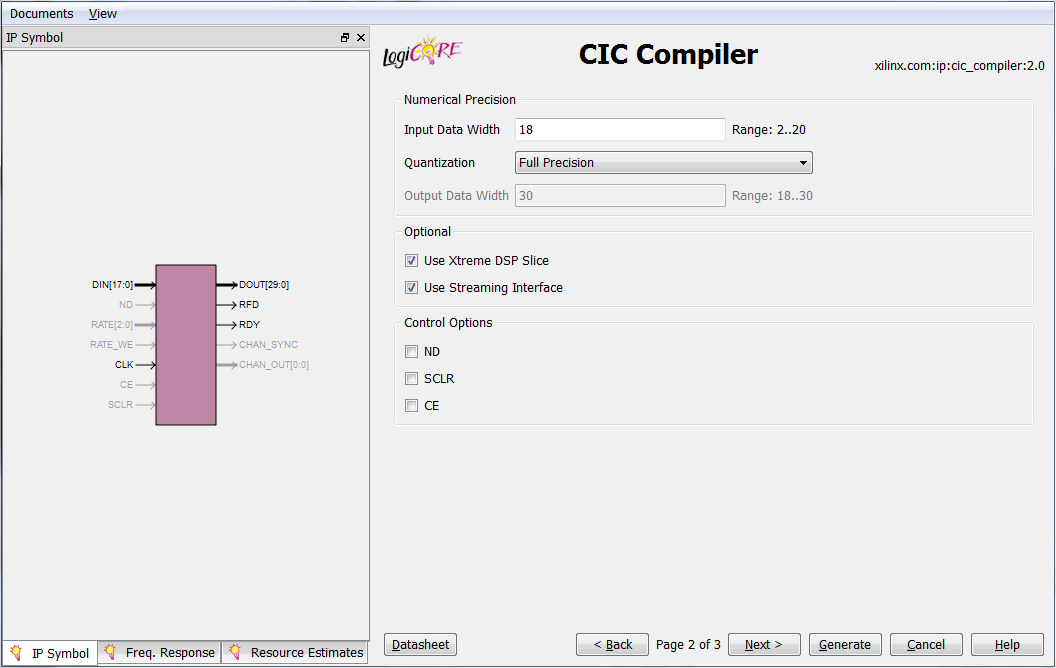

CICコンパイラ-タブ2:

数値精度:

- 入力データ幅 - 入力データの幅 :2..20。

- 量子化 -出力の丸め:ビットグリッドの完全な精度/丸め。

- 出力データ幅 - 出力データの幅。範囲は係数N、D、およびRに依存します(最大値は48ビットです)。

オプション:

- Xtreme DSPスライスを使用-組み込みDSPブロックを使用してフィルターを実装します。

- ストリーミングインターフェースの使用-マルチチャネルフィルターの実装には、ストリームインターフェースを使用します。

制御オプション:

- ND- 「新しいデータ」、フィルター入力へのデータ入力を決定する入力信号。

- SCLR-同期フィルターリセット(この入力の論理ユニットがリセットを実行します)。

- CE- 「クロックイネーブル」、フィルタークロックイネーブル信号。

CICコンパイラ-タブ3:

要約 -リスト形式のこのタブには、最終フィルター設定(ステージ数、周波数パラメーター、入力のビット深度、出力および中間データ、フィルターの遅延など)が反映されます。

CIC Compilerウィンドウの左側には、3つの便利な追加タブがあります。

- IPシンボルは、アクティブなI / Oポートを備えたIPブロックの概略図です。

- 頻度 応答 -CICフィルターの伝達特性。

- リソースの見積もり -占有リソースの見積もり。

すべての設定を設定したら、[ 生成 ]ボタンをクリックします。 その結果、しばらくすると、CORE Generatorアプリケーションはファイルのセット全体を生成しますが、その中で最も基本的なファイルが必要です。

- * .VHD (または* .V ) -VHDLまたはVerilogでモデリングするためのソースファイル。

- * .VHOは役に立たないファイルですが、そこからコンポーネントの説明を取得し、プロジェクトに挿入するために移植できます。

- * .NGC-ネットリストファイル。 選択したFPGAチップのIPコアのアーキテクチャ(使用するコンポーネントとそれらの間の信号接続)の説明が含まれています。

- * .XCO -IPカーネルのすべてのパラメーターと設定が保存されるログファイル。 ザイリンクスISE Design Suiteを使用する場合に役立つファイル。

ISE Design Suite環境で作業している場合、CORE Generatorは必要なファイルを作業ディレクトリに自動的に作成します。 他の開発ツール(ModelsimやAldec Active-HDLなど)の場合、必要なファイルを適切な作業ディレクトリに転送する必要があります。

MATLABのCICフィルター

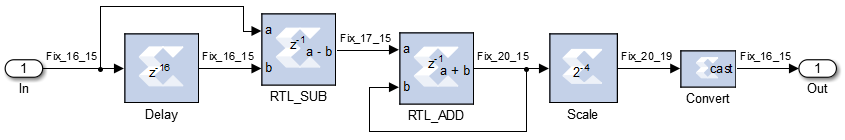

例1:モデリングの場合、MATLABは非常に便利なツールです。 たとえば、Xilinx System Generator Toolboxのロジックエレメントで作成された4次CICフィルターモデルを使用します。 間引きと補間は使用されません(CICはウィンドウ16の移動平均フィルターに縮退します)。 フィルターパラメーター:R = 1、N = 4、D =16。次の図は、MATLABの1つのカスケードのモデルを示しています。

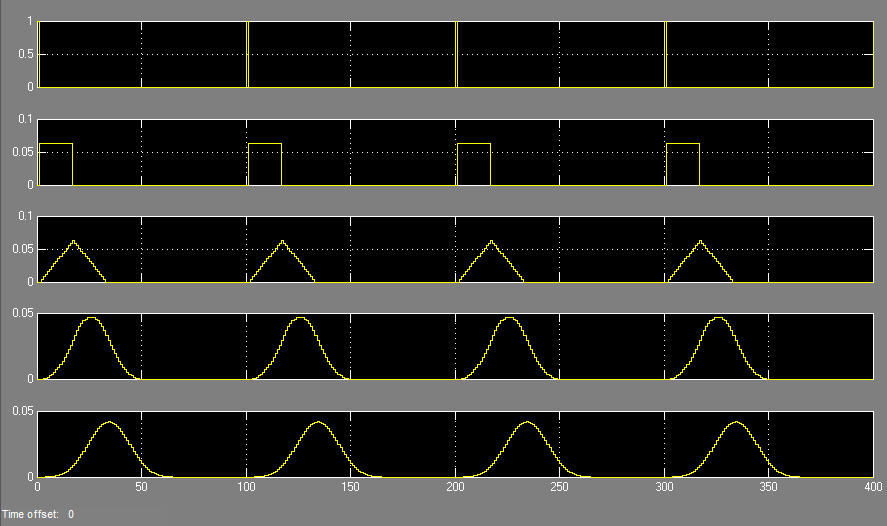

フィルターの各段階の後、インパルス応答がどのように見えるかを見てみましょうこれを行うには、システムの入力に周期的な単一インパルスを適用します。

最初のリンクの出力の信号は、持続時間= Dの矩形パルス、2番目のリンクの出力-持続時間2Dの三角信号、3番目のリンクの出力-放物線パルス、3番目の出力-3次放物線を形成していることがわかります。 結果は理論と完全に一致しています。

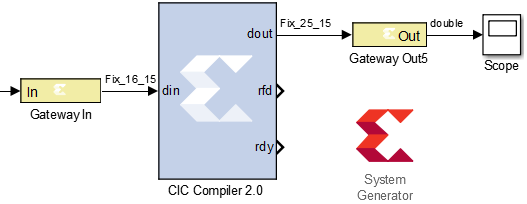

例2: CICフィルターのIPコアを直接。 パラメーター:N = 3、R = 4、D =1。次の図は、フィルターモデルを示しています。

数サイクル(たとえば32)の持続時間を持つ単一のパルスがこのようなフィルターの入力に適用される場合、放物線信号が3次移動平均フィルターに似た出力で形成されます。

まとめ

これを要約したいと思います。 CICフィルターは、サンプリングレートを変更する必要がある多くのタスクで使用されます。 CICフィルターは、ビットレート(44.1 kHzから48 kHz、またはその逆)を変更するオーディオテクノロジーなど、いくつかのサンプリング周波数(マルチレート処理)で動作するシステムで使用されます。 CICフィルターは、DDC(デジタルダウンコンバーター)およびDUC(デジタルアップコンバーター)の実装のために通信システムで使用されます。 CICフィルターの使用例:Analog DevicesのAD6620デジタル受信チップ 。

多くの場合、HDL言語でFPGAに独自のフィルターを実装する必要はありません。また、ベンダーの既製カーネルまたはすぐに使用できるオープンソースプロジェクトを安全に使用できます。 それでもアプリケーションに独自のCICフィルターを実装する必要がある場合は、次の原則を覚えておく必要があります。

CICフィルターには多くの機能があります。

- 実装が簡単で、乗算演算を必要としません。

- CICフィルターのデシメーションと補間はどこでも使用され、整数時間と小数時間の両方でサンプリングレートをすばやく変更します。

- フィルター次数Nと遅延Dが増加すると、中間データと出力データのビット深度が増加します。

- フィルターNの次数が増加すると、サイドローブの抑制が増加し、周波数応答のメインローブの不均一性が増加します。

- 次のように、6〜8以下の次数のフィルターを使用することをお勧めします。 順序が増えると、実装がより複雑になり、占有されるリソースの量が増え、フィルターの周波数応答も帯域幅内で歪みます。

- くし形フィルターの遅延パラメーターDを大きくすると、フィルターのカットオフ周波数が変化しますが、実際にはカスケード接続ではパラメーターD <3です。

- R倍のデシメーションにより、フィルタの出力の容量が大幅に増加します。

- 補間中、中間データと出力データのビット深度への主な貢献は、リンクを統合することによってのみ行われます。

- CICフィルターの周波数応答は、矩形のインパルス応答を持つFIRフィルターの周波数応答と同等です。 トータルフィルターICは、積分器のカスケードと櫛形フィルターカスケードのカスケードのすべてのインパルス特性の畳み込みとして定義されます。

- FPGAのフィルターの出力で周波数を変更する場合、クロックイネーブル信号が使用されますが、処理周波数は変更されません。

- 比率が「処理周波数/サンプリング周波数」>> 1の場合、FPGAでフィルターリソースを再利用できるため、マルチチャネルシステムのクリスタルリソースを最小限に抑えて処理を実装できます。

- 最新のFPGAでは、CICフィルターはDSPブロック(Xilinx、Altera)に実装されていますが、空きリソースがない場合、論理セル(SLICE)に実装できます。

- CICフィルターの後に、信号レベルを目的のダイナミックレンジに調整する、プログラム可能なゲイン(ゲイン乗数)のある乗数をインストールすることをお勧めします

- CICフィルターは出力信号のスペクトルに歪みを導入するため、CICフィルターの後に、補償FIRフィルターをインストールする必要があります(計算手順はアルテラデータシートに記載されており、MATLABは計算に必要です)。

文学

- E. Ifeachor、B。Jervis。 Digitaal l SignProcessing:実用的なアプローチ(第2版)。

- Hogenauer、E.間引きと補間のためのデジタルフィルターの経済的なクラス。

- ウィキペディアCICフィルター

- アルテラCICフィルタユーザーガイド

- ザイリンクスCICコンパイラDS613

- MATLAB CICフィルター

- DSPLIB-CICフィルター

- DSPLIB-CIC間引きおよび補間

- Verilogソースコードと説明

- OpenCoresプロジェクト1.著者の姓は非常に興味深いです:)

- Opencoresプロジェクト2

続行するには...