サインを待っていましたか? 彼がいる!

長年、私はFPGAのプログラミングを始めることを敢えてしませんでした。なぜなら、それは難しく、高価で、苦痛だからです(私にとっては)。 しかし、あなたが最初の一歩を踏み出すのを助けてくれる友人がいるのは良いことです。 そして今、私は一つのことを理解していません-なぜ私はとても長く待っていましたか?

今、私はあなたが最初の一歩を踏み出すのを手伝います!

なぜ必要なのですか?

MKのドックを常に読んだり、大量の情報を頭に入れたりするのにうんざりしていませんか。 asmですべてを書き直しましたが、速度はまだ十分ではありません。 2つの外部デバイスをMKに接続し、3番目のデバイスを接続しましたが、中断が発生し、既に動作していたモジュールが動作しなくなりました。 同じ行からより強力な別のMKを使用しますが、再びマニュアル、フラグレジスタ、ビット...地獄。 プラットフォームを変更します。別のMKに切り替えて、以前のプラットフォームに関する知識をゴミ箱に捨てます。 あなたが何をするにしても、それは難しいです。 コンポーネントからプロジェクトを簡単に構築できる人気のあるプラットフォームを見つけましたが、このMKのハードウェアの制限を超えることはできません... 「これはまさにプラットフォーム上で解決する必要のある問題です」とはいえ、私はこれを行うことができる/始めるために古く/愚かな/忙しい/などです。

最終的に自由に呼吸したいですか? 続けましょう!

FPGA開発の喜び

大変な一日でした。 1つの仕事から2番目の仕事に行き、次に夏の別荘、夕方の雑用、宿題、そして家族が映画を見て、23時だけ完全に自由になりました! 私が疲れたと言うことは何も言わないことです。 しかし、この状態では、440 Hzで蛇行発生器を作るという確固たる目標を持ってラップトップに座っていました。 20分が経過し、すでにヘッドフォンで聞いたことがあります。 私は自分の耳を信じていませんでした! PWMを実行して音量を変更するには、さらに15分かかりました。 その時までに、私はFPGAボードを1週間しか持っていませんでしたが、その前にVerilogについての本をいくつか読んだだけでした。

その夜、私は気づいた: ここに! ここに、自分の考えを本当に簡単に実際のハードウェアに変えることができるプラットフォームがあります!

なぜそう

FPGAの研究と応用における利点について説明しますが、いずれにしてもFPGAを知っています。

- 知識の普遍性-MKモデルを変更するときは、ドックを読む必要があります。 メーカーMKを変更する場合は、ドックを読む必要があります。 あなたは常にドックを読み、常に頭の中にたくさんの情報を保持する必要があります。 FPGA向けに開発する場合、VerilogまたはVHDLを知っていれば、あるメーカーのラインのFPGAをプログラムできるだけでなく、別のメーカー(Altera、Xilinx)に切り替えることもできます。 異なる開発環境の開発の瞬間、わずかなハードウェアの瞬間がありますが、HDLでデバイスを設計するアプローチの本質はこれから変わりません。

- アイデアからハードウェアまで -プロジェクトの開発時に、1ミクロン不足している場合は、別のミクロンを選択する必要があります。 原則として、このMKがプロジェクトに対処するかどうかを推測できます。 または、特定のMKがあり、そこにプロジェクトを収めようとしています。 たいていの場合。 祖父のアプローチを思い出させます。これは、小屋にあるものから階段を作ります。 はしごを設計することはできますが、適切なボードを購入してください...アイデアから鉄へ、そしてその逆ではありません。

- 他の人のデザインの使いやすさ -他の人のモジュールを使用してプロジェクトに適用できます。 コードによって、その仕組みを理解できます。 たとえザイリンクス用であり、あなたがアルテラの下で行ったとしても。 うまくいかない場合もありますが、たとえば、バイナリライブラリをc ++ / Qtプロジェクトに追加するよりも簡単です

- ブロックの独立。 HDLのブロックは、PLの純粋な関数のようなものです。 入力信号のみに依存します。 開発およびデバッグされたモジュールは、プロジェクトがどのように成長しても、正常に機能し続けます。 外部からは、内部からの作業の正確さに影響しません。 とにかく、あなたはそれがどのように機能するかを忘れることができます-それはブラックボックスです。 さらに、ブロックは並行して動作します 。

選択の問題

何を選択するかという質問は、アルテラ/ザイリンクス、Verilog / VHDL、というデバッグボードを採用することで強く停止します。 しかし、まず最初に。

メーカー

アルテラを選びました。 なんで? ザイリンクスという名前は私にとってよりきれいですが、私たちは友人とそのように決めました。 しかし。 あなたが今選択できない場合、私はあなたのためにそれを行います。 アルテラが必要です! なんで? 知りません ここで、選択を行うというステップを踏むことがより重要です。 アルテラを選択しましたが、まだ後悔していません。

言語

私たちはVerilogを採用しています- なぜなら ... ええと 、あなたは理解しています。

デバッグボード

デバッグボードの選択には最も時間がかかりました。 搭載されているFPGAチップでボードが異なることは明らかです。 また、FPGAチップは要素数が互いに異なります。 しかし、テストプロジェクトに必要な数は完全には明らかではありません。 そのため、ほとんどの時間を費やして、あらゆる種類のFPGAプロジェクトを検索し、それらが消費するFPGAリソースの量を調べました。

アルテラファミリでは、リーズナブルな価格で、240、570、および1270要素のCPLD MAX IIを搭載したマザーボード、または最大10,000個以上のセルを備えたCyclone 1、2、3、4を搭載した古いFPGAチップを購入できます。 選択方法

240個のセルに基づいても、 火星探査機プロジェクトは膨大な数のプロジェクトを実行します。 240セルに収まることができるプロジェクトの複雑さの大まかな概念を理解することを強くお勧めします。 一方、プロセッサとその周辺のすべてのロジック( NES 、 Speccy 、 Orion 、 UT-88など)を含む特定のPCのハードウェアコピー用に完全にプログラム可能なプロジェクトがあります。 このためには、5、10、またはそれ以上のセルがすでに必要です。 さらに、これらのボードには追加の外部デバイスが含まれています。

したがって、利用可能な手段に応じて上向きを優先して、240から10,000セルの間に何かを入れることをお勧めします。 デバッグボードでは、余分なセルは怖くありません。十分でない場合は、何もする必要はありません。 次に、デバイスをデバッグすると、必要なセルの数が明らかになります。不必要な「ボディキット」を使用せずに適切な量で購入し、完成したデバイスに残しておく方が安くなります。

セルの数に加えてMAXがCycloneと実際に異なるのは次のとおりです。

1)MAXシリーズには内部にPLLがありません。 各デバッグボードには、通常50 MHzのジェネレータがあります。 プロジェクトの大部分で十分です。 すべての同期は、50 MHzをある値で除算することにより発生します。 または、外部ジェネレーターを使用して、別のFPGA入力に適用することもできます。 しかし、50 MHzを超える周波数が必要な場合はどうでしょうか? 50 MHz以上のジェネレーターをすぐに見つけることができませんでした。 しかしここでは、Cycloneに組み込まれているPLLが役に立ちます。 その上で、たとえば100 MHzまでの周波数を乗算できます。

2)Cycloneシリーズには、ハードウェア乗算ブロックが組み込まれています。 その数は特定のモデルに依存します-ここでは、「指示を一目見れば」どれだけかがわかります。 何らかのDSPを実行する場合は、便利です。セルを保存し、速度を上げます。 一方、乗算器がない場合は乗算できますが、小さなFPGAにはこれに十分なリソースがない場合があります。

他のすべての点で、私の「適合/不適合」基準。 デバッグは明らかにボードが必要とする以上のものであり、これに必要な最小値を埋めます。

どのくらいのお金が必要ですか?

プログラマー

私はプログラマーを自由にはんだ付けする時間がないと信じています。

300ルーブル。 私はebeeで私のものを取りました 、それはこのように見えます:

デバッグボード

金額に応じて、選択の幅が広がります。

350-550ルーブルの初期レベル 。 これらはMAX IIのボードです( 240または570セル)。 最初の慣れと、エンドデバイスへのさらなる統合に適している場合があります。 ボードにはジェネレーター、1組のボタン、1組のLEDがあり、残りの80個のピンは自由に決定できます。

電源

含まれている必要がありますが、常に含まれているわけではありません。 5ボルトのPSUと2Aの電流が必要です。

平均レベルは 900から1500ルーブルです。 これらは、主にセルの数が異なるCyclone 1、2、3、4ボードです。

このようなものにラベルを付けました:

EP 2 C 5 T144-サイクロン2約5kセル

EP 4 CE 6 E22C8N-サイクロン4約6kセル

EP 2 C 8 Q208C8N-サイクロン2約8kセル

サイクロン3には、サイクロン4よりも多くのセルがある場合があります。

以下にいくつかのオプションを示します。

835ルーブル。

ALTERA FPGA CycloneII EP2C5T144学習に最適なシステムボード

880ルーブル

アルテラCycloneII EP2C5T144 FPGAミニ開発ラーニングコアボードE081

1265ルーブル

EP2C8 EP2C8Q208C8N ALTERA Cyclone II FPGA評価開発コアボード

高度な機能を備えたボード 。 これらは、追加のモジュール(UTP、USB、AUDIO)、コネクター(SD、VGA)、ボタン、スイッチ、LED、7セグメントインジケーターなどが取り付けられているボードです。 または、ベースボードを取り付けて、拡張カードを個別に取り付けることができます。

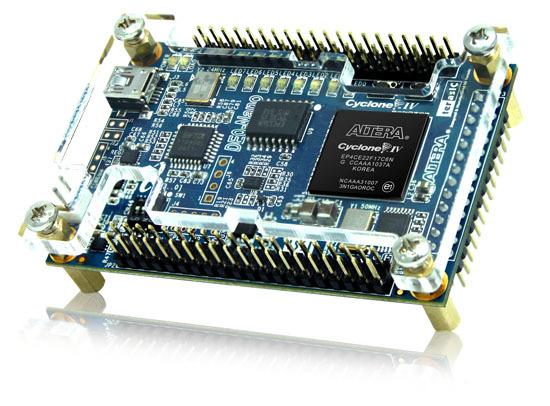

私はそのようなキットを持っています-ボード+拡張ボード:

Altrea EP4CE10E22 FPGA CORE Board + Device Board USB /サウンド/イーサネット/ SDカード/ VGA

2760ルーブル

これがメインボードです。 2つのLED、2つのボタン、4つのスイッチ、7セグメントインジケータ、およびRAMチップがあります。

拡張ボード。 SD、VGA、USBコントローラー(高速USB2.0チップ:CY7C68013A)、オーディオ(最大96kHz / 32ビットADC / DACのサウンドカード:WM8731S)、UTP(100Mイーサネットインターフェイス:DM9000A)がはんだ付けされています:

これらのボードは、一方を他方に挿入するだけですが、引き出しにはまだあります。 私の工芸品には、キットに付属のケーブルと接続するブレッドボードがあります。 5ボルトの電源も含まれています。

その他のオプション:

アルテラCyclone NIOS II SOPC FPGA開発学習ボードEP2C8Q208C8N + LCD1602-2670ルーブル

Terasic Altera FPGA DE0-Nano Cyclone IV開発および教育委員会-4,600ルーブル

Alterボードの幅広い選択肢とそれらの拡張

火星探査機プロジェクト

しかし、一般的に、大きくて高価なデバッグボードの購入はお勧めしません。 高価な購入を正当化する必要がありますが、現時点では何が最適かは明確ではありません。 練習が始まると明らかになります。

注文しました、待っています

ボードが行く間、あなたは精神的および技術的に自分自身の準備を始めることができます:

-Quartus II v.11.1をインストールします

読む:

-本:A.K. デジタル機器の設計におけるPolyakov Languages VHDLおよびVerilog 2003

-www.kit-e.ru/articles/circuit/2008_3_161.php-短期コースHDL

-ローバーでのレッスン、 ヴェロ 、 建築 、 シンプルなスタイルのヒント 。

- 生き方としてのVERILOG

- 良い例

-FPGAの開始方法(ザイリンクス)

すべて!

FPGAに関する興味深いプロジェクトをお待ちしています!

PS。 「あなた」についてあなたに目を向けると、私は平等に人に向け、群衆の一部ではない。 「あなた」への訴えが気分を害した場合は、すみません。

注意! VerilogとFPGAは、問題を解決するための特効薬ではなく、 すべてのプロジェクトのマイクロコントローラーを置き換えることはできません。 FPGAを使用するには、一定レベルの技術トレーニングが必要です。 あなた自身があなたの人生のすべての決定に責任があります。 著者は、FPGAおよびVerilogの分野での研究から生じる可能性のある金銭的および一時的な損失に対するすべての責任を放棄します。