2か月前、 私は最初の顧客がビットコインネットワーク-Avalonをマイニング/サポートするための専用コンピューターを受け取り始めたと書きました。 私はすぐにAvalonの開発者であるYifu Guoに手紙を書き、彼は私にいくつかのチップを送ることに同意しました。 しかし、このパッケージはロシアのスローポストの深aに埋もれていました。

2か月前、 私は最初の顧客がビットコインネットワーク-Avalonをマイニング/サポートするための専用コンピューターを受け取り始めたと書きました。 私はすぐにAvalonの開発者であるYifu Guoに手紙を書き、彼は私にいくつかのチップを送ることに同意しました。 しかし、このパッケージはロシアのスローポストの深aに埋もれていました。

幸いなことに、 needbmwから連絡がありました。Avalonが1個の損傷したチップを持って彼のところに来て、 はんだ付けを解除して 、メールをバイパスしてくれました。 これで、ついにプロセッサの内部を覗くことができます。 これは、アバロンをブラックジャックで刈り取り、数百万を刈り取りたい多くの人にとって特に興味深いでしょう。

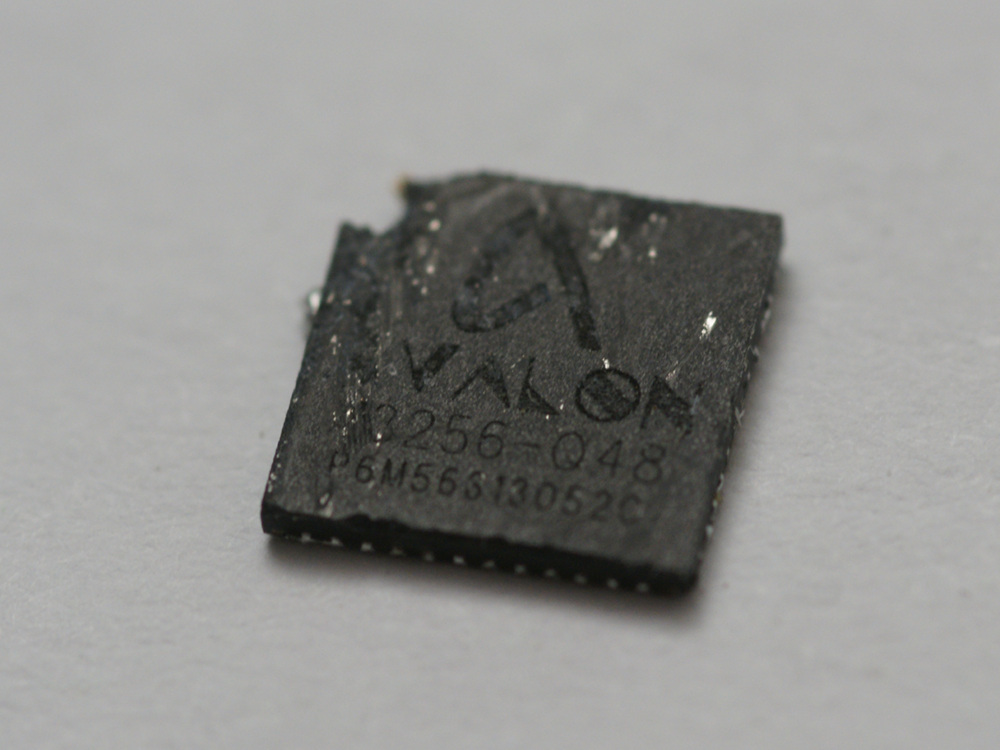

写真

破損したチップ自体:(残念ながらこの赤ちゃんは282 Mhash / s(AMD 6970グラフィックスカードのような)を数え、約2.5ワットを消費します。

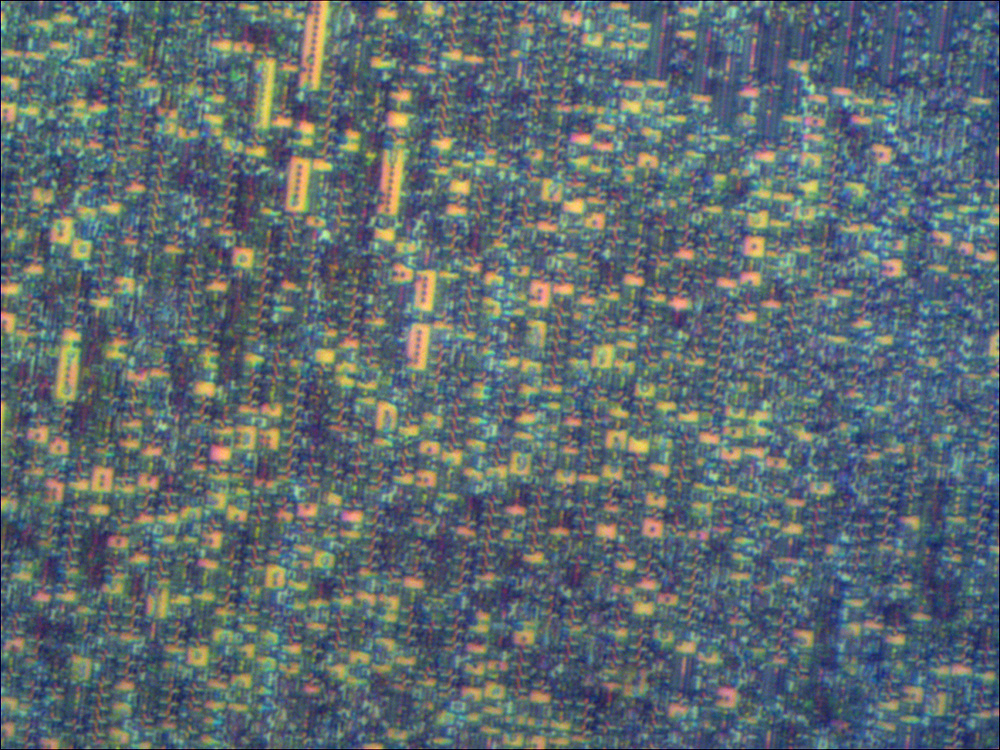

オープンソースから、このチップは110nmの製造プロセス、5層のメタライゼーションを使用してTSMC工場で製造されたことが知られています。 注目すべきは、チップ上の接触パッドがチップ上の結果よりもはるかに大きいことです。 それらのほとんどはそれぞれ電源/グランドであり、1本の足はチップ上のいくつかのパッドに接続されています。

結晶サイズは4.06 * 4.12 mmです。

上から-私たちは、電力/接地分配ネットワークのみを見て、全体の「詰め物」は金属接続の下に隠されています。

メタライゼーションを出血させる場合-Avalonは巨大なモノリシックロジックであり、メモリブロック、レジスタがないことは明らかです。これは通常の意味でのプロセッサではありません。 回路の左側のボックスは、おそらくPLL(外部クロック周波数逓倍器)および補助ロジックです。

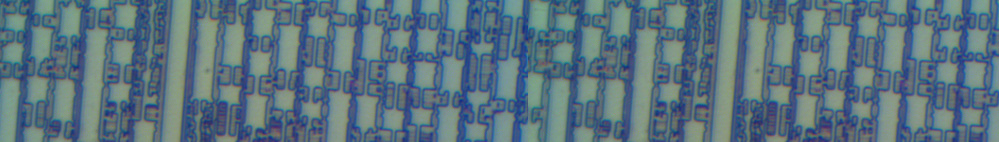

しかし、最大の倍率で超小型回路を見ると、最も興味深いことがわかります(すべての詳細が表示されていないにもかかわらず)。

61%にスケーリングされたスタンダードセルのライブラリに基づいた180nmテクノロジーを使用して製造された超小型回路と比較すると、Avalonのロジックははるかに高密度であることがわかります。

まとめ

Avalonは本物です(ButterflyLabsと混同しないでください。ButterflyLabsは1年以上も皆に朝食を提供してきました)。Yifu Guoは、すべてが急いで行われたことを全員に保証していますが、ロジックの密度は、少なくともいくつかの要素またはブロックが手で描かれたことを示唆しています。

したがって、誰かがオープンソースのBitcoin FPGAリーダーの完成したVerilogの説明を取得してAvalonを自動的に合成することを考えている場合、競争力のある製品を作成するのはそれほど簡単ではなく、同じプロセスで自動合成されたバージョンは2-4倍遅くなります(同じ消費電力で)。