UDBとの連携の実用的な開発において、最後から2番目のステップを踏む必要があります。 今日は、自動UDBエディターを使用せずに、Datapath Config Toolを使用して半手動モードで開発を行います。 このツールの習得に非常に役立つのは、AN82156-PSoC 3、PSoC 4、およびPSoC 5LP-UDBデータパスを使用したPSoC Creatorコンポーネントの設計です。 実際、私は自分で勉強しました。

おそらく、 UDBのドキュメントの翻訳を読んでいるときに、誰かが実際にそこから知識を再現しようとして、出版物に記載されているすべての機能がUDB Editorで利用できるわけではないことに気付きました。 これは、開発者がUDBエディターに特に面倒なメカニズムを配置し始めなかったためです。 AN82156の著者は、UDBエディターでは次のことはできないと主張しています。

- 並列データの入出力を整理します。

- 動的FIFO管理を編成します。

- FIFOクロック信号の逆を実装します。

- CRC機能を実装します。

- PRS機能を実装します。

- 着信転送の選択を実装します。

- 動的なインバウンド移行を実装します。

私自身から、UDB Editorでニブルの順列を実装する方法を見つけられなかったことを付け加えます。

プロジェクトでこれらの機能が必要な場合は、独自のVerilogコードを作成する必要があります。 具体的には、「書き込み」ではなく「作成」という言葉を使用しました。 このプログラミング言語を知ることは、読解レベルで十分です。 つまり、どのデザインが何のために必要なのかを理解する必要があります。 そして、ゼロから書くことができることは常に役に立ちますが、この記事で紹介する内容にはこのスキルは必要ありません。

解決可能な問題として、半合成のケースを選択しました。 一般に、パラレルポートにデータを出力することにしました。特に、手元にあるテキストLCDにはパラレルポートがあります。 3年前にMZ3D 3DプリンターをSTM32に移植したとき、私はそれをMZ3D 3Dプリンターから引き出しました。 そのため、ケースは半合成です。今日、このようなインジケーターは通常I2C入力を備えており、実際の生活ではワイヤーの束を介して接続する必要はありません。 ただし、最新のLCDにはパラレルポートもあるため、誰でもそれらを使用して実験を繰り返すことができます。

reprap.orgから取得した表示切り替えスキームを検討してください(これは簡単なことではありませんでした。私のプロバイダーはこのサイトをブロックします。

素晴らしいレイアウト! まず、読み取りについて考える必要はありません。LCDのデータは書き込みのみ可能です(R / Wラインは接地されており、コネクタでは使用できません)。 第二に、データは4ビット形式であるため、パラレル出力を処理できるだけでなく、ニブル置換関数の動作を確認することもできます。

プロジェクト作成

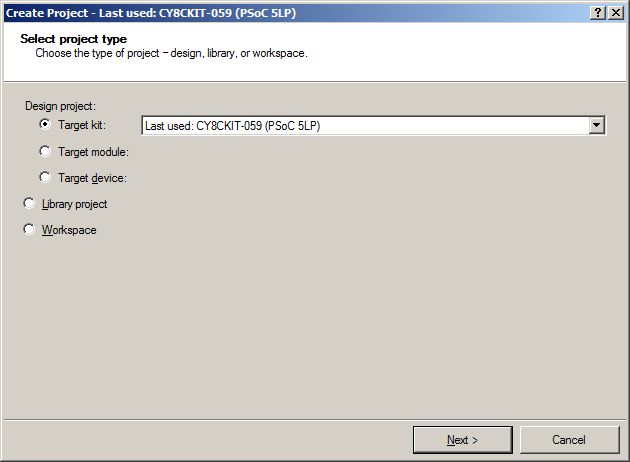

そのため、PSoC Creatorを起動し、 ファイル->新規->プロジェクトを選択します:

次に、ブレッドボードを選択します。

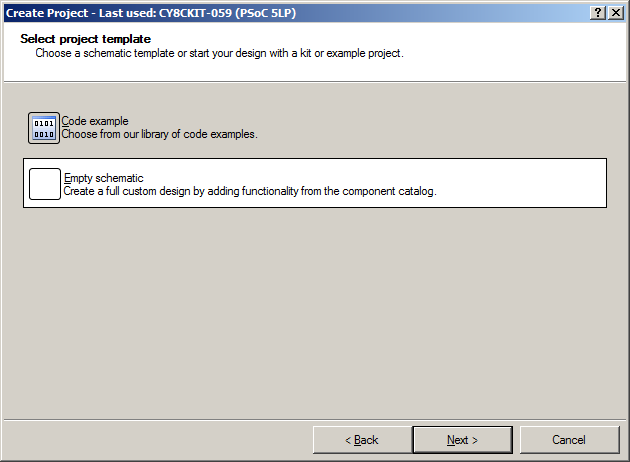

次は空の図です。

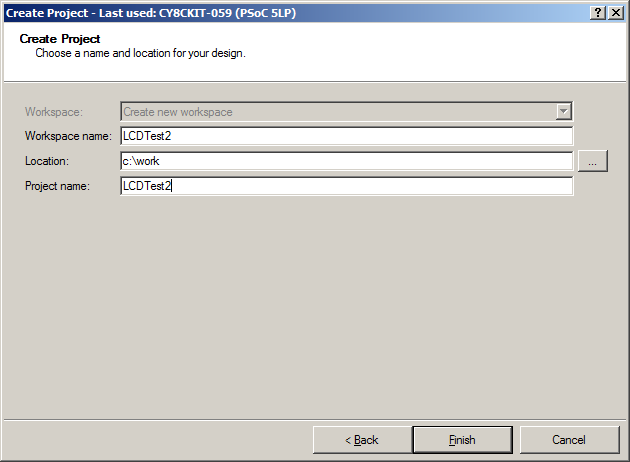

プロジェクトLCDTest2を呼び出します。

さて、前と同じように、[ コンポーネント ]タブに移動します。

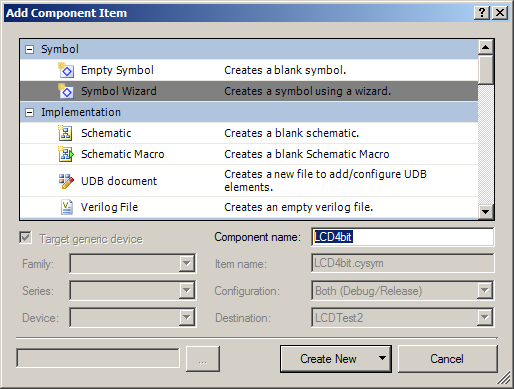

そして、プロジェクトを選択したら、マウスの右ボタンを押して、[ コンポーネント項目の追加 ]を選択します。

ここで、 シンボルウィザードを選択する必要があります。 名前を付けましょう ...さて、 LCD4bitとしましょう。

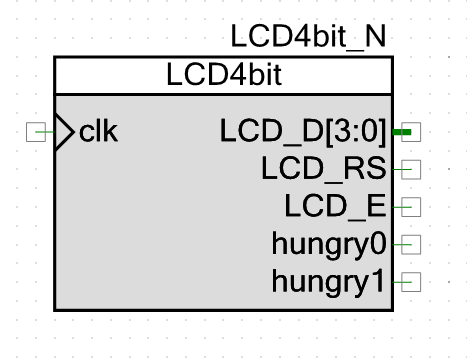

次のポートをシンボルに割り当てました。

clkはクロック入力です。 LCDプレフィックスの付いたポートは、標準のLCDポートです。 空腹-FIFOに空き領域があることをDMAユニットに伝える出力については、 RGB LEDの制御に関する記事で説明されています 。 [OK]をクリックしてキャラクターを取得します。

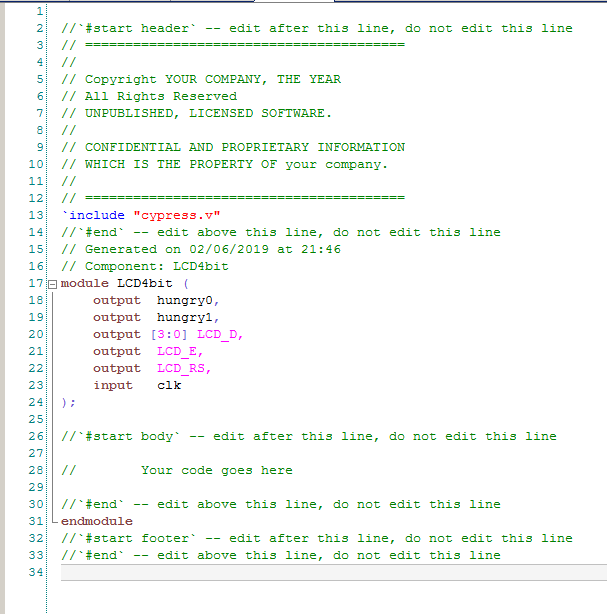

次に、このシンボルに基づいて、Verilogテンプレートを生成する必要があります。 シンボルの近くでマウスの右ボタンを押し、コンテキストメニューで[ Verilogの生成 ]を選択します。

次の図に示すテンプレートを取得しました(テキスト形式ではまだ意味がありません):

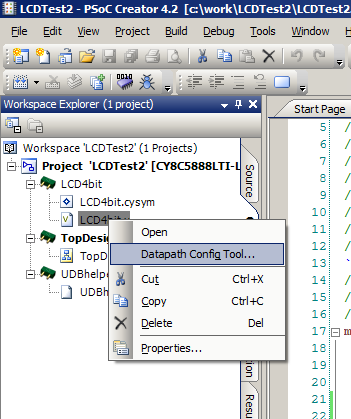

モジュールといくつかのセクションを作成しました。 しかし、彼らはまだデータパスを作成していません。 追加するには、プロジェクトツリーに移動し、 LCD4bit.vファイルを選択し、マウスの右ボタンを押して、表示されるコンテキストメニューでDatapath Config Toolを選択します。

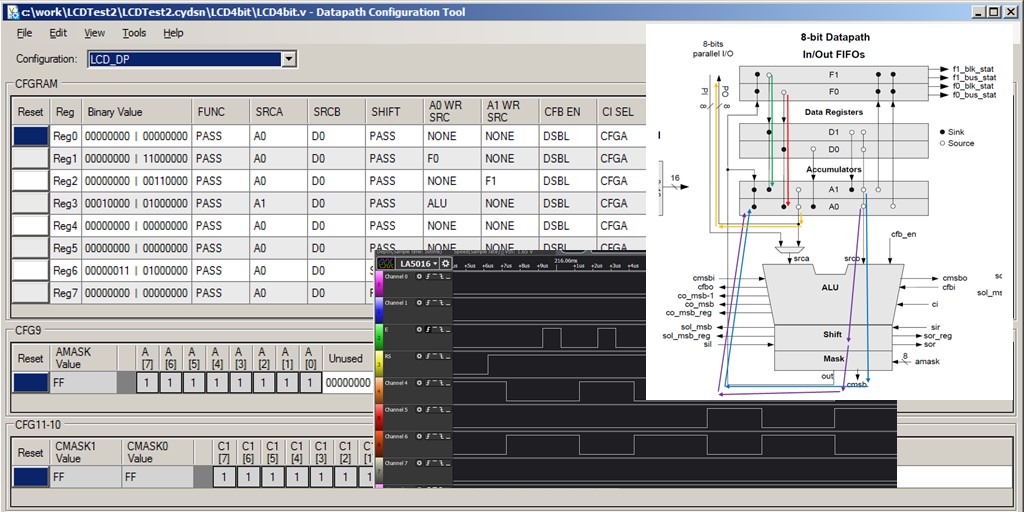

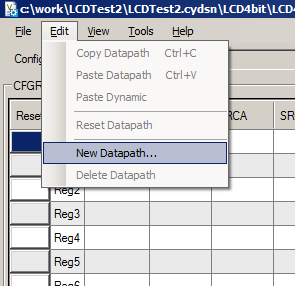

私たちの前にウィンドウが開きますが、今のところは部分的にしか表示しません。

愛してください、データパスエディター。 独自のドキュメントの翻訳で説明されたすべてのビットが含まれています。 しかし、これらのビットが非常に多いため、初期の頃は私は彼を見ましたが、何かをすることを恐れていました。 見て、見て、出て。 そしてしばらくして、それに慣れてから、彼は何かをしようとし始めました。 実際、それが私が窓の一部だけを持ってきた理由です。 なぜ事前にみんなを怖がらせるのですか? それまでは、データパスを作成する必要があるだけなので、メニュー項目[編集]- > [新しいデータパス ]を選択します。

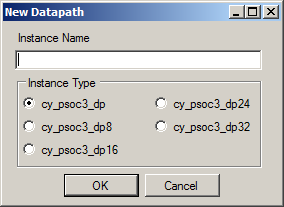

表示されるダイアログで選択するオプションはどれですか?

質問は見かけよりも少し深刻です。 次の段落をハイライトして、誰も捕まらないようにします(私は自分自身を捕まえて、私が得たものからネットワーク上の質問を見て、誰も実際に答えませんでした、そして答えはAN82156にあります、あなたはそこにあるようにそれを斜めに読む必要があります目立たない短いフレーズ)。

並列データを使用する場合は、オプションCY_PSOC3_DPを必ず選択する必要があります。 他のオプションには、パラレルデータを接続するためのポートは含まれません。だから。 インスタンスをLCD_DPと呼びます。

[OK]をクリックし、 データパス構成ツールを今すぐ閉じて、結果の保存に同意します。 後でここに戻ってきます。

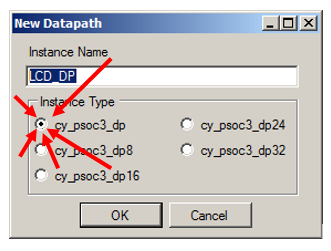

Verilogコードが拡張されました。 現在、データパスがあります。 彼の始まりは完全に読めない。 Datapath Config Toolによって構成されます。

そして、データパスの説明の終わりを決定します。 私たちのサイトはこんな感じ

(この時点から、すべてをテキスト形式にすることが理にかなっています)。

)) LCD_DP( /* input */ .reset(1'b0), /* input */ .clk(1'b0), /* input [02:00] */ .cs_addr(3'b0), /* input */ .route_si(1'b0), /* input */ .route_ci(1'b0), /* input */ .f0_load(1'b0), /* input */ .f1_load(1'b0), /* input */ .d0_load(1'b0), /* input */ .d1_load(1'b0), /* output */ .ce0(), /* output */ .cl0(), /* output */ .z0(), /* output */ .ff0(), /* output */ .ce1(), /* output */ .cl1(), /* output */ .z1(), /* output */ .ff1(), /* output */ .ov_msb(), /* output */ .co_msb(), /* output */ .cmsb(), /* output */ .so(), /* output */ .f0_bus_stat(), /* output */ .f0_blk_stat(), /* output */ .f1_bus_stat(), /* output */ .f1_blk_stat(), /* input */ .ci(1'b0), // Carry in from previous stage /* output */ .co(), // Carry out to next stage /* input */ .sir(1'b0), // Shift in from right side /* output */ .sor(), // Shift out to right side /* input */ .sil(1'b0), // Shift in from left side /* output */ .sol(), // Shift out to left side /* input */ .msbi(1'b0), // MSB chain in /* output */ .msbo(), // MSB chain out /* input [01:00] */ .cei(2'b0), // Compare equal in from prev stage /* output [01:00] */ .ceo(), // Compare equal out to next stage /* input [01:00] */ .cli(2'b0), // Compare less than in from prv stage /* output [01:00] */ .clo(), // Compare less than out to next stage /* input [01:00] */ .zi(2'b0), // Zero detect in from previous stage /* output [01:00] */ .zo(), // Zero detect out to next stage /* input [01:00] */ .fi(2'b0), // 0xFF detect in from previous stage /* output [01:00] */ .fo(), // 0xFF detect out to next stage /* input [01:00] */ .capi(2'b0), // Software capture from previous stage /* output [01:00] */ .capo(), // Software capture to next stage /* input */ .cfbi(1'b0), // CRC Feedback in from previous stage /* output */ .cfbo(), // CRC Feedback out to next stage /* input [07:00] */ .pi(8'b0), // Parallel data port /* output [07:00] */ .po() // Parallel data port );

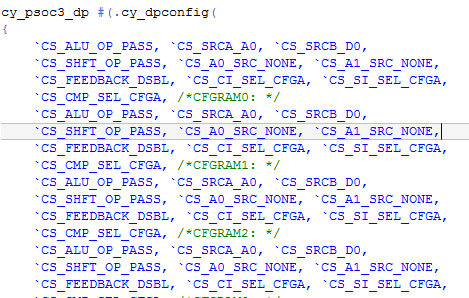

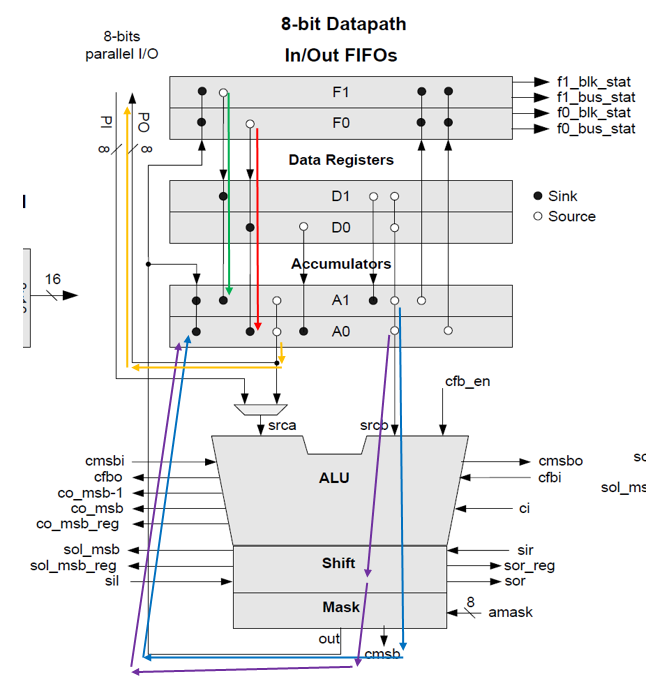

怖い 次に、何が何であるかを理解します-もう怖くない。 実際、このテキストには3つの異なるグループがあります。 ドキュメントの翻訳を思い出しましょう。 写真のデータパスはどのように見えましたか? 図では、グループ「1」、「2」、「3」が属する場所にすぐに注目します。

実際、verilogコードのポートの最初のグループは入力です。 入力マルチプレクサーの出力の名前(図の「1」)とコード内の信号の名前を比較します。

これで、すべての入力がゼロになりました。 クロック入力を接続する必要があり、UDBエディターで行われたように、最大6つの入力ラインを転送できます。 これらの入力は次のとおりです。

/* input */ .reset(1'b0), /* input */ .clk(1'b0), /* input [02:00] */ .cs_addr(3'b0), /* input */ .route_si(1'b0), /* input */ .route_ci(1'b0), /* input */ .f0_load(1'b0), /* input */ .f1_load(1'b0), /* input */ .d0_load(1'b0), /* input */ .d1_load(1'b0),

2番目のグループは出口です。 コード内の名前は、出力マルチプレクサー「2」の入力の名前とも一致します。

/* output */ .ce0(), /* output */ .cl0(), /* output */ .z0(), /* output */ .ff0(), /* output */ .ce1(), /* output */ .cl1(), /* output */ .z1(), /* output */ .ff1(), /* output */ .ov_msb(), /* output */ .co_msb(), /* output */ .cmsb(), /* output */ .so(), /* output */ .f0_bus_stat(), /* output */ .f0_blk_stat(), /* output */ .f1_bus_stat(), /* output */ .f1_blk_stat(),

指定されたDatapath種にのみ3番目のグループがあります(他にはないため、並列データはありません)。 これらは、内部データパス信号であり、これを介して独立してチェーンしたり、他の有用なアクションを実行したりできます。 コード内の名前は、図に散在する内部信号の名前とも一致しています。 それらのうちの1つ(リストの最後、彼の名前はpo )を介して、並列データをチップのレッグに直接出力します。

/* input */ .ci(1'b0), // Carry in from previous stage /* output */ .co(), // Carry out to next stage /* input */ .sir(1'b0), // Shift in from right side /* output */ .sor(), // Shift out to right side /* input */ .sil(1'b0), // Shift in from left side /* output */ .sol(), // Shift out to left side /* input */ .msbi(1'b0), // MSB chain in /* output */ .msbo(), // MSB chain out /* input [01:00] */ .cei(2'b0), // Compare equal in from prev stage /* output [01:00] */ .ceo(), // Compare equal out to next stage /* input [01:00] */ .cli(2'b0), // Compare less than in from prv stage /* output [01:00] */ .clo(), // Compare less than out to next stage /* input [01:00] */ .zi(2'b0), // Zero detect in from previous stage /* output [01:00] */ .zo(), // Zero detect out to next stage /* input [01:00] */ .fi(2'b0), // 0xFF detect in from previous stage /* output [01:00] */ .fo(), // 0xFF detect out to next stage /* input [01:00] */ .capi(2'b0), // Software capture from previous stage /* output [01:00] */ .capo(), // Software capture to next stage /* input */ .cfbi(1'b0), // CRC Feedback in from previous stage /* output */ .cfbo(), // CRC Feedback out to next stage /* input [07:00] */ .pi(8'b0), // Parallel data port /* output [07:00] */ .po() // Parallel data port );

だから。 作業中に、これらの入力と出力の一部を独自のエンティティに接続し、残りを作成する必要があります。作成したフォームにそのまま残してください。

UDB Editorを参照として使用する

そして今、私たちには空白があり、どこで何を書かなければならないかを知っています。 私たちがそこに何を入力するかを正確に理解することは残っています。 たまたま、私は毎日ではなくVerilog言語を使用しているので、一般的に言えば、すべてを覚えています。また、最初から書くのは常にストレスの多い状況です。 プロジェクトがすでに進行中のときは、すべてが記憶されていますが、2か月間何もしなかった後、ゼロから何かを始めると、もちろん、この特定の言語の構文の詳細を思い出せなくなります。 したがって、開発環境に助けを求めることをお勧めします。

自己監視用のUDBエディターは、Verilogコードをビルドします。 メイン回路に関係しないコンポーネントはコンパイルされないため、UDBエディターで補助コンポーネントを作成でき、出力コードには入りません。 そこでオートマトンを描画し、データパスの入力と出力の大まかな調整を行い、自動生成されたテキストをVerilogモジュールに転送して、すべてを創造的に変更します。 これは、Verilog構文の詳細を覚えてすべてを最初から書くよりもはるかに簡単です(ただし、Verilogを常に使用している人は、最初から書く方が確かに簡単です:すぐにわかるように、創造的な完了は簡単ですが、時間)。

そこで、補助コンポーネントを作成し始めます。 通常の手の動きで、プロジェクトに新しい要素を追加します。

これはUDBドキュメントになります。UDBhelperと呼びましょう。

作成されたシートに配置するマシンについて考えます。 これを行うには、どの時間ダイアグラムを使用して作成する必要があるかを考慮する必要があります。

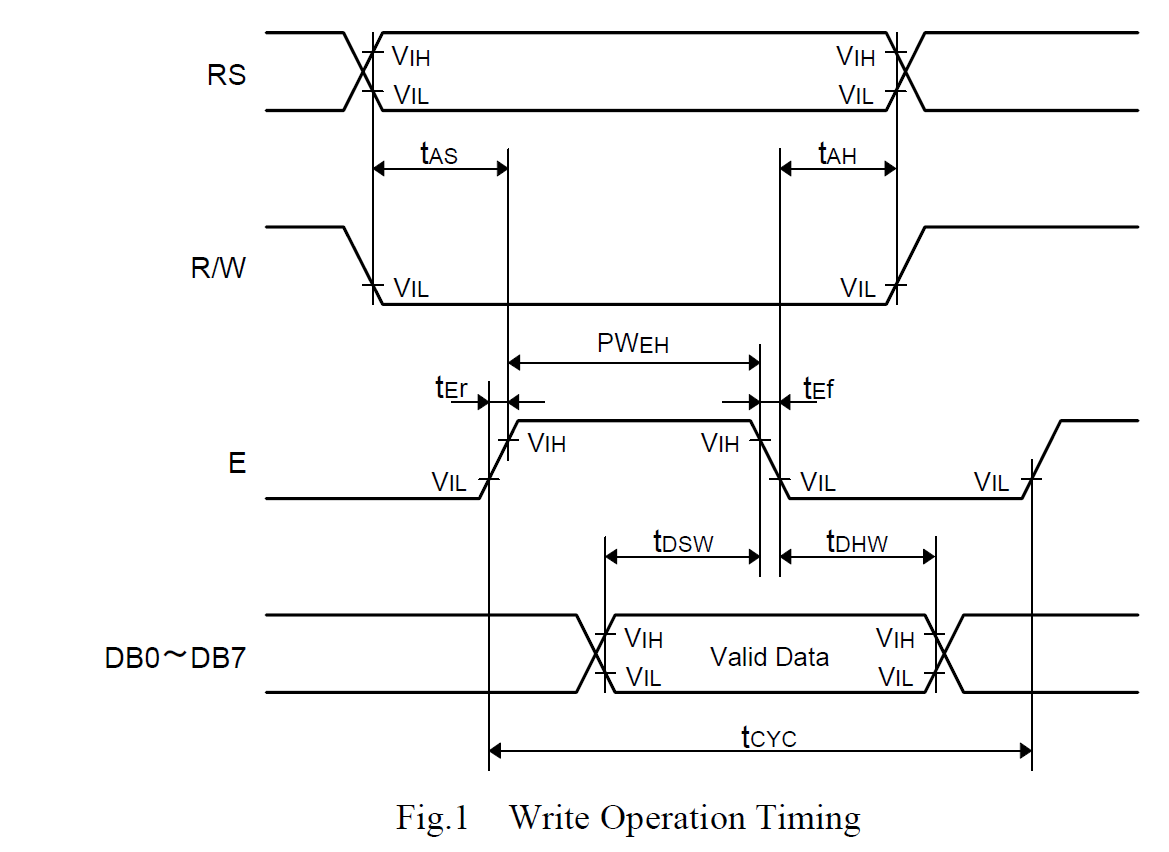

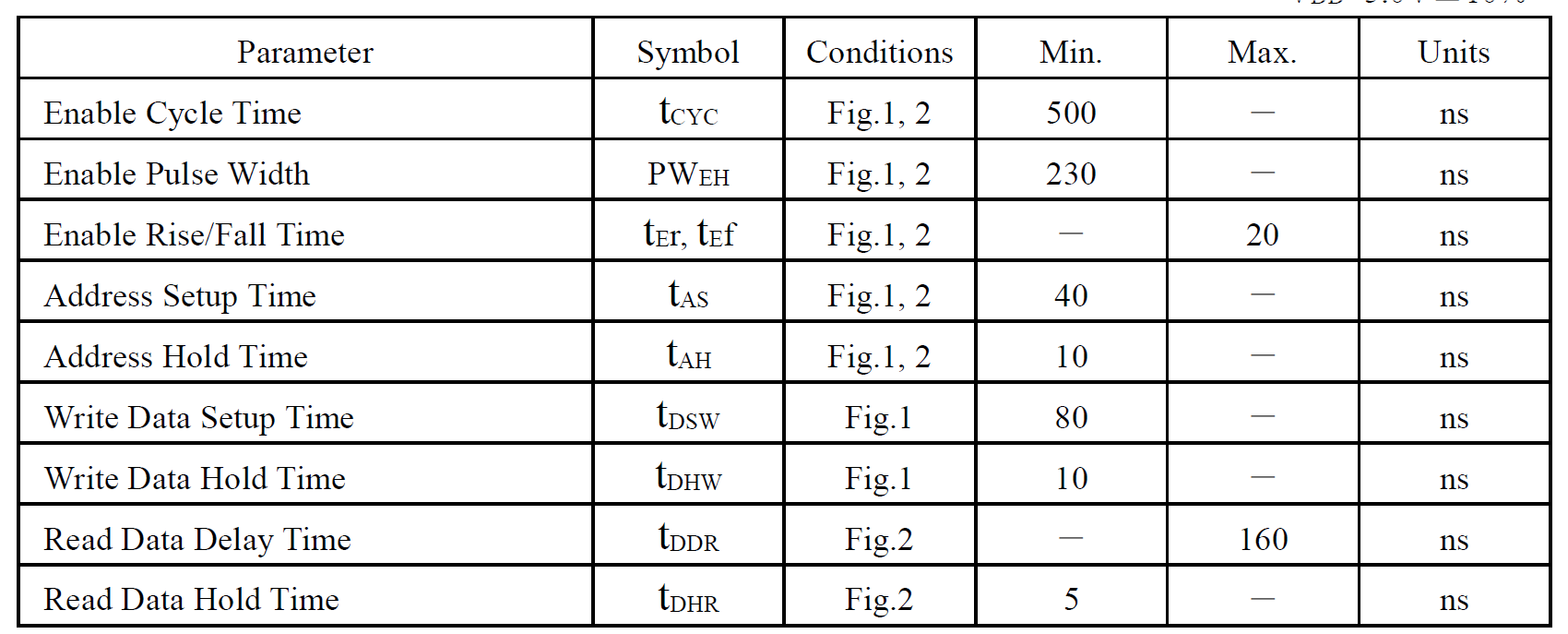

だから。 まず、RS信号を設定する必要があります(ハードウェアでR / Wがゼロにはんだ付けされているため)。 次に、tASを待ってから、信号Eを立ち上げてデータを設定します(Eの立ち上がりエッジでの設定データは制限されません)。 データはtDSW以上のバス上にある必要があり、その後、信号Eをドロップする必要があり、データは少なくともtDHWの間、RS上に少なくともtAHの間存在する必要があります。

RSはコマンドまたはデータフラグです。 RSがゼロの場合、データがあればコマンドが書き込まれます。

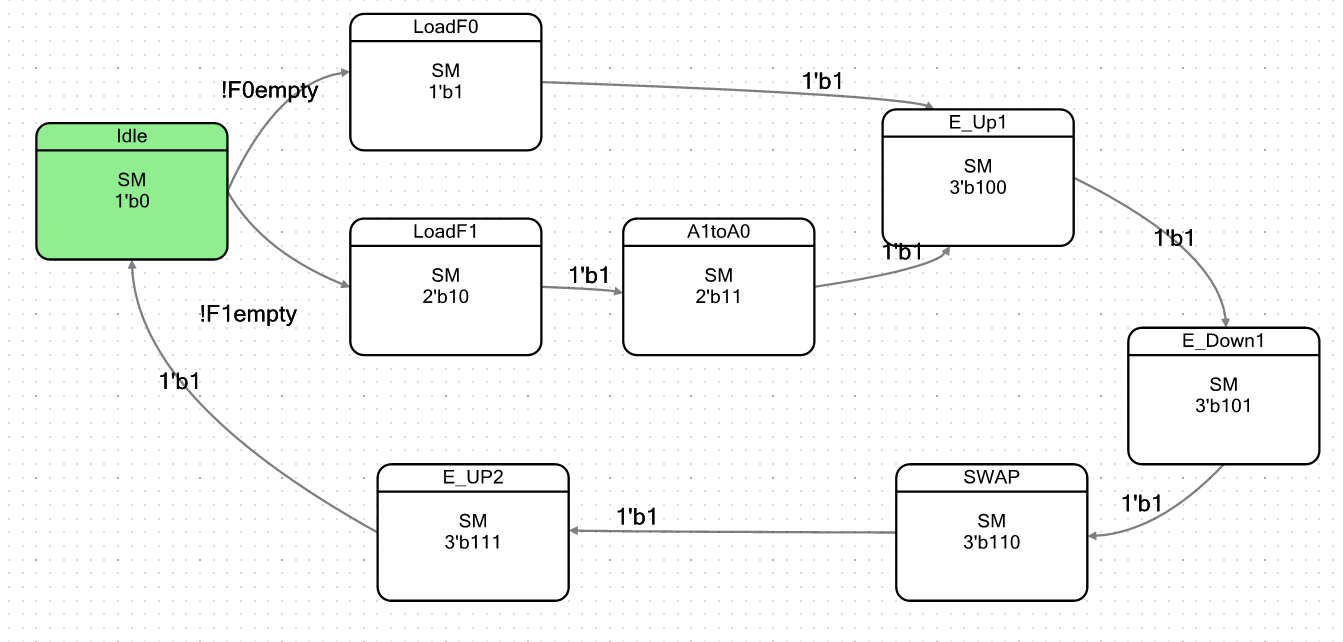

FIFO0経由でコマンドを送信し 、 FIFO1経由でデータを送信することをお勧めします。 現在のタスクのフレームワークでは、これは何にも矛盾しません。 次に、私が提案した有限状態マシンは次の形式になります。

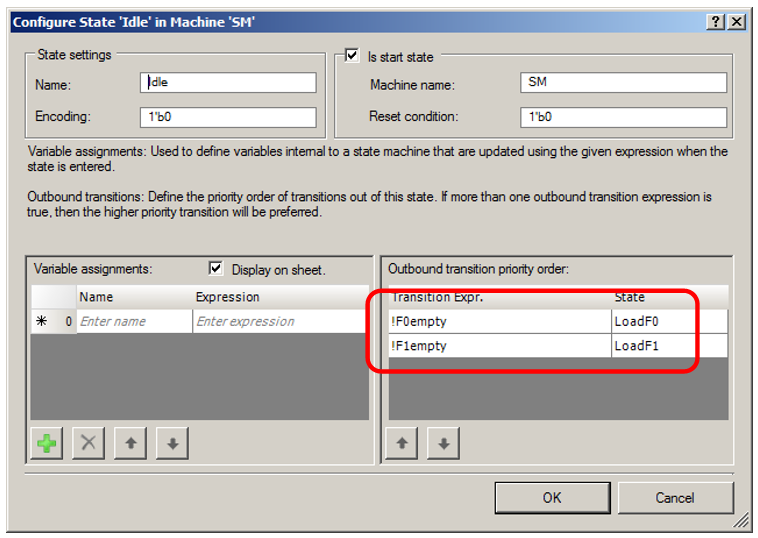

アイドル状態では、マシンにはまだFIFOデータがありません。 データがFIFO0に現れた場合、 LoadF0状態になり、将来、 FIFO0からA0にデータを受信します。

コマンドの送信中は、データを送信しないでください。 したがって、データを受信するための条件は、コマンドを受信するための条件よりも優先順位が低くなります。

データは、 LoadF1状態のA1で受信され( FIFO1からレジスタA1にのみ移動でき、レジスタA0に移動できません)、その後、状態A1toA0でA1からA0にコピーされます。

矢印の収束点にどのように移動しても、A0にデータがあります。 それらはすでにパラレルポートに出力されています。 Eをコック(状態E_UP1 )、ドロップE(状態E_DOWN1 )。 次に、ニブルを交換するための状態( SWAP )があり、その後Eが再び上昇します( E_UP2 )。 これで、3ビットでエンコードできる8つの状態を使い果たしました。 また、DatapathダイナミックコンフィギュレーションRAMには3つのアドレス入力しかありません。 いくつかのトリックを適用できますが、この記事はすでに大規模です。 したがって、2回目には、 アイドル状態でEをドロップします。 そして、8つの州で十分です。

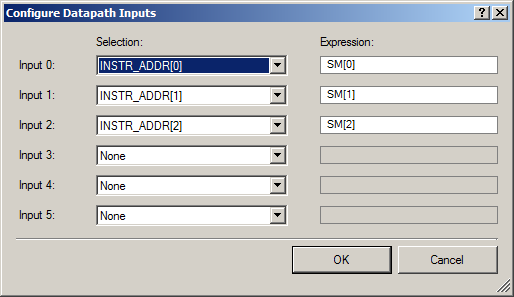

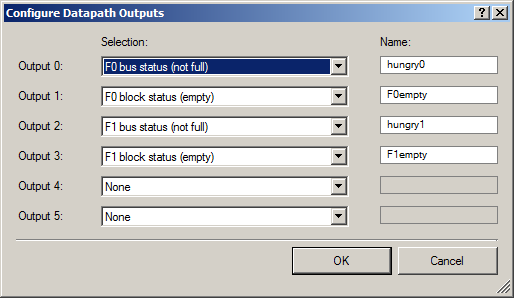

また、データパスをシートに配置し、以前の記事でおなじみの方法で入力と出力を割り当てます。 入力は次のとおりです。

出力は次のとおりです。

新しいことは何もありません。すべてはサイクルの以前の記事ですでに説明されています。 そのため、空白があり、それに基づいて独自の操作を実行できます。 確かに、すべてが順調であることを確認するには、システムをプロジェクトの最上位に移動する必要があります。そうしないと、エラーは検出されません。 そして、エラーのない最初の実験では失敗します。 したがって、もう1つの補助アクションを実行します。

回路の作成方法の説明は、UDBの操作の説明を超えています。 どのサーキットを手に入れたかをお見せします。 DMAユニットは1つしかありません。LCDにコマンドを送信するときは、大きな一時停止に耐える必要があるため、これをプログラムで行う方が簡単です。 他のアプリケーションの場合、 hungry0信号を使用して類推することにより、2番目のDMAブロックを配置することができます。

時間枠を正確に満たすために、1メガヘルツに等しいクロック周波数を選択しました。 周波数以上を使用することも可能ですが、データは干渉の多い状況で長いワイヤを介して送信されるため、ストロボの前後にデータを設定する時間は余裕を持って行う方が良いでしょう。 誰かが同じブレッドボードで私の実験を繰り返す場合は、ポートP3.2を使用しないでください。ボード上のこの脚にコンデンサがはんだ付けされています。 インパルスEを形成しなかった理由を発見するまで、私は30分殺しました。 私はそれをP3.1に投げました-それはすぐに機能しました。 私のデータバスはP3.7-P3.4に行き、RSはP3.3に行くので、Eは元々P3.2に行きました...

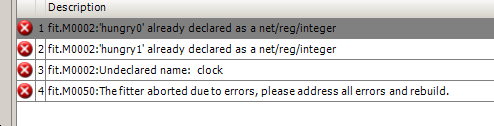

よくここに。 プロジェクトをコンパイルしようとすると、かなり予測可能なエラーが発生します

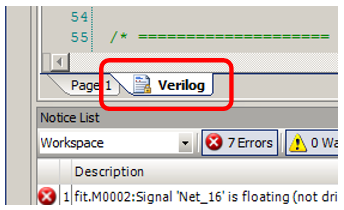

そのため、システムは何かを収集しようとしています。 しかし、彼女はまだ収集するものが何もありません。 コードのコピーに進みます。 これを行うには、UDB Editorの[Verilog]タブに切り替えます(このタブは、UDB Editorシートのウィンドウの下にあります)。

そこで何がおなじみですか? テキストの最後にオートマトンの本文があります。 それから移行を始めましょう。

また、データパスの下に配置します。

/* ==================== State Machine: SM ==================== */ always @ (posedge clock) begin : Idle_state_logic case(SM) Idle : begin if (( !F0empty ) == 1'b1) begin SM <= LoadF0 ; end else if (( !F1empty ) == 1'b1) begin SM <= LoadF1 ; end end LoadF0 : begin if (( 1'b1 ) == 1'b1) begin SM <= E_Up1 ; end end E_Up1 : begin if (( 1'b1 ) == 1'b1) begin SM <= E_Down1 ; end end E_Down1 : begin if (( 1'b1 ) == 1'b1) begin SM <= SWAP ; end end SWAP : begin if (( 1'b1 ) == 1'b1) begin SM <= E_UP2 ; end end E_UP2 : begin if (( 1'b1 ) == 1'b1) begin SM <= Idle ; end end LoadF1 : begin if (( 1'b1 ) == 1'b1) begin SM <= A1toA0 ; end end A1toA0 : begin if (( 1'b1 ) == 1'b1) begin SM <= E_Up1 ; end end default : begin SM <= Idle; end endcase end

このコードの上部には宣言があります(状態の名前、データパスのチェーン、オートマトンの状態をエンコードするレジスタ)。 適切な場所に転送します

コードのセクション:

/* ==================== Wire and Register Declarations ==================== */ localparam [2:0] Idle = 3'b000; localparam [2:0] LoadF0 = 3'b001; localparam [2:0] LoadF1 = 3'b010; localparam [2:0] E_Up1 = 3'b100; localparam [2:0] A1toA0 = 3'b011; localparam [2:0] E_Down1 = 3'b101; localparam [2:0] SWAP = 3'b110; localparam [2:0] E_UP2 = 3'b111; wire hungry0; wire F0empty; wire hungry1; wire F1empty; wire Datapath_1_d0_load; wire Datapath_1_d1_load; wire Datapath_1_f0_load; wire Datapath_1_f1_load; wire Datapath_1_route_si; wire Datapath_1_route_ci; wire [2:0] Datapath_1_select; reg [2:0] SM;

まあ、そして

シグナルバインディングサイトは移植可能です。

/* ==================== Assignment of Combinatorial Variables ==================== */ assign Datapath_1_d0_load = (1'b0); assign Datapath_1_d1_load = (1'b0); assign Datapath_1_f0_load = (1'b0); assign Datapath_1_f1_load = (1'b0); assign Datapath_1_route_si = (1'b0); assign Datapath_1_route_ci = (1'b0); assign Datapath_1_select[0] = (SM[0]); assign Datapath_1_select[1] = (SM[1]); assign Datapath_1_select[2] = (SM[2]);

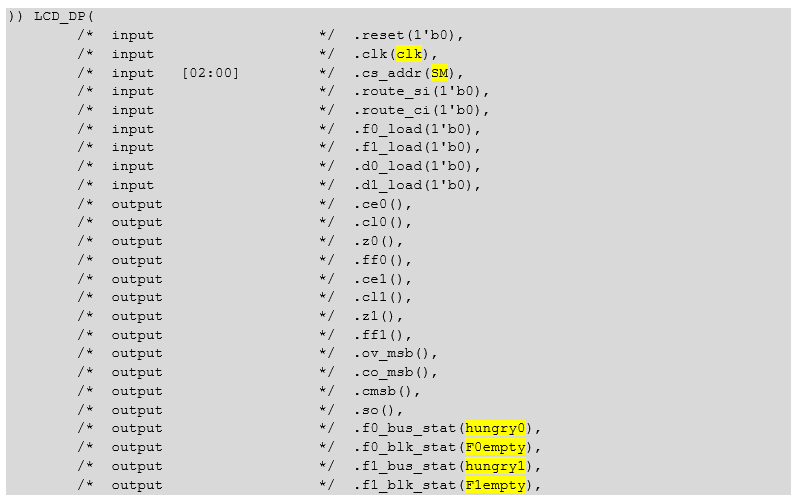

データパスをプラグインする時が来ました。 UDBエディターから移植されたコードは、マシンの編集には適していますが、手動の編集にはあまり適していません。 そこで、一方の端でデータパス入力に接続し、もう一方の端で定数に接続するチェーンが作成されます。 ただし、 データパス構成ツール (手動作業のすべてを行う)で作成されたコードでは、すべての入力が既にゼロ定数に直接接続されています。 したがって、定数ではない行のみを接続しますが、転送されたテキストから定数の転送に関連するすべてを切り取ります。 接続は次のようになりました(色は、データパス構成ツールで自動的に作成されたものに関して編集した場所を強調しています)。

同じテキスト:

)) LCD_DP( /* input */ .reset(1'b0), /* input */ .clk(clk), /* input [02:00] */ .cs_addr(SM), /* input */ .route_si(1'b0), /* input */ .route_ci(1'b0), /* input */ .f0_load(1'b0), /* input */ .f1_load(1'b0), /* input */ .d0_load(1'b0), /* input */ .d1_load(1'b0), /* output */ .ce0(), /* output */ .cl0(), /* output */ .z0(), /* output */ .ff0(), /* output */ .ce1(), /* output */ .cl1(), /* output */ .z1(), /* output */ .ff1(), /* output */ .ov_msb(), /* output */ .co_msb(), /* output */ .cmsb(), /* output */ .so(), /* output */ .f0_bus_stat(hungry0), /* output */ .f0_blk_stat(F0empty), /* output */ .f1_bus_stat(hungry1), /* output */ .f1_blk_stat(F1empty),

並列データはもう少し複雑です。 データパスには8ビットのポートがあり、そのうち4つだけを取り出す必要があります。 したがって、補助回路を起動し、その半分のみを出力に接続します。

wire [7:0] tempBus; assign LCD_D = tempBus[7:4];

そして、次のように接続します:

同じテキスト:

/* input [07:00] */ .pi(8'b0), // Parallel data port /* output [07:00] */ .po( tempBus) // Parallel data port );

アセンブルを試みます(Shift + F6またはメニュー項目Build-> Generate Applicationを使用 )。 エラーが発生します:

ポートhungry0およびhungry1 (コンポーネントを作成するときに表示される)と、同じ名前のチェーン(サンプルからドラッグするときに表示される)があります。 これらのチェーンを削除するだけです(ポートを残します)。 そしてどこかでクロック信号がリークし、 clkと呼ばれるこの回路があります。

すべての不要な回路(最初にDatapath入力にゼロ定数を投げた回路、およびhungry0およびhungry1 )を削除した後、ファイルの先頭に次のコードを取得します。

// Your code goes here /* ==================== Wire and Register Declarations ==================== */ localparam [2:0] Idle = 3'b000; localparam [2:0] LoadF0 = 3'b001; localparam [2:0] LoadF1 = 3'b010; localparam [2:0] E_Up1 = 3'b100; localparam [2:0] A1toA0 = 3'b011; localparam [2:0] E_Down1 = 3'b101; localparam [2:0] SWAP = 3'b110; localparam [2:0] E_UP2 = 3'b111; wire F0empty; wire F1empty; reg [2:0] SM; /* ==================== Assignment of Combinatorial Variables ==================== */ wire [7:0] tempBus; assign LCD_D = tempBus[7:4];

クロックをマシンの本体のclkに置き換えると、同時に自動生成に適したすべての行が破棄されますが、手動編集では混乱が生じるだけです(無条件の結果がTRUEとなるすべての比較など)。 特に、以下の例では、行の約半分を消すことができます(一部の開始/終了はオプションであり、アクションが追加されるため、必要になる場合があります)。

上記の原則に従ってコーミングした後(およびクロックをclkに置き換えた後)、そのようなボディは残ります

(短くなったため、読みやすくなりました):

always @ (posedge clk) begin : Idle_state_logic case(SM) Idle : begin if (( !F0empty ) == 1'b1) begin SM <= LoadF0 ; end else if (( !F1empty ) == 1'b1) begin SM <= LoadF1 ; end end LoadF0 : begin SM <= E_Up1 ; end E_Up1 : begin SM <= E_Down1 ; end E_Down1 : begin SM <= SWAP ; end SWAP : begin SM <= E_UP2 ; end E_UP2 : begin SM <= Idle ; end LoadF1 : begin SM <= A1toA0 ; end A1toA0 : begin SM <= E_Up1 ; end default : begin SM <= Idle; end endcase end

これで、コンパイル中に、 LCD_E回路とLCD_RS回路が接続されていないことがわかります。

実際、これは本当です:

ステートマシンにアクションを追加するときが来ました。 接続されていないチェーンに対応するポートの宣言をregに置き換えます。これは、マシンの本体に書き込むためです(これはVerilog言語の構文です。記述する場合、データをクリックします。トリガーが必要で、キーワードregで指定します )。

同じテキスト:

module LCD4bit ( output hungry0, output hungry1, output [3:0] LCD_D, output reg LCD_E, output reg LCD_RS, input clk );

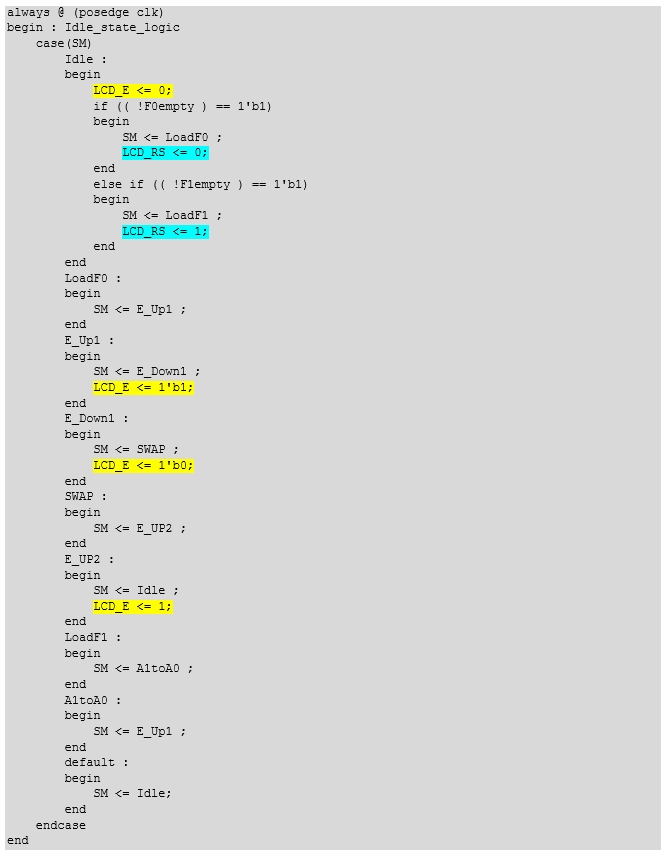

そして、マシンをアクションで満たします。 オートマトンの遷移グラフを検討しているときに、上記のロジックを既に話したので、結果のみを表示します。

同じテキスト:

always @ (posedge clk) begin : Idle_state_logic case(SM) Idle : begin LCD_E <= 0; if (( !F0empty ) == 1'b1) begin SM <= LoadF0 ; LCD_RS <= 0; end else if (( !F1empty ) == 1'b1) begin SM <= LoadF1 ; LCD_RS <= 1; end end LoadF0 : begin SM <= E_Up1 ; end E_Up1 : begin SM <= E_Down1 ; LCD_E <= 1'b1; end E_Down1 : begin SM <= SWAP ; LCD_E <= 1'b0; end SWAP : begin SM <= E_UP2 ; end E_UP2 : begin SM <= Idle ; LCD_E <= 1; end LoadF1 : begin SM <= A1toA0 ; end A1toA0 : begin SM <= E_Up1 ; end default : begin SM <= Idle; end endcase end

この瞬間から、プロジェクトの組み立てが始まります。 しかし、彼はまだ働きません。 これまで私は有名に言っていました:「この状態では、FIFOからレジスタをロードします」、「A1はこれでA0にコピーします」、「ニブルはこれでスワップされます」。 一般に、私は多くのことを話しましたが、これまでのところ何の行動もありませんでした。 それらを実現する時が来ました。 状態がどのようにエンコードされたかを調べます。

localparam [2:0] Idle = 3'b000; localparam [2:0] LoadF0 = 3'b001; localparam [2:0] LoadF1 = 3'b010; localparam [2:0] E_Up1 = 3'b100; localparam [2:0] A1toA0 = 3'b011; localparam [2:0] E_Down1 = 3'b101; localparam [2:0] SWAP = 3'b110; localparam [2:0] E_UP2 = 3'b111;

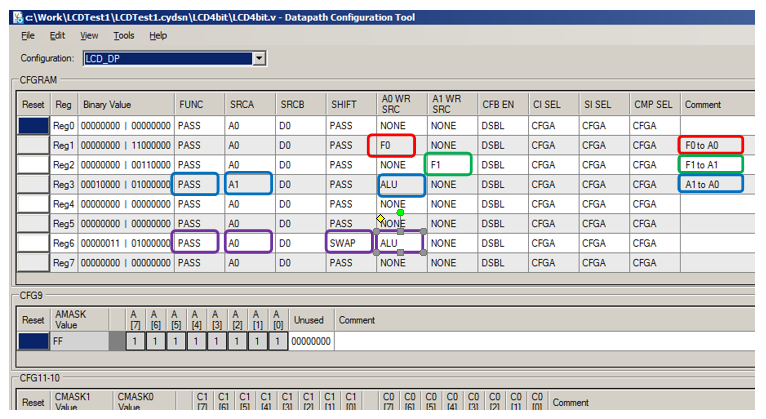

データパス構成ツールを再度開きます。

そして、 CFGRAM行の編集を開始します。 編集するときは、Datapathスキーム、つまり次のことに注意してください。

下の図の赤いフレーム(および上の図の矢印)では、状態LoadF0 (コード001、つまりReg1 )の修正済み領域(およびデータパス)を強調表示しています。 コメントも手動で入力しました。 F0の内容はA0に入るはずです。

緑色のフレームと矢印で、LoadF1の状態の設定とパスをマークしました(コード010- Reg2 )。

青いフレームと矢印を使用して、状態A1toA0(コード011- Reg3 )の設定とパスをマークしました。

紫色のフレームと矢印は、SWAPの状態の設定とパスをマークしました(コード110- Reg6 )。

最後に、オレンジ色の矢印は並列データパスを示しています。 そして、彼らのために行動は取られません。 彼らはいつもSRCAから出てきます。 ほとんどの場合、 SRCAとしてA0が選択されています。データはA0から取得されます。 そのため、入力データをリダイレクトするには、多くの補助アクションを実行する必要がありますが、データを受け入れないため、ここではこれらのアクションは不要で、全員がAN82156でリストを見つけます。 また、静的なデータパス設定を編集する必要がないため、 データパス構成ツールを閉じます。

それだけです 想定されるハードウェアが完成しました。 Cコードの開発を始めましょう。 これを行うには、「 ソース」タブに移動して、 main.cファイルを編集します。

通常のLCD初期化と「ABC」文字出力は次のようになります(コマンドはFIFO0に行き、ドキュメントはチーム間に休止を挿入する必要があり、データはFIFO1に行くことを思い出します、データ間の休止については何も見つかりませんでした):

volatile uint8_t* pFIFO0 = (uint8_t*) LCD4bit_1_LCD_DP__F0_REG; volatile uint8_t* pFIFO1 = (uint8_t*) LCD4bit_1_LCD_DP__F1_REG; pFIFO0[0] = 0x33; CyDelay (5); pFIFO0[0] = 0x33; CyDelay (100); pFIFO0[0] = 0x33; CyDelay (5); pFIFO0[0] = 0x20; CyDelay (5); pFIFO0[0] = 0x0C; // CyDelay (50); pFIFO0[0] = 0x01; // CyDelay (50); pFIFO1[0] = 'A'; pFIFO1[0] = 'B'; pFIFO1[0] = 'C';

なに 画面に最初の文字だけがあるのはなぜですか?

また、データ出力の間に遅延を追加すると、すべてがうまくいきます:

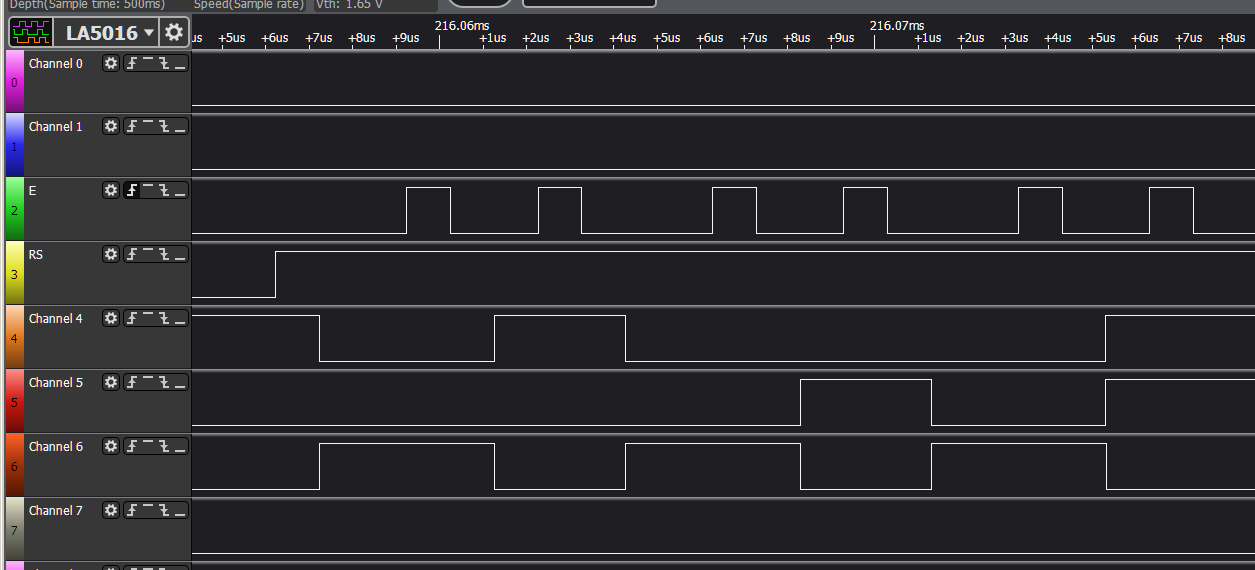

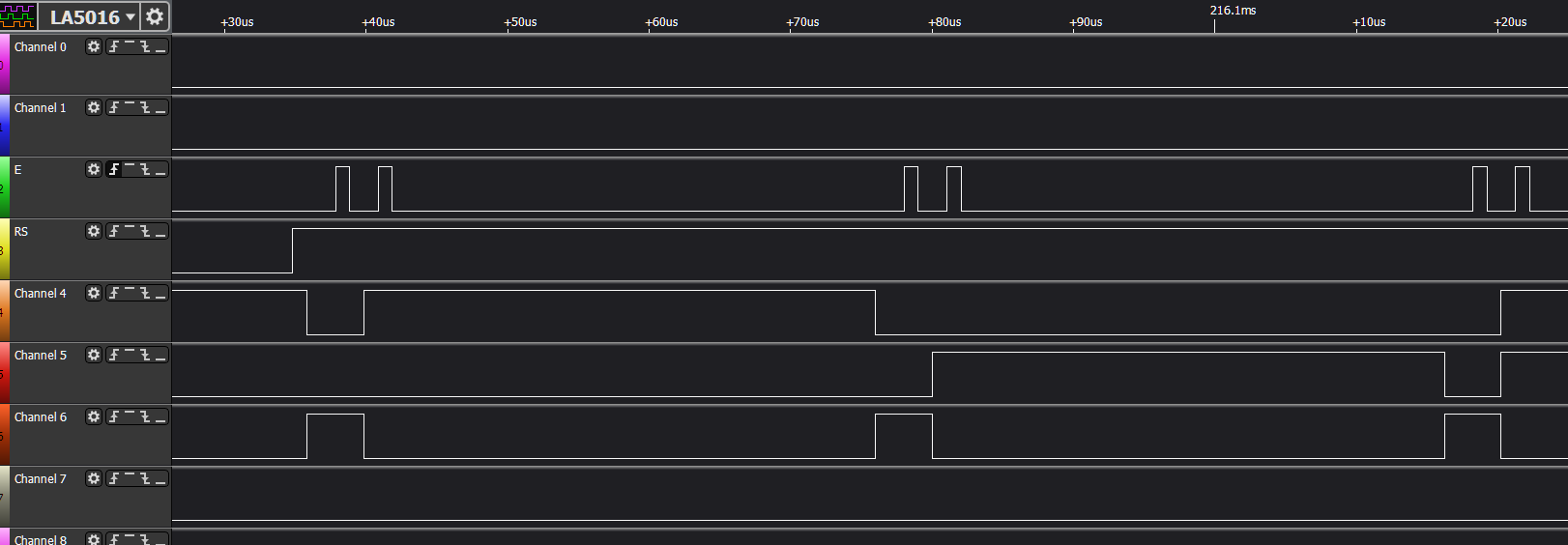

オシロスコープには、このような作業に十分なチャンネルがありません。 論理アナライザーで作業を確認します。 データ記録プロセスは次のとおりです。

すべてのデータが配置されています(パッケージの3つのペア)。 インストールとスナップデータの時間が十分なボリュームに割り当てられます。 一般に、タイムダイアグラムの観点からは、すべてが正しく行われます。 科学的な問題は解決され、希望の時間図が形成されます。 ここにエンジニアリングがあります-いいえ。 これは、LCDに取り付けられたプロセッサの速度が遅いためです。 バイト間に遅延を追加します。

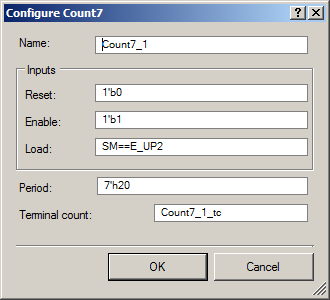

7ビットカウンターを使用して遅延を形成し、同時にこのようなシステムに追加するようにトレーニングします。 一定時間以上アイドル状態にすると、7ビットカウンターがこの時間を測定します。 繰り返しますが、コードを作成するのではなく、作成します。 したがって、再びUDBエディターの補助コンポーネントに移動して、カウンターをワークシートに追加し、そのパラメーターを次のように設定します。

このカウンタは常に機能します( 有効化は 1に設定されます)。 しかし、マシンがE_UP2状態になったときにロードされます(その後、すぐにアイドル状態になります)。 カウンタがゼロにカウントされると、 Count7_1_tc行が1に引き上げられます。これにより、 アイドル状態を終了するための追加条件が作成されます。 この図には期間の値も含まれていますが、Verilogコードには含まれていません。 Cコードに入力する必要があります。 ただし、最初に、[Verilog]タブに切り替えて、自動生成されたVerilogコードを転送します。 まず、カウンターを接続する必要があります(このコードはファイルの先頭にあり、先頭にも移動しています)。

`define CY_BLK_DIR "$CYPRESS_DIR\..\psoc\content\CyComponentLibrary\CyComponentLibrary.cylib\Count7_v1_0" `include "$CYPRESS_DIR\..\psoc\content\CyComponentLibrary\CyComponentLibrary.cylib\Count7_v1_0\Count7_v1_0.v"

線と定数の創造的な洗練がどのように実行されるかはすでに説明されているので、結果を示します。 結果として追加されたチェーンと割り当てを次に示します(残りは定数を設定するため、それらを破棄しました)。

wire Count7_1_load; wire Count7_1_tc; assign Count7_1_load = (SM==E_UP2);

そして、ファイルの最後に置かれたカウンター自体がここにあります。 すべての定数は、この宣言でポートに直接割り当てられます。

Count7_v1_0 Count7_1 ( .en(1'b1), .load(Count7_1_load), .clock(clk), .reset(1'b0), .cnt(), .tc(Count7_1_tc)); defparam Count7_1.EnableSignal = 1; defparam Count7_1.LoadSignal = 1;

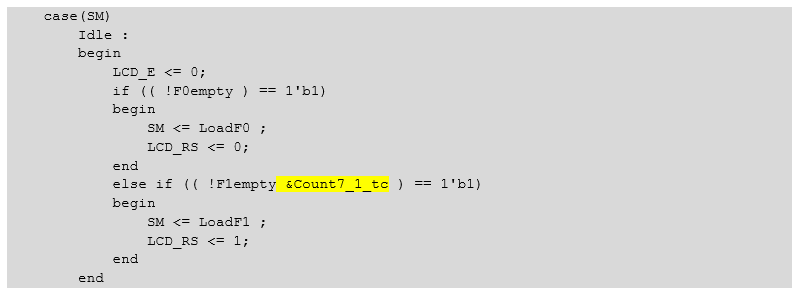

このカウンターを機能させるために、 アイドル状態を終了するための追加条件を自動的に追加します。

同じテキスト:

case(SM) Idle : begin LCD_E <= 0; if (( !F0empty ) == 1'b1) begin SM <= LoadF0 ; LCD_RS <= 0; end else if (( !F1empty &Count7_1_tc ) == 1'b1) begin SM <= LoadF1 ; LCD_RS <= 1; end end

この方法で追加されたカウンターのAPIは作成されないため、 メイン関数に2つの魔法の行を追加します。これは、過去のプロジェクトのAPIで見たもののイメージと似ています(最初の行はアカウントのロード値、同じロード、2番目はカウンターを開始します):

*((uint8_t*)LCD4bit_1_Count7_1_Counter7__PERIOD_REG) = 0x20; *((uint8_t*)LCD4bit_1_Count7_1_Counter7__CONTROL_AUX_CTL_REG) |= 0x20; // Start

アナライザーは、変更された場合に遅延が明らかであることを示します。

LCDにも3つの文字すべてがあります。

しかし、実際のプログラムでの文字出力は受け入れられません。 FIFOに追加するだけでオーバーフローします。FIFOが空になるまで待ちます-これは、プロセッサコアに大きな遅延を作成することを意味します。プロセッサは72 MHzの周波数で動作し、データは1 MHzの周波数で7〜8クロックサイクル出力されます。したがって、実際には、テキストはDMAを使用して表示する必要があります。これは、「起動して忘れてしまった」原則が役立つ場所です。タイミング図のすべての遅延はUDBによって生成され、DMAコントローラーはデータを受信するためのFIFOの準備を決定します。プロセッサコアは、メモリにラインを形成し、DMAを構成するためにのみ必要です。その後、LCDへの出力を気にせずに他のタスクを実行できます。

次のコードを追加します。

static const char line[] = "This is a line"; /* Defines for DMA_D */ #define DMA_D_BYTES_PER_BURST 1 #define DMA_D_REQUEST_PER_BURST 1 /* Variable declarations for DMA_D */ /* Move these variable declarations to the top of the function */ uint8 DMA_D_Chan; uint8 DMA_D_TD[1]; /* DMA Configuration for DMA_D */ DMA_D_Chan = DMA_D_DmaInitialize(DMA_D_BYTES_PER_BURST, DMA_D_REQUEST_PER_BURST, HI16(line), HI16(LCD4bit_1_LCD_DP__F1_REG)); DMA_D_TD[0] = CyDmaTdAllocate(); CyDmaTdSetConfiguration(DMA_D_TD[0], sizeof(line)-1, CY_DMA_DISABLE_TD, CY_DMA_TD_INC_SRC_ADR); CyDmaTdSetAddress(DMA_D_TD[0], LO16((uint32)line), LO16((uint32)LCD4bit_1_LCD_DP__F1_REG)); CyDmaChSetInitialTd(DMA_D_Chan, DMA_D_TD[0]); CyDmaChEnable(DMA_D_Chan, 1);

画面には次のものがあります。

おわりに

半合成ですが、実際のタスクに近い例では、代替メカニズムであるDatapath Config Toolを使用して、UDBのコードを開発するメカニズムを習得しました。このメカニズムは、UDBエディターとは異なり、完全にすべてのUDB管理機能へのアクセスを提供しますが、UDBエディターを使用した場合よりも作業が複雑になります。それでも、この記事の著者が提案した方法では、コードをゼロから作成するのではなく、同じUDBエディターで作成された補助コードに依存して単純に作成できます。

記事を書いたときに得られたテストプロジェクトはここで取ることができます。