サイプレスのサイプレスUDBマイクロコントローラーを使用してRGB LEDを制御することに関する私の記事へのコメントで、 記事の冒頭でUDBとは何かを簡単に伝えるとよいと示唆されました。 この記事で既に述べたように、UDBについて簡単に説明することはできませんが、ファームウェアの機能を実装するための強力なツールに国内の読者を慣れさせるために、会社のドキュメントを簡単に転送できます。

しかし最初に、PSoCが何であるかを見てみましょう。 PSoCは、オンチップシステムを実装するためのチップセットのサイプレスファミリです。 異なるファミリには異なるプロセッサコアがあります(PSoC 3の場合はMCS-51、PSoC 4の場合はCortex M0、PSoC 5LPの場合はCortex M3、PSoC 6の場合は一度に2つです:Cortex M0 +およびCortex M4)。 さらに、このロジックは純粋にデジタルではなく、アナログのものがあります。 異なるADCのセットに加えて、アナログスイッチもあります。 アナログ回路を介してプログラムで脚を接続することもできますが、回路の抵抗はキログラム単位で測定されます。 PSoC内には、プログラムで切り替えることができるオペアンプがあります。これは、異なるアナログブロックを構築することを意味します。

ちなみに、PSoCは2.7〜5.5ボルトの任意の電圧で駆動できます。 つまり、バッテリー電源またはUSB電源のいずれかの安定装置について考える必要はありません。

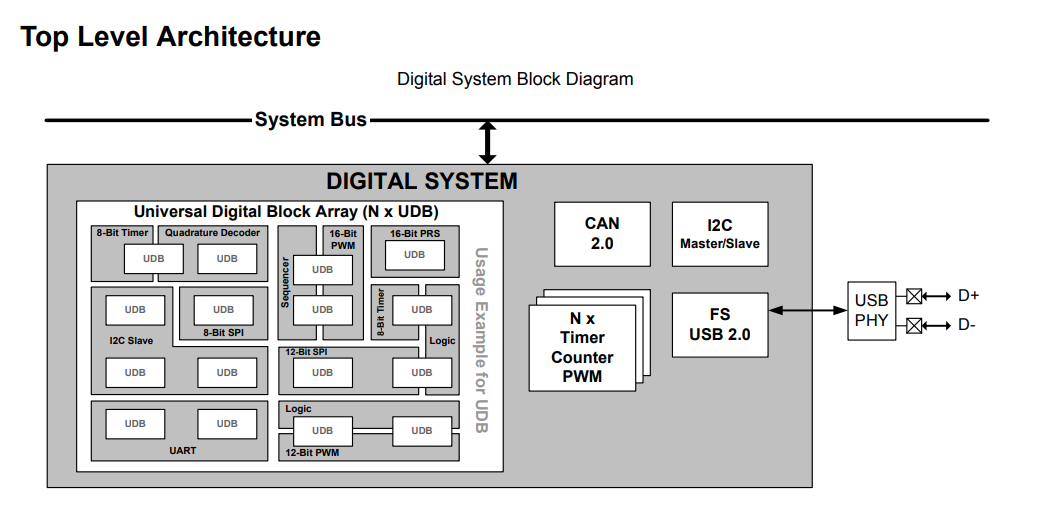

しかし、アナログのことについては、純粋に赤い言葉のために書きました。 次に、デジタルに焦点を当てます。 最新のコントローラーのほとんどには、非常に多様な機能を提供する強力な周辺ユニットがあります。 しかし実際には、特定の各ソフトウェア開発では、これらのブロックは完全には使用されず、部分的にしか使用されません。 また、PSoCでは、従来のFPGAのロジックと同様に、多くの優れたプログラムロジックではなく、プログラムロジックが実装されています。 したがって、必要なモードにブロックを含めることにより、必要なブロックを正確に実装できます。 そして、リソースは未使用のモードに費やされるべきではなく、何らかの独自のものの実装のためにそれらを解放するべきです。

そして、ここでしばしば誤解が生じます。 多くの開発者は、CPLDとFPGAの2種類のプログラマブルロジック集積回路(FPGA)があることに慣れています。 したがって、PSoCについて聞いた多くの人は、VeriolgでプログラムできるCPLDボックスのようなものがあると信じています。 実際、はい、いいえ。 特定の数のPLD(「C」なし、PLDのみ)が実際にあり、Verilogで実際にプログラムできます。 しかし、実際には、これらのPLDはUDBブロックの一部です。 そして、PSoCに実装されているプログラマブルロジックの主要な要素はUDBです。 このブロックは非常に独創的であり、開発者に最も幅広い機会を提供します。 UDBブロックの使用の本質を説明する独自のドキュメントの図を検討してください。

例としてPSoC 5LPファミリを使用してすべてを勉強したので、ドキュメントをそれに翻訳します。 しかし、開始する前に、これらのコントローラーの価格について少し説明します。 アリエクスプレスに行って、彼らのためにブレッドボードを見ると、あなたは悲しい気持ちになります。 率直に言って、STM32-DISCOVERYと比較すると、それらはまだ何もありませんが、STM32F103C8T6プロトタイプと比較すると、少し高価です。 まず、これは企業のモックアップには常に1つではなく、2つのそのようなコントローラーがあるという事実によるものです。 JTAG機能は、ターゲットコントローラーとPSoC 4(通常はUSBポートを持たない)であっても、PSoC 5LPに実装されます。

しかし、価格を2で割ると、プロセッサコアで似ているSTM32F103よりも高いことがわかります。 それでも、外部から最も単純なCPLDでさえSTM32に追加すると、合計価格はすでにPSoCに利益をもたらします。 そして、これらの2つのケースの接続に失われたレッグを追加します(PSoCはすべての接続を内部に持っています)。 また、ボードの平方センチメートルの価格。 したがって、プロセッサコアでのみ作業する必要がある場合、PSoCは実際には必要ないことがわかります。 ファームウェアまたはハードウェアレベルに機能を追加する必要がある場合は、PSoCが必要です。 その上で、システムはより安価で簡単になります。

実際、RTOS MAXのカーネルのハードウェアサポートを作成しようとするman病な考えがあります。 これを行うために、アルテラV SoC用のベアメタルアプリケーションを開発するための方法論を研究しました(また、アーキテクチャ機能はOSの速度を落とすことができますが、速度を上げることはできません。 このために、私はPSoCを習得し始めました。 カーネルのオーバークロックにはまだ到達していません(一般的な考えしかありません)が、UDBのプログラミングのアイデアは本当に気に入りました。 もちろん、私は今、このアイデアを国内のプログラマーの最大数にもたらすことに興味があります。 したがって、UDP上のサイプレス独自のドキュメントの対応する部分の翻訳に進みます。 元の文書に従って、章と図の番号を保持します。

サイクルの一般的な内容「UDB。 これは何ですか?」

パート1.はじめに。 Pld。 (現在の記事)

パート2.データパス。

パート3.データパスFIFO。

パート4.データパスALU。

パート5.データパス。 有用なささいなこと。

パート6.管理およびステータスモジュール。

パート7.タイミングとリセット制御モジュール

パート8. UDBのアドレス指定

UDB。 これは何? パート1

21.ユニバーサルデジタルブロック

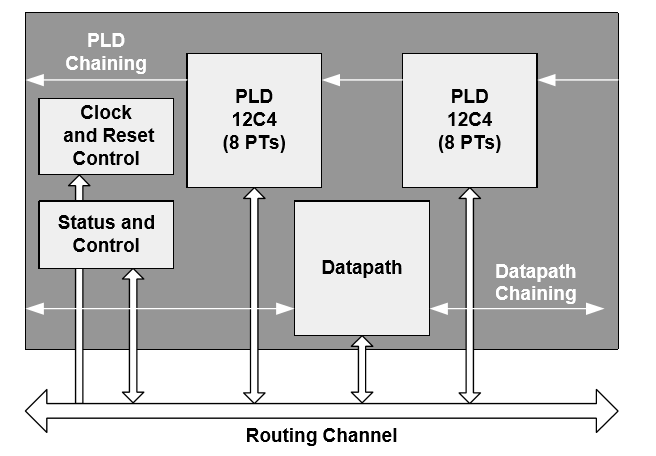

この章では、ユニバーサルデジタルブロック(UDB)がプログラム可能なデジタルペリフェラル機能の開発を可能にする方法について説明します。 UDBアーキテクチャは、構成の粒度と効率的な実装のバランスを取ります。 UDBは、プログラマブルロジックマトリックス(PLM、英語PLD)に似た非変換ロジック、構造化ロジック(操作オートマトン、以下-データパス)、および柔軟なトレーススキームの組み合わせで構成されています。

21.1機能

- 最適な柔軟性のために、各UDBには次のコンポーネントが含まれています。

•8ワード命令、複数のレジスタ、FIFOバッファのストレージを備えたALU(算術論理演算ユニット、ALU)に基づく8ビットデータパス。

•2つのPLD。それぞれに12の入力、8つの連言用語(製品用語、PT)、および4つのマクロセル出力があります。

•管理およびステータスレジスタ。

•クロックおよびリセットモジュール。 - PSoC 5LPには、最大24 UDBのサイズのアレイが含まれています。

- UDB配列要素間の柔軟なトレース。

- UDB要素を分割または連鎖して、より大きな関数を作成できます。

- タイマー、カウンター、パルス幅変調器(デッドバンドジェネレーター付きのPWMを含む)、UART、I2Cバス、SPIバス、CRC検証/生成など、多数のデジタル機能の柔軟な実装。

21.2ブロック図

図21-1は、2つの基本的な論理ブロック、PLD、データパス、および制御、ステータス、クロック、およびリセット機能を含む構成としてのUDBを示しています。

図21-1。 UDBのブロック図。

21.3仕組み

UDBの主なコンポーネントは次のとおりです。

- PLD(2)。 これらのブロックからの入力には、トレースリソースからのデータが供給されます。 組み合わせロジックとデータスナップを実装します。これにより、有限状態マシンの実装、Datapathブロックの操作の制御、入力条件の構成、出力の制御が可能になります。

- データパス。 このブロックには、動的にプログラム可能なALU、4つのレジスタ、2つのFIFOバッファ、コンパレータ、条件生成が含まれます。

- 管理とステータス(ステータスとコントロール)。 これらのモジュールは、中央処理装置(CPU)のマイクロプログラムとUDB操作との同期のためのメカニズムを提供します。 制御レジスタは内部要素に作用し、ステータスレジスタは外部要素のステータスを読み取ります。

- クロックおよびリセット制御 これらのモジュールは、UDB内のリセットの選択と同様に、タイミングの選択と組み込みを提供します。

- シグナルの連鎖。 PLDおよびDatapathには、チェーン内の隣接するブロックをチェーン接続して高ビット関数を作成できる信号があります。

- トレースチャネル UDBは、同じUDB内のブロック間の通信およびアレイ内の他のUDBとの通信のために、プログラム可能なスイッチングマトリックスを介してトレースチャネルに接続されます。

- システムバスインターフェイス(システムバスインターフェイス)。 各UDBのすべてのレジスタとRAMはシステムアドレス空間に投影され、中央プロセッサまたはダイレクトメモリアクセス(英語のダイレクトメモリアクセス、DMA)を使用して8ビットおよび16ビットの形式でアクセスできます。データ。

21.3.1。 Pld

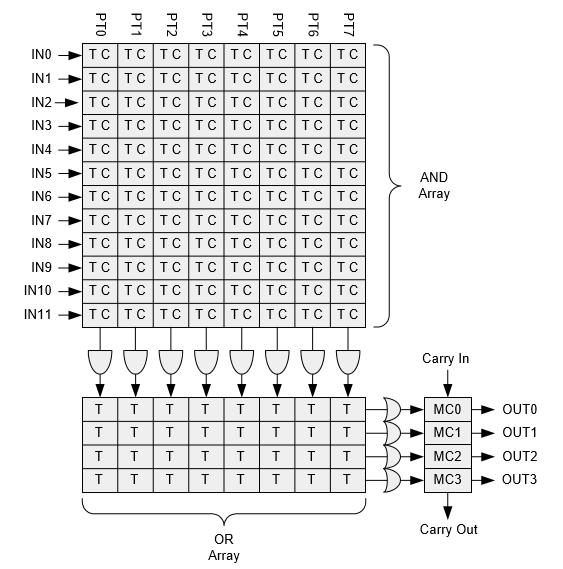

各UDBには2つの12C4 PLDがあります。 図21-1に示すPLDブロックは、ステートマシンの実装、I / Oデータの処理、およびテーブルロジック(Eng。Lookup Table、LUT)の作成に使用できます。 さらに、算術機能を実行し、データパスシーケンスを設定し、ステータスを生成するようにPLDを構成できます。 一般的なロジックを合成し、PLDブロックに投影できます。 このセクションでは、PLDアーキテクチャの概要を説明します。

PLDには、情報をAND配列の8つの連言項に送信する12個の入力があります。 各接続用語では、直接入力(true、T)または逆入力(補数、C)を選択できます。 連言項の出力は、OR配列の入力に送られます。 12C4の文字「C」は、OR項がすべての入力に対して一定であり、各OR入力が接続語にプログラムでアクセスできることを示しています。 この構造は最大限の柔軟性を提供し、すべての入力および出力を移動できるようにします。

図21-2。 PLD 12C4の構造。

21.3.1.1マクロセルPLD

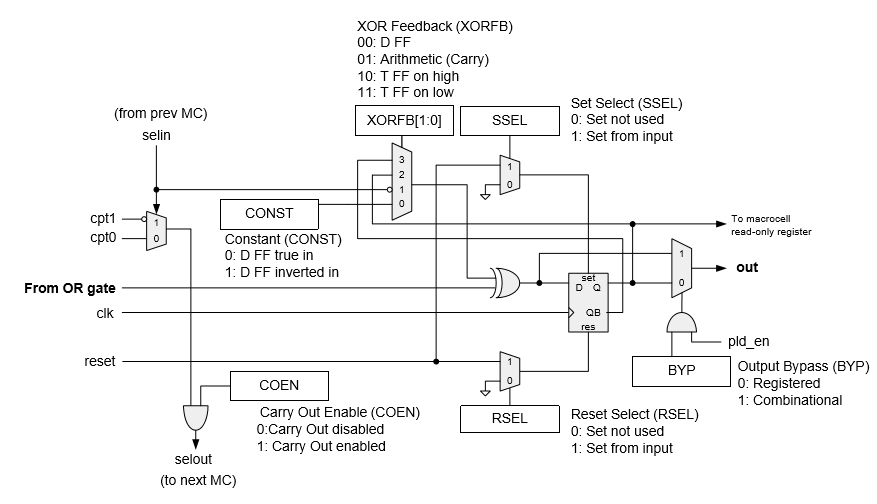

マクロセルのアーキテクチャを図21-3に示します。 出力はトレース配列を制御し、ラッチまたはラマンすることができます。 ラッチには、直接または逆入力のDトリガーまたは高または低入力レベルのTトリガーが使用されます。 出力トリガーは、初期化中に、または通常動作中に非同期で、トレースチャネルからの外部信号によって設定またはリセットできます。

図21-3。 マクロセルのアーキテクチャ。

読み取り専用PLDマクロセルレジスタ

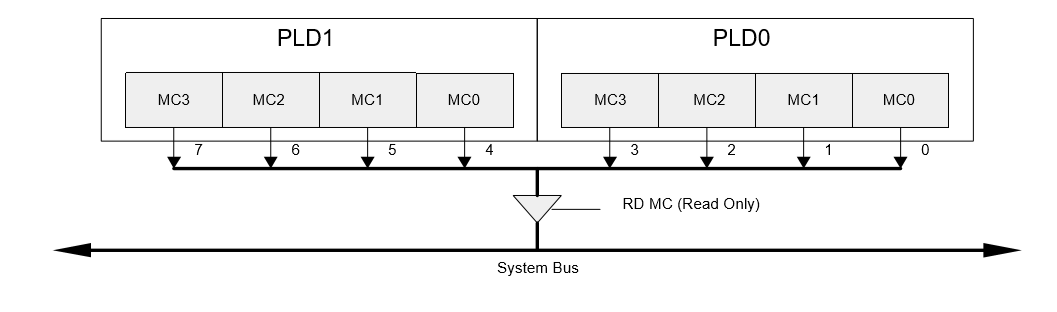

トレースアレイの制御に加えて、両方のPLDのマクロセル出力は、CPUまたはDMAを使用してアクセスできる8ビットの読み取り専用レジスタの形式でアドレス空間に投影されます。

図21-4。 読み取り専用PLDマクロセルレジスタ。

21.3.1.2ハイフネーションチェーンPLD

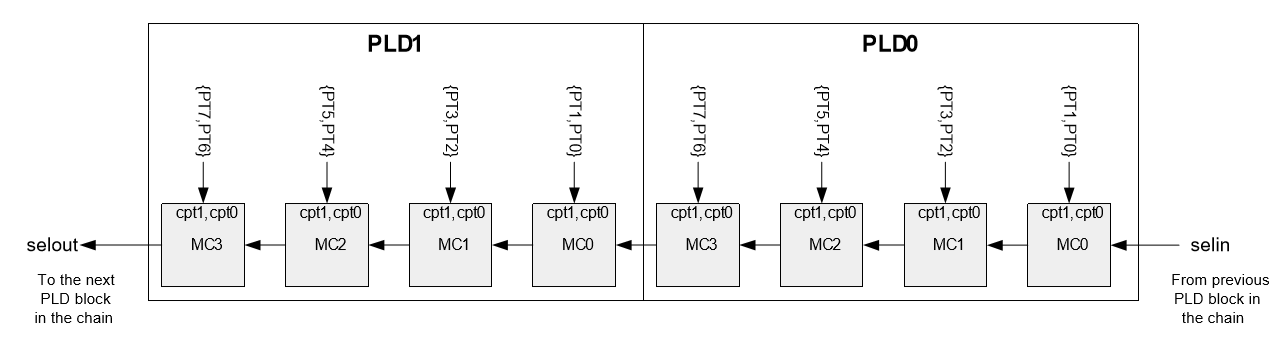

PLDはUDBアドレッシングで結び付けられています。 図21-5に示すように、selin転送チェーンの入力は、前のUDBから両方のPLDの各マクロセルを介して回路に転送され、次に、selout転送チェーンの出力として次のUDBに転送されます。 算術関数の効率的な配置をサポートするために、ハイフネーションチェーンと一緒にマクロセルで使用される特別な連言項(PT)が生成されます。

図21-5。 PLDハイフネーションチェーンと特別な連言用語の入力。

21.3.1.3 PLD構成

各PLDは、CPUまたはDMAの前に16ビットアクセスのRAMの形式で表示されます。 AND配列にはプログラミング用に12×8×2ビットまたは24バイトがあり、OR配列にはプログラミング用に4×8ビットまたは4バイトがあります。 さらに、各マクロセルには1つの構成バイトがあり、PLDごとに合計32の構成バイトがあります。 各UDBには2つのPLDがあるため、各UDBの合計構成は64バイトです。

次回は運用オートマトン(データパス)を検討します。