はじめに

どなたでも歓迎します。 今日、私は自分の経験を共有したいと思いますが、それでも、私の意見では、USB 2.0ホストコントローラーの簡単な標準について、一見しただけで明確に説明しています。

最初は、USB 2.0ポートは4ピンだけで、そのうちの2つがデータを送信するだけ(たとえばCOMポートのように)であると想像できますが、実際はそうではなく、まったく逆です。 USBコントローラーは、原則として、通常のCOMポート経由でデータを転送することを許可しません。 EHCIは、ソフトウェアからデバイス自体へ、および反対方向への信頼性の高い高速データ転送を可能にするかなり複雑な標準です。

この記事は、たとえば、ドライバーの十分なライティングスキルやハードウェアのドキュメントを読むことができない場合に役立つことがあります。 簡単な例:Windowsや他のLinuxディストリビューションがハードウェアをダウンロードしないように、ミニPC用にOSを作成し、そのパワーをすべて自分の目的にのみ使用したい場合。

EHCIとは何ですか?

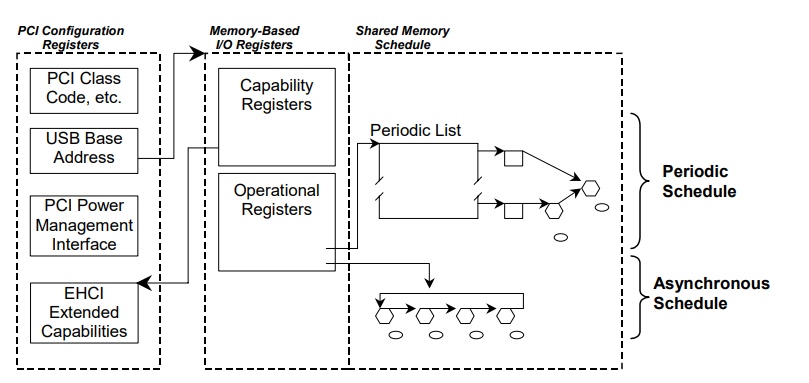

さあ、始めましょう。 EHCI-Enhanced Host Controller Interfaceは、データと制御要求をUSBデバイスに転送するように設計されており、他の方向で、99%の場合、任意のソフトウェアと物理デバイス間のリンクです。 EHCIはPCIデバイスとして動作するため、MMIO(Memory-Mapped-IO)を使用してコントローラーを制御します(はい、一部のPCIデバイスはポートを使用することを知っていますが、ここではすべてを一般化しました)。 Intelのドキュメントには、動作原理のみが記載されており、少なくとも擬似コードで記述されたすべてのアルゴリズムについてのヒントはありません。 EHCIには、機能と動作の2種類のMMIOレジスタがあります。 前者はコントローラーの特性を取得するのに役立ち、後者はコントローラーを制御するのに役立ちます。 実際、ソフトウェアとEHCIコントローラー間の接続の本質を添付します。

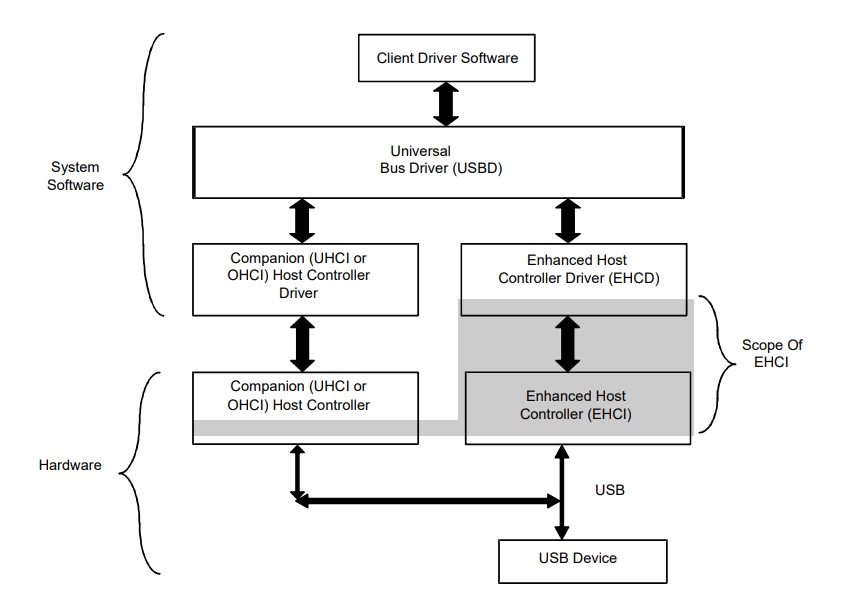

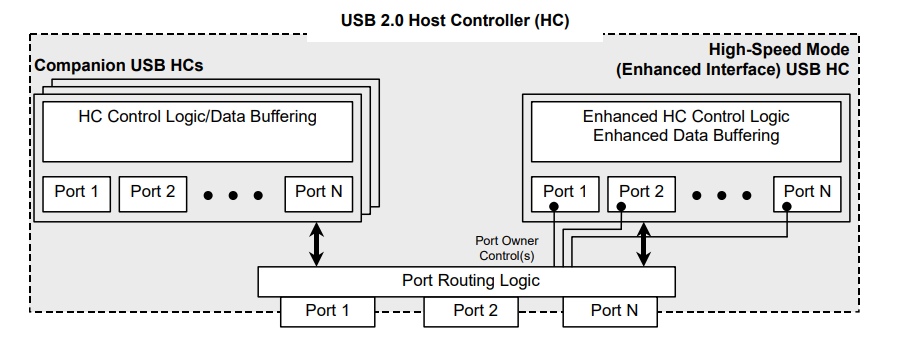

各EHCIコントローラーには複数のポートがあり、各ポートは任意のUSBデバイスに接続できます。 また、EHCIはUHCIの改良版であり、数年前にIntelによって開発されたことにも注意してください。 下位互換性のために、EHCIよりも低いバージョンを持つUHCI / OHCIコントローラーは、EHCIのコンパニオンになります。 たとえば、USB 1.1で動作するUSBキーボード(これまでのほとんどのキーボードはこれに似ていました)(USB 1.1の最大速度は毎秒12メガビットで、FullSpeed USB 2.0には帯域幅があることに注意してください)最大480 Mbps)で、USB 2.0ポートを備えたコンピューターを使用している場合、キーボードをコンピューターに接続すると、EHCIホストコントローラーはUSB 1.1でどのように動作します。 このモデルを次の図に示します。

また、将来的には、このような不条理な状況のためにドライバーが正しく動作しない可能性があることをすぐに警告します:UHCI、EHCIを初期化し、2つの同一のデバイスを追加し、ポート所有者制御ビットをポートレジスタに設定し、 EHCIが自動的にポートをドラッグし、UHCIのポートが応答を停止するため、UHCIは動作を停止しました。この状況を監視する必要があります。

また、EHCIアーキテクチャ自体を示す図を見てみましょう。

右側にはキューについて書かれています-それらについては少し後で。

EHCIコントローラーのレジスター

まず、これらのレジスタを介してデバイスを制御するため、これらは非常に重要であり、それらがなければEHCIプログラミングは不可能であることをもう一度明確にしたいと思います。

最初に、このコントローラーに与えられたMMIOアドレスを取得する必要があります。オフセット+ 0x10で、待望のレジスターのアドレスになります。 1つあります:最初に、機能レジスタが移動し、その後にのみ-操作可能なため、オフセット0(EHCIのMMIOの開始点に対してオフセット0x10で受信した前のアドレスから)に1バイト-機能レジスタの長さがあります。

機能レジスタ

オフセット2には、 HCIVERSIONレジスタがあります -このHCのリビジョン番号。2バイトを占有し、リビジョンのBCDバージョン(WikipediaにあるBCDを含む)を含んでいます。

オフセット+4で、 HCSPARAMSレジスタが配置され 、そのサイズは2ワードで、デバイスの構造パラメーターが含まれ、そのビットは以下を示します。

- ビット16-ポートインジケータ-接続されたUSBデバイスで使用可能なLED。

- ビット15:12-このコントローラーに割り当てられているコンパニオンコントローラーの番号

- ビット11:8-コンパニオンコントローラーのポート数

- ビット7-ポートルーティングルール-これらのポートがコンパニオンポートにマップされる方法を示します

- ビット4-ポート電力制御-各ポートの電源をオンにする必要があるかどうかを示します、0-電源は自動的に供給されます

- ビット3:0-このコントローラーのポートの数。

- オフセット+8にHCCPARAMSレジスタがあります-互換性パラメーターを示し、そのビットは次のことを意味します。

- ビット2-非同期キューの可用性、

- ビット1-定期的(順次)キューの可用性

- ビット0〜64ビットの互換性

操作レジスタ

オフセット0では、 USBCMDレジスタはコントローラのコマンドレジスタであり、そのビットは次を意味します。

- ビット23:16-割り込みしきい値制御-1つの通常のフレームに使用されるマイクロフレームの数を示します。 大きいほど高速ですが、8を超える場合、マイクロフレームは8と同じ速度で処理されます。

- ビット6-非同期キュー内の各トランザクションの後に割り込み、

- ビット5-使用される非同期キュー

- ビット4-順次キューの使用、

- ビット3:2-FrameList'aのサイズ(後で詳しく説明します)。 0は1024要素、1-512、2-256、3-予約を意味します

- ビット1 —ホストコントローラーのリセットを実行するように設定します。

- ビット0-実行/停止

次に、オフセット+4にUSBSTSレジスタがあります-ホストコントローラーのステータス、

- ビット15は、非同期キューが使用されているかどうかを示します。

- ビット14は、順次キューが使用されているかどうかを示します。

- ビット13-空の非同期キューが検出されたことを示します。

- トランザクションの処理中にエラーが発生した場合、ビット12は1に設定され、ホストコントローラーはすべてのキューを停止します。

- ビット4は1に設定され、重大なエラーが発生した場合、ホストコントローラーはすべてのキューを停止します。

- ビット3 FrameList(レジスタ)ロールオーバー-ホストコントローラーがframeList全体を処理したときに1に設定されます。

- ビット1-USBエラー割り込み-エラー割り込みを生成しますか?

- ビット0-USB割り込み-TDにIOCがインストールされている場合、トランザクション処理が成功した後に設定

疲れていない? あなたは自分に強いカモメを注ぎ、肝臓をもたらすことができます、私たちはまさに始まりです!

オフセット+8には、 USBINTRレジスタがあります-割り込みイネーブルレジスタ

長時間書き込まないようにするために、さらに長い間読み取らないようにするために、このレジスタのビットの値は仕様で見つけることができます。そのリンクは以下に残されます。 ここでは、0を書き込むだけです。 私はハンドラー、マップ割り込みなどを書くことを絶対に望んでいないので、これはほとんど完全に無意味だと思います。

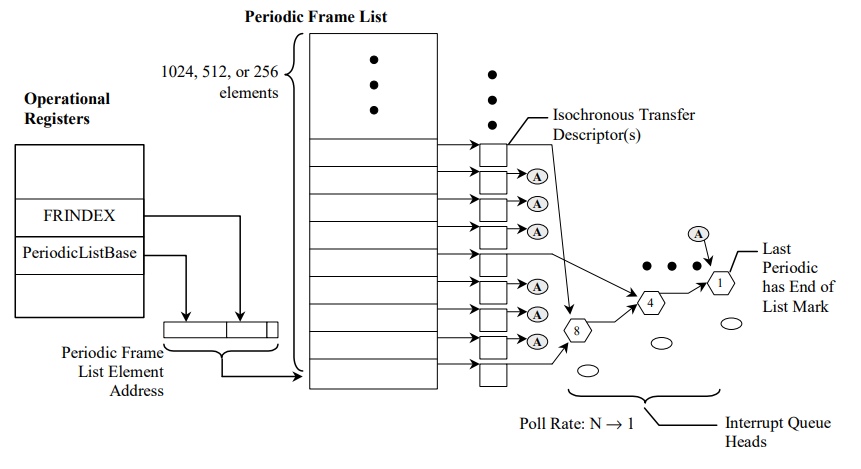

オフセット+12(0x0C)では、 FRINDEXレジスタがあり 、現在のフレーム番号が単純に存在します。最後の4ビットはマイクロフレーム番号を示し、上位28ビットではフレーム番号を示します(値は必ずしもframeListサイズより小さいとは限りません)ただし、インデックスが必要な場合は、0x3FF(または0x1FFなど)のマスクを使用して取得することをお勧めします。

CTRLDSSEGMENTレジスタはオフセット+ 0x10にあり、ホストコントローラーにフレームシートのアドレスの最上位32ビットを表示します。

PERIODICLISTBASEレジスタには+ 0x14のオフセットがあります。フレームシートの下位32ビットを配置できます。アドレスはメモリページのサイズ(4096)に揃える必要があることに注意してください。

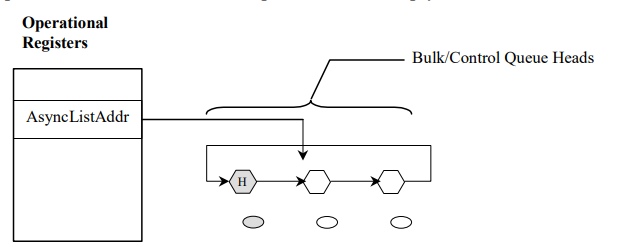

ASYNCLISTADDRレジスタには+ 0x18のオフセットがあります。非同期キューのアドレスを入れることができます。32バイトの境界に配置する必要がありますが、物理メモリの最初の4ギガバイトにある必要があります。

CONFIGFLAGレジスタは、デバイスが構成されているかどうかを示します。 デバイスのセットアップが完了したら、ビット0を設定する必要があります。オフセットは+ 0x40です。

ポートレジスタに移りましょう。 各ポートには独自のコマンドステータスレジスタがあり、各ポートレジスタはオフセット+ 0x44 +(PortNumber-1)* 4で 、そのビットは次のことを意味します。

- ビット12-ポート電源、1-電源が供給されている、0-いいえ。

- ビット8-ポートレスト-デバイスをリセットするために設定されます。

- ビット3-ポートの有効化/無効化の変更-ポートの「包含」のステータスを変更するときに設定します。

- ビット2-ポートのオン/オフ。

- ビット1-接続ステータスを変更します。たとえば、USBデバイスを接続または切断した場合、1に設定されます。

- ビット0-接続ステータス、1-接続済み、0-いいえ。

それでは、ジュースそのものに移りましょう。

データ転送とクエリ構造

要求を処理するための構造の編成には、キューと転送記述子(TD)が含まれます。

現時点では、3つの構造のみを考慮します。

シーケンシャルリスト

シーケンシャル(定期的、定期的)リストは次のように構成されています。

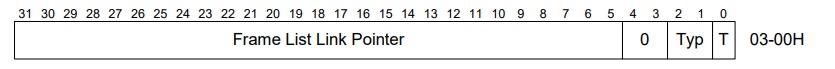

図からわかるように、処理はシートフレームから目的のフレームを取得することから始まります。各要素は4バイトで、次の構造を持っています。

図でわかるように、記述子のキューアドレス/転送は32バイトの境界に配置されます。ビット0はホストコントローラーがこの要素を処理しないことを意味します。ビット3:1はホストコントローラーが処理するもののタイプを示します。 (iTD)、1-この記事の1、2、3を検討しません。

非同期キュー

ホストコントローラーは、シーケンシャルフレームが空であるか、ホストコントローラーがシリアルリスト全体を処理した場合にのみ、このキューを処理します。

非同期キューは、処理が必要な他のキューを含むキューへのポインターです。 スキーム:

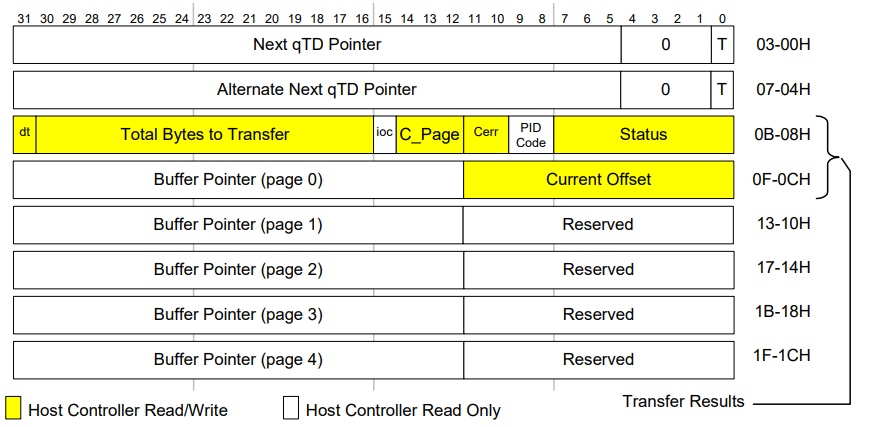

qTD(キュー要素転送記述子)

このTDの構造は次のとおりです。

次のqTDポインター -処理のためのキューの継続へのポインター (水平実行の場合)、ビット0次のqTDポインターは、キューがないことを示します。

qTDトークン -TDトークン、データ転送パラメーターを示します。

- ビット31-データの切り替え(詳細は後ほど)

- ビット30:16-転送するデータの量。トランザクションが完了した後、転送されるデータの量だけ値が減少します。

- ビット15-IOC-完了時に割り込み-記述子処理が完了した後に割り込みを発生させます。

- ビット14:12は、データの交換先となる現在のバッファの番号を示します。これについては後で詳しく説明します。

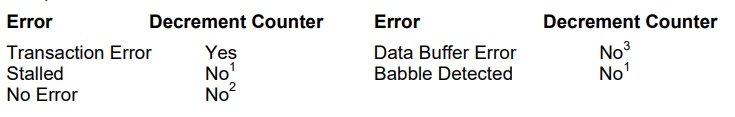

- ビット11:10-許可されるエラーの数。 次の表は、エラーカウントが減少するタイミングを示しています。

脚注1-BabbleまたはStallを検出すると、キューの先頭の実行が自動的に停止します。 脚注3-データバッファエラーはホストの問題です。 デバイスの再試行は考慮されません。 - 9:8-PIDコード-トークンのタイプ:0-入力へのトークン(ホストからデバイスへ)、1-出力へのトークン(デバイスからホストへ)、2-「セットアップ」トークン

- ビット7:0はTDステータスを示します:

ビット7は、このTDがアクティブ状態であることを示します(つまり、ホストコントローラーがこのTDを処理しています)

ビット6-停止-エラーが発生し、TDの実行が停止したことを示します。

ビット4-検出されたバブル-デバイスに送信したデータの量、または1回転あたりのデータ量が送信量より少ない、つまり、たとえば、デバイスが100バイトのデータを送信し、50バイトだけを読み取った後、さらに50バイトを読み取ったこのビットが1に設定されている場合、停止ビットも設定されます。

ビット3-トランザクションエラー-トランザクション中にエラーが発生しました。

qTDバッファーページポインターリスト -5つのバッファーのいずれか。 メモリ内のトランザクションが行われる場所(デバイスへのデータの送信/デバイスからのデータの受信)へのリンクが含まれ、最初のバッファを除くバッファ内のすべてのアドレスがページのサイズ(4096バイト)に揃えられる必要があります。

行頭

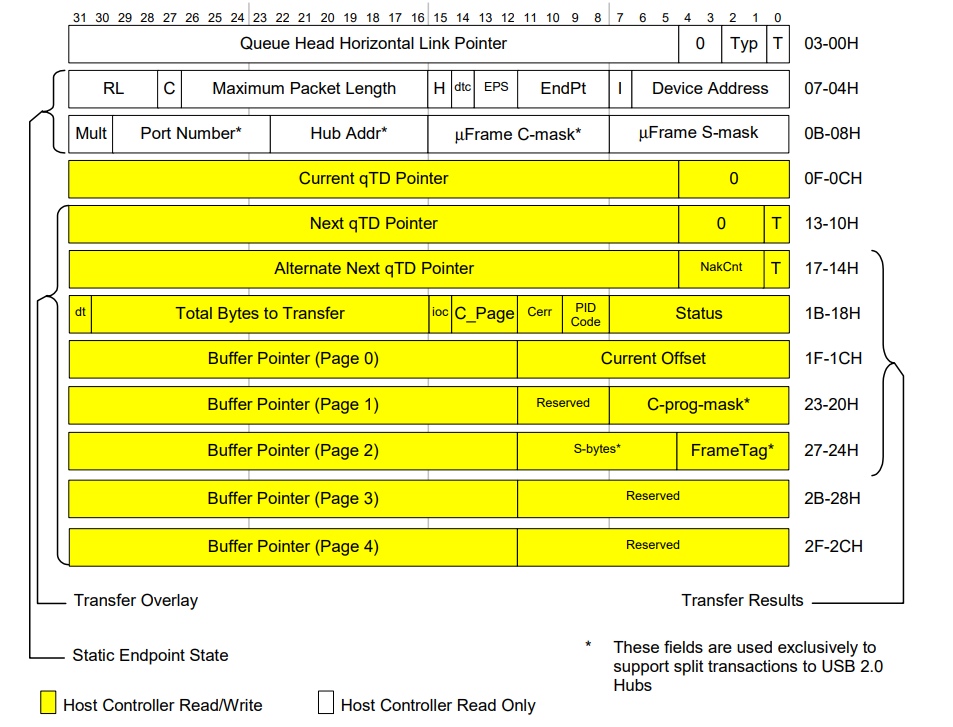

キューヘッドの構造は次のとおりです。

キューヘッド水平リンクポインター -次のキューへのポインター 、ビット2:1にはキューのタイプに応じて次の値があります。

エンドポイント機能/特性 -キューの特性:

- ビット26:16には、送信用の最大パケットサイズが含まれます

- ビット14:データトグル制御-ホストコントローラーが初期データトグル値を取得する場所を示します。0-qTDのDTビットを無視し、キューヘッドのDTビットを保存します。

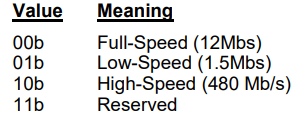

- ビット13:12-伝送速度特性:

- ビット11:8-要求が行われるエンドポイントの番号

- ビット6:0-デバイスアドレス

エンドポイント機能:キューヘッドDWord 2-前のダブルワードの続き:

- ビット29:23-ハブ番号

- ビット22:16-ハブアドレス

現在のqTDリンクポインター -現在のqTDへのポインター。

最も興味深いものに渡します。

EHCIドライバー

EHCIがどのようなリクエストを処理できるかから始めましょう。 リクエストには2つのタイプがあります。たとえば、コントロール-aコマンド、およびバルク-エンドポイントへのデータ交換です。たとえば、大部分のUSBフラッシュドライブ(USB MassStorage)はデータ転送タイプBulk / Bulk / Bulkを使用します。 マウスとキーボードも、データ転送にバルク要求を使用します。

EHCIを初期化し、非同期および順次キューを構成します。

// Base I/O Address PciBar bar; PciGetBar(&bar, id, 0); EhciController *hc = VMAlloc(sizeof(EhciController)); hc->capRegs = (EhciCapRegs *)(uintptr_t)bar.u.address; hc->opRegs = (EhciOpRegs *)(uintptr_t)(bar.u.address + hc->capRegs->capLength); // Read the Command register // uint cmd = ROR(usbCmdO); // Write it back, setting bit 2 (the Reset bit) // , 2(Reset) // and making sure the two schedule Enable bits are clear. // , 2 WOR(usbCmdO, 2 | cmd & ~(CMD_ASE | CMD_PSE)); // A small delay here would be good. You don't want to read // , // the register before it has a chance to actually set the bit // , ROR(usbCmdO); // Now wait for the controller to clear the reset bit. // Reset while (ROR(usbCmdO) & 2); // Again, a small delay here would be good to allow the // reset to actually become complete. // ROR(usbCmdO); // wait for the halted bit to become set // Halted while (!(ROR(usbStsO) & STS_HCHALTED)); // , // , 128 hc->frameList = (u32 *)VMAlloc(1024 * sizeof(u32) + 8192 * 4); hc->frameList = (((uint)hc->frameList) / 16384) * 16384 + 16384; hc->qhPool = (EhciQH *)VMAlloc(sizeof(EhciQH) * MAX_QH + 8192 * 4); hc->tdPool = (EhciTD *)VMAlloc(sizeof(EhciTD) * MAX_TD + 8192 * 4); hc->qhPool = (((uint)hc->qhPool) / 16384) * 16384 + 16384; hc->tdPool = (((uint)hc->tdPool) / 16384) * 16384 + 16384; // Asynchronous queue setup // EhciQH *qh = EhciAllocQH(hc); // , // , qh->qhlp = (u32)(uintptr_t)qh | PTR_QH; // , , qh->ch = QH_CH_H; qh->caps = 0; qh->curLink = 0; qh->nextLink = PTR_TERMINATE; qh->altLink = 0; qh->token = 0; // for (uint i = 0; i < 5; ++i) { qh->buffer[i] = 0; qh->extBuffer[i] = 0; } hc->asyncQH = qh; // Periodic list queue setup // qh = EhciAllocQH(hc); // qh->qhlp = PTR_TERMINATE; qh->ch = 0; qh->caps = 0; qh->curLink = 0; qh->nextLink = PTR_TERMINATE; qh->altLink = 0; qh->token = 0; // for (uint i = 0; i < 5; ++i) { qh->buffer[i] = 0; qh->extBuffer[i] = 0; } qh->transfer = 0; qh->qhLink.prev = &qh->qhLink; qh->qhLink.next = &qh->qhLink; hc->periodicQH = qh; // for (uint i = 0; i < 1024; ++i) hc->frameList[i] = PTR_QH | (u32)(uintptr_t)qh; kprintf("FrameList filled. Turning off Legacy BIOS support..."); // Check extended capabilities // BIOS Legacy support uint eecp = (RCR(hccParamsO) & HCCPARAMS_EECP_MASK) >> HCCPARAMS_EECP_SHIFT; if (eecp >= 0x40) { // Disable BIOS legacy support uint legsup = PciRead32(id, eecp + USBLEGSUP); kprintf("."); if (legsup & USBLEGSUP_HC_BIOS) { PciWrite32(id, eecp + USBLEGSUP, legsup | USBLEGSUP_HC_OS); kprintf("."); for (;;) { legsup = PciRead32(id, eecp + USBLEGSUP); kprintf("."); if (~legsup & USBLEGSUP_HC_BIOS && legsup & USBLEGSUP_HC_OS) { break; } } } } kprintf("Done\n"); // Disable interrupts // //hc->opRegs->usbIntr = 0; MWIR(ehcibase, usbIntrO, 0); // Setup frame list // //hc->opRegs->frameIndex = 0; WOR(frameIndexO, 0); //hc->opRegs->periodicListBase = (u32)(uintptr_t)hc->frameList; WOR(periodicListBaseO, (u32)(uintptr_t)hc->frameList); // //hc->opRegs->asyncListAddr = (u32)(uintptr_t)hc->asyncQH; WOR(asyncListAddrO, (u32)(uintptr_t)hc->asyncQH); // 0 //hc->opRegs->ctrlDsSegment = 0; WOR(ctrlDsSegmentO, 0); // Clear status // //hc->opRegs->usbSts = ~0; WOR(usbStsO, ~0); // Enable controller // , 8 -, // //hc->opRegs->usbCmd = (8 << CMD_ITC_SHIFT) | CMD_PSE | CMD_ASE | CMD_RS; WOR(usbCmdO, (8 << CMD_ITC_SHIFT) | CMD_PSE | CMD_ASE | CMD_RS); while (ROR(usbStsO)&STS_HCHALTED); // Configure all devices to be managed by the EHCI // , //hc->opRegs->configFlag = 1; WOR(configFlagO, 1);\ // Probe devices // EhciProbe(hc);

実際には、ポートを元の状態にリセットするためのコード:

volatile u32 *reg = &hc->opRegs->ports[port]; // , 100 *reg|=(1<<12)|(1<<20); Wait(100); // , 50 EhciPortSet(reg, PORT_RESET | (1<<12) | (1<<20) | (1<<6)); Wait(50); EhciPortClr(reg, PORT_RESET); // Wait 100ms for port to enable (TODO - what is appropriate length of time?) // 100 , , // 100 uint status = 0; for (uint i = 0; i < 10; ++i) { // Delay Wait(10); // Get current status // status = *reg; // Check if device is attached to port // if (~status & PORT_CONNECTION) break; // Acknowledge change in status // - if (status & (PORT_ENABLE_CHANGE | PORT_CONNECTION_CHANGE)) { EhciPortClr(reg, PORT_ENABLE_CHANGE | PORT_CONNECTION_CHANGE); continue; } // Check if device is enabled // , if (status & PORT_ENABLE) break; } return status;

デバイスへの制御要求:

static void EhciDevControl(UsbDevice *dev, UsbTransfer *t) { EhciController *hc = (EhciController *)dev->hc; UsbDevReq *req = t->req; // Determine transfer properties // uint speed = dev->speed; uint addr = dev->addr; uint maxSize = dev->maxPacketSize; uint type = req->type; uint len = req->len; // Create queue of transfer descriptors // TDs EhciTD *td = EhciAllocTD(hc); if (!td) return; EhciTD *head = td; EhciTD *prev = 0; // Setup packet // uint toggle = 0; uint packetType = USB_PACKET_SETUP; uint packetSize = sizeof(UsbDevReq); EhciInitTD(td, prev, toggle, packetType, packetSize, req); prev = td; // Data in/out packets packetType = type & RT_DEV_TO_HOST ? USB_PACKET_IN : USB_PACKET_OUT; u8 *it = (u8 *)t->data; u8 *end = it + len; //EhciPrintTD(td); while (it < end) { td = EhciAllocTD(hc); if (!td) return; toggle ^= 1; packetSize = end - it; if (packetSize > maxSize) packetSize = maxSize; EhciInitTD(td, prev, toggle, packetType, packetSize, it); it += packetSize; prev = td; } // Status packet // td = EhciAllocTD(hc); if (!td) return; toggle = 1; packetType = type & RT_DEV_TO_HOST ? USB_PACKET_OUT : USB_PACKET_IN; EhciInitTD(td, prev, toggle, packetType, 0, 0); // Initialize queue head // : EhciQH *qh = EhciAllocQH(hc); EhciInitQH(qh, t, head, dev->parent, false, speed, addr, 0, maxSize); // Wait until queue has been processed // EhciInsertAsyncQH(hc->asyncQH, qh); EhciWaitForQH(hc, qh); }

キュー処理コード:

if (qh->token & TD_TOK_HALTED) { t->success = false; t->complete = true; } else if (qh->nextLink & PTR_TERMINATE) if (~qh->token & TD_TOK_ACTIVE) { if (qh->token & TD_TOK_DATABUFFER) kprintf(" Data Buffer Error\n"); if (qh->token & TD_TOK_BABBLE) kprintf(" Babble Detected\n"); if (qh->token & TD_TOK_XACT) kprintf(" Transaction Error\n"); if (qh->token & TD_TOK_MMF) kprintf(" Missed Micro-Frame\n"); t->success = true; t->complete = true; } if (t->complete) ....

そして今、エンドポイント要求(バルク要求)

static void EhciDevIntr(UsbDevice *dev, UsbTransfer *t) { EhciController *hc = (EhciController *)dev->hc; // Determine transfer properties // uint speed = dev->speed; uint addr = dev->addr; uint maxSize = t->endp->desc->maxPacketSize; uint endp = t->endp->desc->addr & 0xf; EhciTD *td = EhciAllocTD(hc); if (!td) { t->success = false; t->complete = true; return; } EhciTD *head = td; EhciTD *prev = 0; // Data in/out packets uint toggle = t->endp->toggle; uint packetType = t->endp->desc->addr & 0x80 ? USB_PACKET_IN : USB_PACKET_OUT; uint packetSize = t->len; EhciInitTD(td, prev, toggle, packetType, packetSize, t->data); // Initialize queue head // EhciQH *qh = EhciAllocQH(hc); EhciInitQH(qh, t, head, dev->parent, true, speed, addr, endp, maxSize); //printQh(qh); // Schedule queue // EhciInsertPeriodicQH(hc->periodicQH, qh); }

このトピックは非常に興味深いと思います。ロシア語のインターネット上では、このトピックに関するドキュメント、説明、記事はほとんどなく、存在する場合は非常にぼやけています。 ハードウェアとOS開発の作業のトピックが興味深い場合、多くのことを伝える必要があります。

ドック: 仕様