写真:MeerKAT望遠鏡によるデジタルデータ処理用のSKARABプラットフォーム。 HMCテクノロジーのおかげで、望遠鏡の64個のアンテナのそれぞれは、40 Gbit / sの速度でプラットフォームにデータを送信できます。

来年登場する新しいDDR5 SDRAM標準を見越して、代替技術を検討しています。 この記事では、HMC(ハイブリッドメモリキューブ)について説明します。HMCは、DDR3 DRAMに比べてビットあたりのエネルギーを70%削減し、パフォーマンスを15倍向上させます。

DDR4とDDR5は規格の進化を表していますが、HMCは特殊な高性能コンピューティングの分野だけでなく、フォームファクターが重要なタブレットやグラフィックカードなどの家電の分野でも市場を変えることができる革新的な技術です。エネルギー効率と帯域幅。

HMCのアーキテクチャとデバイス

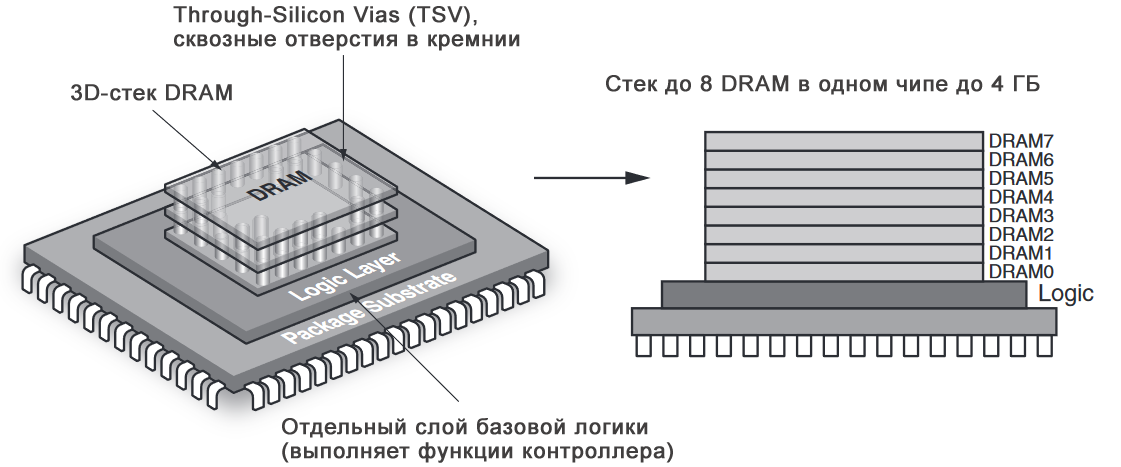

HMCは、ハイブリッドメモリキューブ、ハイブリッドメモリキューブの略です。 物理的には、このチップはTSVテクノロジーを使用してシリコン遷移によって接続された複数の層で構成されています。 上の層はDRAMメモリの結晶で、下の層はデータの送信を制御するコントローラーです。

HMCチップの内部構造:

HMCは、パフォーマンスが必要な場合、および必要なメモリサイズ用の少数のチップで使用されます。 HMCチップは、最大8個のシリアルチェーンで組み合わせることができます。 2 GBおよび4 GBの容量のチップが利用可能です。 データは、シリアルインターフェイスを介して、ラインあたり15ギガビット/秒の速度で送信されます。 ラインの総数は32〜64です。したがって、理論上の帯域幅は240 Gb / sに達することができますが、160 Gb / sのレベルでのDRAMクリスタルの帯域幅によって制限されます。

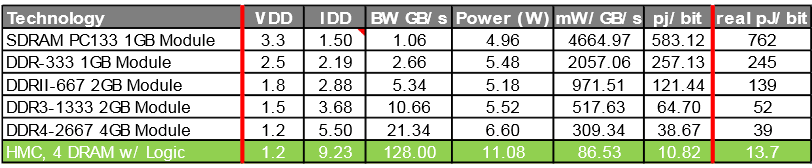

次の表は、データビットごとの消費量を示しています。

HMC比較表、DDR4(第1世代、4 + 1メモリ構成)

HMCに加えて、他の開発会社からも同様の指示がいくつかあります。

- MoSys Bandwidth Engine(BE) -QDRメモリを置き換えるために設計されたチップは、SRAMのように機能します。 最大16 Gb / sの速度でシリアルトランシーバーを使用します。 このタイプのメモリの目的は、パケット全体を格納するのではなく、パケットヘッダーまたはルックアップテーブルを格納するための読み取り遅延の少ないバッファです。

- TCAM(Ternary Content Addressable Memory)は、ルーターやネットワークスイッチで使用される特別な高速メモリであり、価格が高くなっています。 高電力消費により実現される高性能。 データ送信は並行して実行されます。

- 高帯域幅メモリ(HBM)は、サムスンが開発したメモリの一種です。 チップの形では利用できません。ユーザーがこのメモリを使用する場合は、会社に連絡してシリコン基板にし、ユーザーのチップに統合する必要があります。 このメモリはDDRに似ており、シリアルトランシーバを使用してデータを送信しません。

HMC接続の例

物理的に、HMCのデータはSerDesインターフェイスを介して15 Gb / sの速度で順次送信されます。 すぐに30 Gbit / sの速度でチップがあります。 16行が1つの論理チャネルに結合されます。 チャネルは、フルチャネルモードとセミチャネルモードの両方で動作できます(8ラインが使用されます)。 通常、HMCは2または4チャンネルで使用できます。 各チャネルは、マスターまたは中間のいずれかです。 チェーンで複数のチップを組み合わせる必要がある場合、中間モードが使用されます。 プロセッサーは各HMCチップを構成する必要があります。

HMCチップのチェーンの例:

HMCチップとスターを組み合わせた例、マルチホストモードの可能性:

論理チャネルのデータ転送

チャネル伝送構造:

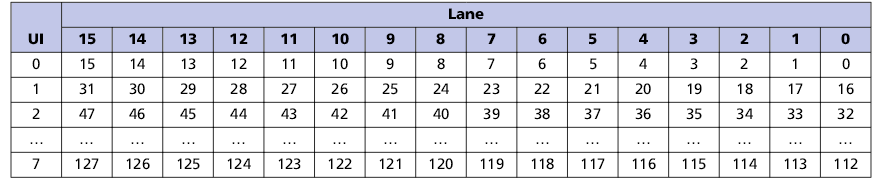

コマンドとデータは、パケットプロトコルを使用して両方向に送信されます。 パケットは、FLITと呼ばれる128ビット長のグループで構成されます。 それらは物理回線を介して順次送信され、受信側で組み立てられます。

パッケージサービスの3つのレベル:

- 物理層は、データの受信、送信、シリアライゼーション、デシリアライゼーションを提供します。

- リンク層は低レベルのパケット追跡を提供します。

- トランスポート層は、フィールド、パケットヘッダーを決定し、パケットと通信チャネルの整合性をチェックします。

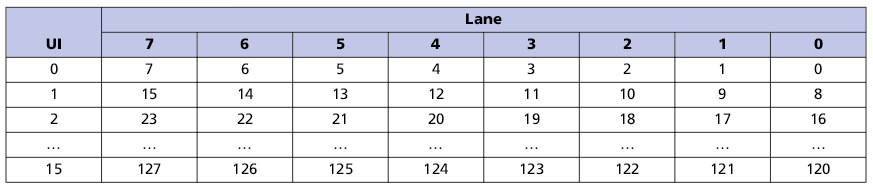

さまざまなモードの物理回線を介した128ビットFLIT伝送の構成:

1.フル構成のライン(16ライン)に沿ったFLITパケットの配布

2.ハーフ構成のライン(8ライン)に沿ったFLITパケットの配布

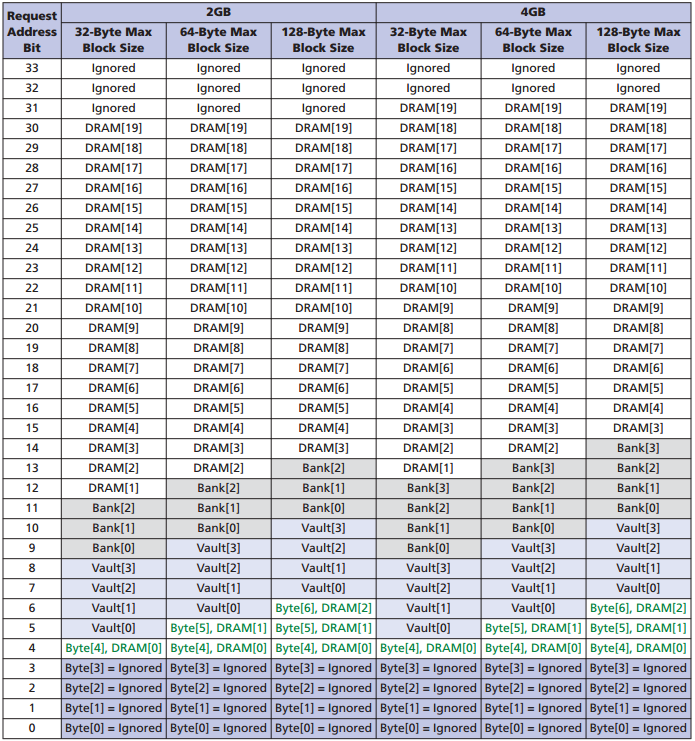

メモリアドレッシング

パケットヘッダーには、バンク、DRAMアドレスを含む34のアドレスビットが含まれています。 現在の構成では、1つのチップで最大4 GBをアドレス指定できますが、上位2ビットは無視され、将来のために予約されています。 データの読み取りと書き込みは、16バイトのグラニュレーションで行われます。 ブロックサイズは、16、32、64、128バイトに設定できます。

HMCでのアドレス指定:

これらのコマンドの詳細については、 Micron WebサイトのHMC仕様をご覧ください。

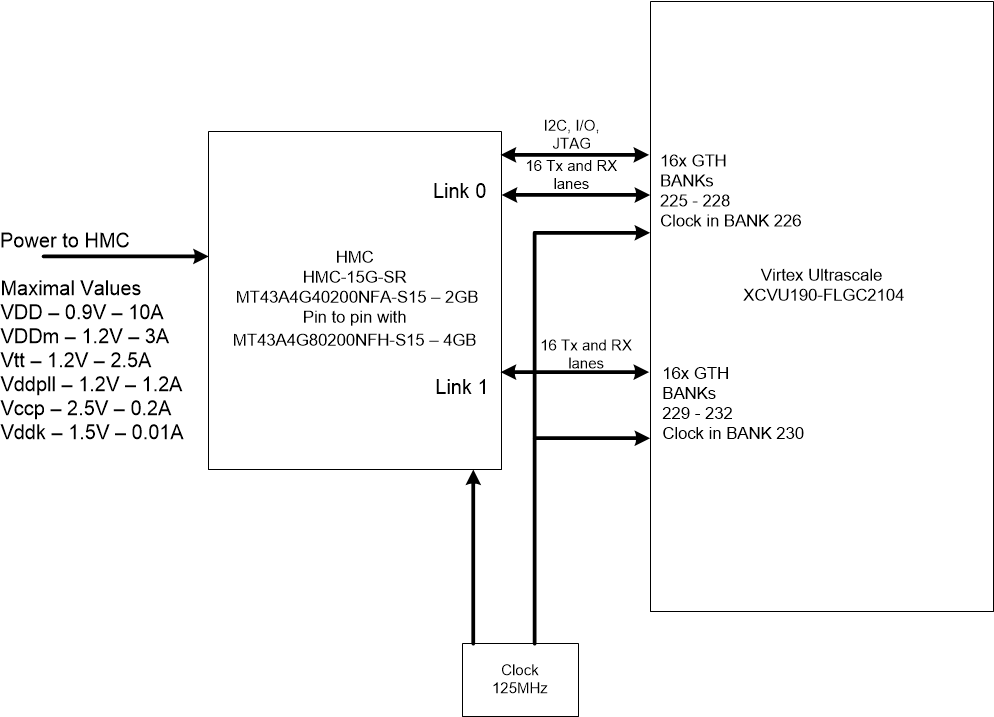

ザイリンクスVirtex Ultrascale FPGAへの一般的なHMC接続と電力要件

メモリはGTXトランシーバーを介してFPGAに接続されます。 同じチャネル内で8つのトランシーバーと最大16のトランシーバーを使用できます。 このようなチャネルが4つある場合がありますが、FPGAトランシーバーに適切に接続するには、いくつかのルールに従う必要があります。

- チャネル内のトランシーバーは一列に並んでいる必要があり、トランシーバーを介してジャンプすることはできません。

- SSI(スタックドシリコンインターコネクト)テクノロジを備えたデバイスの場合、トランシーバーは同じSLRにある必要があります

- FPGAバンクは連続する必要があり、バンクを飛び越えることはできません

典型的なFPGA接続、フルモードの2つのチャネル:

このトピックをより深く理解するには、HMCテクノロジーコンソーシアムのウェブサイト-hybridmemorycube.orgにアクセスして、最新のHMC仕様バージョン2.1を公開します。