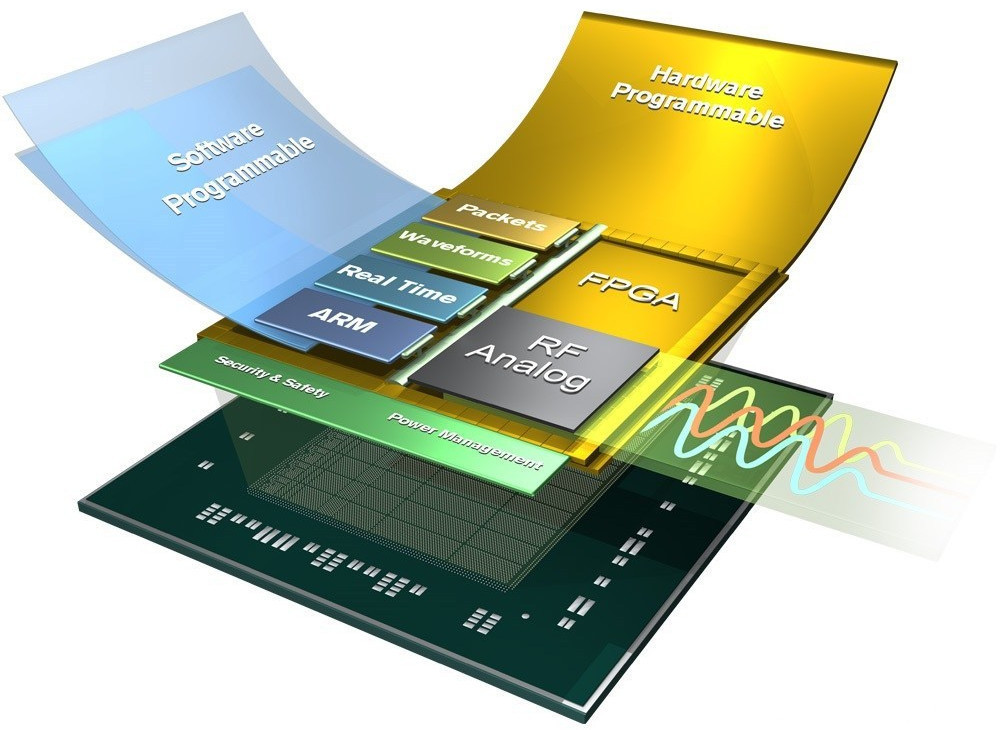

ザイリンクスは、最新の無線および送信機の外観と開発プロセスを完全に変更できる製品を、不要なポンプなしで静かに発表しました。 これは、無線信号の処理と生成の90%を組み合わせた小さなチップです。

- プログラマブルロジック(FPGA)、

- 信号処理およびユーザーアプリケーション用のプロセッサ(2つのARM)、

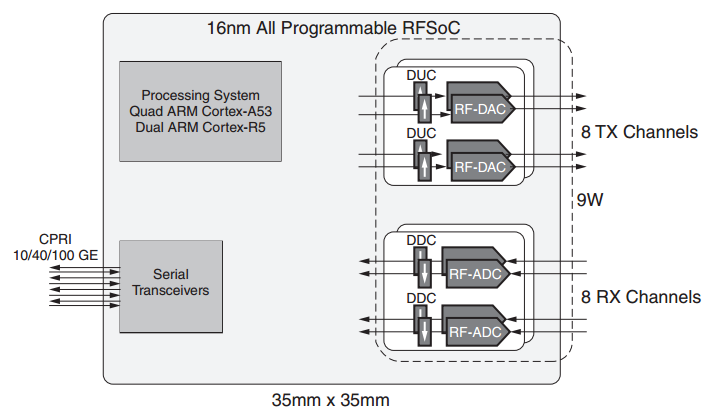

- 最大4 GHz(!)のサンプリング周波数で最大8個の12ビットADC

- 最大周波数6.4 GHz(!)の最大8個の14ビットDAC。

トランシーバーのアーキテクチャーが現代のPCのアーキテクチャーと同じくらい普遍的になる時代に突入しているようです。 HWではなくSWを作ろう!

時代からZynq

少し歴史。 私は、過去10〜15年間の主な活動が衛星航法の分野の研究開発である小さなチームの代表です。

この間に私たちがしていないこと! GLONASSの新しい信号を開発し、可能なすべての信号を処理し、ナビゲーションシステムからの信号をシミュレートし、妨害電波を検出するシステムを作成し、アンテナアレイの超小型回路を作成し、量子光学ステーションのテレビサイズの受信機を作成しました。 一般的に、私たちの冒険によれば、信号処理のカーマスートラを安全に書くことができます(私たちはそうしました )!

このようなタスクの動物園では、標準の受信機ではできないことは明らかです。 私たちはGeosとNV-08Cモジュールを愛し、知っています。これらのプロジェクトにも参加しましたが、プロジェクトでは常に独自の開発を使用しました。

小規模なレシーバーを作成する唯一の方法は、FPGAを使用することです。 ここで、現代の信号の処理がコンピュータグラフィックスの仕事に似ていることを説明する価値があります。 操作は比較的単純ですが、並行して多くを行う必要があります。 この意味で、最新のコンピューターのGPUとしてのレシーバー向けのFPGA(または大規模シリーズのシリコン片)。

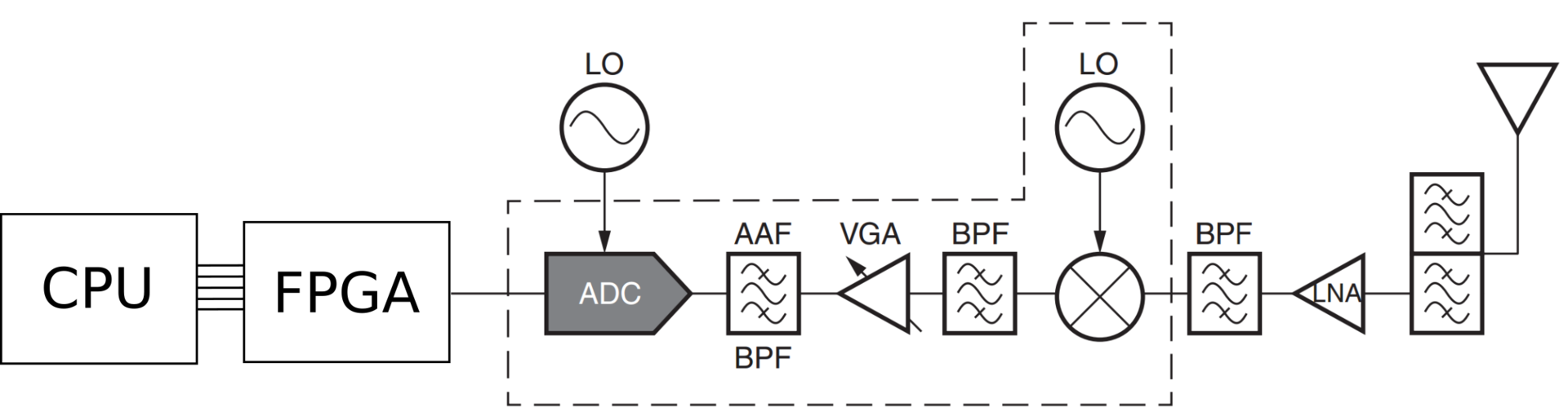

10年前の受信機のブロック図はどのように見えましたか?

この回路の何が問題になっていますか? プロセッサとプログラマブルロジックは、異なるマイクロ回路に分離されています。 そして、それは多くの問題を引き起こします。

信号処理の特異性には、厳密なリアルタイムモードでのプロセッサとFPGA間のデータ交換が常に必要です! ナビゲーションレシーバーのストリームは、数ギガビットに達します。

各超小型回路には、接続のために独自の結合、冷却、多層回路基板が必要であり、プリント基板上で角質が発生します。

そして最終的に、それはただ難しいです。 また、システム構築の複雑さは、障害とほぼ同義です。

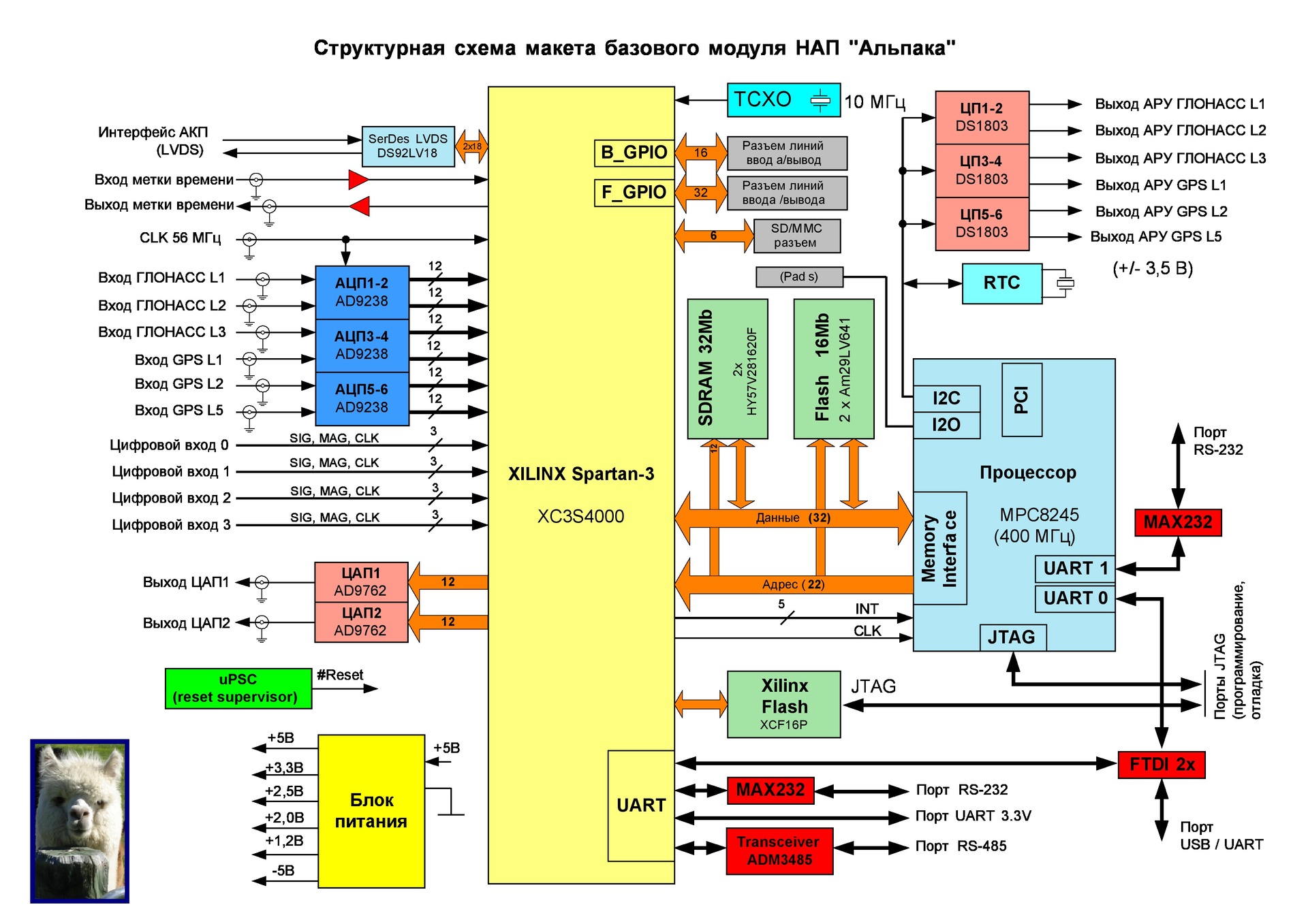

たとえば、2007年に行った受信機のブロック図:

ザイリンクスのSpartan 3がFPGAとして使用され、MPC8245の形式の巨大なPowerPCがプロセッサとして使用されました。 ツールチェーンの転送、ドライバーの検索、FPGAとプロセッサー間の交換の整理などに時間がかかりました。

しかし、突然世界が変わりました...

プログラマブルロジックとプロセッサシステムを組み合わせたSoCの登場

上記の痛みは、小規模生産とプロトタイピングの特徴です。 多数の個別のFPGA +個別のCPUの場合、高コスト、大量消費、および寸法が特徴的です。 さらに悪いことに、ソフトウェアは耐えられませんでした。 新しい組み合わせごとに、ほとんどのソフトウェアを書き直す必要がありました。

製品がASICの生産に勝つとすぐに、メーカーは独自のチップを開発しました。 すべてのデジタル処理は、中間周波数のADC、デジタル処理の並列ロジック、プロセッサ、およびインターフェイスなどのマイクロ回路に統合されました。 このスキームによると、最新のナビゲーションチップはすべて構築されています。

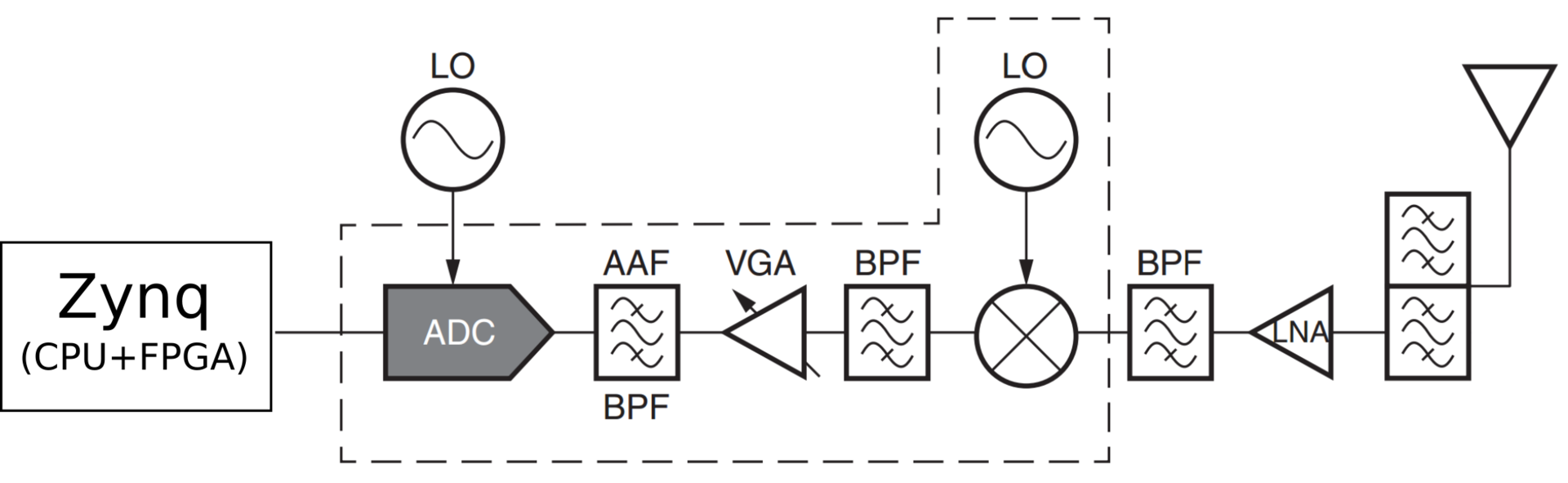

2010年代初頭、ザイリンクスとアルテラは、問題の半分を解決した製品を発表しました。 ザイリンクスは、プログラマブルロジック(FPGA)とプロセッサシステム(周辺機器のフルセットを備えたデュアルコアARM)を組み合わせたZynqシリーズのチップを発売しました。

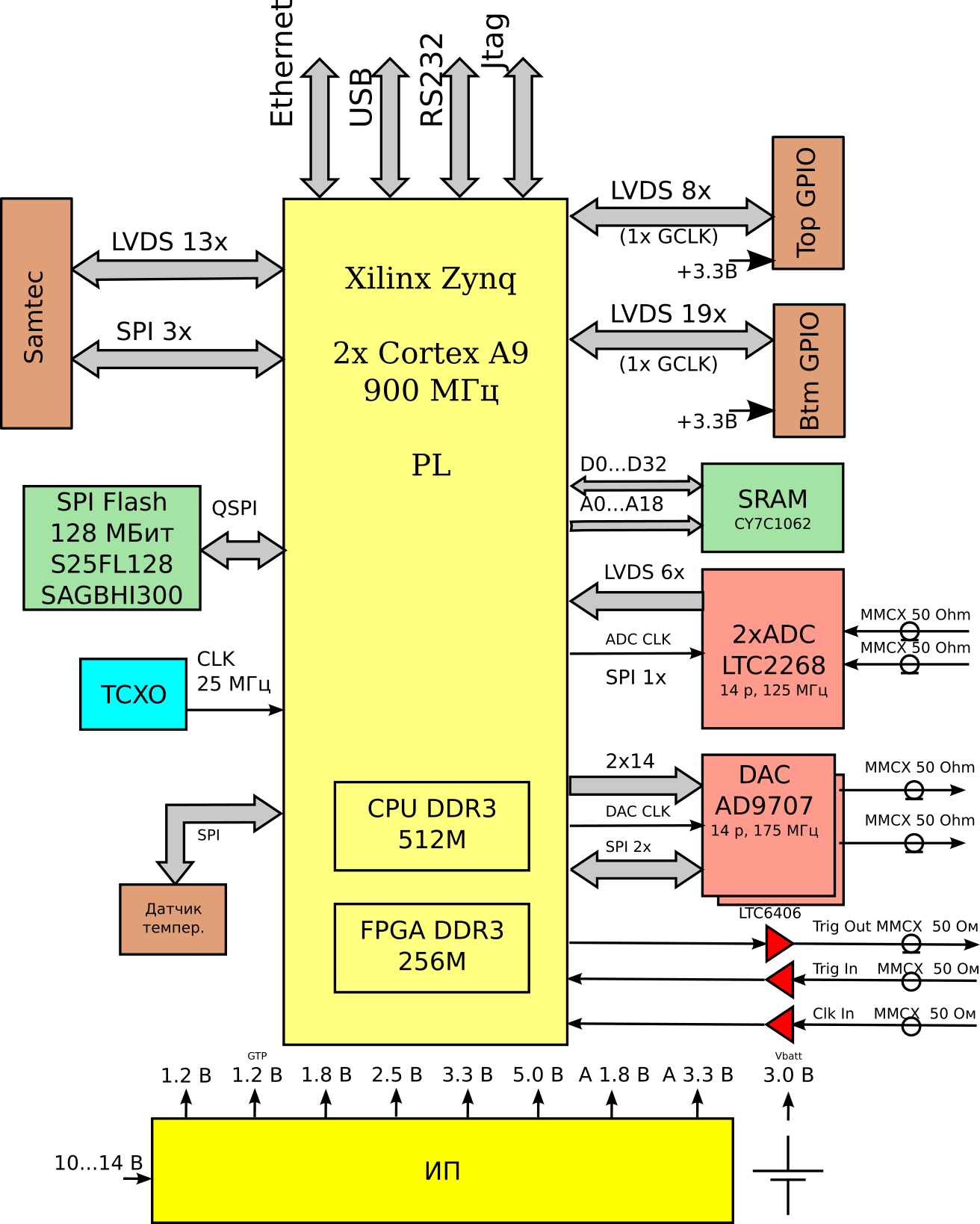

Zynqチップシステムは大幅に改善されました。 コードが大幅に簡素化され、プロセッサシステムとプログラマブルロジック間の交換レートが上昇し、回路基板が簡素化されました。 たとえば、2013年のプロジェクトの構造図では、違いが感じられます。

そして最も重要なことは、突然新しい品質が生まれたということです。現在、当社のソフトウェアはZynqを搭載したボードで発売されています。

無線エンジニアリングデバイスの開発サイクルでは、アルゴリズムとソフトウェアの作成、関連する研究、および開発に80%の時間がかかります。 Javaがクロスプラットフォームである場合、Zynqはクロスボードです。 これで、ボードの開発を顧客に移し、主なものであるソフトウェアに集中できます。

さらに、ザイリンクスはツールチェーン、ドライバー、その他の無線技術の問題を引き継ぎました。

Zynqsの発売から5年後、興味深い現象が現れました-プログラマブルロジックに基づく商用製品。 例は、 Piksi MultiまたはTersus Preciseです。 はい、これらのレシーバーは、ASIC上に構築された同様のレシーバーを引き続き使用します。 しかし、価格は同等になりました! プログラマブルロジックを備えたLittle Zynqを50ドルで購入できるようになりました! そして、これは可能なアプリケーションの数を桁違いに増やします!

来日...

上記を考慮すると、次のステップはADCとDACを水晶に追加することであることが論理的になります。 しかし、ザイリンクスは2つのステップを踏み出すことにしました。

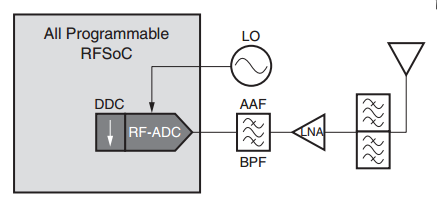

ここでもう少し。 最新の受信機または送信機は2つの世界です。 デジタルおよびアナログ。 たとえば、受信機を考えてみましょう。

アナログの世界:

- 電磁場を電気信号に変換するアンテナ。

- フロントエンド。その機能は、信号の搬送周波数をフィルタリング、増幅、および低下させ、デジタル処理によってプルされるようにすることです。

次は、さまざまなコンピューターによって実装されるデジタルの世界です。

ザイリンクスはアナログの世界に飛びました!

周波数が4 GHz以上のADCを使用すると、キャリアですぐにデジタル処理に切り替えることができます! 最高6 GHzの最高周波数のDAC-すべてのリンクをパワーアンプに接続します。

そして、これらのADCとDACは8つあります! これにより、MIMO、CRPA、ビームフォーミング、方向決定など、毎年より重要になるマルチアンテナシステムの問題が解決されます。

アナログ-デジタルコンバーターは単一チップに実装されているため、特性の高い同一性が保証されます。 同時に、彼らは高いダイナミックレンジ-約65 dB SFDRを持っています。

したがって、受信機のアナログ部分は、アンテナ、プリフィルター、プリアンプに縮小されます。 送信機で-パワーアンプとアンテナに。 そして、動作周波数が示されているよりも高い場合、ヘテロダインの1ステップ。

ザイリンクスによると、RFSoCを使用すると、エネルギー消費を大幅に改善できます。 8個のADCと8個のDACを備えたバージョンでは、27 Wの消費電力が示されています。

Zynq UltraScaleシリーズと同様に、プロセッサシステムは、無線オペレーター(デュアルコアCortex-R5)とユーザーアプリケーション(クアッドコアCortex-A53)用の2つのプロセッサーで表されます。

まとめ

ザイリンクスの発表は、ラジオエンジニアリングの一般的な傾向を反映しています。これは、統一とソリューションがすべて一体となったコースです。 個人的には、20世紀のコンピューターの発展を思い起こさせます。 業界にどのような結果がもたらされ、同じタイプのPCが登場し、プログラマーの職業に何が起こったのか、そして世界がどのように変化したのかを思い出す必要はありません。

ここでの主な質問は、彼らがこの奇跡を私たちに売るかどうかです。 十分なお金で民間バージョンを期待することは残っています。