注釈

この記事では、NetMOS / MosChip MSC98XX-CVおよびSystemBase SB16C1052PCIマイクロチップ上に構築され、最大1 Mbpsのデータ転送速度でシリアルRS-422物理インターフェイスを実装する市販のマルチポートI / O拡張アダプターの変更について説明します。

テキスト

IBM PCコンピューターの時代以来、ほとんどの場合、UARTプロトコルで動作するパーソナルコンピューター、ワークステーション、およびサーバーのシリアルポートは、RS-232物理信号インターフェイスを使用していました。 以前は、シリアルポート、またはシステムソフトウェアの用語でのCOMポートは、主に交換電話回線やその他の低速通信チャネル用のマウス型マニピュレーターとモデムの接続に使用されていました。 現代のコンピューター技術では、これらの周辺機器はUSBで接続されています。 ただし、RS-232シリアルポートは、バーコードスキャナーなどのさまざまな技術機器とのインターフェイス、および3番目のネットワークスイッチなどのデバイス用の組み込みソフトウェアを使用してターミナルモードで作業するためのさまざまなデバッグおよび診断のニーズに引き続き使用されますレベル、コントローラー、無停電電源装置など

RS-232シリアルシグナリングインターフェイスは、5〜15ボルトのバイポーラ信号を使用し、負電圧は論理ユニットに対応し、正電圧は論理ゼロになります。 このような振幅の信号は高速でデータを送信できないため、標準シリアルポートの最大速度は115.2 kbaudに制限されています。 周波数1.8432 MHzの信号からUARTクラス16C550を同期する場合、115.2 kbaudの速度はDLLレジスタをゼロに設定し、DLMレジスタを00000001に設定することに対応します。

RS-232シグナリングインターフェイスに加えて、シリアルポートはRS-422およびRS-485規格を使用できます。これにより、電気信号の形式で10〜20 mの距離で最大10 Mbaudの速度でケーブルを介してデータを送信し、低速で最大1500 mの通信範囲を提供できます。 UARTインターフェースでRS-422およびRS-485信号規格を使用することは、厳しい動作条件向けに設計された産業用および特殊機器で一般的です。

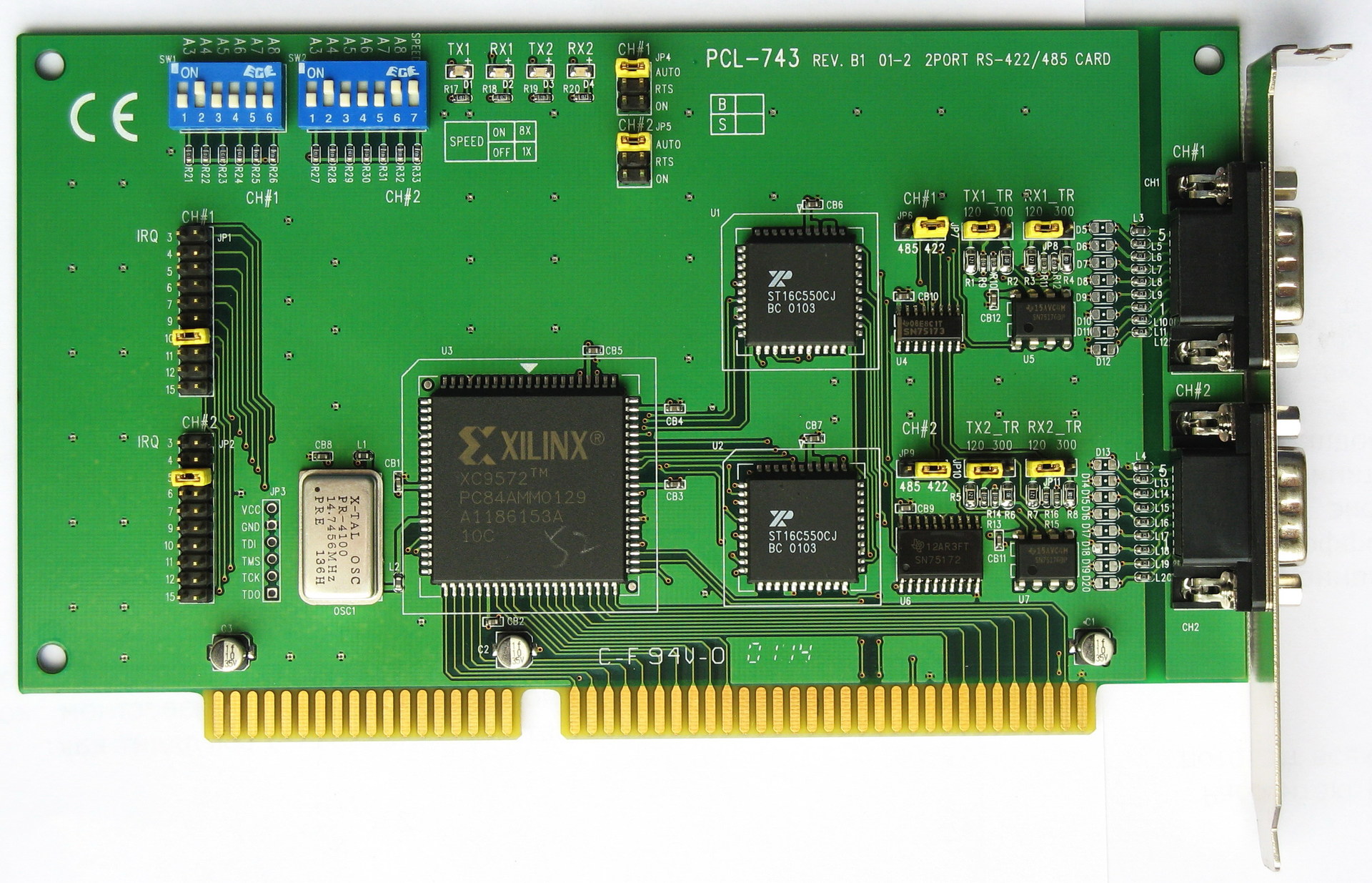

パーソナルコンピューターと産業用コンピューターをRS-422シリアルインターフェイスと接続するために、最大16個のUARTチャネルを実装する専用のI / Oアダプターが利用可能です。 例として、ISAシステムバス用のAdvantech PCL-743アダプタを考えます(図1を参照)。 1.このアダプターには、Xilinx XC9572 FPGAとRS-422 / RS485レシーバーおよびトランスミッターのマイクロ回路を制御する2つのUART 16C550コントローラーが含まれています。 スイッチを設定することにより、アダプターが16C550コントローラーに使用するアドレス範囲が設定されます。 スイッチを正しく設定すると、BIOSおよびオペレーティングシステムで定義された標準のCOMポートとして動作するようにアダプターを構成できます。 これを行うには、マザーボードのCOMポートのアドレス範囲と一致しないように、16C550コントローラーのベースアドレスをリストの値02E8h、02F8h、03E8h、03F8hに設定します。

さらに、アダプターを使用すると、RS-422規格またはRS-485規格に従って、2つのポートのそれぞれに個別に物理インターフェースを構成できます。

高速を達成するために、水晶発振器がPCL-743アダプターに取り付けられ、14.7456 MHzの周波数を形成します。これは、標準周波数1.8432 MHzの8倍です。 一番右のスイッチの位置は、16C550コントローラーの同期周波数を設定します:標準または8倍増加。 高周波での作業では、最大921.6 kbaudの速度で作業できます。この場合、ソフトウェアで115.2 kbaudの速度設定が選択されます。

アダプタボードの左側にあるジャンパを使用すると、各UARTチャネルの割り込みラインを手動で構成できます。

考慮されたアダプタは、最新のコンピューティングシステムにISAバスがないため、かなり高価で時代遅れのソリューションです。

図 1. Advantech PCL-743インターフェイスアダプター

市場で広く入手可能なPCIシステムバス用の従来の周辺機器インターフェースの安価なコントローラーを変更することにより、最大1 Mbpsの速度でRS-422規格に従って動作するシリアルポートアダプターの実装を検討することを提案します。

MosChipのMCS9820、MCS9835、MCS9845に基づくEspadaのマルチポートコントローラーが、この記事で説明されているアダプターの基盤として採用されました。 MCS9805、MCS9815、MCS9820、MCS9835、MCS9845チップファミリは、10〜12年前にNetMOSによって開発され、ピン配置と内部ロジック構成が高度に統合されました。 この統合により、共通のPCB設計を使用した多数の周辺機器インターフェイスコントローラーの開発が可能になりました。

次のEspadaコントローラーは同じPCB上に構築されており、インストールされているコネクターと電子部品の構成のみが異なります。

•FG-PIO9820-1S-01-CT01-1つのRS232ポート、MCS9820チップ。

•FG-PIO9835-2S-01-CT01-2つのRS232ポート、MCS9835チップ。

•FG-PIO9835-2S1P-01-CT01 – 1つのLPTポート、2つのRS232ポート、MCS9835チップ。

•FG-PIO9805-1P-01-CT01– 1つのLPTポート、MCS9805チップ。

•FG-PIO9815-2P-01-CT01– 2つのLPTポート、MCS9815チップ。

また、ユニファイドプリント回路基板は、外部非同期バスを備えたMCS9845チップに基づくEspadaコントローラーによって使用され、16C550、16C552、16C554タイプの追加のUARTコントローラーが接続されます。

•FG-PIO9845-4S-01-CT01-4つのRS232ポート、MCS9845チップ+ 2個。 16C550;

•FG-PIO9845-6S-01-CT01-6つのRS232ポート、MCS9845 +16554マイクロサーキット。

6つのシリアルRS232ポートを備えた最大構成コントローラーの外観を図5に示します。 2。

図 2. Espada製RS232インターフェイスアダプター

元の構成では、リストされているすべてのEspadaアダプターには、RS-232インターフェースを操作するためのレベルコンバーターがあり、最大速度115.2 kbaudで動作するように構成されています。 それにも関わらず、MCS98xx-CV超小型回路のドキュメントの初期バージョンでは、シリアルポートコントローラーの最大速度は1 MBaudです[1、2]。 後のドキュメントでは、最大速度が115.2 kbaud [3、4]に低下しました。これは、PCIバスイニシエーター(マスター)機能をサポートするより高度なMosChip MCS9865-IVインターフェースマイクロ回路の市場参入による商業的理由による可能性が最も高い。

MCS9820、MCS9835、MCS9845のマイクロサーキットには、PCI構成レジスタを介して個別に構成された8バイトのI / Oアドレス範囲を使用する最大2つの統合16C550クラスUARTコントローラーがあります。 3つ以上のシリアルポートを実装するアダプターは、PCIバスの読み取りおよび書き込みトランザクションが構成内の追加のUARTコントローラーの範囲に属するI / Oアドレスに送信される非同期8ビットローカルバスによって接続された多数のMCS9845および16C550チップセット(16C552、16C554)を使用します16C550チップ(16C552、16C554)。 追加のUARTコントローラーのI / Oアドレス範囲も、ベースアドレスレジスタ(PCI構成スペース内のBAR)を介して構成されます。 PCIコンフィギュレーションスペースレジスタは、MCS98xxマイクロサーキットの標準[5]に従って実装され、チップセットの一部としてシステムコントローラーを使用して読み取りおよび/または書き込みを行うことができます。

UARTコントローラーを同期するために、MCS9820、MCS9835、およびMCS9845マイクロ回路には2つの搬送周波数入力があります。

•ACLK信号(ピン59)は、UART-Aの搬送周波数を設定します。

•BCLK信号(ピン57)は、UART-Bの搬送周波数を設定します。

UARTクラス16C550コントローラーのキャリア周波数は、ボーレートの16倍でなければなりません。 したがって、115.2 kbaudの速度の場合、1.8432 MHzのキャリアが必要であり、1 Mbaudの速度の場合、キャリア周波数は16 MHzでなければなりません。

MosChip独自のドキュメント[1-4]によると、MCS98xxチップの一部であるクロックジェネレーターから信号を送信するために、ACLKおよびBCLK入力が提案されています。 ただし、CMOSまたはTTLレベルの外部クロックソースからの信号は、これらの入力に適用できます。

内蔵クロックには、入力XTAL1(ピン62)と出力XTAL2(ピン61)の間に接続された3つの出力周波数を生成する外部クリスタルが必要です。

•水晶振動子の周波数を3で割った周波数の3XCLK信号(端子55)

•水晶振動子の周波数を6で割った周波数の6XCLK信号(ピン56)

•水晶振動子の周波数を12で割った周波数の12XCLK信号(ピン58)。

MCS9820、MCS9835、MCS9845のマイクロ回路に基づくRS-232インターフェイスアダプターの元の構成では、周波数22.1184 MHzの水晶振動子が使用され、周波数がそれぞれ1.8432 MHzである12XCLK出力からの信号がACLKおよびBCLK入力に供給されます。

MCS9820、MCS9835、MCS9845超小型回路に基づくほとんどのアダプターには0603抵抗ジャンパーがあり、ボード上のさまざまな位置に取り付けることで、出力3XCLK、6XCLK、および12XCLKからACLKおよびBCLK入力に信号を取り付けることができます。 したがって、水晶振動子を48 MHzの周波数のアナログに置き換え、3XCLK出力へのACLKおよびBCLK入力の切り替えに対応する位置にジャンパーを再はんだ付けすると、統合されたUARTコントローラーの搬送周波数が16 MHzになります。 このような改良の後、シリアルポートのシステム速度は115.2ボー(ソフトウェア設定で)になり、実際の速度1メガボーに対応します。

Espada FG-PIO9820またはFG-PIO9835アダプターで実行されたこのような改良の結果を図5に示します。 3。

図 3. 1 MbaudをサポートするためのEspadaアダプターの改良

市場に出回っているシリアルポートインターフェイスアダプターの大半は、DB-9MコネクタへのRS-232インターフェイス出力を実装しています。 RS-232インターフェースは元々、通信機器の接続に焦点を合わせていたため、UARTクラス16C450および16C550コントローラーにも実装された多くの特別な信号があります。

従来のRS-232デバイス接続スキームには、直接ケーブルで接続されたDTE(データ端末機器)端末機器とDCE(データ通信機器)通信機器が含まれます。 「ストレートケーブル」という用語は、ソケットとプラグタイプのコネクタを備えたケーブルを意味し、コンタクトは同じ番号で接続されます(プラグのピン-1はソケットのピン-1に接続され、プラグのピン-2はソケットのピン-2に接続されます) )

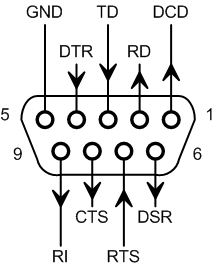

DTE端末機器の場合、DB-9Mタイプのコネクタ(プラグ)が伝統的に使用されており、その配線は図1に示されています。 4 a。 端末機器の役割は、パーソナルコンピュータ、ワークステーション、サーバー、LANスイッチ、コントローラー、または情報パッケージのジェネレーターとして機能するマイクロプロセッサを含むその他の機器です。

DCEデータ伝送機器の場合、DB-9Fコネクタ(ソケット)が従来から使用されています。その配線は図3に示されています。 4、b。 データ伝送装置は伝統的に、特別な制御信号を形成するさまざまな通信チャネル用のモデムによって表されます。nRI-交換機からの呼び出し信号およびnDCD-通信チャネルでのキャリア周波数の検出の兆候。 また、情報パッケージの受信機またはパッケージのパッシブソースとして機能する他のデバイス、たとえば、実行ユニットやセンサーは、DCEとして機能できます。

でも

b

図 4. RS-232コネクターの配線:

a-DTE用のDB-9Mプラグ、b-DCE用のDB-9Fソケット

RS-232を介したDTEおよびDCEデバイスの直接接続図を図1に示します。 5.直接インターフェースケーブルには、DTE(コンピューター)に接続するためのDB-9Fソケットと、DCE通信機器(モデム)に接続するためのDB-9Mプラグがあります。 ケーブルには、両端のプラグとソケットの金属ハウジングに接続された共通のスクリーンに9つの絶縁接続があります。

nDCDキャリアディテクタとnRIコールの特別な信号を使用しない接続では、デバイスのDTEおよびDCEタイプへの分割はかなりarbitrary意的であり、主にコネクタのタイプ(DTEのプラグとDCEのソケット)によって決定されます。

図 5. RS-232経由の直接接続のスキーム

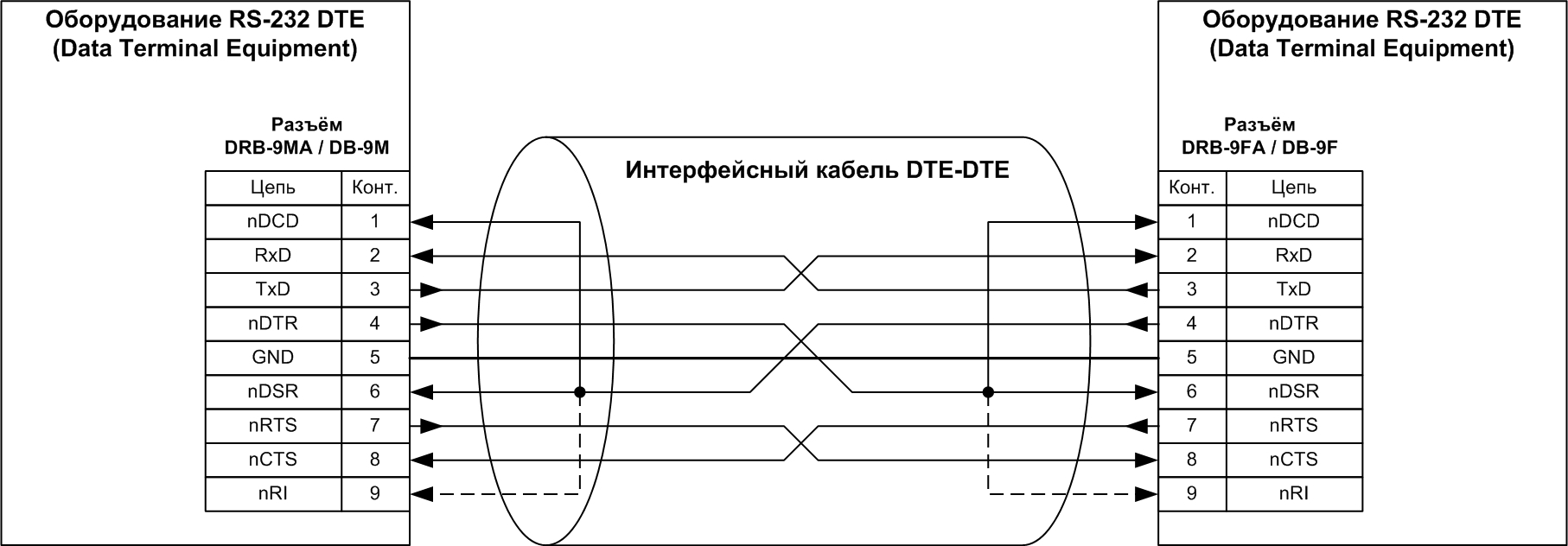

現代の機器では、統一の理由から、DTEなどのコネクタを使用することを好みます。 2つのDTEデバイスを接続するには、クロスケーブルとも呼ばれるゼロモデムケーブルを使用します。 このようなケーブルは、TxD-RxD、nRTS-nCTS、nDTR-nDSRの順に、さまざまなデバイスの送信機と受信機をペアで切り替えます。 RS-232クロスケーブルの完全な実装では、nDTR-nDCDおよびnDTR-nRI接続を確立できます。

一般に、他のすべての信号は側波帯であり、プログラムレベルでのみデータ交換プロセスに参加できるため、データ転送にはTxD-RxDスイッチングで十分です(MCRビットによってアクティブ化されるUARTクラス16C550の古いバージョンのAuto-CTSモードは例外です) [5])。

ヌルモデムケーブルを使用したRS-232インターフェイスを介した2つのDTEデバイスの接続図を図1に示します。 6。

図 6. RS-232経由のヌルモデムケーブルを使用した接続図

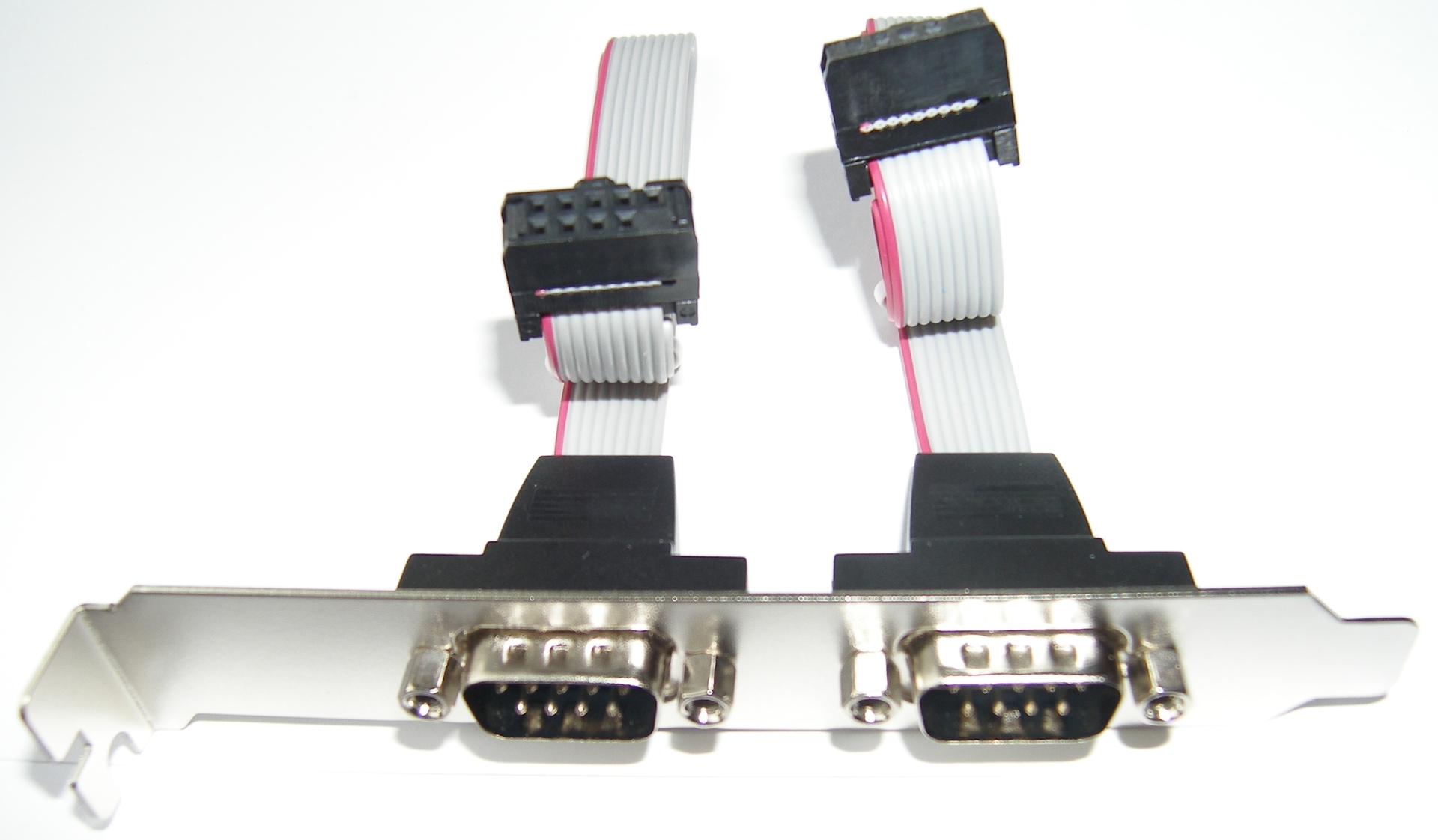

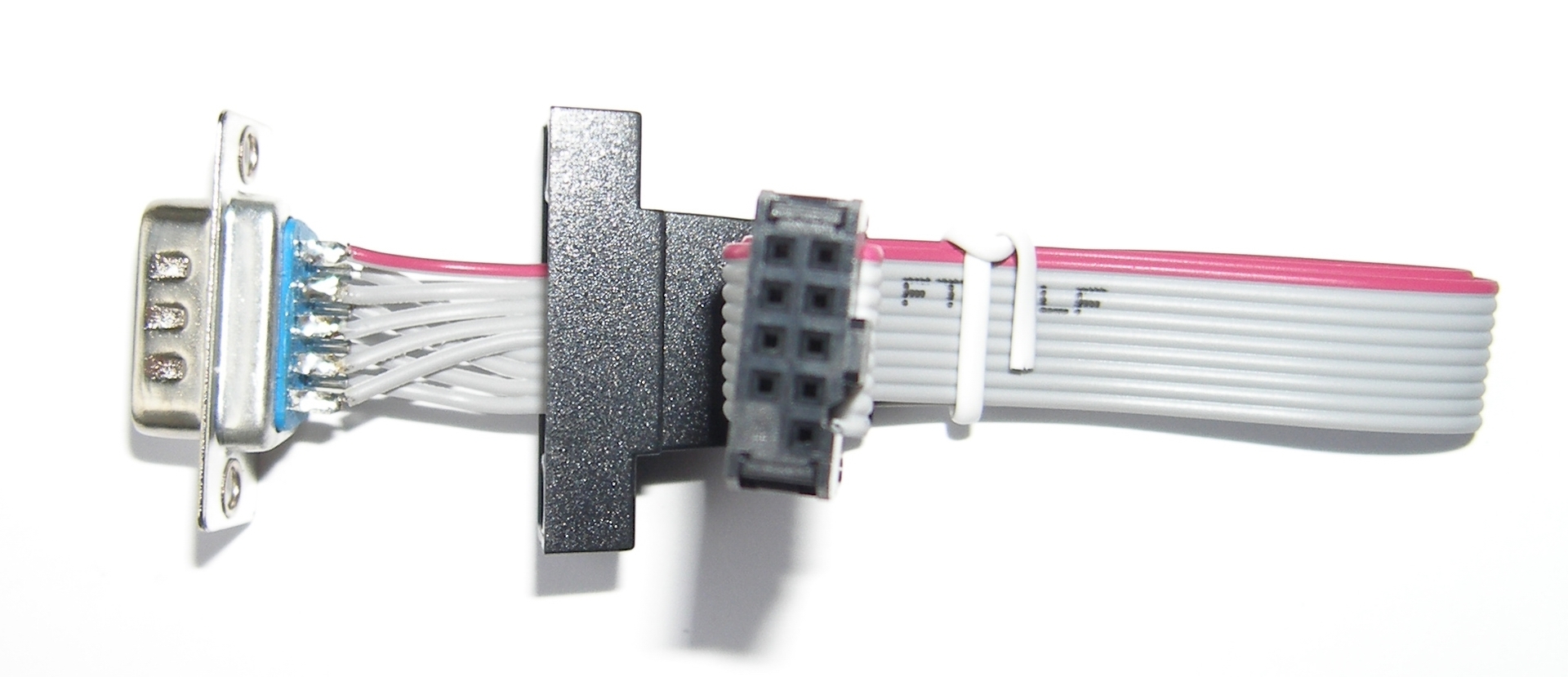

最新のRS-232インターフェイスアダプターのほとんどは、DRB-9MAコーナープラグを外部コネクタとして使用して、プリント基板に取り付け、シャーシの取り付けブラケットに固定します。 マルチポートアダプタは、DB-9Mコネクタが固定された追加のストリップを使用します。このストリップには、フラットケーブルが1.27 mmのピッチではんだ付けされ、両端にIDC-10ソケットが押し込まれています。 7。

図 7. DB-9Mコネクタ付きの追加ブラケット

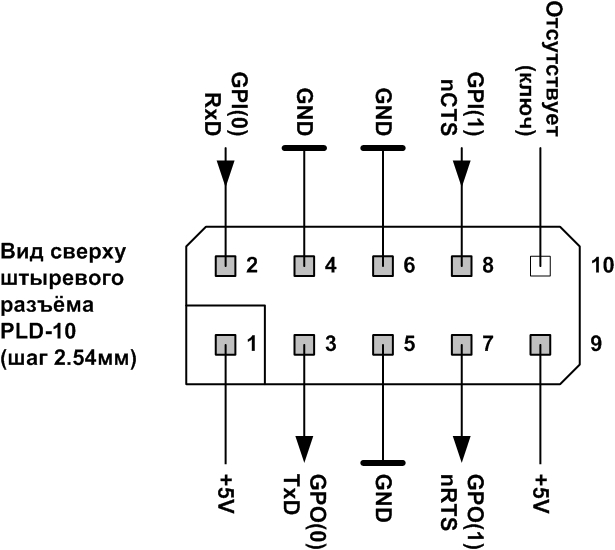

IDC-10ソケットには、10番目の接点の代わりに1つの止まり穴があり、キーとして機能します。 コントローラの回路基板上の対応物は、10番目のリモート接点を持つPLD-10ピンコネクタです。 2つの追加ブラケットを接続するためのコネクタは、図1に示すように、アダプタボードFG-PIO9845-6S-01-CT01の背面にあります。 2。

ほとんどのRS-232アダプタのPLD-10ピンコネクタの配線は、追加ストリップのケーブルのIDC-10ソケットの最初の接点が外部DB-9Mコネクタの最初の接点に接続され、IDC-10ソケットの2番目の接点が2番目に接続されるように統合されていることに注意してくださいDB-9Mピンコンタクトなど したがって、ピン番号によるピン割り当ては、外部DB-9Mコネクタのピン配列を繰り返します(図8)。 DB-9Mコネクタの対応する配線を図5に示します。 10(最初の接点はループの赤い線です)。

img src = " habrastorage.org/files/658/f59/b3c/658f59b3c3614cf68e2b2358a506fe0c.jpg " />

図 8. PLD-10オスコネクタでのRS-232信号の配線

図 9. DB-9Mコネクターの配線

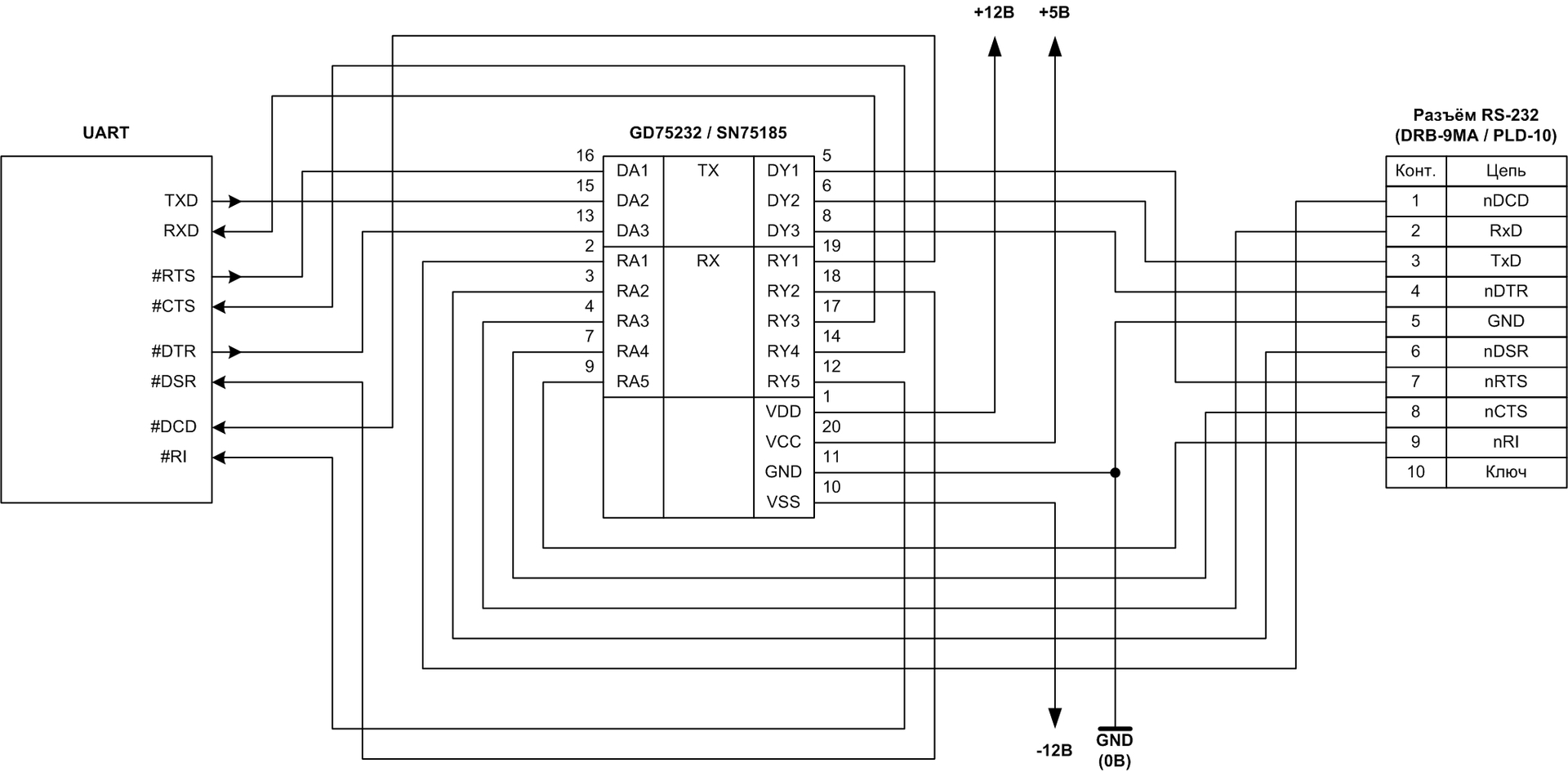

RS-232物理インターフェイスは、インターフェイスアダプターとマザーボードの両方で、従来、レベルコンバーターマイクロサーキットGD75232またはその完全なアナログSN75185 [6、7]を実装しています。 これらのマイクロ回路には、TxD、nDTR、nRTS回路用のバイポーラRS-232信号の3つのドライバーと、TTL信号に対するRS-232レベルの5つのレシーバーコンバーターが含まれています。 各GD75232 / SN75185チップは、VSS-マイナス12V、VCC-5V、VDD-12Vの3つの電源電位を使用します。 すべての電圧は、合計ゼロ(GND)に対して測定されます。

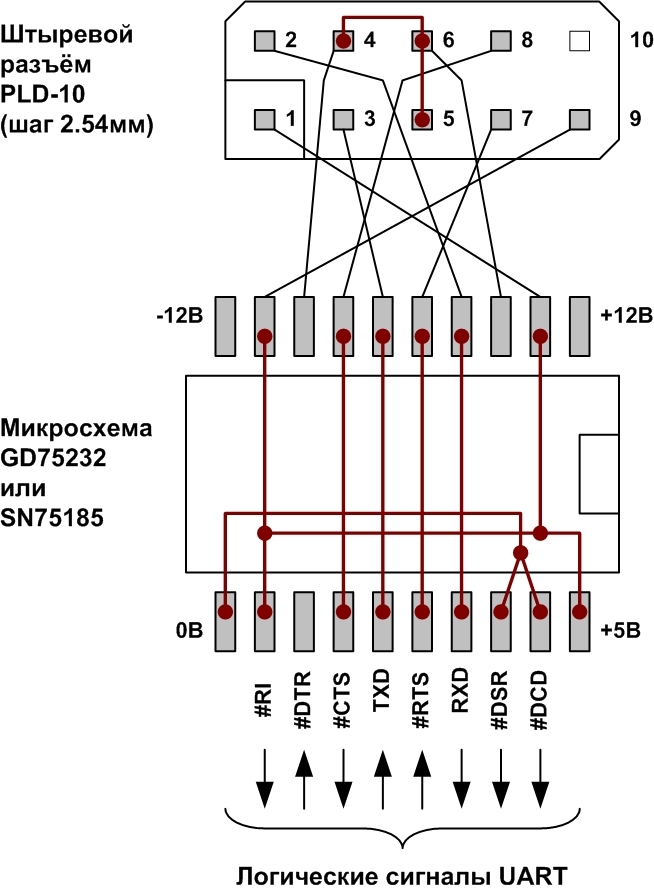

GD75232 / SN75185チップを使用して、UARTコントローラーをRS-232ポートに接続する従来の方式があります。 図に示されています。 10. Espadaボードを含むほとんどのRS-232インターフェイスアダプターに実装されているのはこの回路です。

図 10. UARTコントローラーとRS-232ポートの接続図

RS-422物理インターフェイスはTIA / EIA-422規格によって規制されており、最大10 Mbaudの速度でツイストペアワイヤを介してデータを送信できるようにする差動信号のレベルと波形を決定します(帯域幅はインターフェイスのビット深度とデータエンコーディングの方法に依存します)。

パラレルインターフェイスでのRS-422信号の使用例は、「高電圧」差動SCSIインターフェイス(HVD-高電圧差動)です。

産業機器のシリアル非同期UARTインターフェースも、物理RS-422インターフェースを使用することがよくあります。 産業用および特殊技術で一般的なRS-485差動インターフェイスとは対照的に、RS-422物理インターフェイスはポイントツーポイント接続のトポロジに対応しています。

シリアルポートでRS-232の代わりに物理的なRS-422インターフェイスを使用すると、短い接続でのデータ転送速度を上げるか、1つの接続の通信範囲を大幅に増やすことができます。

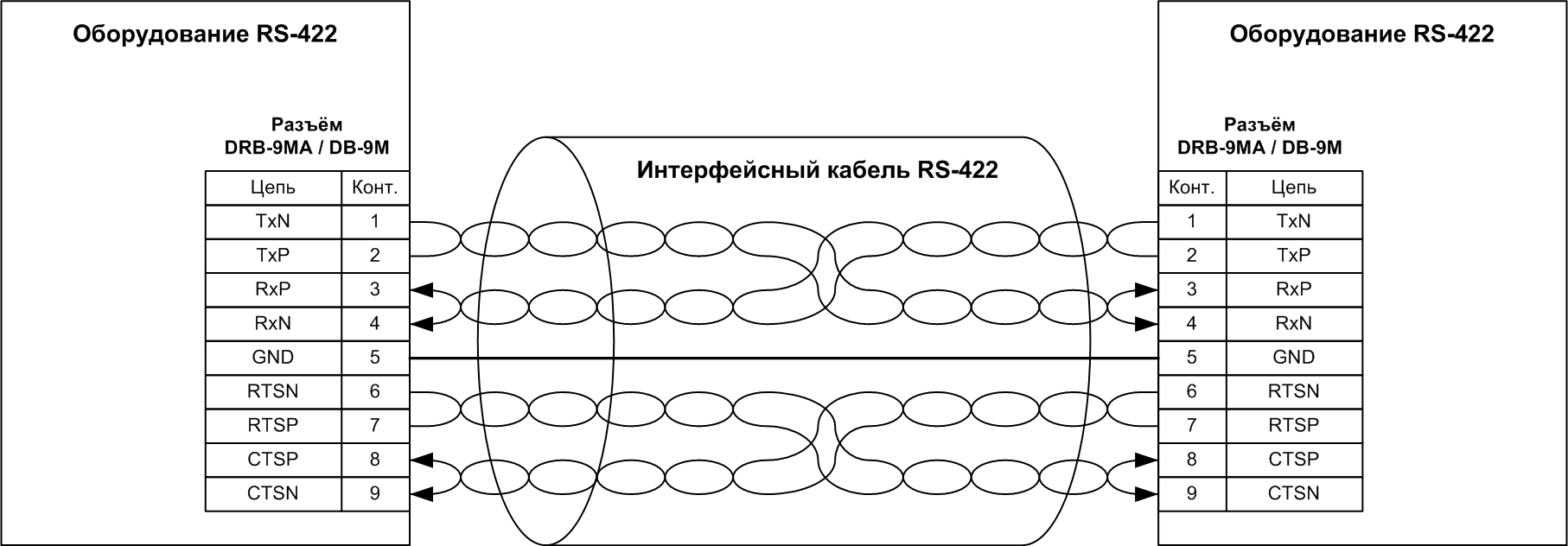

ほとんどの場合、RS-422物理層とのUARTインターフェイスの実装では、4組のワイヤを使用します。2組の順方向および逆方向のデータ伝送と、2組の補助RTS-CTS信号です。 UARTプロトコルを介して動作するシリアルインターフェイスRS-422を介した2つのデバイスの接続図を図1に示します。 11。

図 11. RS-422シリアルインターフェイスの接続図

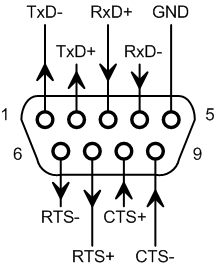

シリアルポートに適用されるDB-9コネクタには、差動RS-422信号の単一の統合配線はありません。 アドバンテックがPCL-743アダプタ(図1)に実装した配線を検討することを提案します(図1を参照)。 12。

図 12. RS-422インターフェース用のDB-9Mコネクタ配線

RS-422インターフェイスを実装するためのシリアルポートアダプタの再装備は、次の方法で実行することを提案します。

1. RS-232レベルコンバーターのマイクロチップを分解します。

2.次のUARTコントローラー信号をPLD-10ピンコネクタに接続します:TxD、RxD、nRTS、nCTS。

3.低レベル(GND)をUARTコントローラーのnDCDおよびnDSR入力に、高レベル(+ 5V)をnRI入力に適用するか、UARTコントローラーの信号を接続します:nDTR-nDSR-nDCD-nRI、

4. PLD-10オスコネクタの接点1および9に、+ 5Vの電位を印加してRS-422トランシーバーに電力を供給し、

5. PLD-10アダプターピンコネクターにRS-422トランシーバーモジュールを取り付けます。このコネクターには、ブラケットに取り付けられたDB-9MコネクターからのケーブルでIDC-10ソケットが接続されます。

6. PLD-10コネクタのピン4と6をGND回路に接続します。

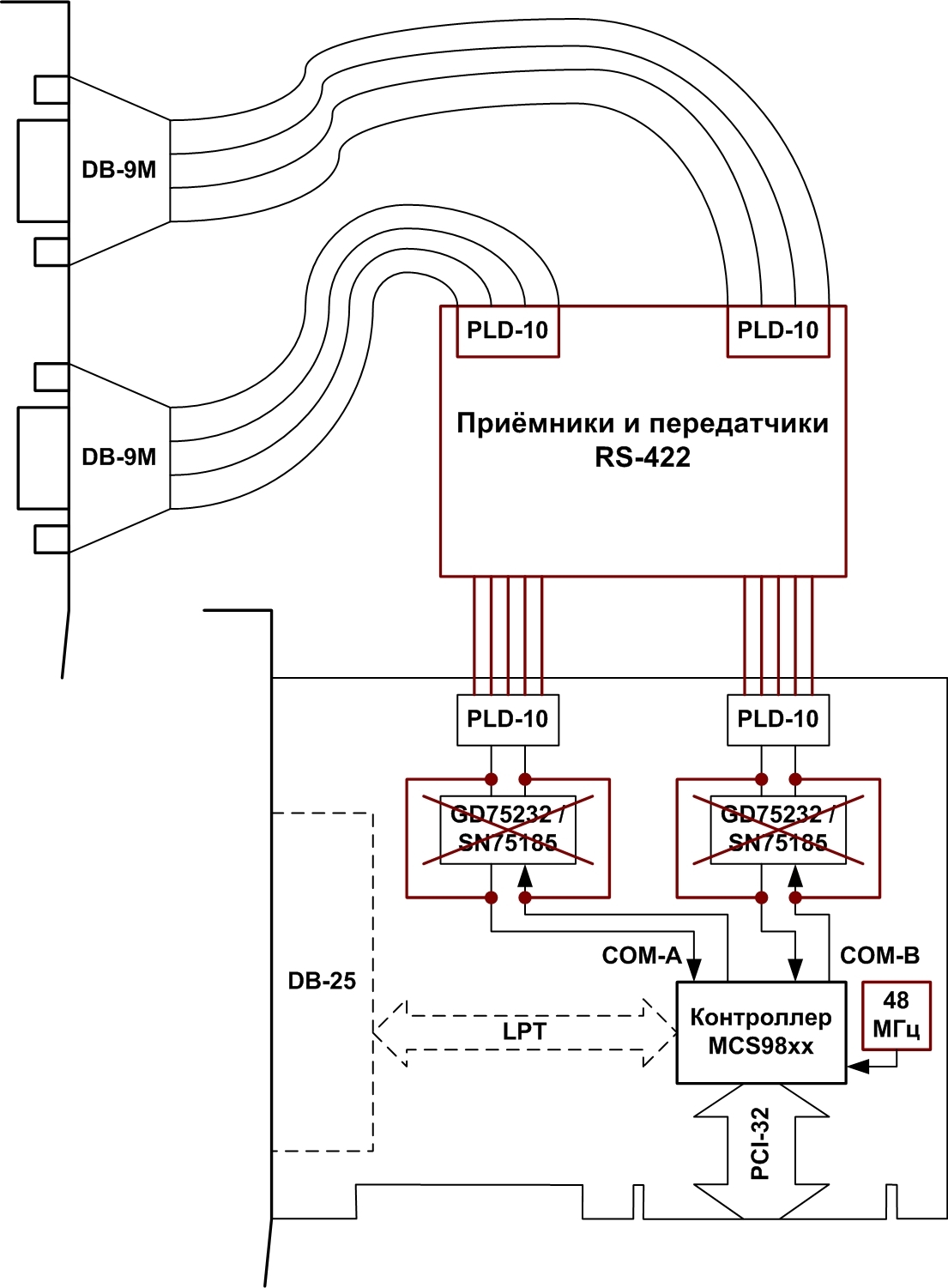

概略的に、記載されているアダプターの近代化の原理は図に反映されています。 13。

図 13. RS-422インターフェース用のRS-232アダプターの再装備

説明されたアクションの結果として、PLD-10ピンコネクタの信号配線は図に従って変化します。14。

図 14. PLD-10ピンコネクタでのUART信号の配線

GD75232 / SN75185フットプリントのボリュームのパッドを使用して、MGTF取り付けワイヤなどを使用してアダプタPCBの開発を完了することを提案します。UARTコントローラのアイドル信号nDTR、nDSR、nDCD、nRIを切り替えるための2つのオプションの接続トポロジを図5に示します。15.ピンコネクタの位置は、Espada FG-PIO9820およびFG-PIO9835アダプタの例に示されています。

でも

b

図 15.アダプターが再装備された後の接続トポロジ

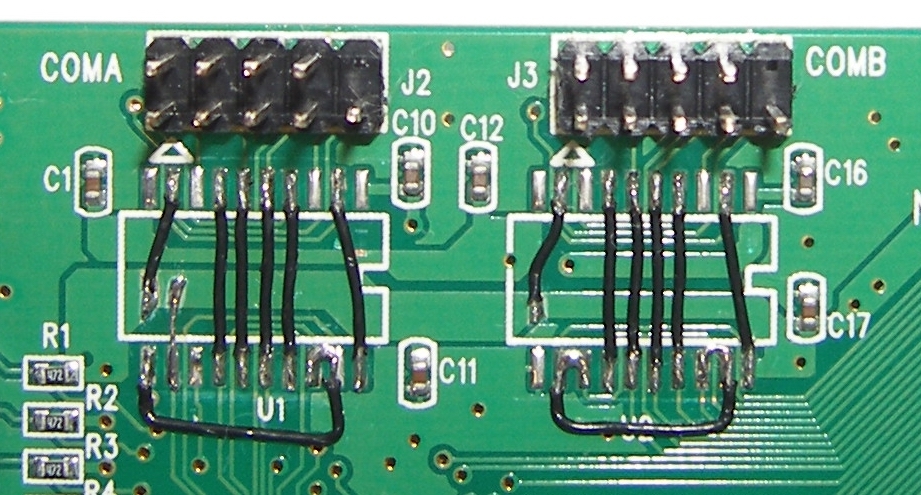

統合されたGD75232 / SN75185マイクロサーキットスイッチング回路(図10)を考慮すると、変更を完了するには、これらのマイクロサーキットを解体し、図から類推してワイヤーからジャンパーを取り付けるだけで十分であると結論付けることができます 15. GD75232 / SN75185チップを分解した後のアダプターFG-PIO9835-2S1P-01-CT01のプリント基板の図を図15に示します。16.図による接合部の最終形態 単一のボード上の図15、aおよび図15bによると、図16を示す。17。

図 16.チップGD75232 / SN75185を分解した後のアダプターFG-PIO9835-2S1P-01-CT01のプリント基板

図 17. 2つの変更オプションを備えたFG-PIO9835-2S1P-01-CT01アダプタープリント回路基板

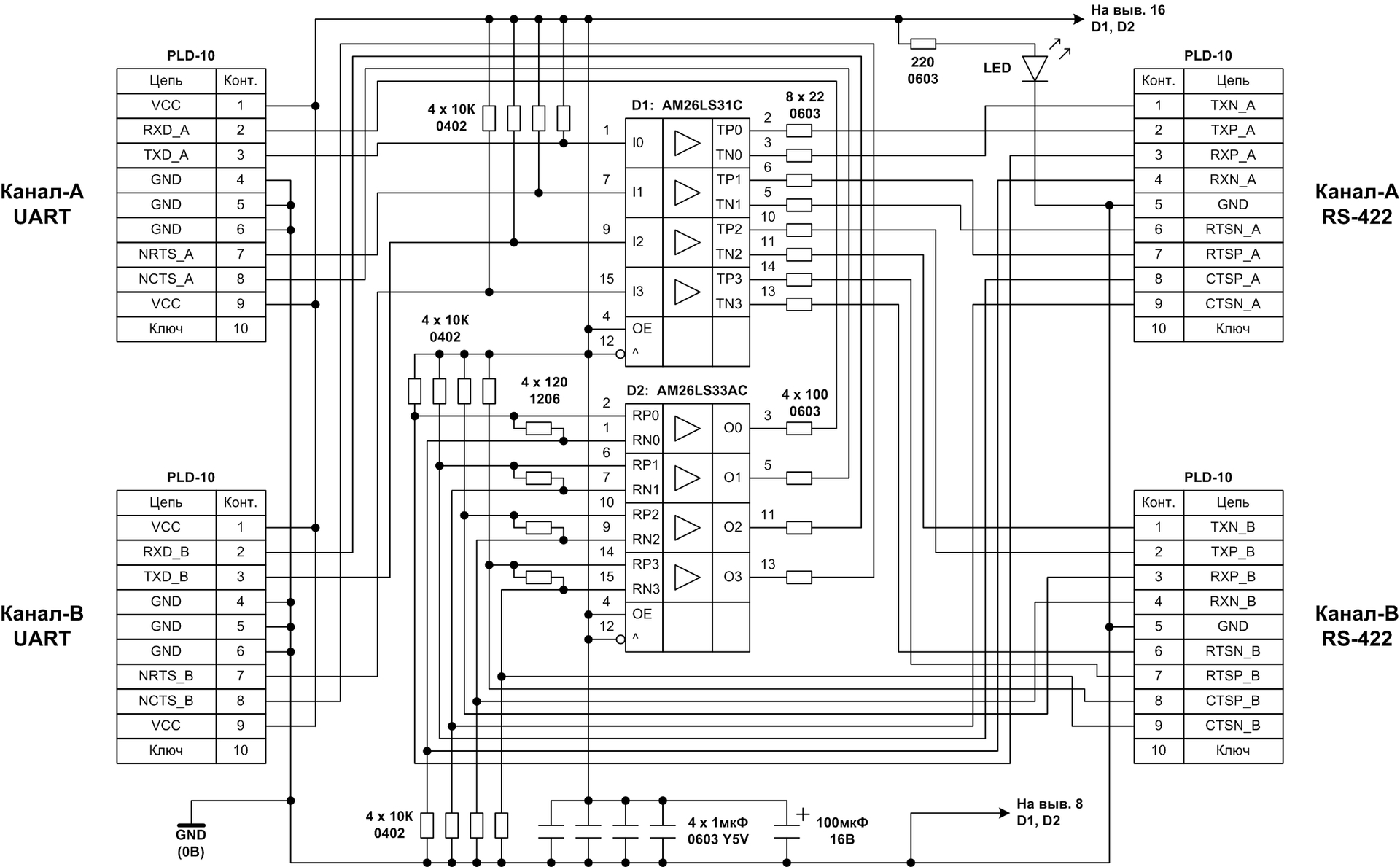

AM26LS31CトランスミッターとAM26LS33ACレシーバーマイクロ回路を使用して、RS-422トランシーバーモジュールを別の回路基板に実装することを提案します [9、10]。 RS-422トランシーバーモジュールの回路図を図1に示します。 18.モジュールにはPLD-10ピンコネクタ用の4つのシートがあり、そのうち2つはアダプタコネクタへのはんだ付け用に設計され、他の2つはブラケットからケーブルを接続するためのPLD-10Rコネクタを取り付けます。

図 18. RS-422

トランシーバーモジュールの概略図図に示す電気回路に従ってRS-422トランシーバーモジュールを実装するプリント回路基板のトポロジ。図18 19.プリント回路基板は内部層なしで作られており、SOIC-16パッケージにAM26LS超小型回路と、電気回路図に寸法が示されているチップコンポーネントを取り付けるように設計されています。電解アルミニウムコンデンサの直径は5または6 mm、高さは8 mm以下です。 LEDはバージョン1206でも、リード線で穴に取り付けることもできます。

回路の左側にあるコネクタはボードに取り付けられていません。アダプタボードに取り付けられたPLD-10ピンコネクタの自由端は、穴にはんだ付けされます。

サイズ1206の120オームの抵抗器は、長いケーブル接続に必要なインピーダンスを一致させる機能を実行します。公称値が10 kOhmの抵抗器が設置され、ラインに信号源がない場合に電圧レベルを受動状態にシフトします。

公称値が100オームの直列抵抗は、5ボルトの電圧の入力信号レベルを許可しないUARTコントローラーと接続された場合に電流を制限するように設計されています。

トランスミッタを過電流から保護するために、公称値が22オームの直列抵抗が取り付けられています。このような保護が必要ない場合は、これらの抵抗の代わりに、サイズ0603のジャンパを取り付ける必要があります

ボードのトポロジは、Espadaアダプタで使用するように設計されています。

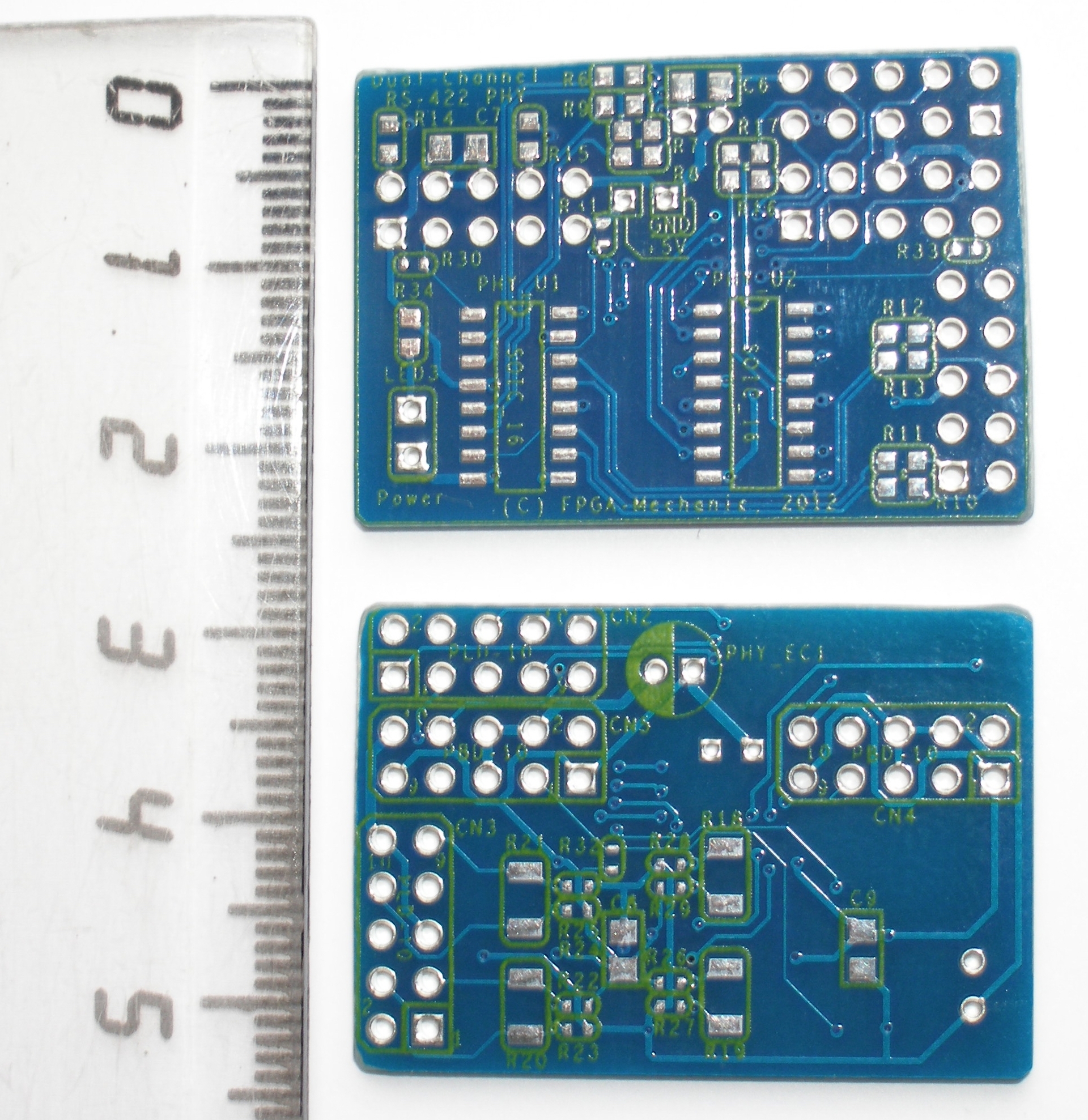

図 19. RS-422

トランシーバーモジュールのプリント回路基板のトポロジーRS-422トランシーバーモジュールは、AM26LS31およびAM26LS33マイクロ回路をDIP-16パッケージに取り付けることにより、2.5 mmまたは2.54 mmの穴ピッチのブレッドボードを使用して組み立てることができます。この実施形態は、図1に示されるようなカスタムプリント回路基板の製造コストを回避する。 19、しかしインストール作業の複雑さとボリュームを増加させます。ブレッドボード上の接続は、取り付けワイヤを使用して行う必要があります。

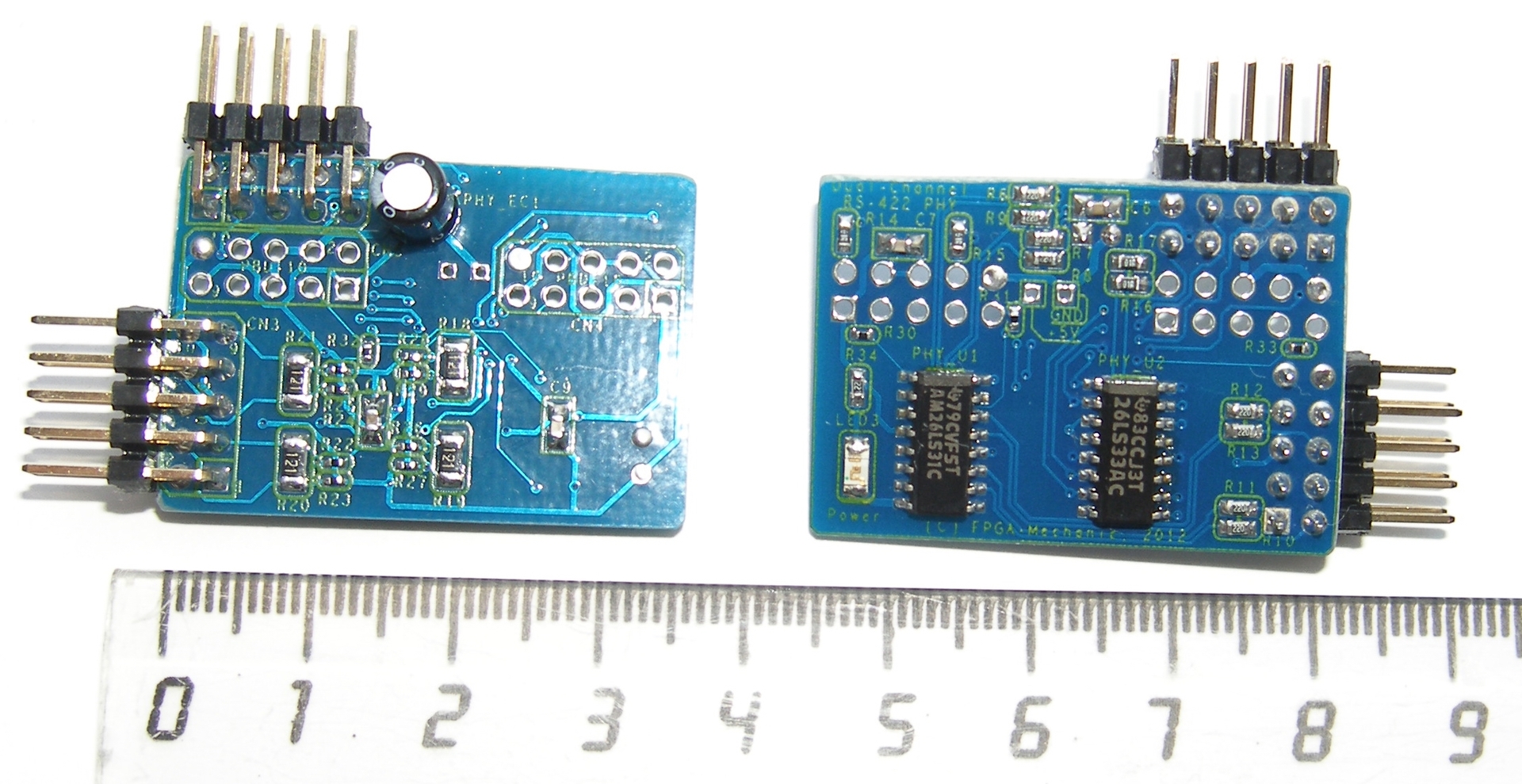

組み立てられたRS-422インターフェーストランシーバーモジュールの外観を図20(シングルチャンネルバージョン)および図21に示します。 21(2チャネル実行)。

シングルチャネルモジュールには、公称値が22オームの電流制限抵抗器、サイズが1206の120オームの整合抵抗器、および1つのコネクタはありません。リストされたコンポーネントは、2番目のUARTチャネルで使用されます。設計のシングルチャネルバージョンは、MCS9820チップ上に構築された1つのシリアルポートでアダプターを完成させるように設計されています。完成したアダプターEspada FG-PIO9820-1S-01-CT01の画像を図1に示します。22。

図 20.シングルチャネルRS-422トランシーバーモジュール

図 21. 2チャンネルRS-422トランシーバーモジュール

:モジュールは、AM26LS31およびAM26LS33チップが上にくるようにアダプターに取り付けられます。これにより、障害が発生した場合の交換が簡単になります。

図 22.シングル

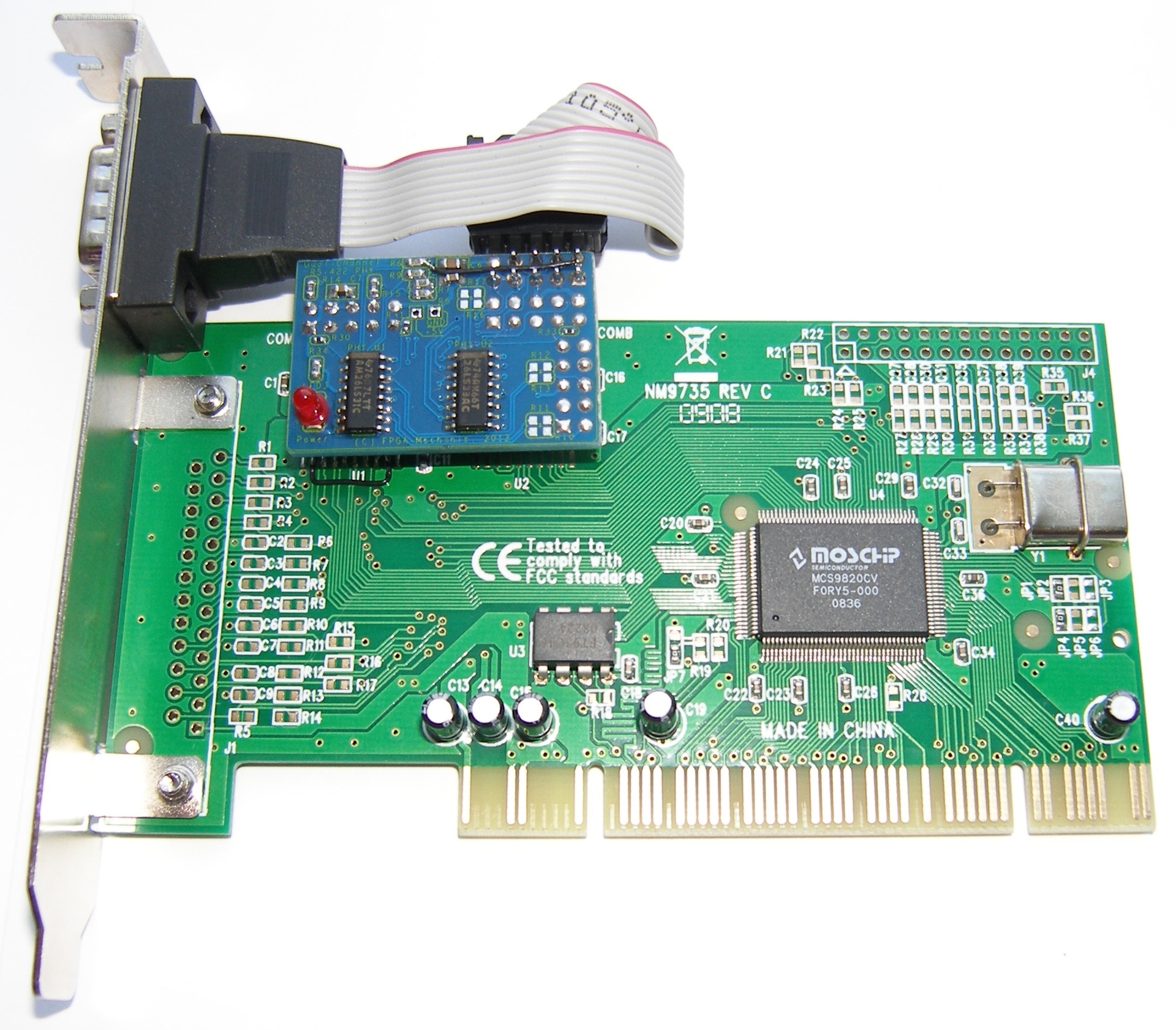

チャンネルRS422シリアルインターフェースアダプター 2チャンネルRS-422トランシーバーモジュールは、MCS9835マイクロサーキット上に構築された2つのシリアルポートを備えたアダプターへのインストール用に設計されています。モジュールのコネクタ間の距離は、Espada FG-PIO9835-2S-01-CT01およびFG-PIO9835-2S1P-01-CT01アダプタのプリント基板に対応しています。完成したアダプターEspada FG-PIO9835-2S1P-01-CT01の画像を図1に示します。23。

図 23.デュアルチャネルRS422シリアルインターフェイスアダプター

変更されたEspadaアダプターは、ワークステーションの一部としてMicrosoft Windowsのシリアルポートを操作するための診断ソフトウェアによってテストされました(図24)。テストは、マシンへの直接相互接続(ゼロモデム)に4ペアネットワークUTPケーブルを使用し、RxDへのTxDデータパスとCTSへのRTS制御パスを閉じるプラグで実行されました。 UTPケーブルでは、各ツイストペアは差動信号の1つを送信するために使用されます。 2つのペアはクロスオーバーTxD-RxDおよびRxD-TxDを実装し、残りの2つのペアはクロスオーバーRTS-CTSおよびCTS-RTSを実装します。シャーシの低品質の接地またはRS-422シリアルインターフェイスを介して絶縁されたシャーシでデバイスを接続する場合、シャーシを接続するケーブルに追加の回路を実装する必要があります。これは、デバイス間の電位を等しくするために必要です。そうしないと、電位差によってインターフェイストランシーバが損傷する可能性があります。 AM26LS33ACチップを使用すると、入力電圧をゼロから15ボルト以下だけずらすことができます。

図 24. RS-422デュアルポートアダプターの

テストテストプラグはDB-9Fソケットで、D-Subコネクター用の折りたたみ可能なプラスチックハウジングに収納されています(図25)。ハウジング内で次の接続が行われます:1-4、2-3、6-9、7-8。

テストは、15.2ボーのシステム速度で失敗せずに合格しました。これは、1メガボーの実際の速度に対応します(水晶振動子の交換と分周器の変更により)。

図 25.テストプラグ

MosChipマイクロチップの欠点の1つは、33 MHz PCIバス周波数の制限です。クロック周波数が66 MHz(66.667 MHz、15 nsの周期)のバスセグメントで動作するには、他のメーカーのコントローラーを使用できます。このようなコントローラーを使用した手頃な価格のソリューションとして、Espada FG-PMIO-B1T-0001S-1-CT01アダプターをお勧めします。このアダプタは、SystemBase [8]のSB16C1052PCIチップに基づいています。

SystemBase SB16C1052PCIコントローラーは、最大66 MHzの周波数を持つ32ビットPCIバスのターゲットインターフェイスをサポートし、大容量FIFOバッファーを備えた1つまたは2つのシリアルポートを実装します。従来の16C550クラスコントローラーでは256バイト対16バイト。

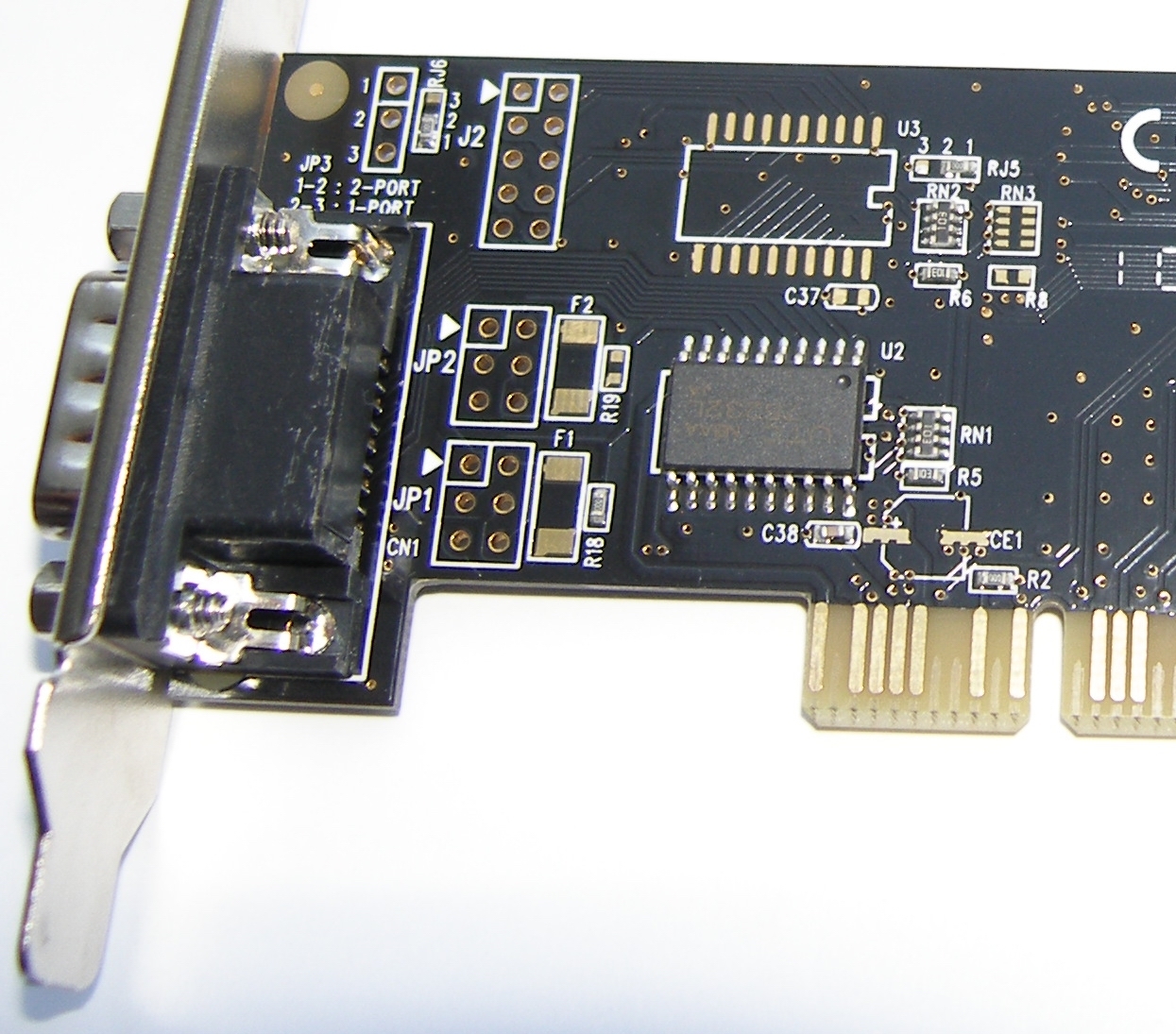

実験のために、RS-422インターフェイスをサポートするために、シングルチャネルアダプタFG-PMIO-B1T-0001S-1-CT01が完成しました。同時に、標準のRS-232ポートは変更されていません。抵抗ジャンパーRJ6を位置2-3にはんだ付けすることにより、SB16C1052PCIコントローラーの2番目のUARTインターフェイスがアクティブになり、U3チップのシートに移動します。ゼロ抵抗R19を取り付けると、2番目のポートの9番目のピン(nRI回路)がU3フットプリントの9番目の接触パッドに接続されます(図26)。 RS-232レベルコンバータとJ2ピンコネクタの配線は、図2の回路に似ています。 10.したがって、図10に示す改良を実行することにより、図15に示すように、座席J2にピンコネクタを取り付けると、図16に示すピン配列でUARTインターフェイスが得られます。 14。

シングルチャネルRS-422トランシーバーモジュールが取り付けられた、変更されたアダプターFG-PMIO-B1T-0001S-1-CT01の図を図1に示します。27. 2番目のポートの外部コネクタは、フラットケーブル付きのDB-9Mプラグの形で、その端にIDC-10ソケットが押し込まれています(図9)。DB-9Mプラグは、ブラケットに取り付けるか、適切なスロットを使用してエンクロージャの壁に直接取り付けることができます。

その結果、結合された2ポートアダプターRS-232とRS-422になります。この場合、両方のシリアルポートは標準の速度セットで動作します。

図 26.レベルコンバーターRS-232アダプターFG-PMIO-B1T-0001S-1-CT01のトポロジー

図 27.変更されたアダプターFG-PMIO-B1T-0001S-1-CT01

結論

•RS-422インターフェイスを使用すると、最大1 Mbpsの速度で動作するシリアルポートインターフェイスを構築でき、RS-232インターフェイスと比較してケーブル長を大幅に延長することもできます。

•MosChipのMSC98xxシリーズのチップを使用すると、1 MBaudの速度でシリアルポートを操作できます。これには、アダプターの簡単な適合が必要です。

•物理的なRS-422インターフェースは、2つの超小型回路と少数の受動部品に実装できます。これは非常に安価な技術ソリューションです。RS-422トランシーバーモジュールは、3x4 cmの小さなプリント基板上

に構築できます•RS-422ケーブルインフラストラクチャを構築するには、波動インピーダンスが100オームの標準UTPまたはFTPネットワークケーブルが適しています。

引用文献

1. MCS9820 PCIシングルUART。データシート改訂 2.0。MosChip Semiconductor、2006年5月22日

。2. MCS9835 PCIデュアルUARTとプリンターポート。データシート改訂 2.0。MosChip Semiconductor、2006年5月22日

。3. MCS9820 PCIシングルUART。データシート改訂 2.4。MosChip Semiconductor、2007年7月29日

。4. MCS9835 PCIデュアルUARTとプリンターポート。データシート改訂 2.4。MosChip Semiconductor、2007年7月31日

。5. PCIローカルバス仕様。リビジョン3.0。-PCI Special Interest Group、2002年-344秒。

6. GD65232、GD75232複数のRS-232ドライバーおよびレシーバー。Texas Instruments SLLS206J。1995年5月、2004年11月改訂

。7. SN75185複数のRS-232ドライバおよびレシーバ。Texas Instruments SLLS181D。1994年12月、2006年1月改訂

。8. SB16C1052PCIデュアルUART搭載PCIターゲットインターフェイスコントローラー。データシートリビジョン1.00。システムベース株式会社 2009年7月

。9. AM26LS31C、AM26LS31M 4倍差動ラインドライバー。Texas Instruments SLLS114I。1979年1月、2006年2月改訂。

10. AM26LS32AC、AM26LS32AI、AM26LS32AM、AM26LS33AC、AM26LS33AMクワッド差動ラインレシーバー。Texas Instruments SLLS115D。1980年10月、2002年3月改訂。