最初に、セットアップとホールドを定義しましょう。

- セットアップのインストール時間は、データ入力でのトランジェントの完了から、ブロックの前面がトリガーのクロック入力に到達するまでの最小時間です。

- ホールド時間ホールド-ブロックの前がクロック入力に到達した瞬間から、トリガーデータの入力で新しいトランジェントが開始されるまでの最小時間。

トリガー入力でのイベントについて書いているのはなぜですか? 静的時間分析は遅延を計算するためのグラフを作成し、要素の入力はこのグラフの頂点であるためです。 グラフの構築と静的時間分析の内部「キッチン」の詳細については、最初のメモhttps://habrahabr.ru/post/273849/を参照してください 。

次に、セットアップとホールドの違反がどのようにチェックされるかについて話しましょう。 同期回路では、すべての過渡現象はクロック入力で始まります(または、外部発振器またはPLLの出力で始まりますが、静的解析は超小型回路の限界を超えないため、超小型回路のクロック入力についてのみ説明します)。 そのため、過渡プロセス(クロック、クロックパルス)は回路に沿ってトリガーのクロック入力に伝播し、出力の前にトリガーを通過してロジックに落ち、これらのトリガーレシーバーの入力で終了する多くのトランジェントに分割されます。 同期回路の動作の主な条件:すべての過渡は1サイクルで終了する必要があります。 または、より正確には、1クロックサイクルではなく、次のクロックパルスが到着するまでに、実際のマイクロ回路のクロック回路はツリーの原理に基づいて構築されているため、トリガーごとに異なります。

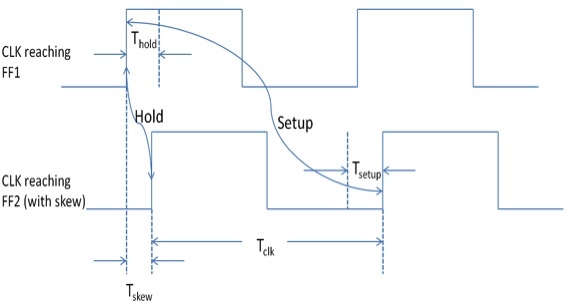

ツリーについて。 明らかに、クロック回路には非常に多くの負荷があり、すべてのロジック要素に十分な電力を供給するロジック要素はありません。 したがって、クロック回路はツリーの形で設計され、その最上部はマイクロ回路のクロック入力であり、ブランチはパワーバッファーまたはインバーターであり、リーフはトリガーのクロック入力です。 ツリーは完全ではありません(意図的にこの方法で作成されることがよくあります)。そのため、さまざまなトリガーにタクトが同時に到着することは常にありません。 このため、回路の一部では過渡現象が早く終了し、他の部分では後で終了する必要があります。これは、クロックパルスが到着する前にTsetupに間に合うようにするためです。 次の図を見てみましょう(図と式は、英語の記事http://www.edn.com/design/systems-design/4392195/Equations-and-Impacts-of-Setup-and-Hold-Timeから取られています )

この図は、トリガーFF1とFF2にクロックパルスが到着する波形を示しています。トリガーFF1とFF2の間には、信号を遅延させる特定の組み合わせ回路があります。 つまり、FF1は信号のトリガーソース、FF2はレシーバーであり、ロジックを介した信号は、入力条件によっては、非常に速く、非常にゆっくりと到達する可能性があります。 表記を扱いましょう:Tskew-クロックツリーのスキュー。これは、FF2のクロックがFF1よりもTskewの値だけ遅れているためです。 Tc2q-クロック入力とデータ出力の間のトリガー内部の信号遅延。 同期回路では、すべての過渡現象の原因はクロックパルスであるため、信号パスはクロック入力を介してトリガーデータ出力を経由し、ロジックを経由します。 Tcombはロジックの遅延、Tclkはクロック周期、Tsetupは上記で定義されたトリガー特性(セットアップ)です。

写真を見ると、トリガーデータの入力でのトランジェントの最大終了時間は、次の不等式(1)を満たす必要があることがわかります。

Tc2q + Max(Tcomb) + Tsetup ≤ Tclk + Tskew (1)

ここで、Max(Tcomb)はTcombの可能な最大値です。 式から、不等式の違反に対処する方法は2つあることがわかります。クロックパルスの到着の瞬間を右にFF2に移動する、Tskewを変更する、またはMaxロジック(Tcomb)の遅延を減らす

ここで、ホールド違反に対処してみましょう。 一般に、セットアップの違反が次のクロックパルスの到着の瞬間と比較されるため、セットアップの違反が次のメジャーに関連している場合、ホールドの違反は現在のメジャーですでに確認する必要があります。 ホールド違反はどのように発生しますか? 写真によると、FF1の出力からの信号がロジックを非常に速く通過するため、FF2の入力のデータが損なわれると、現在のクロックサイクルで違反が発生します。 これは、FF1の出力からの信号がTskew用に調整されたThold時間よりも速く到着できないという条件を意味します。 不等式を得る(2)

Tc2q + Min(Tcomb) ≥ Thold + Tskew (2)

ここで、Min(Tcomb)はTcombの可能な最小値です。 この式から、Tskewを移動するか、ロジックMin(Tcomb)の遅延を増やすことで違反に対処することもできます。

次に、CADが違反の排除にどのように取り組んでいるかについてお話しましょう。 その主なタスクは、設計された回路の速度を拡張することです。 設計のいくつかの場所で1.2 nsのロジック遅延がある一方で、1 GHzの周波数を取得する必要があるとします。 CADはこのロジックを1 nsに圧縮しようとするか、トリガーレシーバーのTskewが200 psになるようにクロックツリーをスキューしようとします。 似たようなものが上の写真に示されています。 通常、ロジックは圧縮できないため、CADが最初に行うことは、クロックツリーを再構築し、それによってTsetup違反を排除することです。 Tskewの増加に伴い、ホールド違反のリスクが増加することに注意してください。

目的の周波数に達すると、ホールド補正の順番になります。 今回はCADはクロックツリーに触れず、2番目のトリック-Min(Tcomb)の増加、つまり ホールド違反が存在するロジックの最小遅延。 遅延は非常に単純に増加します-バッファ要素を挿入することにより。 もちろん、バッファを追加すると、回路の消費量が増えます。

加熱、電力の低下、放射線の蓄積、または経年変化による回路の遅延の増加が、マイクロ回路の動作周波数の低下によって相殺されるのは不思議です。 実際、式(1)からわかるように、遅延が増加する場合、Tclkを減らす必要があります。 しかし、過剰な冷却または供給電圧の増加により回路の遅延が減少した場合、マイクロ回路のホールド違反を修正するものは何もありません-マイクロ回路は式(2)から単純に動作を停止します。 それでは、マイクロチップはどのように低温、さらには極低温用に設計されていますか? ほとんどの場合、そのようなスキームは通常の方法で設計されますが、保留の大きな予備を作成します。 供給量が多いほど、計算された温度以下で超小型回路を冷却することが可能になりますが、その量を示すのは実験のみです。 また、パフォーマンスの低下を伴う最も均一な(最も一般的に使用されるいわゆるHツリー)を優先してスキューしたクロックツリーを拒否すると、違反の可能性も低下します。 そして最も信頼できる方法は、パラメトリック障害に完全に耐える非同期(SI、DI)回路を設計することです。

さて、結論として、FPGAはそれと何の関係があるのでしょうか? まず、ハブにASICセクションがありません 第二に、良いFPGAは遅かれ早かれASICの設計に成長します。 そして第三に、クロックスキューの操作でFPGAが去勢されていても、それらは去勢されたままです。 誰かがこの記事を役に立つと思うことを願っています。