トリガーとは何かを覚えておいてください

古典的なDトリガーは、最新のデジタルマイクロ回路に情報を保存するための基本ユニットです。 高レベルの抽象化では、データ入力D、データ出力Q、および入力制御クロック信号(clk-英語の用語ではクロック)を備えたメモリデバイスです。 ここでのすべての信号は論理的であり、論理0(以下「0」)または論理1(以下「1」)のいずれかです。 ボルト単位の電圧の絶対値にはまだ興味がありません。 信号エッジがクロック入力に到着すると、つまり 「0」から「1」に移行すると、トリガーはデータDの入力で現在の値を記憶し、それを出力Qに渡します。他のすべての状況では、トリガーは古い値を保存し続けます。 また、トリガーには他の制御信号、特にaclr非同期リセット信号が存在する場合があり、これは他の入力に関係なくトリガーを「0」に設定します。

トリガーには、正しい操作のために満たす必要がある2つの時間パラメーター(要件)があります。

- Ts-セットアップ時間-プリセット時間。 入力Dの信号がクロック信号のエッジに到達する前に安定している必要がある時間。

- Th-保持時間-保持時間。 クロック信号のエッジの到着後、入力Dの信号が安定している必要がある時間。

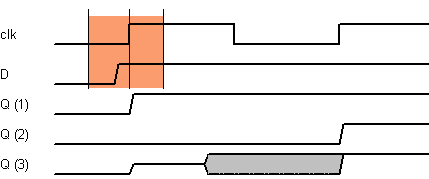

これらの2つのパラメーターの合計は、入力データが安定している必要があるクロックエッジの近くの時間ウィンドウを提供します。 他の入力、特に非同期リセット入力(回復および削除時間と呼ばれます)には、同様のパラメーターがあります。 これらの要件を順守しないと、トリガーの状態が未定義になります。 最も単純なケースでは、ブロックの正面のすぐ近くにあるデータ入力Dで受信された「古い」または「新しい」値ですが、どれが不明であるかです。 多くの場合、これは調整できます。 次の図では、出力Q(1)およびQ(2)は、入力時間パラメーターに違反した場合のトリガー操作の2つの実装です。

空中でホバリングするコイン

ただし、時間パラメータに違反すると、デジタル世界が境界を超えて、「0」または「1」に明確に対応する状態を採用する代わりに、トリガー出力が中間状態でぶら下がり始め、電圧が「0」と「 1 "。 「メカニカルワールド」からの大まかなアナロジーは、ヘッダーイメージで取り出されます。 安定した位置では、ボールは左または右にあります。 別の状態になるには、プッシュする必要があります。 あなたがそれを十分に強くすれば-それは簡単にトップを通過し、反対側でそれ自身を見つけます(通常のトリガー切り替え)。 プッシュが弱すぎる場合-すぐにロールバックします。 あなたが幸運な人なら、ボールを押すチャンスがあります、あなたはそれを正確にトップでフリーズさせます。

メタスタビリティと呼ばれるのはこの効果です。 上の図では、このオプションはQ(3)として指定されています。 最終的に、トリガーは特定の状態の1つに「落ち」ますが、いつ発生するかを正確に言うことはできません。 準安定状態でのトリガーの滞留時間は確率的な量であり、要素ベース、温度などの技術パラメーターに依存します。 オシロスコープでは、この画像は次のようになります(トリガータイミングに違反する入力信号は青で表示され、トリガー出力はピンクで表示されます)。

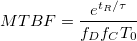

なぜ準安定性が悪いのですか? 第一に、この状態自体は不定であり、後続の要素で未知の結果を引き起こします。 さらに、多くの場合、1つのトリガーの出力信号は、他のいくつかの要素にすぐに適用されます。これは、技術基盤が不完全であるため、しきい値がわずかに異なる場合があります。 したがって、同じ信号は、ある場所では「1」、別の場所では「0」として解釈されます。 これは、デバイスのさまざまな部分の不一致と一般的な誤動作(つまり、デバイス自体が終了できない状況)につながる可能性があります。 さらに、準安定状態が次のクロック信号の到着まで続いた場合、チェーン内の次のトリガーを同様に準安定状態にすることができます。 これの確率は高くありません、なぜなら トリガーが準安定状態に陥る入力電圧の範囲は非常に狭いです。 ただし、このような状況が高周波数で定期的に発生するという事実を考えると(最新の回路は最大1 GHz以上の周波数で動作できます)、このイベントは非常に現実的です。 繰り返しますが、このようなイベントの可能性は、デバイスのパラメーター、クロック周波数、データ変更の頻度を考慮して推定できます。 障害間の時間を推定する一般的な式は次のとおりです。

どこで

どこで

t_R-準安定からの「保護」の時間間隔。 概算では、1つのトリガー、クロック信号の周期から2番目のトリガーのプリセットと伝播の遅延を引いたもの、および後続のトリガーごとの周期に0が等しいと仮定できます。

\ tau-技術依存のパラメーター、最新のデバイス、単位/数十ピコ秒。

T_0-準安定状態に入るための時間枠。 数十/数百ピコ秒。

f_cはクロック周波数です。 数百メガヘルツ。

f_Dは、データ変更の頻度です。 0からf_cの範囲。

最新の機器では、チェーンの最初のトリガーが準安定状態に入る期間はマイクロ/ミリ秒単位で、2番目は時間単位で、3番目は数十億兆年単位で測定されます。

準安定性の影響は、いくつかの古典的な状況で発生する可能性があります。

- トリガーのパラメーターTsおよびThの明示的な違反。 通常、デバイスは、信号伝搬パスが長すぎるために物理的に動作できない周波数で動作させようとしたときに発生します。 この状況は一時的なアナライザーによって制御され、通常の操作中(一時的な要件を満たす場合)には発生しません。

- 非同期リセット入力の時間パラメーターの違反。 驚くべきことに、リセットは非同期であるにもかかわらず、リセットするトリガーのクロック信号と同期する必要があります。 その時間パラメータは、クロックパルスの先頭に対して相対的に宣言されます。 これはしばしば忘れられ、どこからでもダンプを提供します。 繰り返しますが、リセットトリガーのクロック信号と同じクロック信号を使用してリセット信号が生成された場合、タイムアナライザーはそれを自動的に判断します。

- 他のデバイスから同期的に(既知の遅延と同じ周波数で)供給される信号-ここでは、最も単純な時間分析(つまり、クロック周波数のみを宣言する)は機能せず、入力/出力信号の時間特性を明示的に設定する必要があります。 これは、一時的な分析という別の難しい(しかし完全に解決可能な)タスクです。

- そして最後に、最も難しいケース-信号は非同期に送信され、受信トリガーとは完全に異なるクロック周波数で(そして未知の位相シフトで)送信されます。 それらのソースは、外部機器(少なくともボード上のボタンまたはシリアルポート)または異なるクロック周波数で動作する同じマイクロ回路のブロックのいずれかです。 この状況について、さらなる議論が行われます。

しかし、最初に、多くのクロック信号がどこから来るかについてのいくつかの言葉。 もちろん、最も簡単で楽しいオプションは、クロック信号が1つしかない場合です。 その後、プロジェクトでの作業は簡単で便利です。 残念ながら、これは非常にシンプルなデバイスでのみ可能です。 多かれ少なかれ複雑なデバイスは通常、それぞれが独自のクロック信号を持つことができる複数の外部デバイス/インターフェースと通信します。 たとえば、ADCからデータを受信し、外部のダイナミックメモリにバッファリングしてから、イーサネット経由で転送する必要があります。 この場合、相互に接続されていない少なくとも3つのクロックドメイン(ADCインターフェイス、システムバス、DDRメモリ、およびイーサネットインターフェイスの塊)があります。 そのため、これらのクロックドメイン間でデータ(パラメータ、制御信号、ステータスフラグなど)を正しく転送するタスクに直面しています。

戦う方法

まず悪いニュースです。準安定の影響を完全に克服することは不可能です。そのため、最も近い原子力発電所が突然爆発したり、飛行機が突然sudden落したりする可能性が常にあります。 ただし、多くの単純なアクションによってこの確率が大幅に低下する可能性があります。これは明日、大天使ラファエルが音を鳴らして審判の日を発表する確率とほぼ同じです。 一般的な戦術は理解できます。データを使用できるように、いくつかのトリガーを連続して配置します(上記の式が示すように、2つの同期トリガーは現実主義者にとっては十分です)。 ただし、送信されるデータのタイプに依存する多くの技術的なニュアンスがあります。

最も単純なケースは、 疑似静的スカラー(単一ビット)信号が送信されることです。 たとえば、モード選択信号など。 -非常にまれに切り替えます。 この場合、私たちの唯一の関心事は、準安定性に対する保護です。受信周波数の2つのトリガーを配置し、問題が発生します。 1クロックの不確実性(気にしません)で、ソースからレシーバーに送信されます。

1ステップイネーブル信号 困難なのは、周波数が一致しない場合、信号を完全に失う可能性が高い(受信周波数が元の周波数より低い場合)か、数クロックサイクルにわたって信号を引き伸ばす可能性が高いという事実です。

この場合に使用される一般的なアプローチは、信号を数クロックサイクル「延長」し、既知の方法で新しいクロックドメインに転送し、そこでフロントイベントを選択し、1クロックサイクルの期間で信号を再生成します。

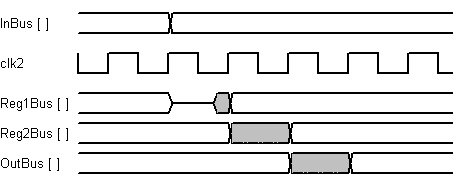

単一の疑似静的値 (たとえば、構成パラメーター)を送信するマルチビットバス 。 すべてがシンプルなように思えます-バスの各ビットにトリガーのペアを置きます-他に何が必要ですか? ただし、メタステーブル状態を終了した後、トリガーは古い値と新しい値の両方を取得できることを知っています。 さらに、パラメータがわずかに異なるために準安定状態に入らなくても、放電の1つのトリガーは新しい値をキャッチし、もう1つのトリガーは古い値をキャッチします。

この場合、少なくとも1クロックサイクルの間、バスの出力に誤った値が存在します。 入り口に提出された古いものと新しいもののどちらにも等しくなりません。 一部のスキームではこれは重要ではありませんが、一部のスキームでは重要な場合があります。 そのため、入力データをクリックして出力するのが安全なポイントを示す確認信号を使用して、より信頼性の高い回路を作成しようとします。

そして最後に、最も難しいケースは、 あるクロックドメインから別のクロックドメインに送信されるデータの流れです 。 データが比較的少ない場合(10クロックサイクル以上で1データワード)、前の段落と同様のハンドシェイクスキームを実装できます。 しかし、データが各ビート(またはそれに近い)に進むとどうなりますか? ここでは、特別なハードウェアユニット、つまり独立したクロック信号を備えたデュアルポートメモリが役立ちます。 このようなメモリは、最新のFPGAとカスタムマイクロサーキット用の技術ライブラリの両方で利用できます。 2つの別個のポートを介して完全に独立して書き込みおよび読み取りができます。 唯一の制限は、同じメモリアドレスでの書き込みと読み取りへの同時アクセスです-未定義の結果につながる可能性があります。 このようなメモリブロックに基づいて、FIFOモジュールが作成されることがよくあります。これにより、一方のクロックドメインからデータを書き込み、他方のクロックドメインにデータを取り込むことができます。 同時に、FIFOロジックにより、同じメモリセルへのアクセスが発生しないことが保証されます。

おわりに

最後に、いくつかの便利なヒントをまとめて説明します。

- クロック信号が少ないほど、プロジェクトでの作業が簡単になります

- ベースシンクロナイザーは、お互いの後ろに立つ2つ(またはそれ以上)のトリガーです。

- すべての非同期クロックドメイン間で、データ転送メカニズムを検討する必要があります。 システム設計の段階でプロジェクトのクロック構造を描くのが最善です

- 非同期リセット信号を含む、デバイスに対して非同期のすべての外部信号は同期する必要があります

- 1つのモジュール内では、1つのロックのみを使用することをお勧めします

- モジュール内に複数のシュレッドがある場合、各内部信号について、それが形成するシュレッドとその使用方法を明確に理解する必要があります。 信号名に直接コーディングする方が安全です

- プロジェクトの最上位レベルでは特に注意してください。ここでは、1つのクロックドメインから別のクロックドメインへの信号の誤った接続が再同期なしで発生することが非常に多くあります。

- 内部周波数逓倍モジュール(PLL / DCM / MMCMなど)によって生成されるクロック信号は通常同期的であり、一時的なアナライザーによって検査され、データ再同期はほとんどの場合必要ありません。 けがはしませんが。

- 最新の設計ツールは、クロックドメイン間のデータ転送の状況を独立して検出しようとします。 たとえば、アルテラのデザインアシスタント(Quartusに組み込まれています)、アルデックのALINTです。 警告やヒントを聞く価値があります。

そして最後に、起こりうる技術的な問題に関するいくつかのコメント。

タイミング図は、簡単な無料プログラムTimingEditorを使用して作成されました 。 一部のプロジェクトはQuartusで構築されました-回路エディターの利便性だけのためです。 純粋なHDL(VHDL / Verilog)にすべて同じものを実装できます(そうすべきです!)。 準安定性の物理学をより深く理解する必要がある場合は、キーワード「準安定性」と「クロックドメインの交差」を使用して、このトピックをさらに詳しく調べることができます。 たとえば、スティーブゴルソンのかなり詳細な研究「同期とメタスタビリティ」、およびランギノサールの短い文書「メタスタビリティとシンクロナイザー」などは、オンラインで入手できます。