会社の経験と他の作品での私自身の経験に基づいて、PCB生産がどのように設定されるかに関する記事を提示したいと思います。 私の仕事は、既存の取締役会を近代化して、既存の品質を改善し、おそらく、これまで見たことのない新しい地平を開くことです。

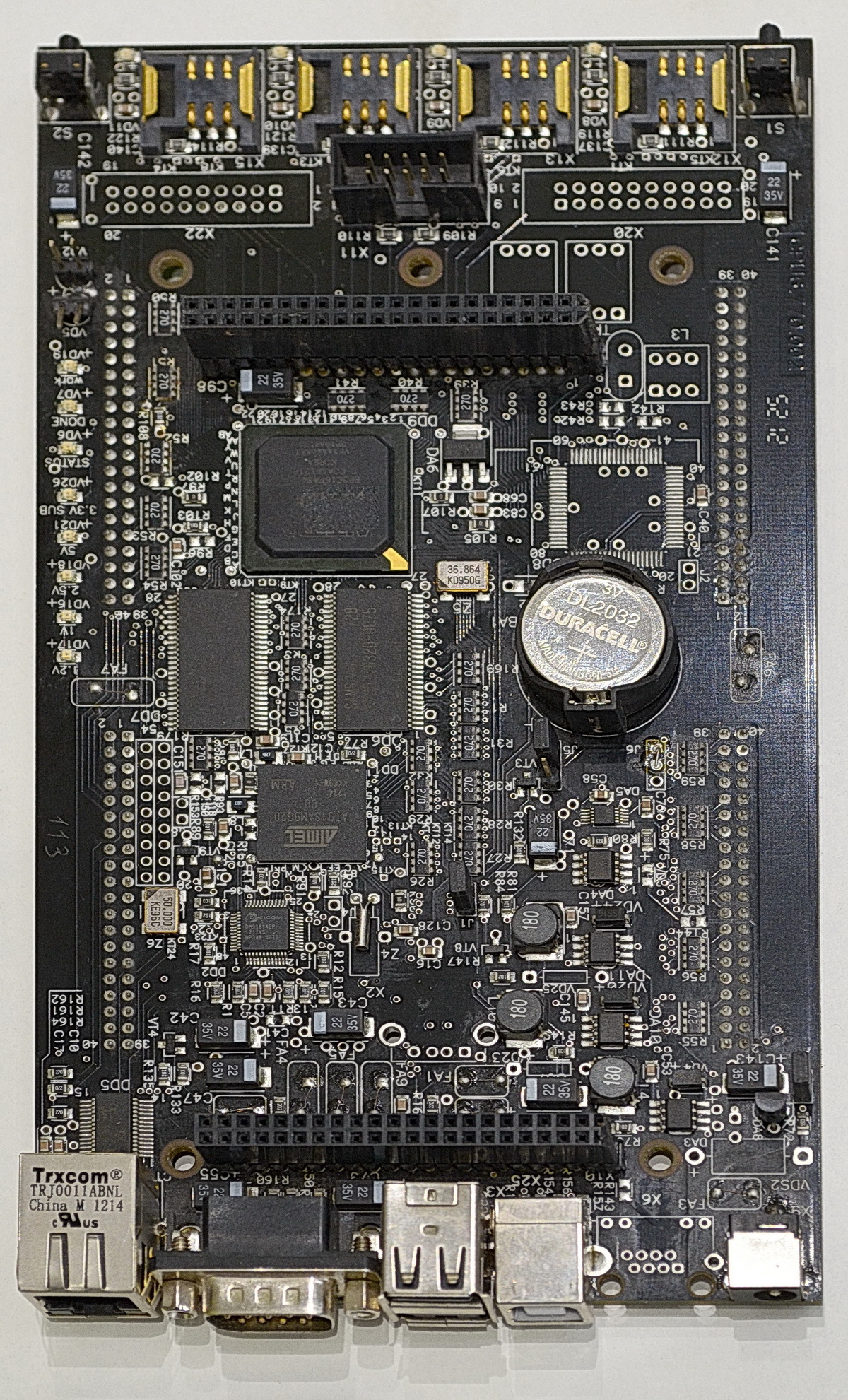

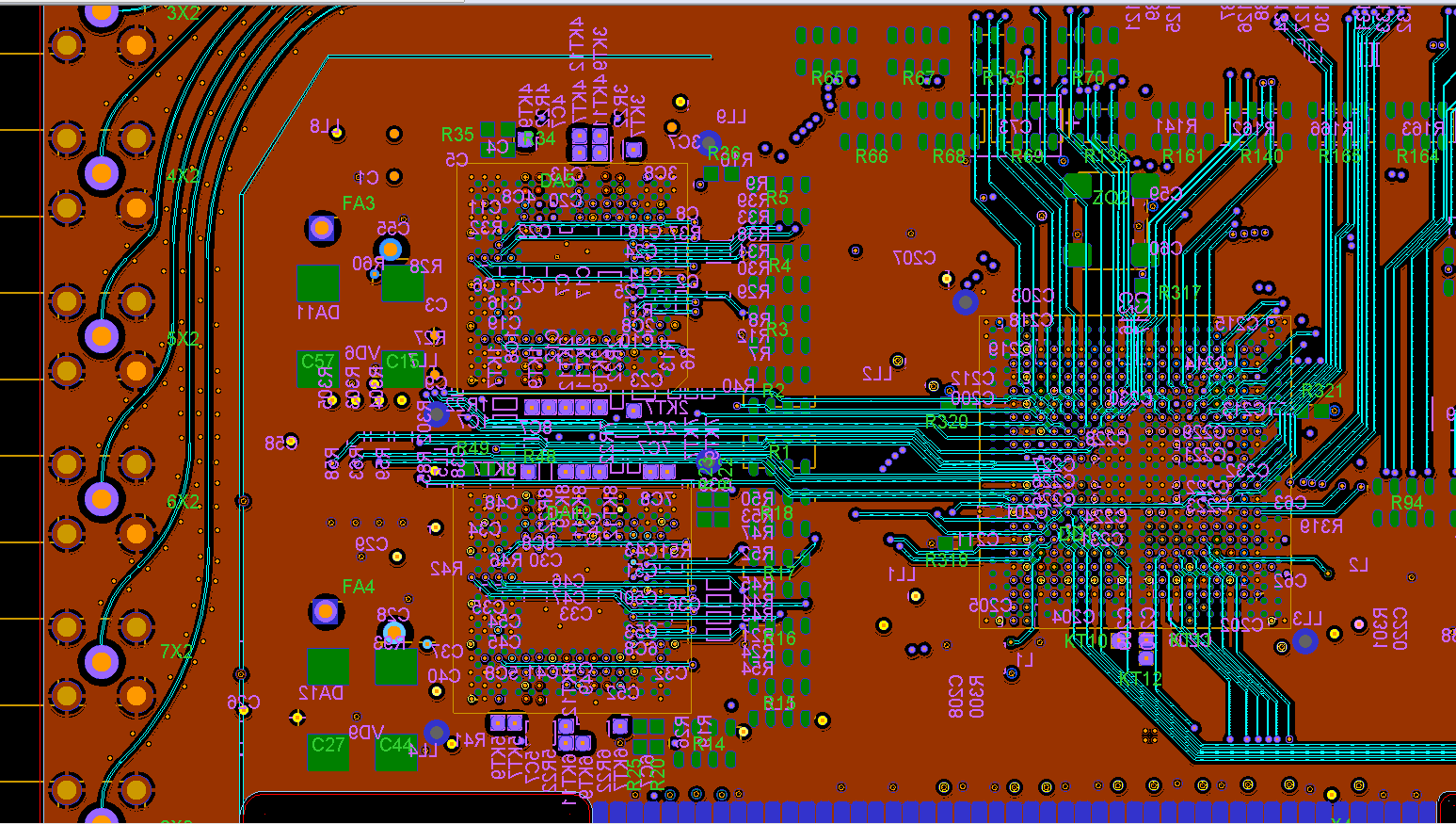

基礎は、コード名「G20」のCPUボードによって採用されました。

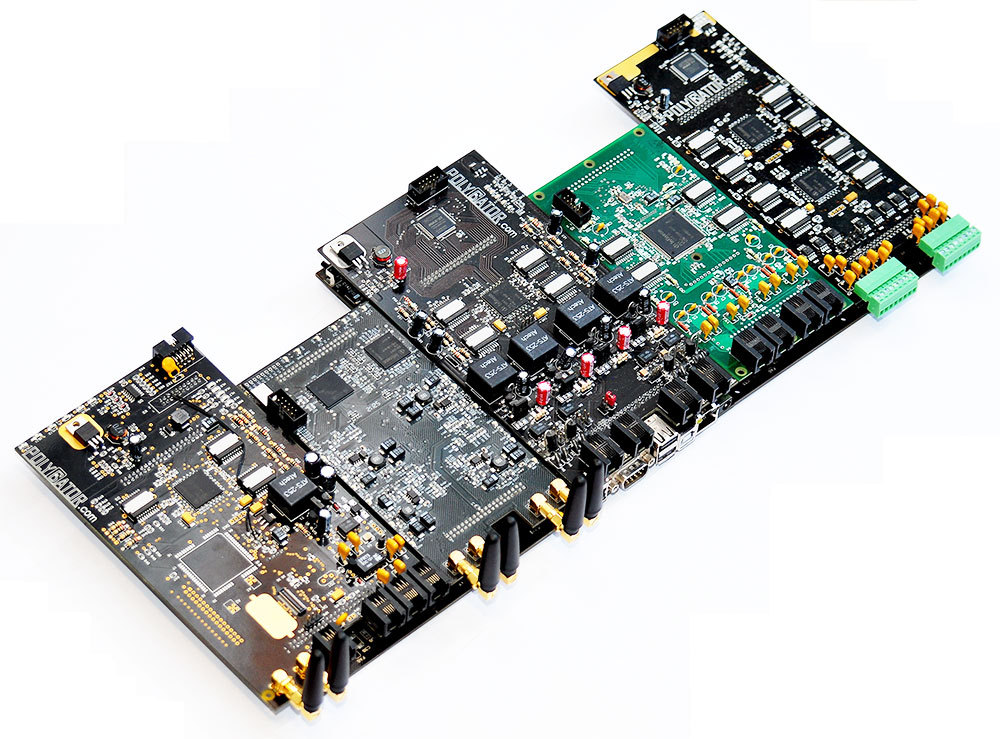

このボードは後に会社の開発の多くの主要なボードになりました。 さまざまな構成の固定ボードで使用されます。 複数の開発者がこれらのボードのプロジェクトに取り組んでおり、それぞれが独自のアドインとコアボードを持っています。

むかしむかし、私の前でさえ、よく考え抜かれた設計のおかげで、私の会社は素晴らしいボードを開発しました。それは会社の多くのデバイスのクラストとして機能しました。 アルテラは、Atmel ARM9 G20プロセッサでFPGA(プログラマブルロジック集積回路、英語の文献ではFPGA)として選択され、アルテラはCyclone IIIを使用して他のボードと通信します。 FPGAとCPU間の接続は、プロセッサメモリバスと互換性のあるパラレルバスを介して行われます。

プロセッサは400 MHzの周波数で動作し、メモリボードには32ビットバスを介して2つの512MビットSRAMチップが搭載されています。 ボードには高速イーサネット10/100および2ホストUSBもあり、プログラムのダウンロードとWi-Fi、ネットワークアダプター、その他のデバイスへの接続の両方に使用できます。 また、回路にはPRIチップがあり、電話ネットワークに接続する場合にE1 / T1ストリームを提供します。

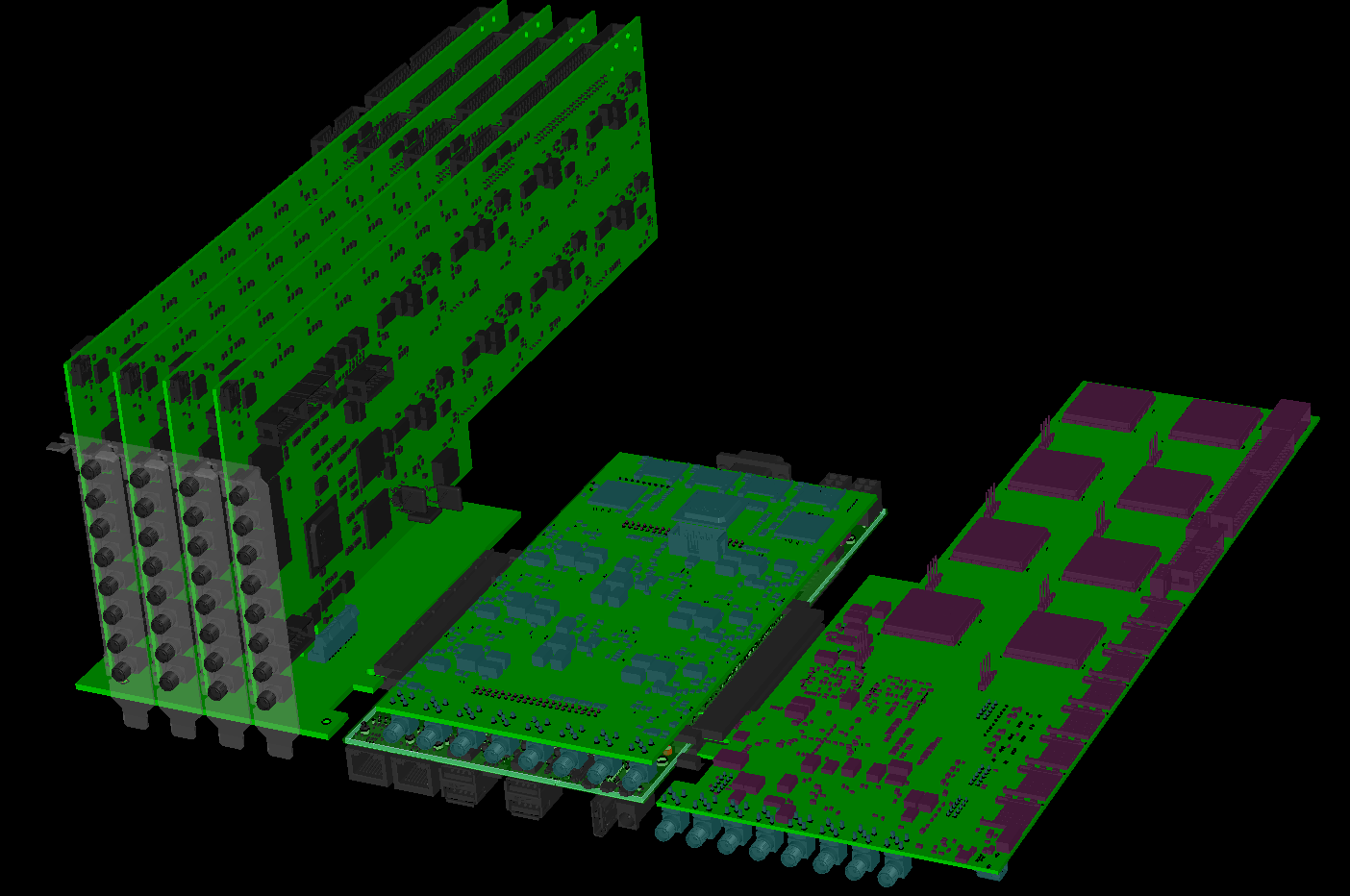

ボードには、補助カードを接続するためのコネクタがあります。 1つのボードを上部(メザニンの形)に接続し、2つのボードを側面に接続できます。 ピッチが2.54 mmの2列コネクタ、穴にはんだ付け。 それらの利点は、価格と店舗の両方、バザールとビンの両方でのアクセシビリティです。 同じことが合致にも当てはまります。 マイナス-接続線の数が少ない接点間の大きな段差のため、それらは大きく、穴に取り付けられたコンポーネントはボードのすべての層でトレースするためのスペースを占有し、上部ボードのコネクタはボードを3つの部分に区切っています。 穴に取り付けると、コネクタを上下に置くことができます。 実際には、すべてのボードはメインボードの上に配置されます。

このボードでは、いくつかのタイプのサブモジュールボードが開発されており、これらは構造的にメザニンと呼ばれます。 また、ボードは、ボードの側面にあるアダプターを介して接続できます。

これらのモジュールの1つは、4または8チャネル用のGSMボードです。 取り外し可能なメザニンにより、さまざまな企業のさまざまなGSMモジュールでボードを開発し、いくつかの範囲(GSM、UMTS、WCDMA)でボードをリリースできました。 また、従来の電話や高度な機能を備えたPBXの作成用のボードもインストールします。 100 SIMカード用のSIMバンクを備えたバージョンがあります。

機能を複数のボードに分割することにより、ボードを互いに個別にデバッグし、その後メザニンの改良モデルをリリースすることが可能になりました。

このボードは、将来のシステム用に個々のソフトウェアモジュールをデバッグおよびテストするのにも役立ちます。 EvBoardをその連絡先に接続し、独自のボードを作成する前にデバッグを開始できます。

時間が経つにつれて、メインボードの機能は十分ではなくなり、既存のボードを置き換える新しいボードを開発することが決定されました。 パラレルバスを使用すると、交換レートと同時にロードされるボードの数に制限が課されました。 これにより、新しいボードの要件を作成できました。

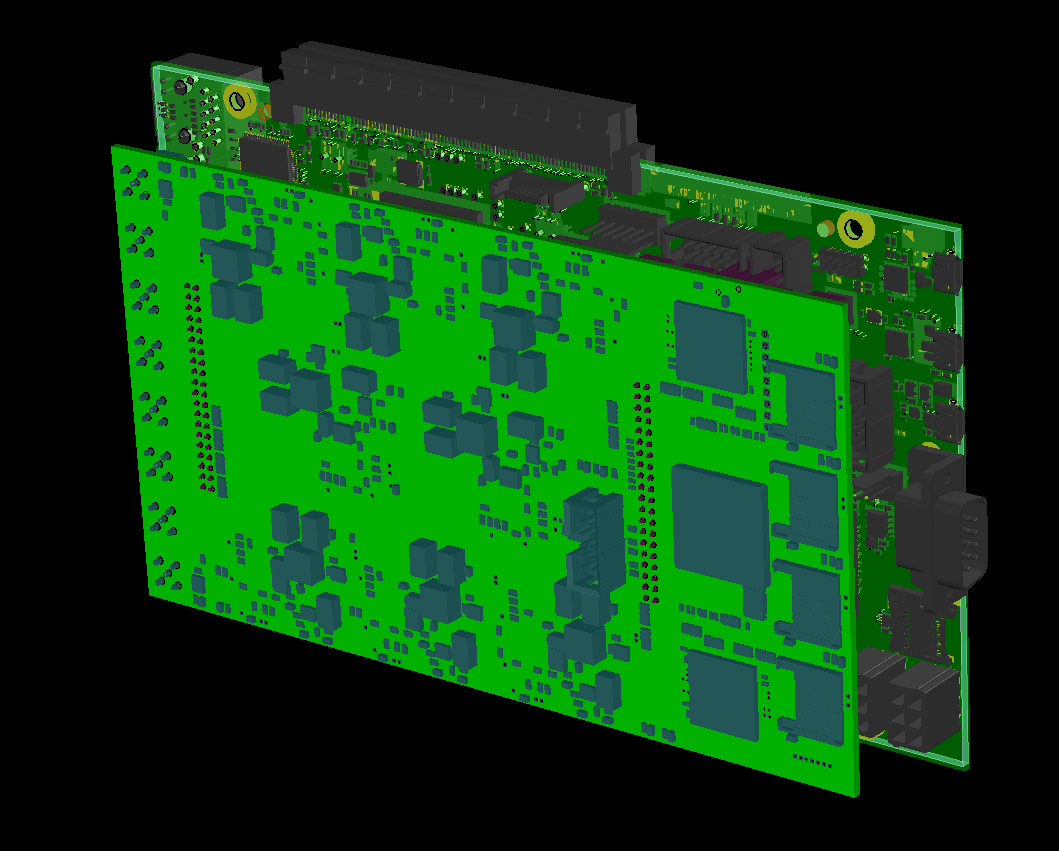

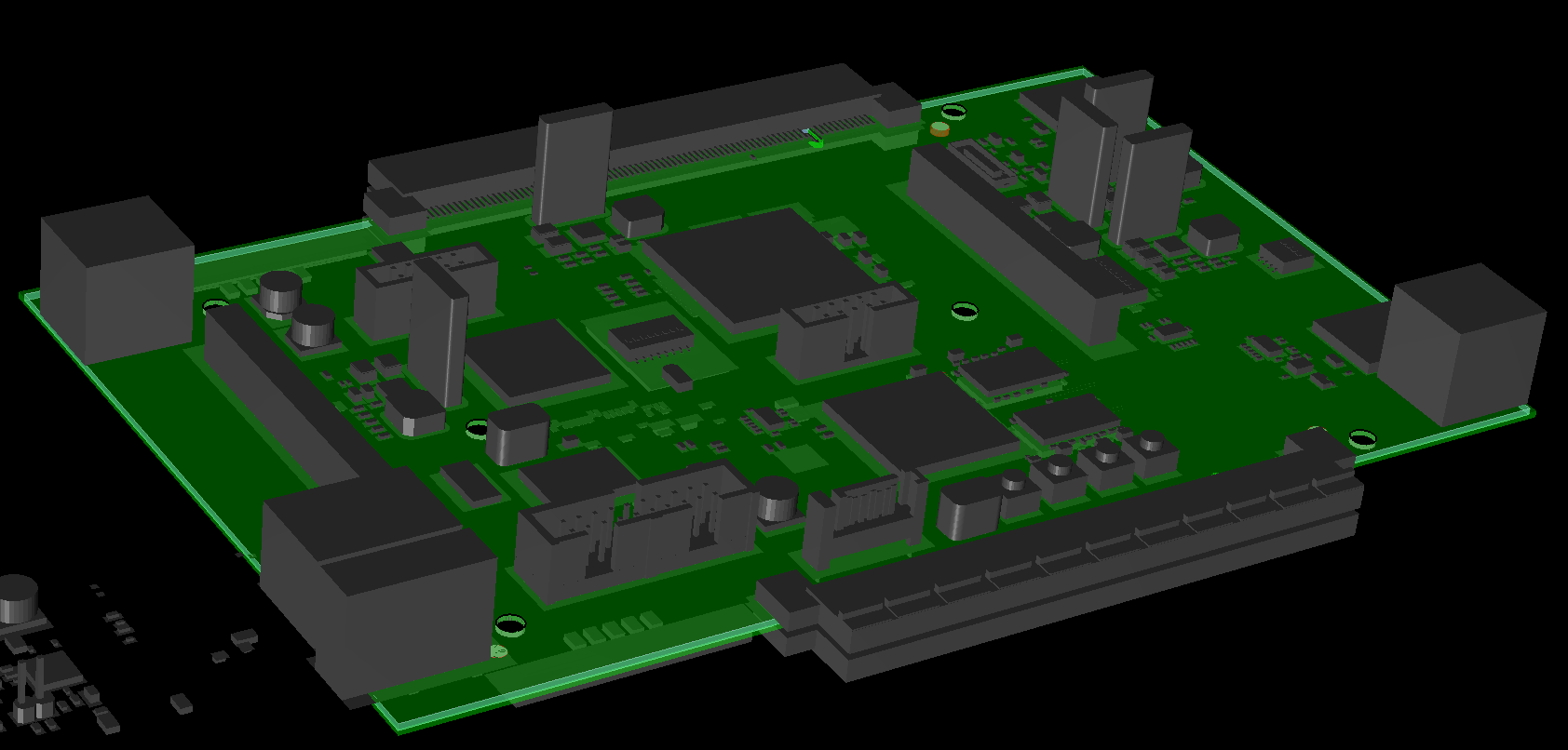

ボードには、より多くのRAM、メモリとFPGA間の独立したバス、高速シリアルチャネルを使用してボードと通信する機能、およびPCIeが必要です。 コンポーネントの選択段階で、FPGA用の組み込みプログラマ、2つのイーサネットコネクタ、USBハブ、HDMI、古いボードとの互換性などの追加要件が追加されました。 インターフェイスの一部は、ループを使用してデバイスを接続するための個別のコネクタとして作成されました。

利用可能なプロセッサを分析した後、選択はフリースケールのiMX6で決まりました。 競合他社と比較して、すべてのドキュメントは彼のために開かれていました。彼は、NDA、「単純な」はんだ付けBGAに適したハウジング、「通常の」メモリバス、浮動小数点サポート、および他の多くの利点なしで利用できる健全なドキュメントと推奨事項がありました。 ARM Cortex-A9コア、浮動小数点サポート、およびその他のバンには投票しませんでした。 そのため、最新のモバイル技術と生産能力の妥協点を見つけました。

スキームはデバッグキットの1つから取得され、ニーズに合わせて処理されました。

サイドボード用のコネクタの選択は、多くのパラレルおよびシリアル信号を取得したいという要望とコネクタの価格との間の妥協点でもあります。 いくつかの価格は60 cuを超えることができます PCIeコネクターの最後で停止することが決定されました。 将来的には、これにより、1組のボードの1つのコネクタを節約できます。 同時に、コネクタは、Cyclone GXに存在する最大3.125 GHzの高速信号の両方の送信を満たします。

E-Inkディスプレイを使用する必要がないため、パラレルプロセッサバスにFPGAをインストールし、PCIeプロセッサバスとギガビットFPGAバスを高速キーでさらに接続しました。 これで、プロセッサはPCIeまたはサイドコネクタのいずれかにPCIeを送信できます。 PCIe x1に加えて、両側の4ギガビットチャネルがプロセッサからコネクタに送信されます。 将来的には、「クイック」接続に使用する予定です。

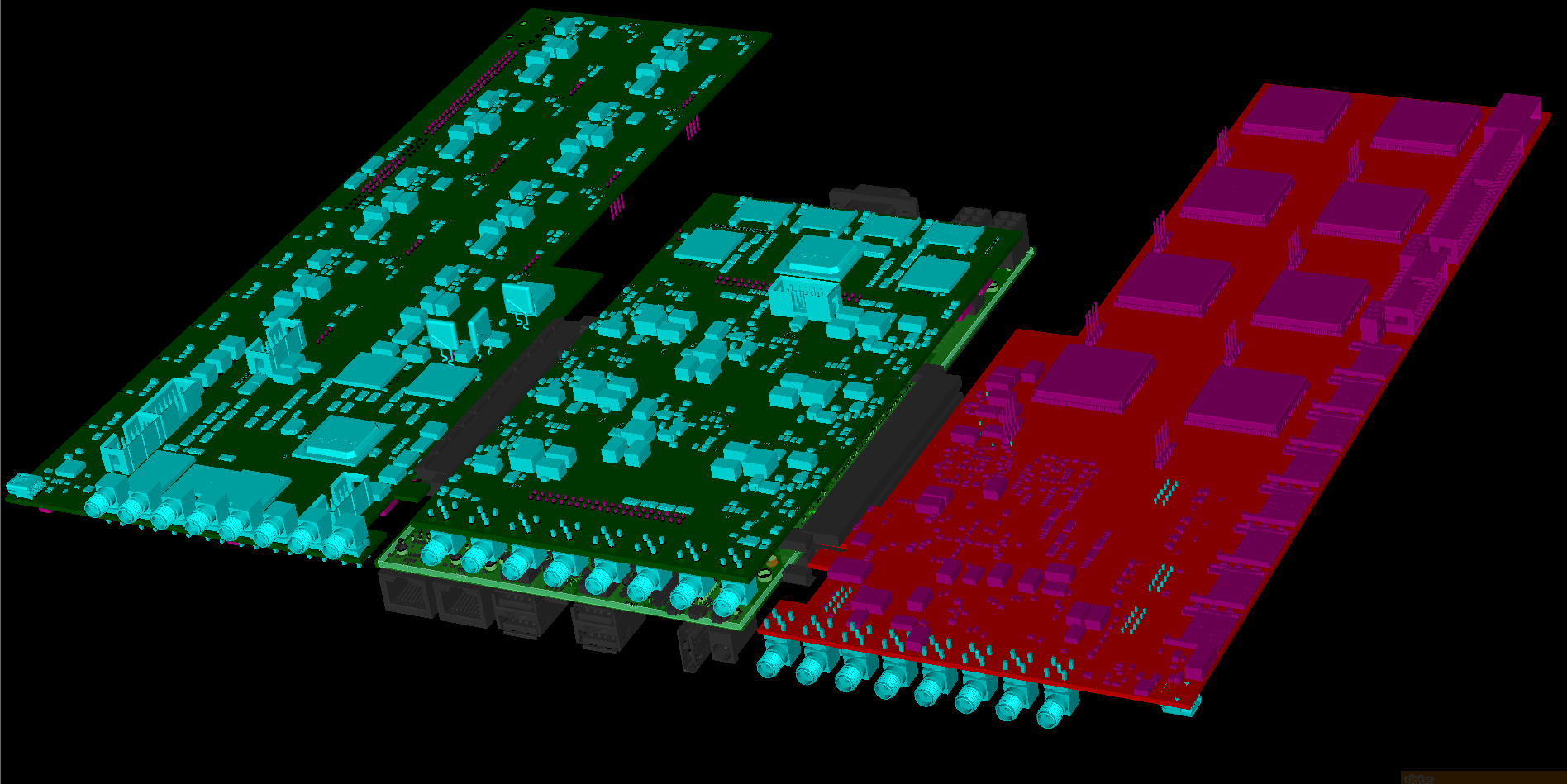

設計パッケージ内の3Dモデリングにより、重要なコネクタを他のボードと「閉じない」ことができます。

次に、必要な基板サイズにすべてを合わせる必要がありましたが、同時に「これをはんだ付けしますが、これをはんだ付けしません」という場合に備えて、基板を仕上げる可能性を残します。 このアプローチにより、契約メーカーから複雑な料金を支払うことができ、自宅の顧客にインターフェースをはんだ付けすることができます。 その結果、顧客は自分が使用したものに対して支払いをしません。 これらの制限により、すべてを0201の量でミニチュアにし、できるだけ近くに配置することはできません。 また、ジャンパーをはんだ付けできるように、外部に信号を出力する必要がある場合があります。 これは汎用性のための料金です。

占有面積を最小化する他の方法を探す必要があります。

そのため、たとえば、同じ定格と電圧のコンデンサは、高さまたは面積でより多くのスペースを占有する可能性があります。 多くの超小型回路はさまざまなタイプのケースで利用でき、同じ機能でスペースを大幅に節約できます。

SOICとQFNのDC-DCコンバーターの場合の違いを理解できます。 それらと比較して、DDPAKおよびTO220ケースは単に巨大です。

Texas Instrumentsには、さまざまなタイプの降圧DC-DCがあります。 しかし、最新のコンバータはより高い周波数で動作することができ、より低いインダクタンス値を必要とします。 電流の大きさが1〜2 Aの場合、許容サイズの場合、インダクタンスと12〜18μHを見つけることができます。 また、5 A以上の電流を供給する必要がある場合、インダクタンスの寸法が大きくなりすぎます。 別のコンバータを選択すると、インダクタンス1〜2μHになり、全体の性能に適合することができます。 また、面積と高さだけでなく、コンポーネントの重量も重要です。

プリント回路基板を設計するときは、コンポーネント同士の影響を考慮し、ノイズに敏感な回路を干渉源から分離する必要があります。 ところで、これはパルスDC-DCコンバーターです。 したがって、シールドされたインダクタンスの使用、補償スキーム、および敏感な回路から二次電源を遠ざけることは、将来の神経の束を節約することができます。 ボード上の要素をレイアウトすることが不可能な場合、ボード内の信号の影響を制限することにより、さまざまな方法でだまさなければなりません。

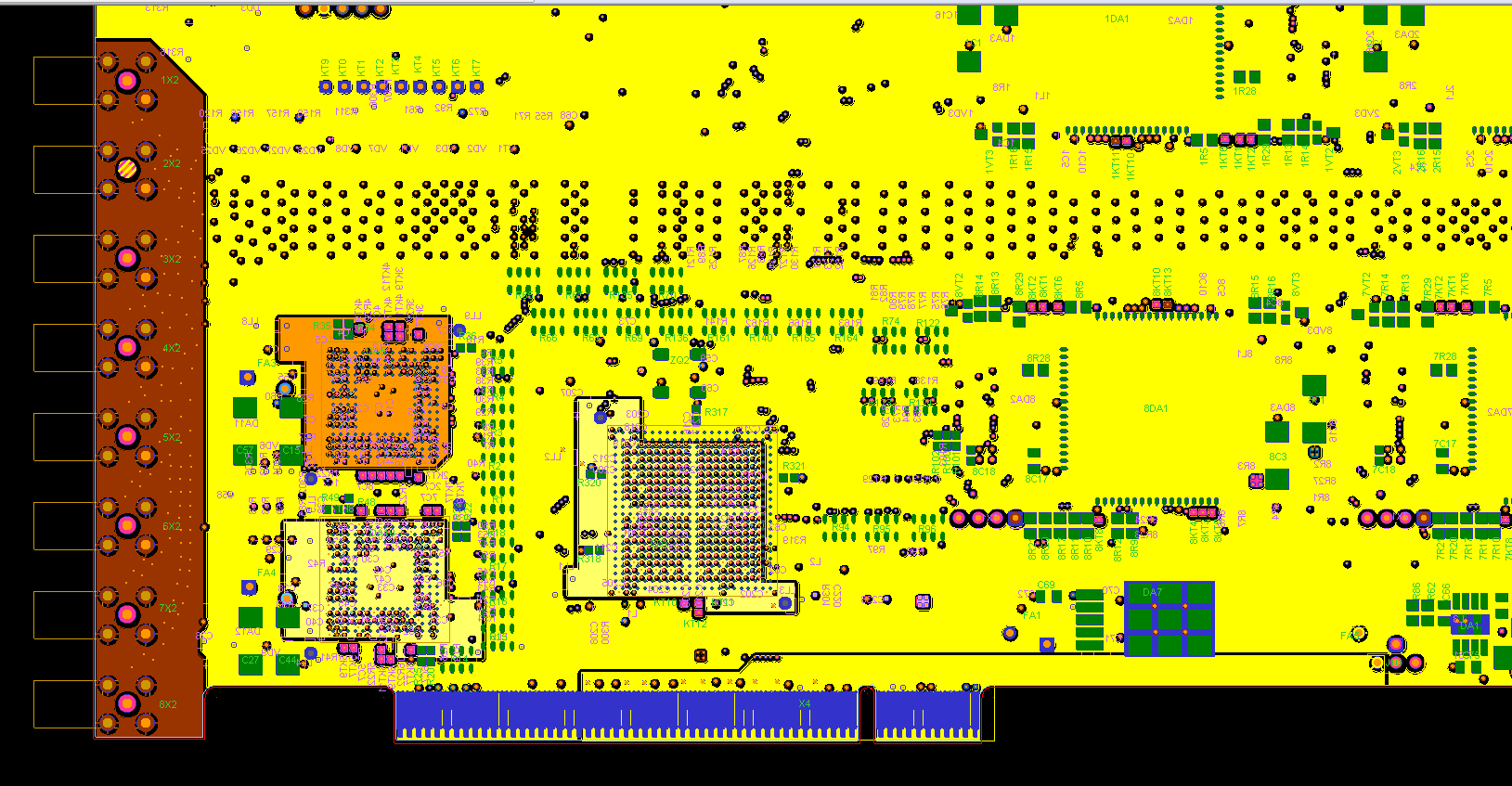

これは、PCIゲートウェイPCIカードの電源層内のRFコネクタ近くのグランド層の領域を示しています。

GSMゲートウェイのPCIカードに対するデジタルノイズとHFノイズの相互影響を低減するために、地球の内側の層に切り抜きを入れます。

LUT生産用と工場での生産用のプリント回路基板のトレースが異なることは注目に値します。

また、コンポーネントのインストール要件にも違いがあります。

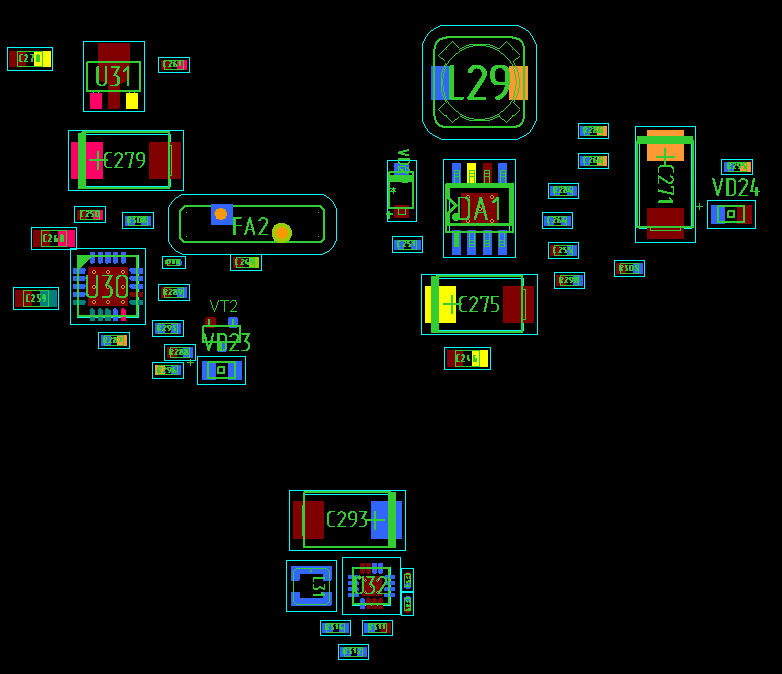

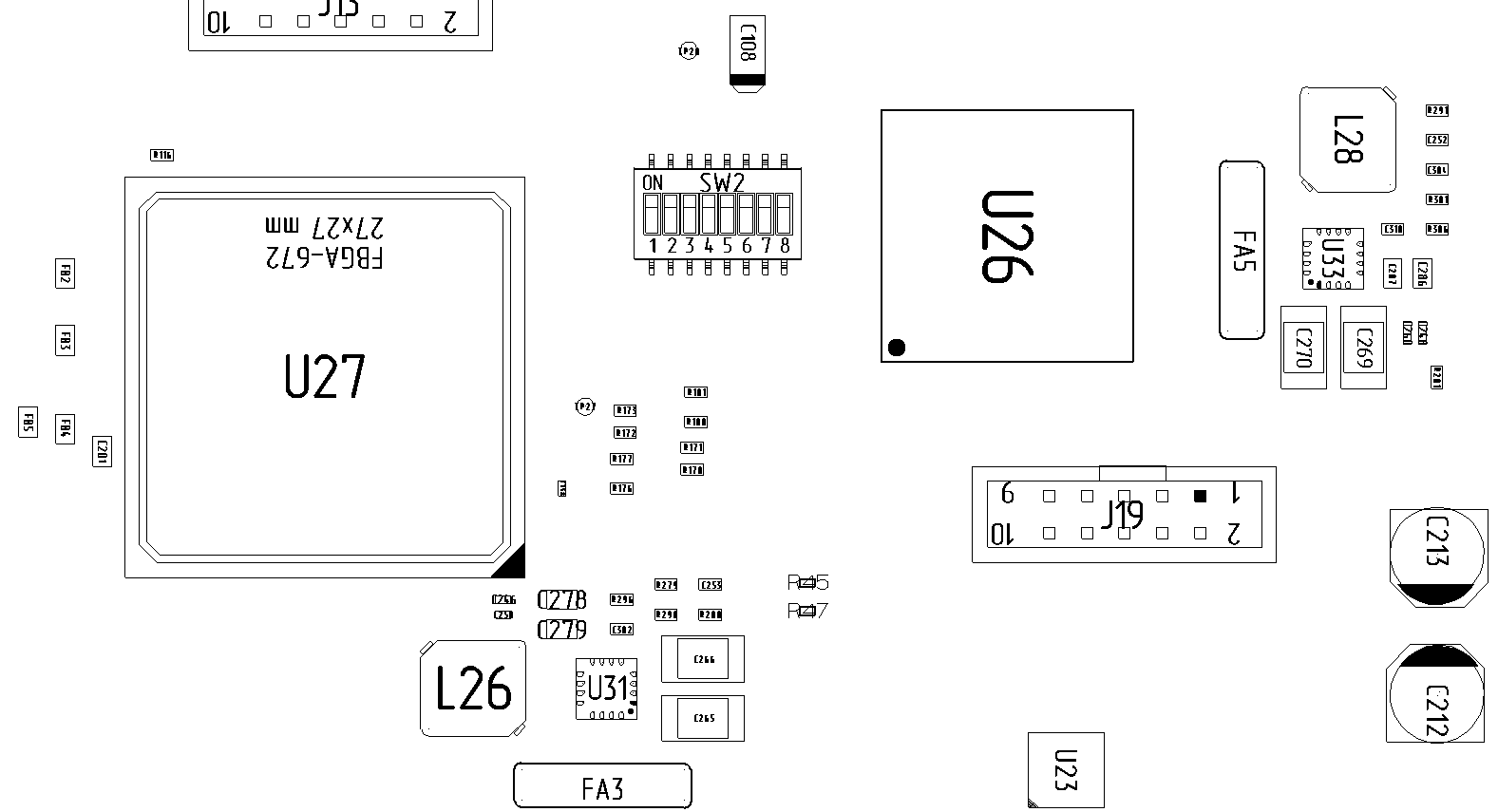

小規模バッチまたは単一のプロトタイプ生産では、インストーラーの要件は次のようになります。「ボードとコンポーネントが必要です。SMDコンポーネントを取り付けるためのステンシルがある場合は、それをやりましょう。」 多くの場合、コンポーネントマウントカードで十分です。このコンポーネントでは、インストールするコンポーネントを異なる色で表示したり、参照符号を単に表示したりすることがあります。 正確な座標を指定しません。 以下は、このようなアセンブリ図面の一部です。

複雑なボードまたは単純なボードを大量に作成する場合、真剣な契約ビルダーに注意を払う価値があります。 彼らは、組み立てられた回路基板のインストールとテストの両方のための機器を持っています。 より多くの要件があります。 プリント基板、ステンシル、コンポーネント、さらにはトレースの品質。

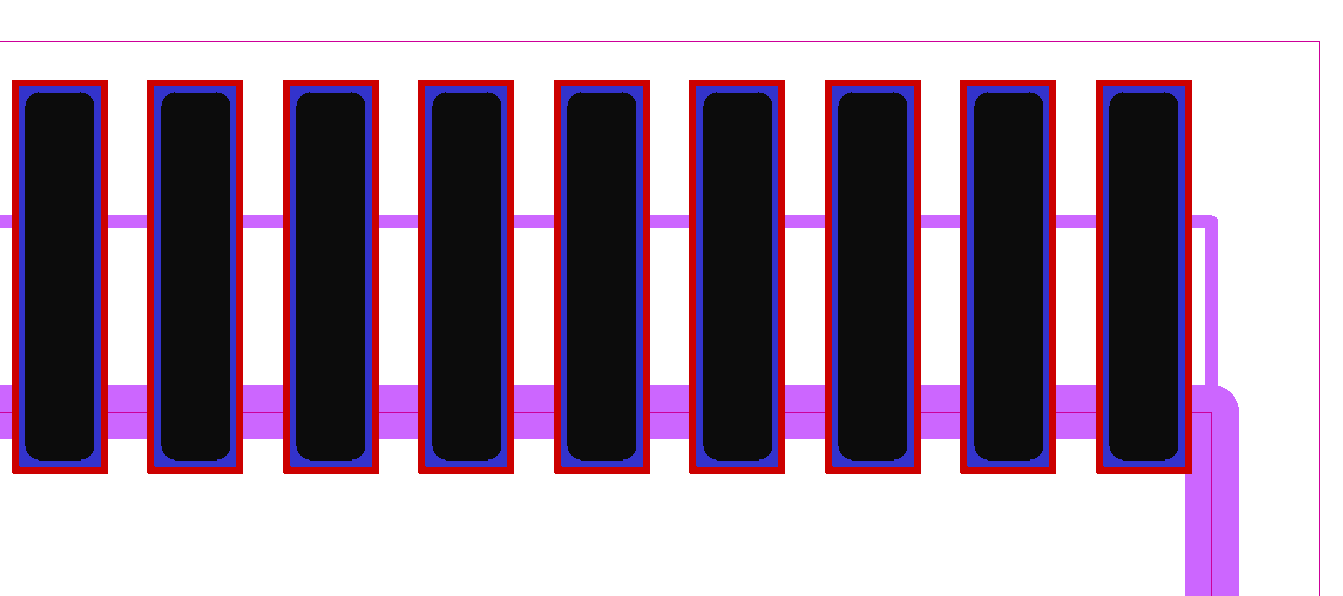

プリント回路基板では、基板がコンベアに沿って移動するために、端に技術的領域が必要になる場合があります。 サイズはメーカーによって異なり、3〜5 mmで十分です。 コンポーネントがボードの端に取り付けられていない場合、技術ゾーンは省略できます。 ボードはコンベアに沿って移動し、その端に寄りかかります。 ボードの輪郭が不均一な場合、コンベアに沿った通常の動きのために、技術ゾーンを使用して輪郭を揃える必要があります。

はんだペーストを塗布するための追加の機器も必要になる場合があります。 表面実装要素を使用するプロジェクトの場合、これは通常ステンシルです。 ボードの大規模なバッチを作成する予定がある場合、またはボードが単一ではない場合は、ライブラリコンポーネントをすぐに「生産用」に変更することをお勧めします。

「生産用」という用語は、アセンブリ生産とボード自体の生産の両方を意味します。

インストーラーの場合、すべてのコンポーネントのフットプリントが正しいことが重要です。

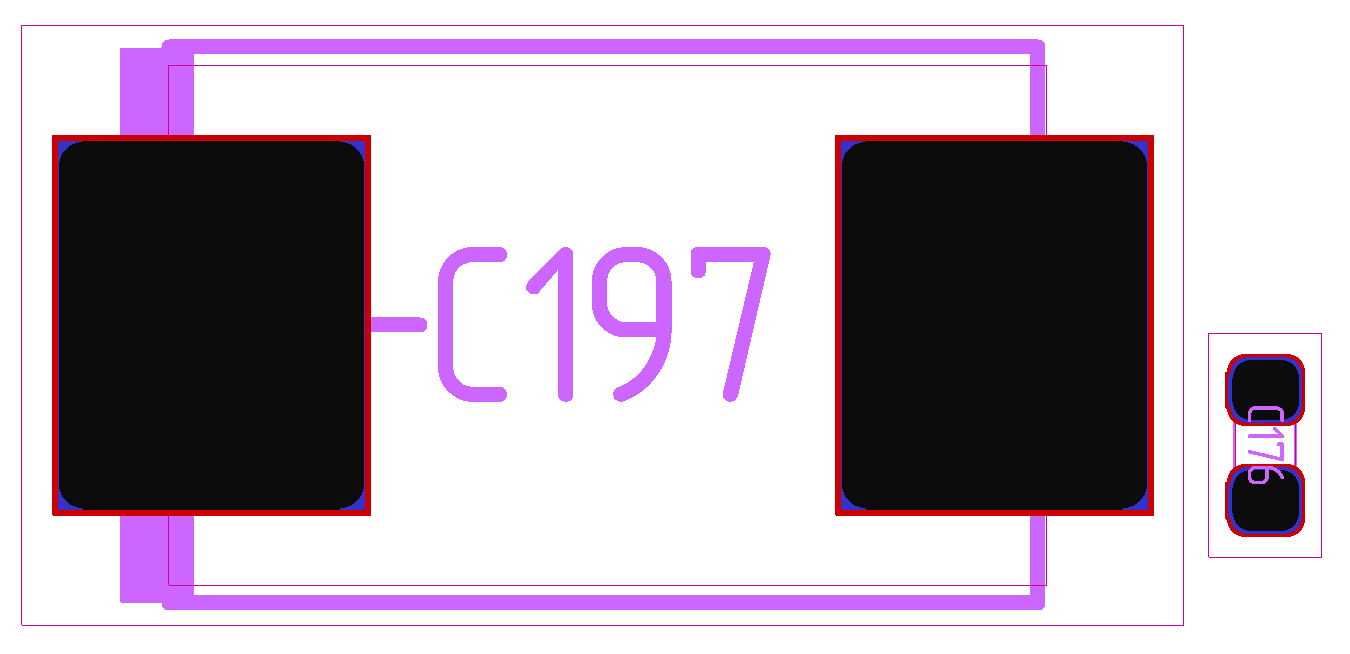

コンポーネントのシートは、通常、はんだ付けされた要素よりもわずかに大きいため、位置決めが不正確な場合にギャップが生じます。 しかし、彼らはあまり大きくする価値はありません。 大規模なサイトでは、小さなコンポーネントが離れてしまい、インストールに問題が生じます。 さらに、広い面積にはんだペーストが多すぎる可能性があり、溶融すると、沸騰フラックスがコンポーネントを横方向に持ち上げます。 接触面積が大きく、ステンシルの開口部が小さくなると、はんだがその領域に広がり、コンポーネントの脚に届きません。

リード間のピッチが0.5 mm未満のコンポーネントの場合、はんだペーストが取り付けられたコンポーネントによって押し出されず、リフロー中に短絡やジャンパーが形成されないように、はんだペーストを接触面積よりも小さいステンシルで開くことをお勧めします。

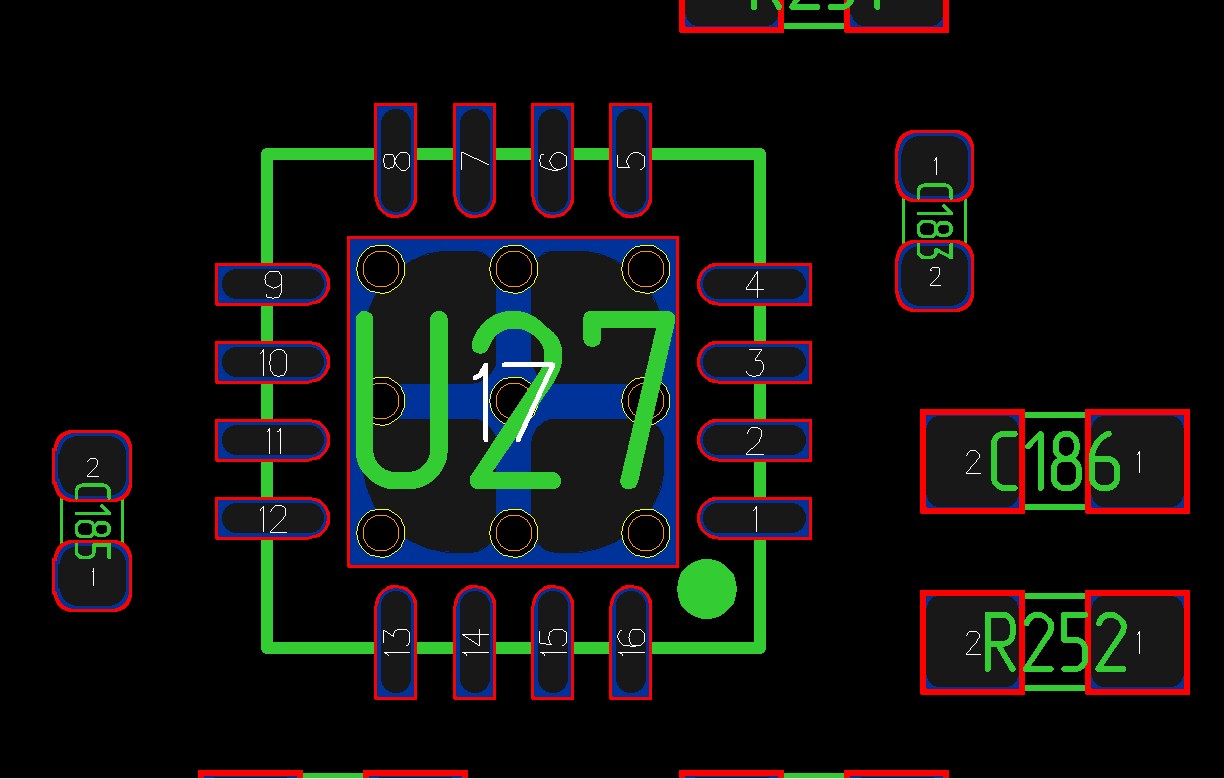

図は、はんだマスクの開口部の境界を赤、紫-接触領域、黒-はんだペーストの下のステンシルの開口部で示しています。

現在、多くのコンポーネントがますます小さなケースで利用可能になり、効率が向上しているにもかかわらず、開発者はチップから熱を除去するタスクに直面しています。 したがって、ケースの寸法が小さい場合、必要な熱量は蓋から放散できず、「馬に乗る」ことになります-チップの底部をボードにはんだ付けすると、ボードはすでに銅の層を通して熱を除去します。

実際には、腹部がはんだ付けされていないマイクロ回路で過熱に対する熱保護がオンになっており、はんだ付け後にマイクロ回路の温度が低下し、基板が上昇し、熱がグランド層に放出されてコネクタが温まり始めたときに、このような冷却方法の有効性を検証する機会がありましたコネクタハウジングのはんだ付け先。

そのため、一部の「腹部」を除いて地面との接触がないため、このような超小型回路の座席の設計に関する推奨事項を注意深く読む必要があります。 そして、コンタクトの下にはんだペーストを置かないと、マイクロ回路はグランドに接続されません。 脚の数が少ない超小型回路では、ケースの下の熱降下は小さく、大型の超小型回路では注意が必要です。 製造業者は、推奨事項で、はんだペースト用のステンシルのどの接触パッドと穴を作成するかを示しています。 ドキュメントには、熱ドロップの面積の60〜70%が示されている場合があります。また、ステンシルで大きなウィンドウをいくつかの小さなウィンドウに分割することを推奨する場合があります。その後、はんだペーストを塗布するときに、スパチュラで大きな穴から絞り出されません。 また、大きなインダクタンスなど、他のコンポーネントの大きなコンタクトパッドを使用することもお勧めします。

コンポーネントインストールシステムがコンポーネントを正しくインストールできるようにするには、ボード上の基準点と、コンポーネントのインストール座標と回転角度が必要です。 これについては、プリント回路基板またはPCB基準のリファレンスマークに関する情報を参照してください。 座標を含むファイルは、PCB設計プログラムで自動的に準備されます。

出力にタブ付きの同様のファイルを取得します。

タイトル:

$ヘッダー$

BOARD_TYPE PCB_DESIGN

単位MM

$ END HEADER

コンポーネントを含むパーツ:

$ PART_SECTION_BEGIN $

R303 RC0402FR-0768KL 270.00 120.30 39.10底面はい

C580 CC0402-KR-X5R-5BB-104 180.00 38.40 88.50底面はい

VT3 NDS331N 90.00 56.80 26.40トップいいえ

...

C282 CC0402-KR-X5R-7BB-104 180.00 128.10 26.20底面はい

VS2 BZT52C-3V3 90.00 71.40 27.10底面はい

U23 MCIMX6Q4AVT08AC 0.00 106.00 45.90トップいいえ

$ PART_SECTION_END $

基準マーク付きの座標:

$ FIDUCIAL_SECTION_BEGIN $

ボード42.50 8.00ボトム

ボード177.00 8.00 BOTTOM

ボード183.40 113.50ボトム

ボード183.40 113.50トップ

ボード177.00 8.00トップ

ボード42.50 8.00トップ

U23 94.50 57.40トップ

U23 117.50 34.40トップ

U10 22.70 87.00トップ

U10 38.70 109.00トップ

U18 52.50 69.50トップ

U18 81.50 98.50トップ

$ FIDUCIAL_SECTION_END $

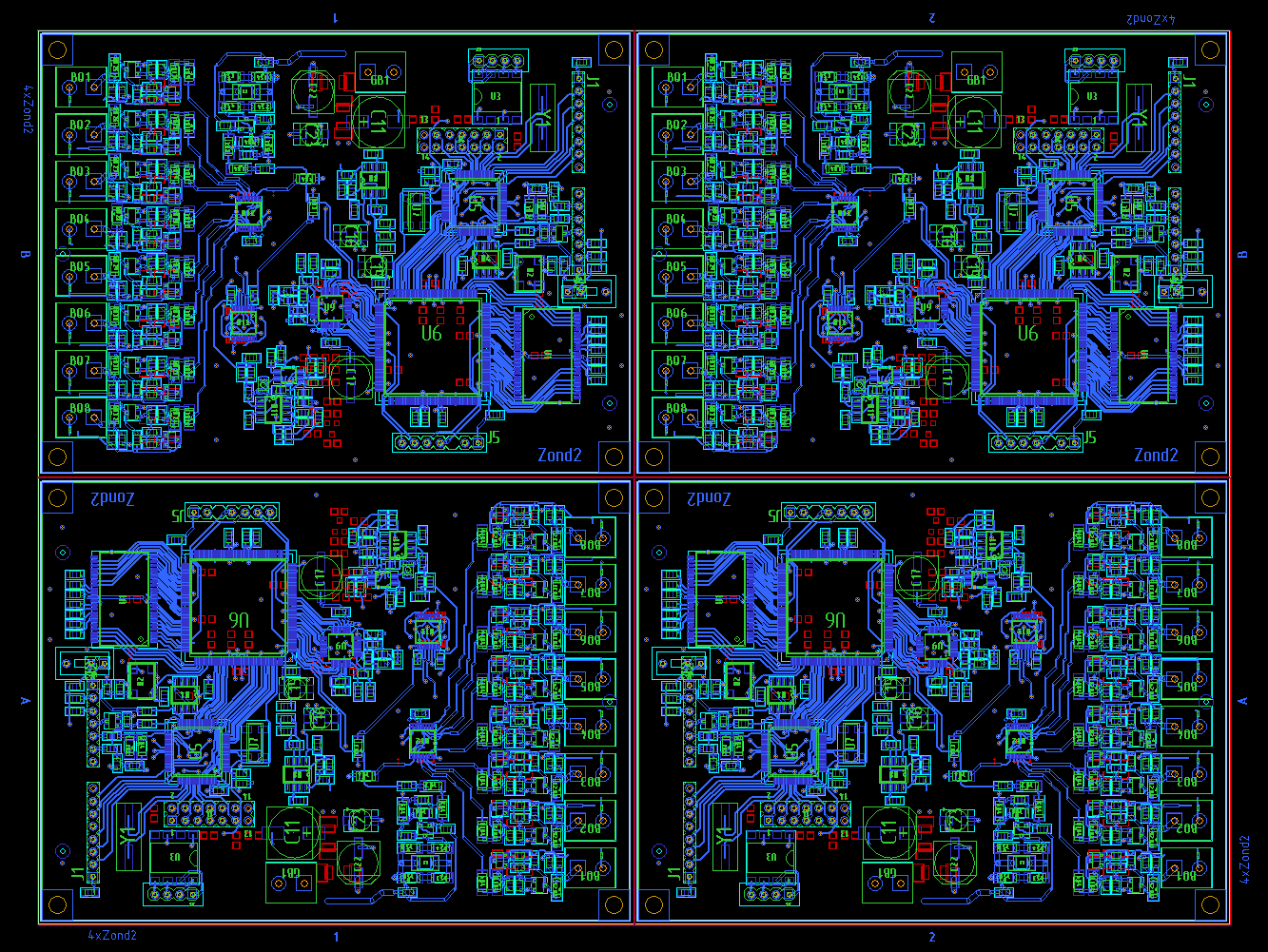

小型ボードでは、小型ボードをグループブランクまたはパネルに結合する必要があります。 PCBバッキングメーカーとインストーラーの両方にこの要件があります。 取り付けには、1つのボードのコンポーネントの座標、ワークピース内のボードのステップ、およびワークピース内のボードの回転角度が与えられます。

基板の回転は、主に湾曲した回路基板でワークピースの面積を縮小するために必要です。 ただし、長方形のボードはパネル内で回転させることもできます。 組み立て工場では、ボードの端に非常に近いピッチのコンポーネントを配置する必要があるため、ボードの片側の技術的なインデントを5から30 mmに増やすことを要求しました。 ボードをパネルに組み合わせた場合、ボードの問題のあるエッジはパネルの中央に配置され、技術的なマージンはすべての辺で5 mmのままでした。 これにより、プリント回路基板の製造において、1つの大きなガラス繊維シート上に2つのパネルを配置することが可能になりました。 同時に、取締役会の顧客は、取締役会の無駄のために過払いをしませんでした。

ガスメーターボードの製造用パネル。

設置後、パネルボードは設置場所で切断するか、簡単に切り離すことができます。 次に、検証、ファームウェア、セットアップ、パッケージング、および販売前の準備が行われます。

これらは、生産のためにボードとデバイスを準備するすべての段階ではありません。 コンポーネントのリストの最小化、製造可能性の確認、ケースの開発、ボード上へのコンポーネントの配置などの操作を追加できますが、私がしなければならないアクションを説明しようとしました。

PS新しいボードの写真はまだ到着していないため、まだありません。 新しいボードのスキームに基づいて、ボードは古いボードの寸法で作成されており、高価なFPGAディスプレイなどの形で不要なフリルがありません。