5月15日に、 「Javaでのマルチコアプログラミング」コースの最初のウェビナー(16のうち) が開催されました 。 ここで、講義で言及された資料 、 ソース 、 用語 、 写真 、 課題 へのリンクを公開したいと思います 。 おそらく誰かがそれらを自分自身に役立つと思うでしょう。

また、udemy.comオンライン教育プラットフォームでScala for Java Developersコースを教えています(Courser / EdXに似ています)。

はじめに

- ムーアの法則

- ハーブサター、 「無料ランチは終わりました」

- アムダールの法則

「鉄」

次のソースで「写真を見る」ことは価値があります

- 「すべてのプログラマがメモリについて知っておくべきこと」

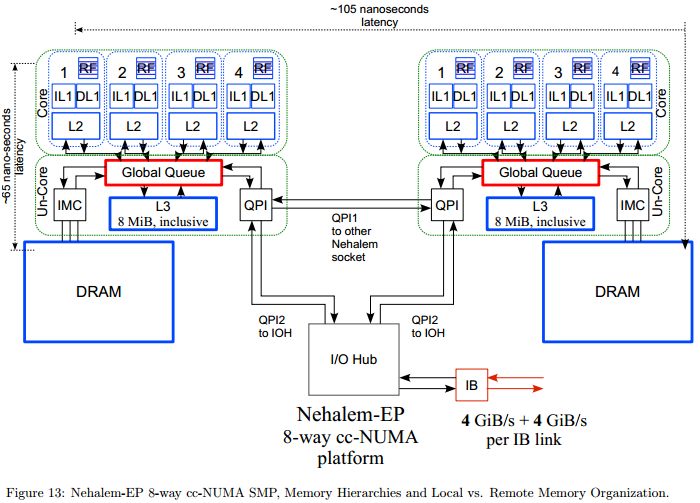

- 「NehalemプロセッサとNehalem-EP SMPプラットフォームのアーキテクチャ」

- 「メモリの一貫性とキャッシュの一貫性に関する入門書」

教科書

Maurice Herlihy、Nir Shavit、 「マルチプロセッサプログラミングの技術」 :「ハードウェアの基礎」ページ469-482

「写真」

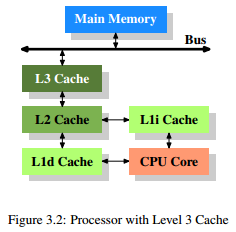

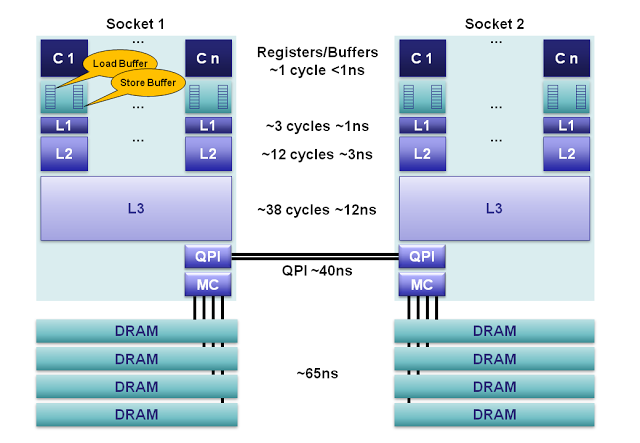

メモリ階層#1

メモリ階層#2

メモリ階層#3

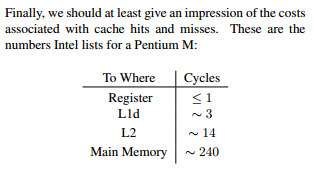

さまざまなメモリレベルへの一般的なアクセス時間

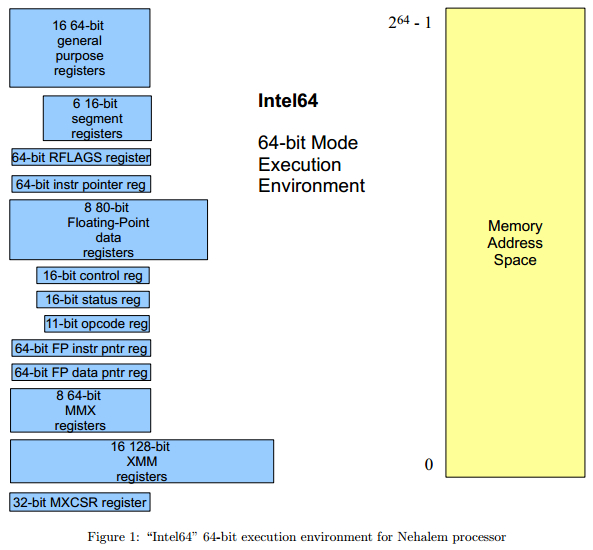

特定のプロセッサレジスタの例

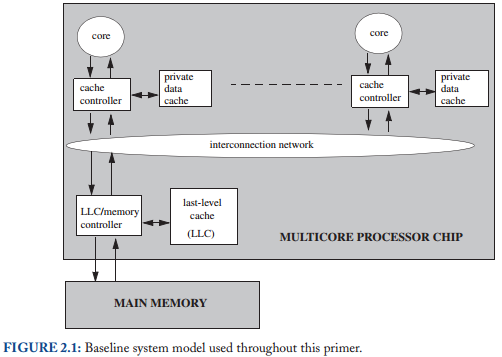

キャッシュコントローラーの概略的な相互作用

偽共有:コード

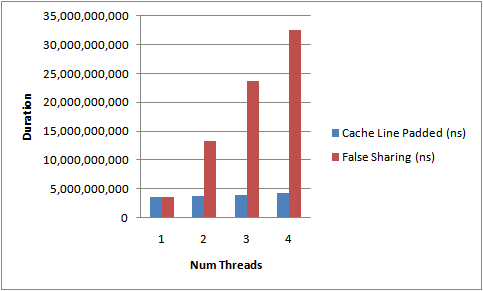

偽共有:効果(負のスケーラビリティ)

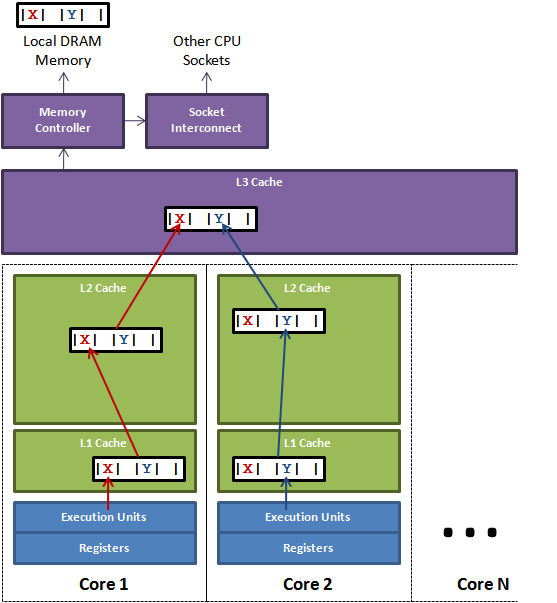

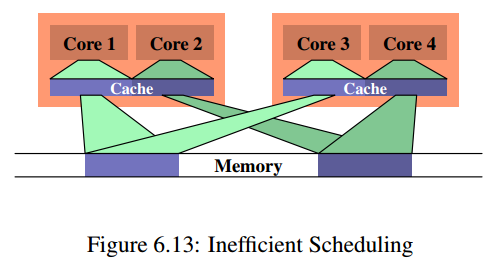

コア、キャッシュ、データ間の不一致

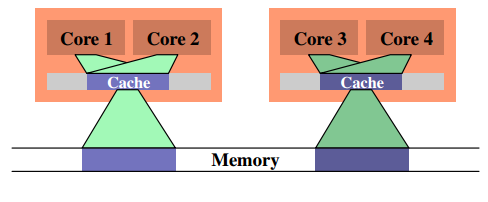

コア、キャッシュ、データ間の良好な一致

規約

規約

CPU、コア、マルチコア時代、メモリウォール、メモリ階層、レジスタ、L1 / L2 / L3キャッシュ、キャッシュライン、偽共有、メモリパディング、キャッシュ汚染、キャッシュミス、SMP、NUMA、マルチソケット、スレッドアフィニティ

用語で読むもの

-機械的同情: 「CPUキャッシュフラッシュの誤Fall」

-機械的な同情: 「メモリアクセスパターンは重要です」

-機械的同情: 「偽りの共有」

-機械的同情: 「False Sharing && Java 7」

-Ruslan Cheremin: 「偽りの共有」

-Ruslan Cheremin: 「キャッシュコヒーレンシ#3:偽共有」

-Ruslan Cheremin: 「キャッシュがハッシュに与える影響」

講義番号1への割り当て

次のプロセッサ特性を返すユーティリティクラスを(オプションAまたは両方のオプション(AとB)で)作成します。

-キャッシュラインサイズ

-キャッシュの数とサイズ(L1、L2、L3)

-コアの数

-SMPまたはNUMAアーキテクチャを定義します

A)「ソフトウェア実験のセットアップ」。 「Gallery of Processor Cache Effects」の記事を読むことをお勧めします(講義2では、記事の例を分析し、問題を解決する方法を概説します)。

B)オペレーティングシステムのAPI呼び出しにJNAを使用する

public class HardwareSpy { public int cacheLineSize() {...} public int cacheL1Size() {...} // -1 , L1 public int cacheL2Size() {...} // -1 , L2 public int cacheL3Size() {...} // -1 , L3 public int coreCount() {...} public int isSMP() {...} public int isNUMA() {...} }

連絡先

ウェビナー、ビデオ録画、プログラムのソースコード、タスクの検証は、コースに登録した人のみが利用できます。

Javaトレーニングをオンラインで行い( プログラミングコースはこちら) 、Java Coreコースの再設計の一環としてトレーニング資料の一部を公開しています 。 視聴者の講義のビデオ録画は、 YouTubeチャンネルで見ることができます。おそらく、 この記事ではチャンネルのビデオがより体系化されています 。

スカイプ:GolovachCourses

メール:GolovachCourses@gmail.com