レトロコンピュータにはさまざまな程度の細心の注意が必要です。 エミュレーションを使用したコンテンツもあります。 FPGAを好む人もいます。その理由は、エミュレーションではなくレクリエーションだからです。 最後に、3番目のプロセッサにサービスを提供します。

しかし、プロセッサは動作するために多くを必要とします! 繰り返しますが、ジレンマ:同じ年の実際のチップを使用するのか、それともすべてをFPGAに入れてプロセッサーを外に置くのですか? しかし、なぜFPGAが必要なのですか? Arduinoとクラシックプロセッサの結合を長く生き続けましょう!

Arduinoに「第2の頭脳」を与え、よりスマートにします。

真の8ビットマイクロプロセッサがプログラムを実行し、ArduinoがROM、RAM、および単純な周辺機器をエミュレートします。

Arduino IDEで仮想周辺機器を設計し、マイクロプロセッサでアセンブラコードを実行します。 複雑な回路やフラッシュパラレルROMを組み立てる必要はありません。

サポートされているマイクロプロセッサー:6502、6809、およびZ80(18581)、その他は準備中です。

マイクロプロセッサを備えたシールドは、LCD、メモリカードなどの他のシールドの接続を妨げません。

自己アセンブリ言語に加えて、マイクロプロセッサでいくつかの古典的なコードを実行しようとすることができます。

確かに、マイクロプロセッサは非常に低い周波数(約95 kHz)で動作します。その正確な値は、周辺エミュレーションコードの最適化に依存します。

アドレス空間の分布は、プログラムでスケッチに設定されます。 マイクロプロセッサは、Arduino Megaで利用可能な8 kB RAMの4〜6 kBに割り当てることができます。 ROMは、使用可能な256のうち200 kB以上を割り当てることができます。

Arduino MegaシリアルポートはUARTをエミュレートできます。

回路、ボード図面、ガーバーファイルはCC-BY-SA 4.0 ここで利用できます 。 同時に、次の警告が含まれているため、必ずREADME.mdファイルを添付する必要があります。

周辺エミュレーションスケッチがアップロードされるまで、シールドを接続しないでください! そうしないと、マイクロプロセッサの出力ラインが短絡する可能性があります。はい、そしてスケッチ自体で、同じ理由で何かを慎重にやり直す必要があります。

6502のデバイスのスキーム:

6809のデバイス図:

Z80上のデバイスのスキーム:

すでに実行できます:

6502を搭載したデバイス-Apple I、Woz Monitor + BASIC ROM

6809を搭載したデバイス- 同じ開発者の自家製コンピューターSimon6809のアナログ、アセンブラーと逆アセンブラーを備えたトレーニングモニター

Z80を搭載したデバイス-これまでのところ、シリアルポートのエコーテストのみで、仮想8251(KR580VV51A)のパフォーマンスを確認できます。

周辺機器をエミュレートするためのファームウェア-MITライセンスの下。

行動原則の簡単な説明:

6502デバイスへ

6809のデバイスへ

Z80のデバイスに-準備中。

開発者はデバイスを販売しようとしていますが、配送は米国のみです。 スキームは非常に単純であるため、購入する特別な理由はありません。ブレッドボード上で1時間で繰り返すことができます。

RCA1802、68008、8085(182185)、8088(181088)で同様のボードを開発する予定です。 K1801BM1については言われていませんが、著者にそのような考えを投げることができます。

ファイル:

6502のデバイス: 組立説明書 、 シルクスクリーン印刷 、 図

6809のデバイス: 組立説明書 、 シルクスクリーン印刷 、 図

Z80のデバイス: 組み立て説明書 、 シルクスクリーン印刷 、 図

Arduinoと6502デバイスの相互作用を考慮するArduinoは、クロックパルスを供給するように設計されたマイクロプロセッサの入力レベルを0から1、またはその逆に定期的に変更します。 各ステップで、制御線とアドレスバスで何が起こっているかをチェックし、状況に応じて、データバスから情報を読み取るか、そこに送信します。 ArduinoはIRQおよびNMIラインを制御することもでき、中断を引き起こします。 この図は、データのタイプとその送信の方向を示しています。

Arduinoポートとマイクロプロセッサー出力の対応は、スケッチで構成されます。

/* Digital Pin Assignments */ #define DATA_OUT PORTL #define DATA_IN PINL #define ADDR_H PINC #define ADDR_L PINA #define ADDR ((unsigned int) (ADDR_H << 8 | ADDR_L)) #define uP_RESET_N 38 #define uP_RW_N 40 #define uP_RDY 39 #define uP_SO_N 41 #define uP_IRQ_N 50 #define uP_NMI_N 51 #define uP_E 52 #define uP_GPIO 53

各メジャーを次のイベントに分割します。

CLKは状態を1から0に変更します(拒否)

CLKはゼロの状態です

CLKは状態を1から0に変更します(上昇)

CLKはユニット状態です

CLKは再び状態を1から0に変更します...

状態遷移の瞬間に何が起こりますか?

6502は、入力CLK0でクロックパルスを受信し、それらをバッファリングして、CLK1とCLK2の2つの出力に送信します。 マイクロプロセッサ内のすべてのイベントはCLK1に関連付けられていますが、遅延は小さく、マイクロプロセッサがArduinoからクロックパルスを受信するラインであるCLK0に関連付けられていると想定しています。 そして、信号を単にCLKと呼びます。

1. CLKは状態を1から0に変更します。

2.マイクロプロセッサは、新しいアドレスをアドレスバスに出力し、R / W出力への読み取りと書き込みの切り替え信号を出力します。 しかし、彼はまだデータ交換の準備ができていません。

3. CLKはユニット状態になり、これはデータの交換が開始されたことを意味します。 これが読み取り操作の場合、マイクロプロセッサはデータバス出力を入力状態に転送してデータを受信し、書き込み操作の場合、それらを出力状態に転送してデータを送信します。 また、R / W信号は、外部デバイスを書き込みモードまたは読み取りモードに切り替えます。これは、マイクロプロセッサーの対応する状態の反対です。

4. CLKがゼロになります。 これで、マイクロプロセッサも入出力デバイスもデータバスに何も出力しません。 マイクロプロセッサは、データバスラインとR / Wピンを新しい状態に設定できます。

子供が理解できる簡単な説明。 マイクロコントローラのみをプログラミングする場合、これらの「舞台裏の陰謀」について誰も考えません。 アセンブラーでも。

周辺機器を接続する必要がある場合は、CLKラインにユニット(準備時間)が表示される前にデータを準備する時間が必要です。ユニットが存在する間は、変更しないでください。 CLKがゼロのときに周辺機器にデータを準備する時間がない場合、またはユニットが存在するときにデータを変更する場合、なぜコードが機能しないのか長い間不思議に思うでしょう。 マイクロプロセッサのクロック周波数は公称周波数の10〜15倍低いため、この要件に容易に準拠できます。 しかし、それは必要です。

そのため、クロックパルスを生成するためにArduinoを「教える」必要があり、アドレスバスとR / Wラインで何が起こるかを継続的にチェックし、それに応じてデータバスとやり取りします。 これを行うために、スケッチはtimer1タイマー割り込みを使用し、95 kHzの周波数のパルスを生成します。 Arduinoはマイクロプロセッサよりもはるかに高速に動作するため、クロック間ですべてを読み取り、準備することができます。 スケッチを変更した後、この条件が引き続き満たされるようにすることが重要です。

これは、CLKがゼロから1に移行する方法と、次に何が起こるかを示すスケッチからの抜粋です。

//////////////////////////////////////////////////////////////////// // Processor Control Loop //////////////////////////////////////////////////////////////////// // This is where the action is. // it reads processor control signals and acts accordingly. // ISR(TIMER1_COMPA_vect) { // Drive CLK high CLK_E_HIGH; // Let's capture the ADDR bus uP_ADDR = ADDR; if (STATE_RW_N) ////////////////////////////////////////////////////////////////// // HIGH = READ transaction { // uP wants to read so Arduino to drive databus to uP: DATA_DIR = DIR_OUT; // Check what device uP_ADDR corresponds to: // ROM? if ( (ROM_START <= uP_ADDR) && (uP_ADDR <= ROM_END) ) DATA_OUT = pgm_read_byte_near(rom_bin + (uP_ADDR - ROM_START)); else if ( (BASIC_START <= uP_ADDR) && (uP_ADDR <= BASIC_END) ) DATA_OUT = pgm_read_byte_near(basic_bin + (uP_ADDR - BASIC_START)); else // RAM? if ( (uP_ADDR <= RAM_END) && (RAM_START <= uP_ADDR) ) DATA_OUT = RAM[uP_ADDR - RAM_START]; else // 6821? if ( KBD <=uP_ADDR && uP_ADDR <= DSPCR ) { // KBD? if (uP_ADDR == KBD) { ... // handle KBD register } else // KBDCR? if (uP_ADDR == KBDCR) { ... // handle KBDCR register } else // DSP? if (uP_ADDR == DSP) { ... // handle DSP register } else // DSPCR? if (uP_ADDR == DSPCR) { ... // handle DSPCR register } } } else ////////////////////////////////////////////////////////////////// // R/W = LOW = WRITE { // RAM? if ( (uP_ADDR <= RAM_END) && (RAM_START <= uP_ADDR) ) RAM[uP_ADDR - RAM_START] = DATA_IN; else // 6821? if ( KBD <=uP_ADDR && uP_ADDR <= DSPCR ) { // KBD? if (uP_ADDR == KBD) { ... // handle KBD register } else // KBDCR? if (uP_ADDR == KBDCR) { ... // handle KBDCR register } else // DSP? if (uP_ADDR == DSP) { ... // handle DSP register } else // DSPCR? if (uP_ADDR == DSPCR) { ... // handle DSPCR register } } } //////////////////////////////////////////////////////////////// // We are done with this cycle. // one full cycle complete clock_cycle_count ++; // start next cycle CLK_E_LOW; // If Arduino was driving the bus, no need anymore. // natural delay for DATA Hold time after CLK goes low (t_HR) DATA_DIR = DIR_IN; }

アドレス空間の割り当ては任意の方法で行うことができます。変更されていないスケッチでは、256バイトのROM、8キロバイトのBASIC用ROM、4キロバイトのRAM、6821入出力デバイスを備えたApple 1と同じです。

// MEMORY LAYOUT // 4K MEMORY #define RAM_START 0x0000 #define RAM_END 0x0FFF byte RAM[RAM_END-RAM_START+1]; // ROMs (Monitor + Basic) #define ROM_START 0xFF00 #define ROM_END 0xFFFF #define BASIC_START 0xE000 #define BASIC_END 0xEFFF //////////////////////////////////////////////////////////////////// // Woz Monitor Code //////////////////////////////////////////////////////////////////// // PROGMEM const unsigned char rom_bin[] = { 0xd8, 0x58, 0xa0, 0x7f, 0x8c, 0x12, 0xd0, 0xa9, 0xa7, 0x8d, 0x11, 0xd0, ... 0x00, 0xff, 0x00, 0x00 }; // BASIC ROM starts at E000 PROGMEM const unsigned char basic_bin[] = { 0x4C, 0xB0, 0xE2, 0xAD, 0x11, 0xD0, 0x10, 0xFB, ... 0xE0, 0x80, 0xD0, 0x01, 0x88, 0x4C, 0x0C, 0xE0 };

RAMは、バイトRAM配列[RAM_END-RAM_START + 1]によってエミュレートされます。 エミュレートされたROMの内容がマイクロコントローラーのフラッシュメモリに保存されるように、2つのPROGMEMキーワードが必要です。

6821は十分にエミュレートされており、仮想キーボードとディスプレイは「ターミナル」を介して機能します。 Woz MonitorとBASICが動作しますが、これは著者が求めていたものです。

周辺機器をエミュレートするには、そのデータシートを注意深く読み、そのレジスタが何であり、何のためにあるのかを調べる必要があります。 エミュレーションの利便性は、周辺のソフトウェアの類似物を作成できる柔軟性にあります。

I / Oデバイスはマイクロプロセッサのアドレス空間にあり、メモリセルと同じ方法でアクセスされます。 LCDディスプレイ、メモリカード、サウンド出力などの「鉄」周辺機器を使用するには、アドレススペースに場所を割り当てる必要があります。

参照:

www.6502.org

www.callapple.org/soft/ap1/emul.html

skilldrick.github.io/easy6502

searle.hostei.com/grant/6502/Simple6502.html

wilsonminesco.com/6502primer

SB-Assembler: www.sbprojects.net/sbasm

6809に移動すると、以下が含まれます。

2つの8ビットバッテリーAおよびB、1つの6ビットバッテリーに結合可能

2つの16ビットスタックインデックス

命令カウンターに関連するアドレス指定

1または2を自動的に加算または減算します

2つの8桁の符号なし数値の乗算

16ビット演算

すべてのレジスタ間でのデータの転送および交換

すべてのレジスタおよびそれらの任意の組み合わせの書き込みと読み取り

マイクロプロセッサ6809E(外部)には外部クロックジェネレータが必要で、6809には内部クロックジェネレータがあります。 日立では、それぞれ6309Eおよび6309と呼ばれ、通常の操作とは異なり、操作内で32ビット形式で動作しますが、クラシックバージョンとの互換モードに切り替えることができます。

実際、RetroShieldプロジェクト全体が開始されたのは、作者が自分で作ったコンピューターSimon6809をアップグレードして、結果をSimon6809 Turboと名付けようとしたためです。 しかし、彼がそこに実装したかったすべてのものの標準的なロジックチップには、多くが必要であることがわかりました。 したがって、著者は6809に関連して初めてRetroShieldのアイデアを策定し、「他のプロセッサと同じことが同じ場合はどうなるのか?」と考えました。

もちろん、デバイスは外部クロックを必要とする6809Eを使用するため、外部から作業を同期できます。 両方のプロセッサのEおよびQラインは同じものと呼ばれ、6809のみに出力があり、6809Eには入力があります。

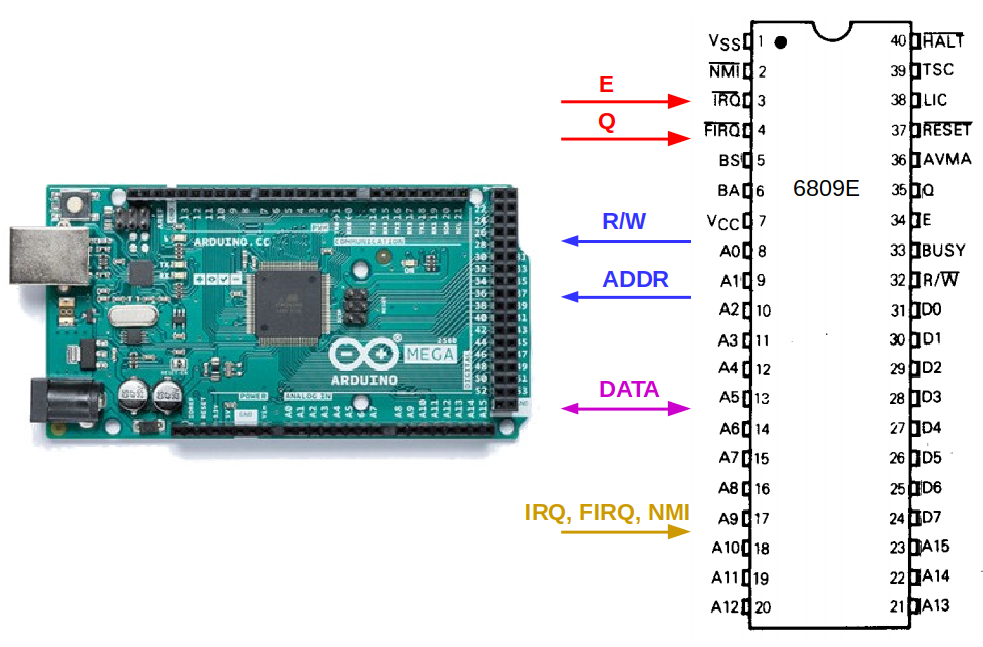

Arduinoは6502と同様に6809と対話しますが、2つのクロック入力(EとQ)、および3つの割り込み入力(IRQ、FIRQ、NMI)があります。

今回、Arduinoポートとマイクロプロセッサピン間の対応は次のように構成されます。

/* Digital Pin Assignments */ #define DATA_OUT PORTL #define DATA_IN PINL #define ADDR_H PINC #define ADDR_L PINA #define ADDR ((unsigned int) (ADDR_H << 8 | ADDR_L)) #define uP_RESET_N 38 #define uP_E 52 #define uP_Q 53 #define uP_RW_N 40 #define uP_FIRQ_N 41 #define uP_IRQ_N 50 #define uP_NMI_N 51 #define uP_GPIO 39

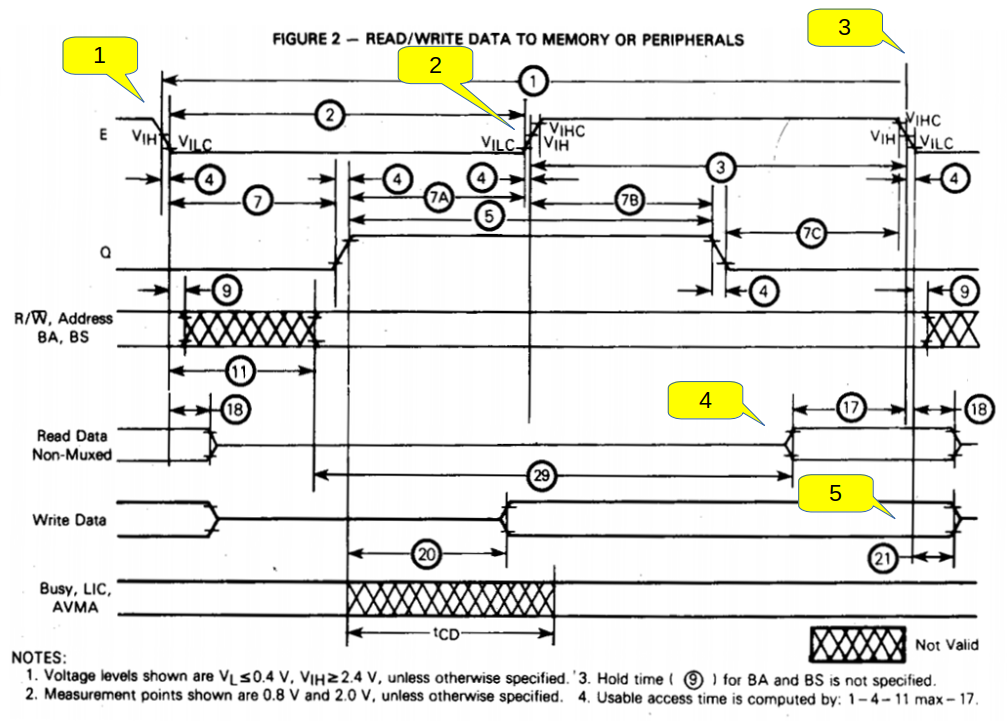

グラフからわかるように、信号Qは周期Eに対して周期の1/4だけシフトしています。

すべてのイベントはEに関連付けられているため、Qにはほとんど注意を払いません。すべてが次のように発生します。

- Eはゼロに切り替わります。 プロセッサは、アドレスバスに新しいアドレスを設定し、R / Wラインの状態を変更します。

- Eは1に切り替わり、プロセッサはデータ交換の準備が整います。

- Eが1である限り、データバスに何が起こるかは問題ではありません。主なことは、必要なデータがEがゼロに戻った時点でそこに存在することです。

- データを読み取る場合、I / Oデバイスは、ラインEが1から0に移る前に必要なデータをデータバスに供給する必要があります(最小遅延は円の番号17で示されます)。

- 記録するとき、I / Oデバイスは、Eが1から0になった時点の形式で、あるレジスタのデータを修正する必要があります。 プロセッサは、Qが1(円の20)に遷移する瞬間に、このデータをさらに早くバス上に提供します。

- Eがゼロに移行した後、すべてが繰り返されます。

上記のすべては、時間に関係するすべての信号を開発するための周辺機器(仮想デバイスを含む)の必要性について6502について述べています6809。

6502の場合のように、信号EとQの生成。2つの信号があり、グラフに従って切り替える必要があるという唯一の違いがあります。 同様に、割り込み時に呼び出されるサブルーチンは、必要なタイミングでデータの入力または出力を実行します。

変更されていないスケッチのアドレススペースは、 自家製のSimon6809コンピューターと同じ方法で配布されます。

// MEMORY #define RAM_START 0x0000 #define RAM_END 0x0FFF #define ROM_START 0xE000 #define ROM_END 0xFFFF byte RAM[RAM_END-RAM_START+1]; //////////////////////////////////////////////////////////////////// // Monitor Code //////////////////////////////////////////////////////////////////// // static const unsigned char PROGMEM const unsigned char simon09_bin[] = { 0x1a, 0xff, 0x4f, 0x1f, 0x8b, 0x0f, 0x36, 0x7f, 0x01, 0xa5, 0x10, 0xce, ... 0x00, 0x09, 0x00, 0x0c, 0x00, 0x0f, 0xe0, 0x00 };

RAMとROMは、6502バリアントと同じ方法でアレイに保存されますが、唯一の違いは、ROMデータを持つアレイが1つしかないことです。

I / Oデバイスにもアドレス空間の一部が割り当てられ、仮想デバイスでも実デバイスでもかまいません。 Simon6809はビンテージの要素ベースに基づく最新のマシンであるため、「ターミナル」が実行されているPCからFTDIを介してデータを交換します。 ここではエミュレートされています。

参照:

Artoページの 6809に関する多くの情報

6809に関するウィキペディアの記事

SWTPc 6809システム

FLEXオペレーティングシステムに関するウィキペディアの記事