TFTが発明されなかった場合はどうなりますか? CSTN LCDモニター

エントリー

CRTモニターが普及したとき、次の議論が支持されました:すべての改善にもかかわらず、LCDディスプレイは画質において決してチューブディスプレイを上回ることはありません。 以前のように、エネルギー効率と薄い厚さが必要な場合にのみアプリケーションを見つけます[1]。 数十年が経過し、この議論の支持者が正しかったかどうかがわかりました。 しかし今日、その当時のLCDを見るのは興味深いです。それらは本当にそれほど低品質ですか? 2019年のCSTNマトリックスを見るのはどうですか?

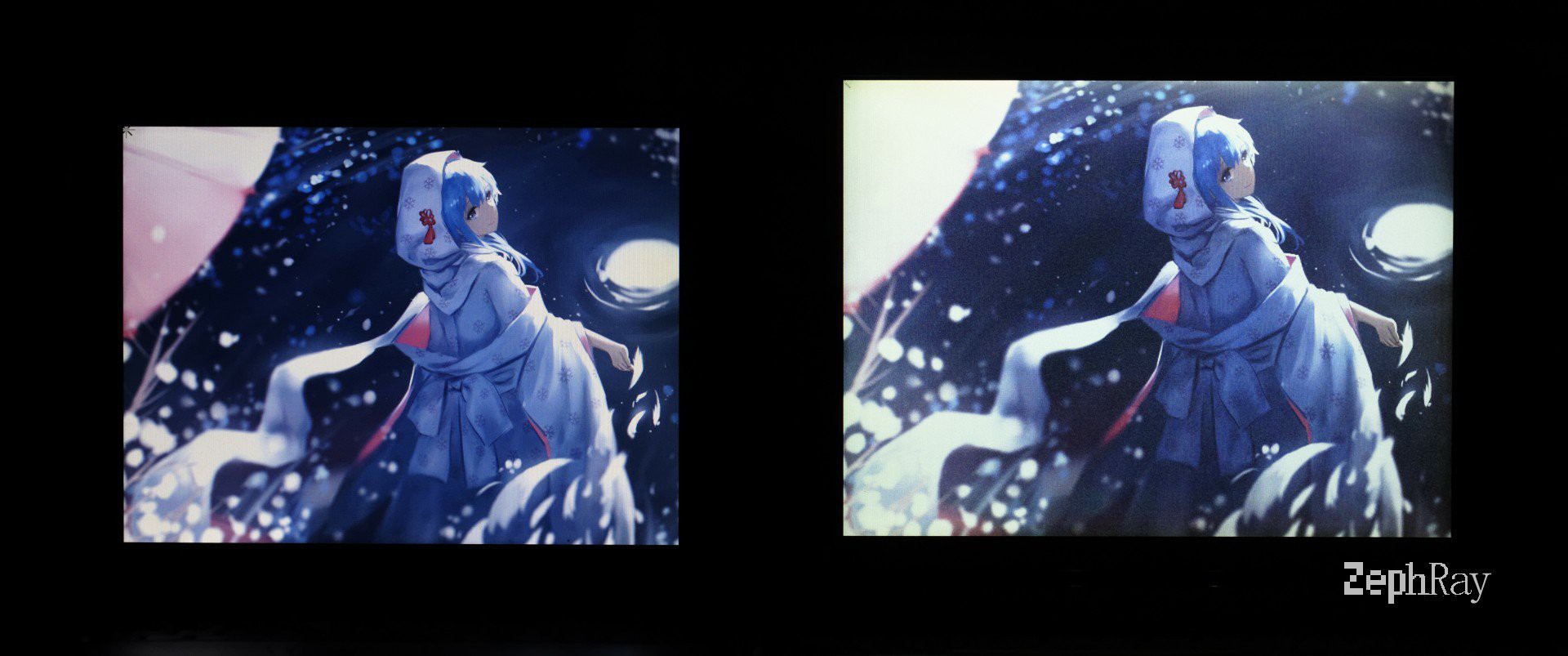

左TFT、右CSTN、両方とも90年代のディスプレイ

前世紀のLCD

TFTに切り替える前は、ポータブルコンピューターでさまざまなディスプレイ技術が使用されていました。 最初は、デスクトップコンピューターと同じCRTモニターを使用しましたが、小さいモニターのみを使用していました。 たとえば、Compaq Portable(1983)、IBM 5155(1984)、またはCommodore SX-64(1984)。

IBM 5155、著者:Soupmeister、ライセンス:CC-BY-SA-2.0、 こちらから

そのようなPCをどこにでも持ち運ぶのは難しく、まったく異なるものでした。たとえば、IBM 5140(1986)、Toshiba T1000(1987)などのTN-LCD(ねじれネマティック)を搭載したラップトップです。 これらのディスプレイは、コントラストと視野角が低くなっています。

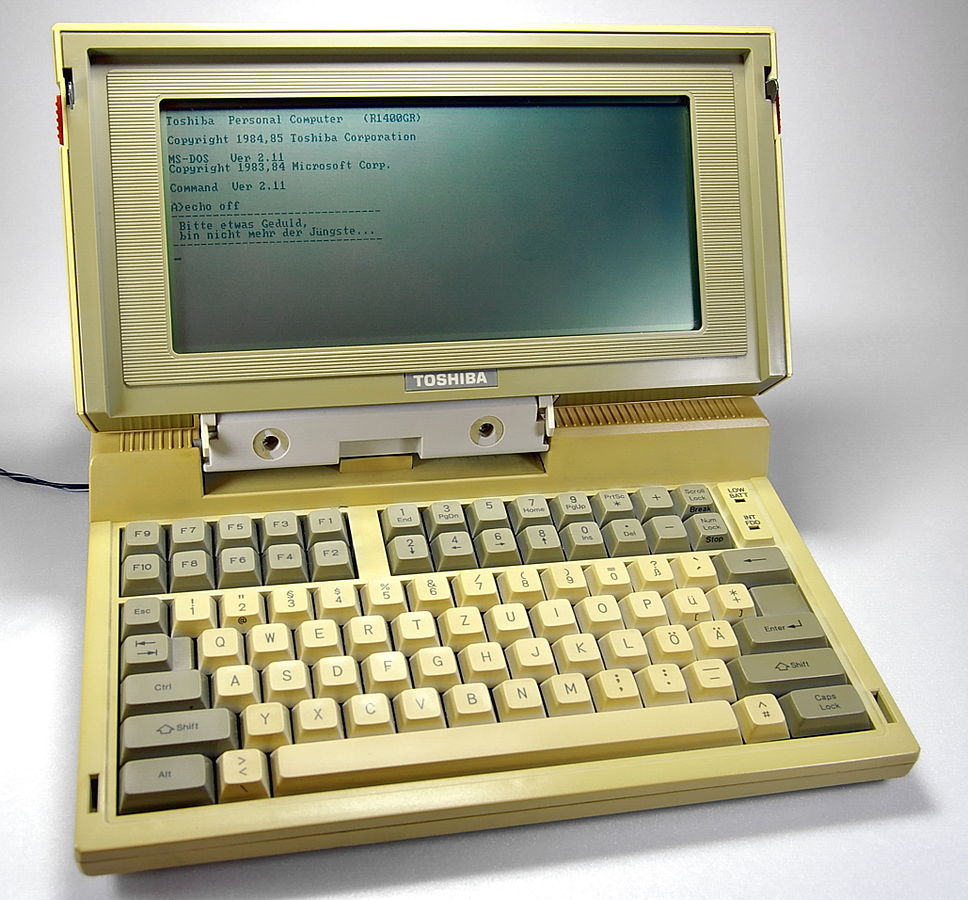

モノクロTNディスプレイを搭載したToshiba T1100、著者:Johann H. Addicks、ライセンス:GFDL、 ここから、リンクが壊れています、オリジナルも

Toshiba T3200(1987)およびIBM PS / 2 P70(1991)ラップトップが光を放ったため、一部のメーカーはガス放電マトリックスを実験しました。 これらは、高コントラストと赤オレンジ色の光の輝度のいくつかのグラデーションを提供しましたが、かなり高価でした。 最後に、STN-LCD(スーパーツイストネマティック)は、たとえばElectronics MC1504およびそのプロトタイプToshiba T1100で開発されました。 コントラストははるかに良く、1:5から1:50であり、ビジネスアプリケーションには明るさのいくつかのグラデーションで十分でした(日常生活でラップトップを使用するのはまだ高価すぎました)。 しかし、ユーザーがカラー画像が必要な場合はどうでしょうか? このケースでは、TFTとCSTN(カラースーパーツイストネマティック)の2つの技術を提供されました。 TFTを搭載した最初のラップトップであるNEC PC9801NCは1990年に導入され、当時の画質は賞賛に値しませんでしたが、「このようなおもちゃ」のコストは他のラップトップコンピューターよりもはるかに高く、それほど高価ではありません。 さて、CSTNディスプレイは単なるSTNディスプレイであり、その上にフィルターが重ねられています。 長い間、ラップトップは両方のタイプのマトリックスを使用していました。 また、ニューヨークの地下鉄車両では、CSTNモニターが引き続き機能します。

それらの1つ、ソース: Transit + PLUS

CSTroN

著者はCSTNディスプレイを見たかった。 どうやって? 手始めに、古いラップトップを購入して使用するだけです。 AMD 5x86-P133プロセッサであることが判明しました。 つまり、そこで実行できる最もダイナミックなものはDOSゲームです(まあ、MPEG1はQVを引くでしょう-プログラムの翻訳者)。 もちろん、それらをプレイするのは素晴らしいことですが、たとえばYouTubeや現代のゲームがこのようなディスプレイ上でどのように見えるかを見たかったのですが、これは不可能です。

それとも?

一般に、何らかの方法でVGAまたはHDMI入力を追加する必要があります。そして、最新のものから信号を送信できます。 ラップトップのTFTスクリーンは非常に頻繁にモニターに作り直されます。 マトリックスに一致するボードを購入するだけで完了です。 また、FPGAで独自のプレフィックスを作成して、VGAまたはHDMI信号をピクセルデータストリームに変換できます。

むかし、CSTNマトリックスをVGAモニターに変換するためのボードも製造されていましたが、これはもう見当たりません。 ただし、このためにFPGA ML505のデバッグボードを適合させることができます。

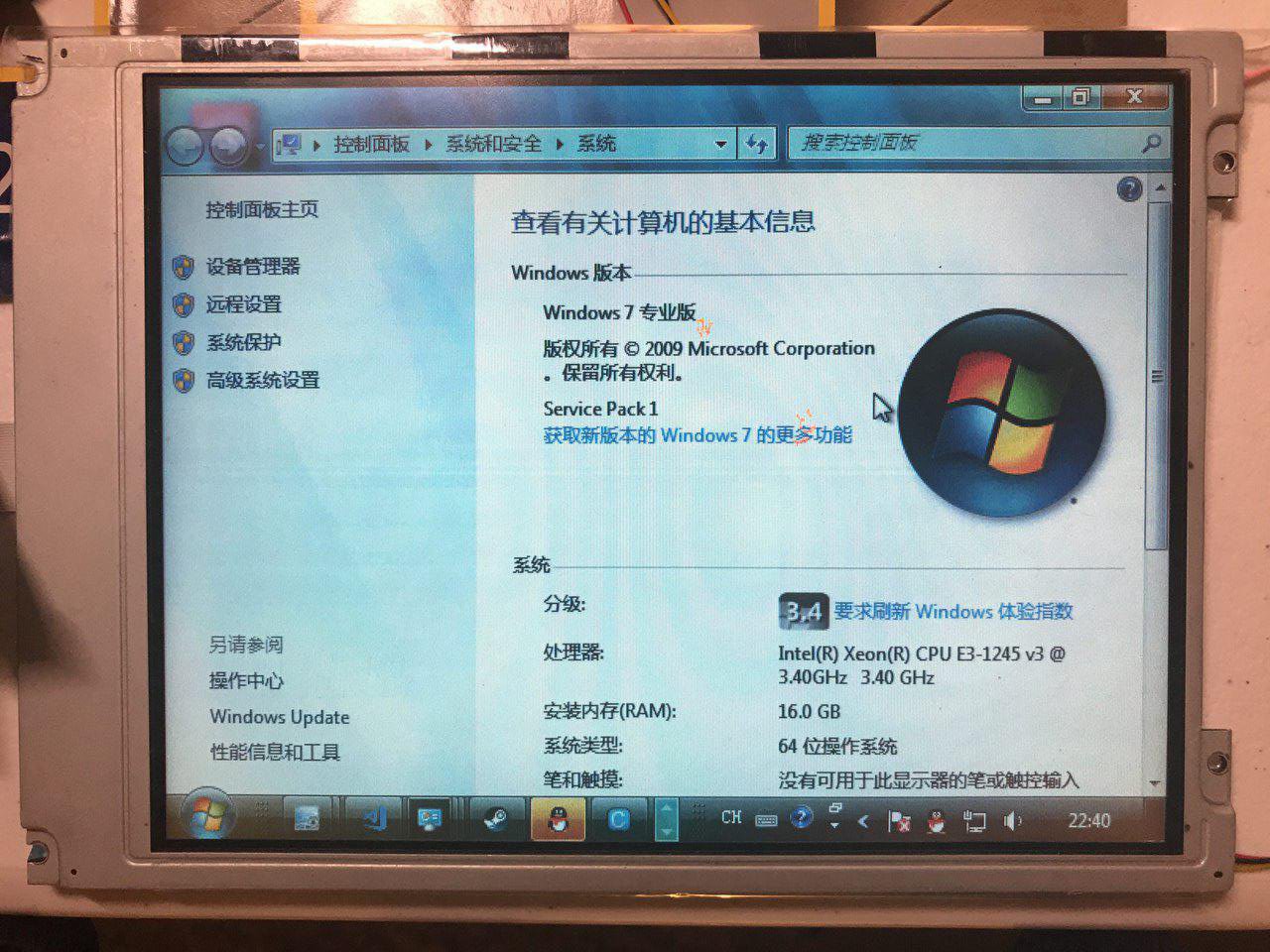

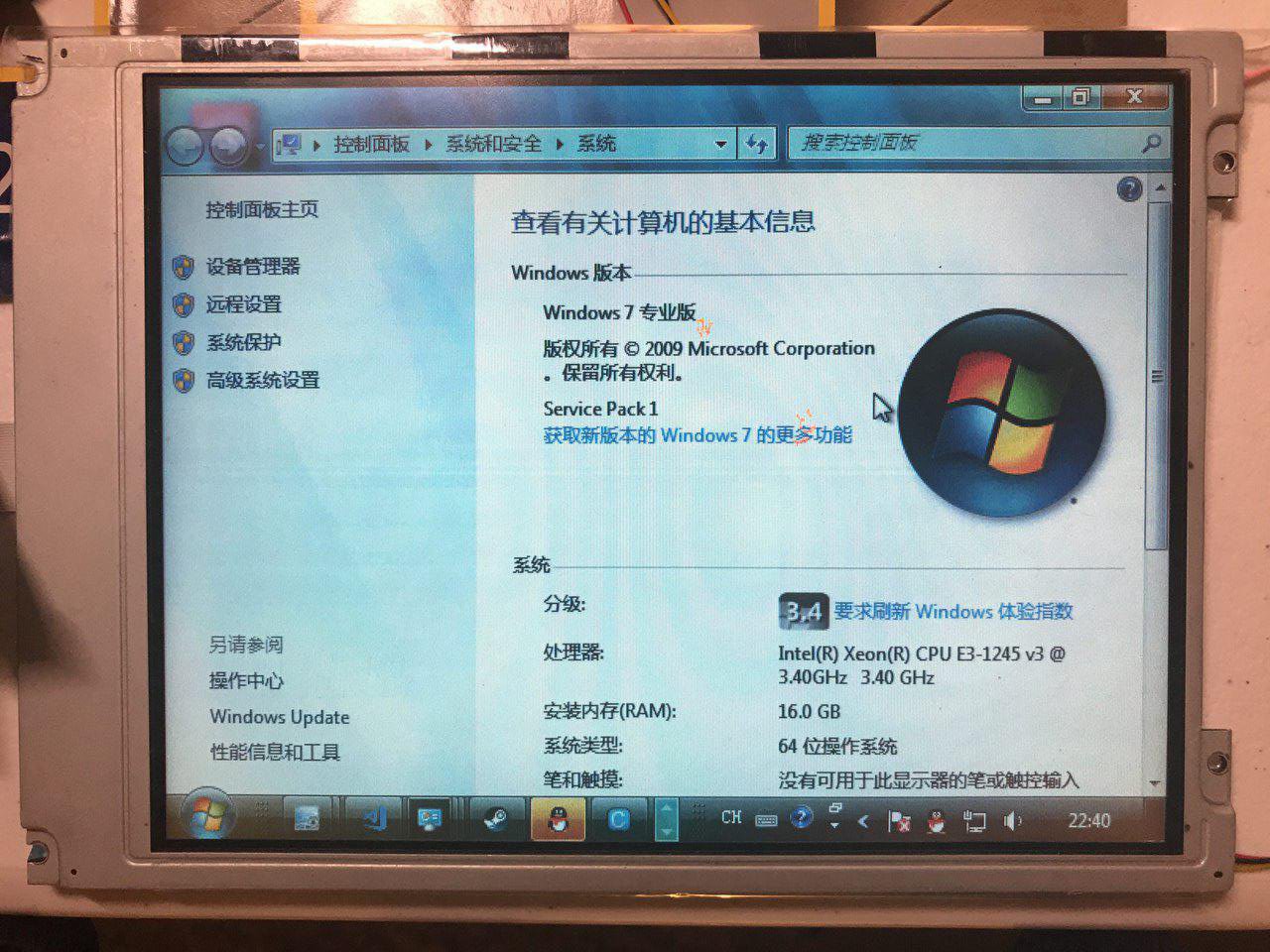

完成した結果。 これをCSTNディスプレイで見るのはかなり珍しいことです:16 GBのRAM。

マトリックス管理

基本から始めましょう。 他のマトリックスディスプレイと同様に、CSTNディスプレイには行と列があります。 マイクロコントローラーからLEDマトリックスを制御したことがありますか? ここでも同じですが、電圧は可変です。 選択した行と選択していない行と列の両方に特定の信号を適用する必要があります。選択した行と列の交点のピクセルに必要なものが表示されます。 信号の形状は非常に複雑で、電圧の平均二乗値、行と列の電圧間の位相シフト、オフセット...そして、ピクセルごとに画像が形成されます。

幸いなことに、FPGAはこれらすべての信号を生成する必要はなく、膨大な数のライン上でも必要ありません。 これはすべて、ディスプレイに組み込まれたモジュールによって行われます。 そこで、パルス変換器は定電圧を増加させ、それが分圧器とリピータを通過するため、バイアス電圧が得られます。 行および列ドライバーは、この電圧を必要な形状の変数に変換します。 必要なのは、ピクセル状態データのストリームをディスプレイモジュールに送信することだけです。

DPI(デジタルパラレルインターフェイス)を備えたTFT-LCDでは、1つのピクセルに関するすべてのデータが単一のクロックサイクルで一度に受信されます。 水平およびフレーム同期のラインでは、各ラインおよびフレームの後にそれぞれパルスが受信されます。 ピクセルは、ラインごと、フレームごとに単純に連続的に送信されます。 フルフレームの送信に1/60秒かかる場合、リフレッシュレートは60 Hzです。 データバスの幅は、通常16(赤と青の場合は5ビット、緑の場合は6ビット)、18(各色の場合は6ビット)、または24(各色の場合は8ビット)の色深度と同じです。 LVDSも同じです。ビットのみがパラレルで送信されるのではなく、差動ペアで順番に送信されますが、MIPI DSIではパケットに結合されます。 SPI / i80バスを使用すると、さまざまなコマンドをコントローラーに送信でき、コントローラーはそれらを実行して、DPIまたは同様のインターフェイスの信号を生成します。 これは、VGAを幾分連想させるものであり、各色の明るさに関するデータのみがアナログ形式ではなくデジタル形式で受信されます。 VGAからDPIへのコンバーターがあり、その逆もあります。 Raspberry PiからVGA信号を受信できるボードは非常に便利ですが、最初はこのコンピューターはHDMIとコンポジットビデオのみを生成します。

DPIインターフェイスを備えたTFTマトリックスに供給される信号と非常に類似した信号は、CSTNマトリックスのディスプレイモジュールに供給される必要があります。 SX21V001 [2]のデータシートは、640x480の解像度でCSTNディスプレイを制御する方法を示しています。

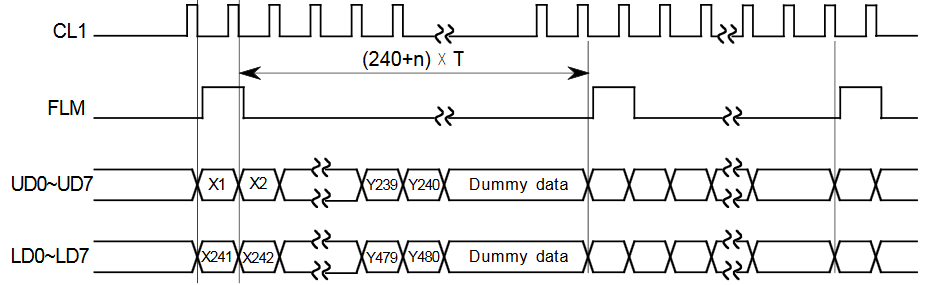

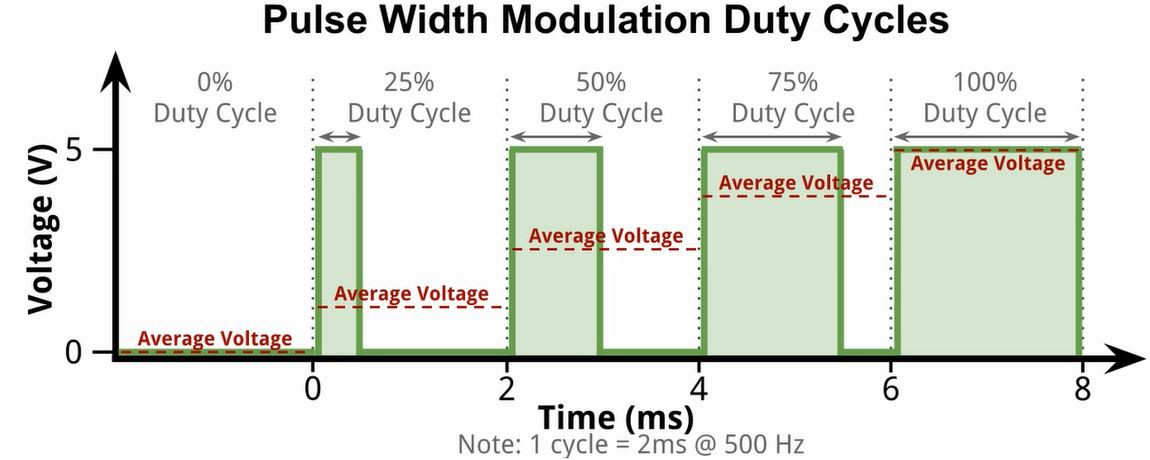

これは、フレーム全体の転送を示しています。 信号は、各ラインの後にCL1のラインに、各フレームの後にFLMに到着します。 また、16行のデータバスがあります。 実際、この図でエラーが発生しました。1行目と2行目の送信中に、データY1とY2が送信され、X1とX2ではなく、それぞれY140とY242がUD0-UD7ラインで受信されます。 ここで、UとLはそれぞれ上部と下部です。つまり、ディスプレイは上下に位置する640x240の解像度を持つ2つのマトリックスで構成されます。 ここに、古いラップトップ広告からの神秘的な「デュアルスキャン」があります。そこから、画面全体に水平ストリップが表示されます。 STNおよびCSTNディスプレイの場合、コントラストは行数に反比例するため、この分離によりコントラストを上げることができます。 しかし、これがTFTとの制御の点で異なる唯一の方法ではありません。

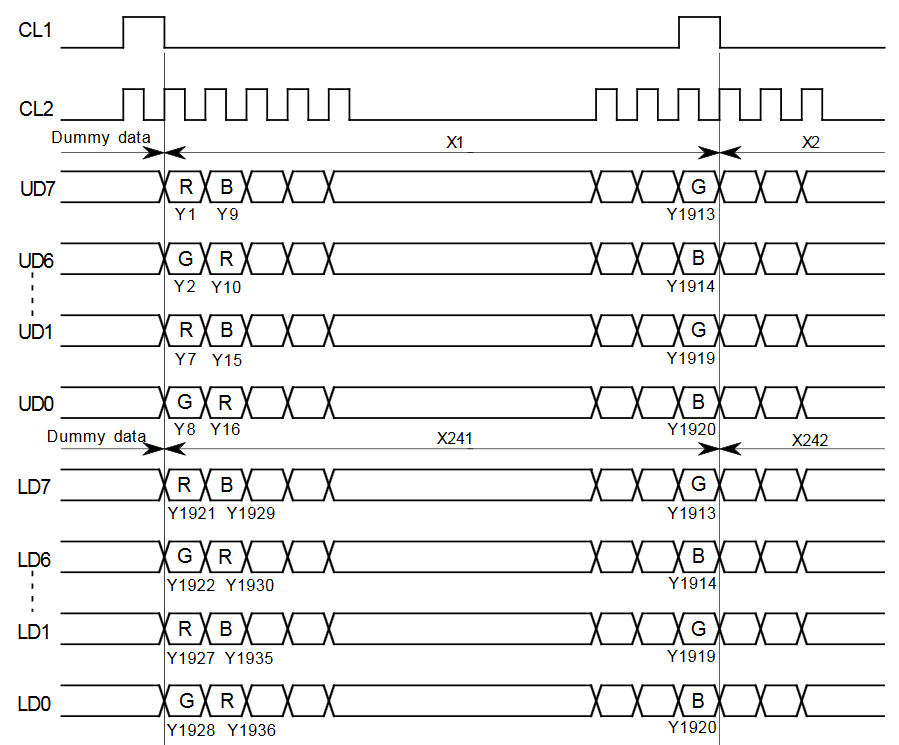

ここで横軸がYと呼ばれた理由は明らかではありません...しかし、いずれにせよ、ここのCL2はピクセルを切り替えるクロックパルスを供給するためのラインです。 しかし、1サイクルのUDおよびLDバスでは、TFTのような1つのマルチビットピクセルに関するデータは送信されませんが、一度に複数のピクセルに関するデータがそれぞれ3ビット送信されます。 カラーごとに1ビット、ピクセルごとに3ビット—合計8色。

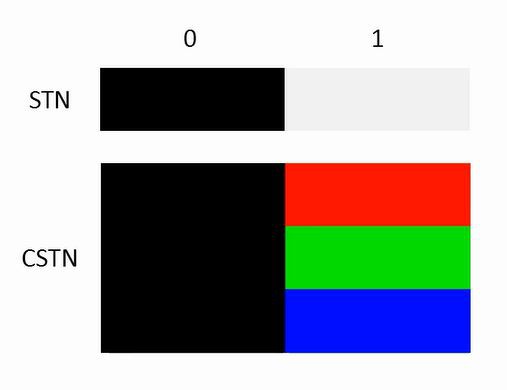

しかし、どのように? CSTNディスプレイには、たとえば4096や32768などの少数の色がありますが、8はありません。 ここでPWMが適用されていることがわかります。 LEDはこの方法で制御されます。つまり、LCDピクセルが可能です。 たとえば、50%の輝度が必要です。偶数フレームでピクセルをオンにし、奇数フレームでピクセルをオフにします。 この方法はFRC(フレームレートコントロール)と呼ばれますが、このコンテキストでのPWMは、同じ方法でピクセル輝度コントロールと呼ばれますが、2つ以上のフレーム内で1つです。 この機能がサポートされている場合、FRCは外部デバイスを実装し、PWMはディスプレイモジュールチップを実装します。 著者は、PWMを使用したCSTNディスプレイを知りませんが、これらはHPAタイプのマトリックスであることを示唆しています。 いずれの場合でも、PWMは使用できないため、FRCを使用して必要な色深度を取得できます。

ちらつきがこの価格になるため、CSTNディスプレイでは、(TFTと比較して)巨大なフレームレートが見られます。 たとえば、このモジュールは当初120 Hzでしたが、作成者は240にオーバークロックしました。

実装方法

開発者は一度にいくつかの困難に直面しました。

-入力信号のフレームレートは60 Hzです。2倍にするか、4倍にする必要があります

-入力信号では、フレームはそれぞれ640x240ピクセルの上半分と下半分に分割されませんが、ここでは分割する必要があります

-また、FRCを実装する必要があります。それ以外の場合、色深度はピクセルあたり3ビットになります

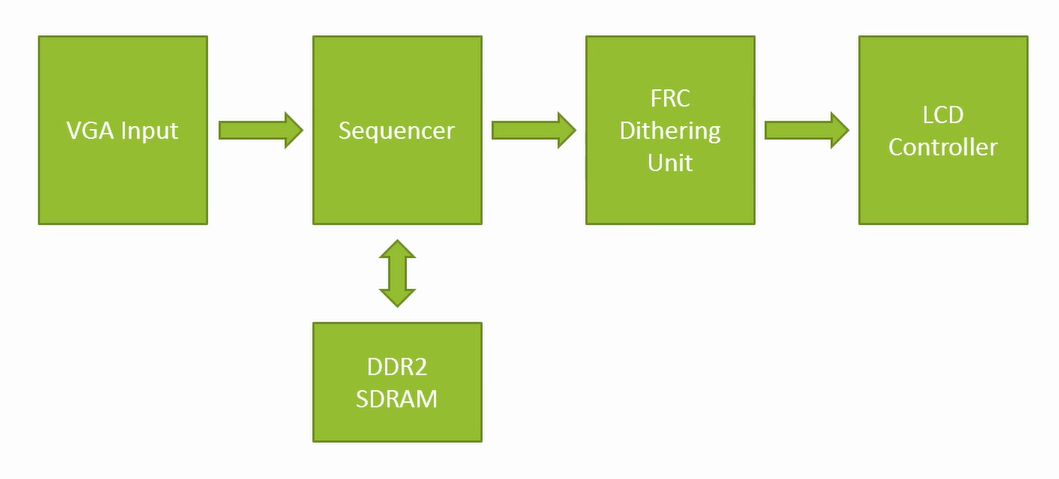

最初の2つのポイントは、フレームバッファが必要であることを意味し、単純なものではなく、2ポートのものが必要です。 さて、3番目のタスクはGLDP LUT(グレースケールレベルの表示パターンルックアップテーブル)[3]を使用して解決されます。 ルックアップテーブルには、表示する色とフレームカウンターの状態の2種類の入力があります。 そして、1種類の出力:特定の瞬間に特定のピクセルのサブピクセルに送信する必要がある3ビット。 そのため、次のノードが必要です。

最初に行うことは、画面全体を何らかの色で塗りつぶすことです。 この段階では、どのピクセルがどこにあるかを知る必要はありません。ディスプレイモジュールがマトリックスに必要な波形を配信することを確認するだけで十分です。 FPGAに入力するためのコードはこちらです。

次に、明るさも不完全なものを引き出そうとします。 フリッカーを最小限に抑えるためにFRCルックアップテーブルを探します。 著者は、市松模様のピクセルに適用される2つのテーブルを思いつきました。 したがって、2つの隣接するピクセルごとに非同期でちらつきます。 コードはこちらです。

したがって、画像を表示するようにボードに「教え」ました。次に必要なのはフレームバッファです。 640x480および各色の5ビットで、ボリュームは約600キロバイトになります。 それほどではありませんが、FPGAではそれほどではありません。 まあ、ボードにはそれを制御するためのDDR2やザイリンクスMIGのようなRAMがあります。 読み取り用と書き込み用の2つのFIFOが実装されています。 アービターは、DDR2との次のデータ交換が読み取りか書き込みかを決定します。 バッファは2つあり、レコードは1つに移動し、他のバッファから読み取ります。フレームを変更すると、場所が変更されます。 調停者コードはこちらです。

ビデオキャプチャの実装は引き続き行われます。以前のプロジェクトの1つでは、作成者が既に同様の操作時間を持っていますが、改良後、VGAからDPIへのコンバーターのコードはこのようになりました 。

そして何が起こったのですか?

見て!

これは著者にとって3番目のFPGAプロジェクトです。ザイリンクスのMIGとDDR2、および単純なコンベアを使用することは興味深いものでした。 デルタシグマ変調によるより良いFRCが計画されているほか、シャープのHPA(High Performance Addressing)テクノロジーを使用した後のCSTNパネルの実験も計画されています。

ご清聴ありがとうございました!

ソース

1. Li、W.、&Guo、Q.(2000)。 液晶ディスプレイ応用技術。 北京:電気産業プレス。

2.日立(1999)。 SX21V001-Z4お客様の受け入れ仕様。

3. Hsueh、Y.、&Lee、J.(2008)。 LCDフレームレートコントローラーの画像改善方法。 2008 IEEE国際コンシューマーエレクトロニクスに関するシンポジウム。 土井:10.1109 / isce.2008.4559534