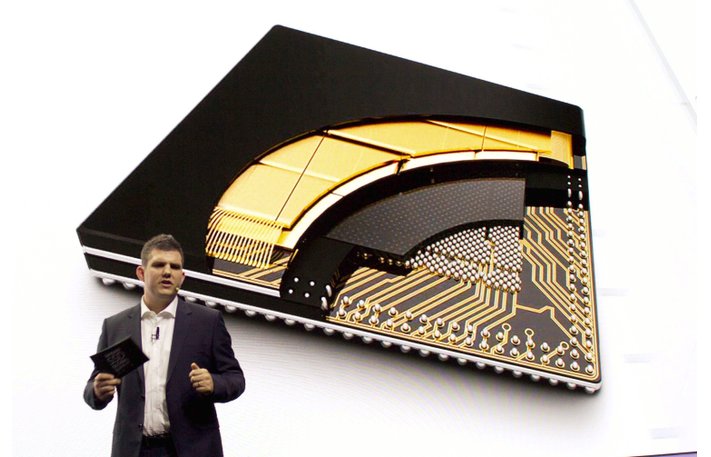

Intel Foveros 3D

ムーアの法則は適用されなくなったため、チップ設計者はパフォーマンスを改善する他の方法を探す必要があります。 これに適した技術の1つは、3Dチップスタッキングと呼ばれます。 これはチップの3次元スタックアーキテクチャであり、その開発においてIntelはリーダーです。 2か月前、インテルはFoveros 3Dアーキテクチャを導入しました :10nm CPU、I / Oチップ、チップの中央にあるTSV(Through Silicon Via)垂直電気接続、およびチップ全体のメモリチップを含む3次元構造です。

ライスオイルアンドガスHPC高性能コンピューティング会議で、AMD は自社バージョンの3Dチップアーキテクチャで作業していることを確認しました。

シニアバイスプレジデント兼ゼネラルマネージャーであるフォレストノロッドは、ムーアの法則の終了と、トランジスタ密度とクロック周波数の成長を停止する結果に関連する問題を回避し、リターンを増やすいくつかの技術を開発していると述べました。 これらは、トランジスタのサイズがほんの数原子(シリコン原子のサイズは0.2ナノメートル)である限界に近づいている製造業者の避けられない結果です。 近年のコンピューターの処理能力の向上は、計算速度の向上によるものではなく、並列性の向上によるものです。

他の企業と同様に、AMDは約700mm²のチップ面積の制限に直面しており、3Dアーキテクチャの開発を余儀なくされています。 同社はすでにこのアプローチを採用しており、HBM2メモリをGPU基板の隣に配置しています。つまり、プロセッサと同じケースです。 しかし、将来的には、より高度な3Dスタッキングに移行する予定です。

Norrodは、AMDがSRAMとDRAMをコンピューティングコンポーネント(プロセッサやGPUなど)の上に直接配置して、さらに多くの帯域幅とパフォーマンスを提供することに取り組んでいると述べました。

サムスンポラリス

このアプローチは、NorrodがSamsung Polarisチップを例として使用して示したように、2つの完成したケースを単純に重ねる通常のパッケージオンパッケージ(PoP)実装とは異なります。 この例では、DRAMエンクロージャーは、ベースチップを囲むBGAコネクタの追加の2行を介して接続されています。 これらのBGAコネクタは、2つのチップ間でデータを送信します。 他の標準設計と同様に、ロジックはスタックの一番下にありますが、これはコネクタを追加する必要があるためですが、2つのクリスタルは直接接続されていません。 したがって、PoPアプローチは最大密度を提供しますが、これは最速のオプションではありません。

真の3Dスタッキングでは、2つのチップ(この場合はメモリとプロセッサ)が上下に配置され、それらを直接インターフェースする垂直TSV接続によって接続されます。 これらのTSV接続は、可能な限り最高の速度でクリスタル間でデータを転送し、Intel Foveros 3Dで見たように、通常はチップの中央に配置されます。 この直接ペアリングにより、生産性が向上し、消費電力が削減されます(すべてのデータ移動には電力が必要ですが、直接接続するとプロセスが最適化されます)。 3Dスタッキングも密度を高めます。

Norrodは開発中のプロジェクトの詳細には触れませんでしたが、これはAMDプロセッサの設計における根本的な変化である可能性があります。

新しいIntel Foveros 3Dテクノロジーは、業界にとって決定的な瞬間になる可能性があるため、AMDがこの方向に進んでいると聞いても驚くことではありません。

これまでのところ、AMDの3Dスタッキングテクノロジーに関する技術的な詳細はありませんが、Forrest Norrodが「ムーアの法則を超える作業」と呼ばれるプレゼンテーションで述べたこと以外は、以下のビデオを参照してください。

Gordon Mooreによって予測された指数関数的成長曲線に戻るために、他にどのような選択肢がありますか? この質問に対する単一の答えはありません。 半導体産業は、シリコンの代わりに使用できる材料を実験しています。 一部のIII-V半導体材料は、シリコンよりも低い電圧と高い周波数で動作することができますが、原子を小さくしたり遅くしたりすることはありません。 物理的な制限は引き続き適用されます。

問題は、将来の3Dチップがいかにクールになるかということです。 エネルギーがチップ全体に分散しているときに、そのようなチップを効果的に冷却する方法は? マイクロ回路は、過熱せずにすべての回路に同時に電力を伝達することはできません。 彼女はおそらく、ほとんどの場合、一部の部品を切断したままにし、使用中は各部品にのみ電力を供給する必要があります。