前回は、ソフトウェアからファームウェアレベルまで部分的に削除された、ステッピングモーター用のパルスを生成するオプションを検討しました。 完全に成功した場合、これにより、最大40 KHzの周波数で到着する割り込みを処理する必要がなくなります。 しかし、このオプションにはいくつかの明らかな欠陥があります。 まず、加速はサポートされていません。 次に、そのソリューションの許容ステップ周波数の粒度は数百ヘルツです(たとえば、40,000 Hzと39966 Hzの周波数を生成することは可能ですが、これら2つの値の間の大きさの周波数を生成することは不可能です)。

高速化の実装

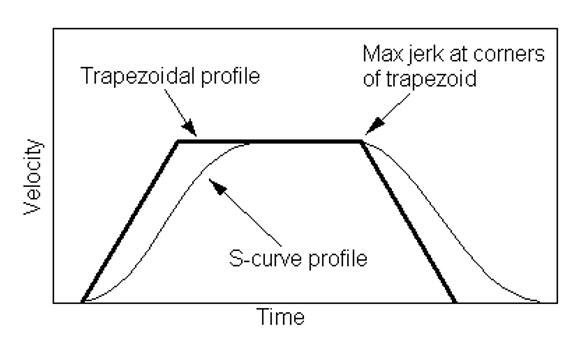

システムを複雑にすることなく、同じUDBツールを使用してこれらの欠点を排除することは可能ですか? 正しくしましょう。 最も困難なものから始めましょう-加速。 加速はパスの最初と最後に追加されます。 まず、ステッピングモーターに高周波パルスをすぐに印加すると、動作を開始するためにより大きな電流が必要になります。 高許容電流は加熱とノイズであるため、制限することをお勧めします。 ただし、エンジンは開始時にステップをスキップできます。 そのため、エンジンをスムーズに加速することをお勧めします。 第二に、重い頭が突然停止すると、慣性に関連した過渡現象が発生します。 プラスチックに波が見えます。 したがって、分散するだけでなく、頭を止めることもスムーズに必要です。 従来、エンジン速度のグラフは台形で表示されます。 以下は、Marlinファームウェアのソースコードの一部です。

UDBを使用してこれを実装することが可能かどうかを把握しようとはしません。 これは、別の種類の加速が現在流行しているという事実によるものです。台形ではなく、Sカーブです。 スケジュールは次のようになります。

これは間違いなくUDBには当てはまりません。 あきらめますか? まったくない! UDBにはハードウェアインターフェイスが実装されておらず、ソフトウェアのコードの一部をファームウェアレベルに転送するだけでよいことは既に説明しました。 プロファイルでCPUを計算すると、ステップパルスの形成によりUDBが実行されます。 中央処理装置は計算に多くの時間を費やしています。 頻繁な中断をなくすというタスクは引き続き非常に洗練されたものであり、ファームウェアレベルまでプロセスを完全に削除する予定はありません。

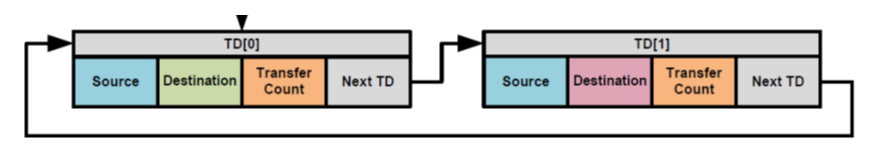

もちろん、プロファイルをメモリに準備する必要があり、UDBはDMAを使用してそこからデータを取得します。 しかし、どのくらいのメモリが必要ですか? 1ミリには200ステップが必要です。 24ビットエンコーディングでは、これは1 mmの頭の動きにつき600バイトです! 繰り返しになりますが、すべてをフラグメントで送信するために頻繁にではなく、常に中断することを覚えていますか? そうでもない! 実際、PSoCのDMAメカニズムは記述子に基づいています。 1つの記述子からタスクを実行すると、DMAコントローラーは次の記述子に進みます。 したがって、チェーンに沿って、多くの記述子を使用できます。 公式文書からのいくつかの図面でこれを説明します。

実際、このメカニズムは、3つの記述子のチェーンを構築することでも使用できます。

| いや | 解説 |

|---|---|

| 1 | メモリからFIFOにアドレス増分で。 加速プロファイルのあるセクションを示します。 |

| 2 | アドレスインクリメントなしでメモリからFIFOへ。 一定の速度のために、メモリ内の同じワードに常に送信します。 |

| 3 | メモリからFIFOにアドレス増分で。 ブレーキプロファイルのあるセクションを示します。

|

メインパスはステップ2で説明されており、物理的に同じ単語が使用され、一定の速度が設定されていることがわかります。 メモリ消費は大きくありません。 実際には、2番目または3つの記述子で2番目の記述子を物理的に表すことができます。 これは、TRMによると、最大ポンプ長が64キロバイトになる可能性があるためです(修正はより少なくなります)。 つまり、32,767ワードです。 1ミリメートルあたり200ステップの場合、163ミリメートルの経路に対応します。 エンジンが一度に移動できる最大距離に応じて、2つまたは3つの部分のセグメントを作成する必要がある場合があります。

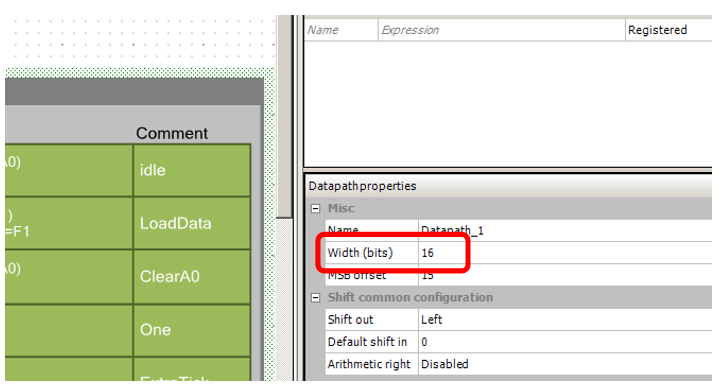

それでも、メモリ(およびUDBブロックの消費)を節約するために、24ビットのDatapPathブロックを放棄し、より経済的な16ビットのブロックに切り替えることを提案します。

だから。 改訂の最初の提案。

ステップの継続時間をエンコードする配列がメモリに準備されます。 さらに、この情報はDMAを使用してUDBに送信されます。 直線セクションは1つの要素の配列によってエンコードされ、DMAブロックはアドレスを増やしず、常に同じ要素を選択します。 加速、直線、および制動の各セクションは、DMAコントローラーで利用可能な手段によって接続されます。

ミッドレンジの微調整

ここで、周波数粒度の問題を克服する方法を検討します。 もちろん、正確に設定することはできません。 しかし、実際には、元の「ファームウェア」でもこれを行うことはできません。 代わりに、Bresenhamアルゴリズムを使用します。 一部のステップに1小節の遅延が追加されます。 その結果、平均周波数は、より小さな値とより大きな値の間の中間になります。 定期的期間と延長期間の比率を調整することにより、平均頻度をスムーズに変更できます。 速度がデータレジスタではなくFIFOを介して送信され、パルス数がDMAを介して送信されるワード数を介して設定される場合、UDBの両方のデータレジスタが解放されます。 さらに、パルス数をカウントするバッテリーの1つも解放されます。 ここでは、それらに特定のPWMを構築します。

通常、ALUは同じインデックスを持つレジスタを比較して割り当てます。 1つのレジスタのインデックスが0で、もう1つのレジスタのインデックスが1の場合、すべての操作オプションを実装できるわけではありません。 しかし、私はレジスタからソリティアをまとめ、PWMを実行することができました。 図のようになりました。

条件A0 <D1が満たされると、指定されたパルス長に追加のビートが追加されます。 条件が満たされない場合、我々はしません。

通常の状態での球状の馬

そのため、新しいアーキテクチャを考慮して、UDB用に開発されたブロックの変更を開始します。 データパスのビット深度を置き換えます。

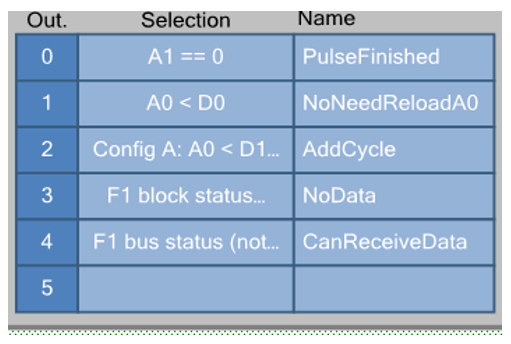

前回よりも多くのDatapathからの出口が必要になります。

それらをダブルクリックすると、詳細が表示されます。

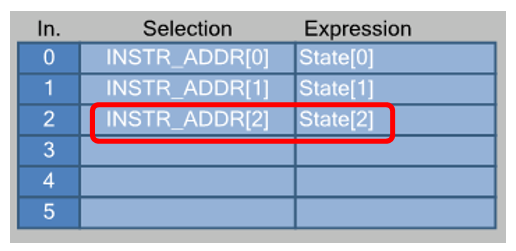

State変数にはさらに数字があります。古い数字を接続することを忘れないでください!!! 古いバージョンでは、定数0がありました。

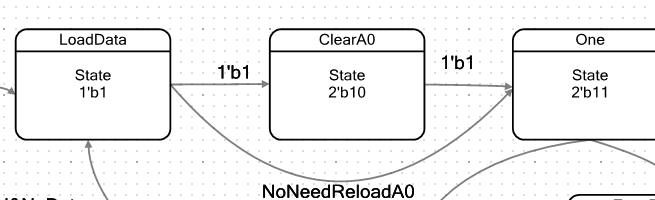

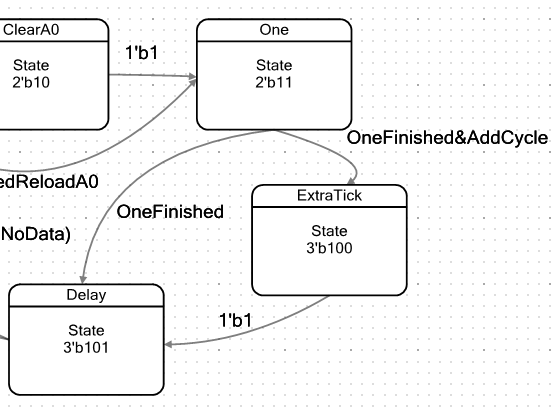

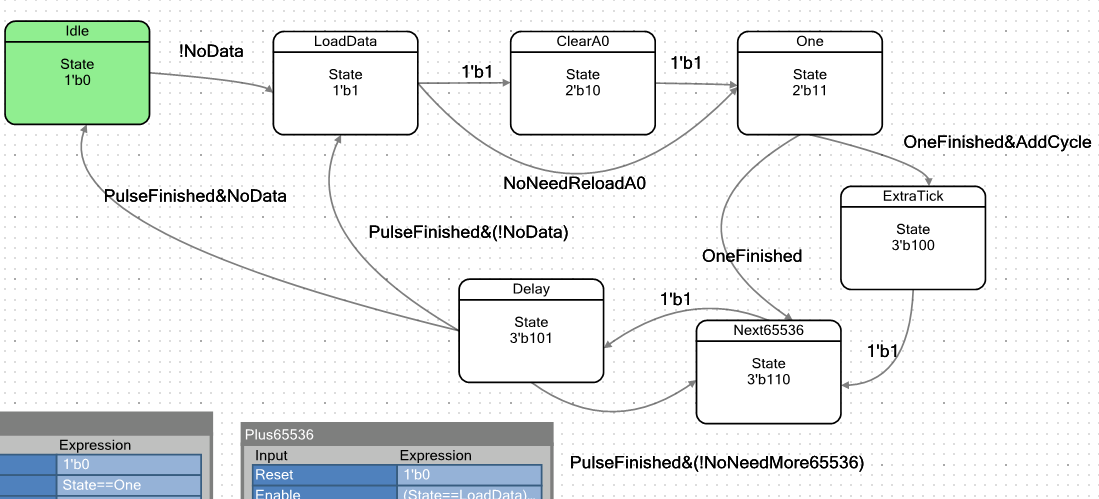

私がこのようになったオートマトンの遷移グラフ:

FIFO1が空の間、 アイドル状態になります。 ちなみに、FIFO0ではなくFIFO1で作業するのは、ソリティアがまさに形成された結果です。 レジスタA0はPWMの実装に使用されるため、パルス幅はレジスタA1によって決定されます。 そして、私はFIFO1からのみダウンロードできます(他の秘密の方法があるかもしれませんが、それらは私には知られていません)。 したがって、DMAはデータをFIFO1に正確にアップロードし、 アイドル状態を終了するのはFIFO1のまさに「空ではない」状態です。

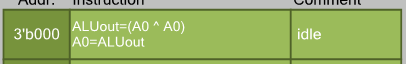

IDLE状態のALUはレジスタA0を無効にします。

これは、PWM動作の開始時に常に最初から作業を開始するために必要です。

しかし、データはFIFOに入りました。 マシンはLoadData状態になります。

この状態では、ALUは次のワードをFIFOからレジスタA1にロードします。 途中で、不必要な状態を作成しないために、PWMを操作するために使用されるカウンターA0の値が増加します。

カウンタA0がまだ値D0に達していない場合(つまり、条件A0 <D0がトリガーされ、NoNeedReloadA0フラグが設定されている場合)、 One状態に移行します。 それ以外の場合、 ClearA0状態になります。

ClearA0状態では、 ALUは単にA0の値をゼロにし、新しいPWMサイクルを開始します。

その後、マシンも1状態になり、1ビート後になります。

1つは、古いバージョンのマシンから私たちによく知られています。 その中のALUは機能を実行しません。

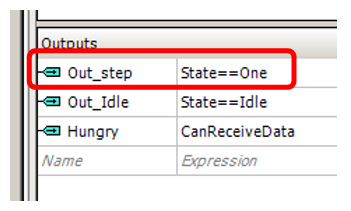

したがって、この状態では、 Out_Stepの出力でユニットが生成されます(ここでは、条件によってユニットが生成されたときにオプティマイザーがうまく機能し、これは経験的に検出されました)。

すでにわかっている7ビットカウンターがゼロにリセットされるまで、この状態になります。 しかし、以前に1つのパスに沿ってこの状態を抜けた場合、ビートへの直接パスと遅延パスの2つのパスが可能になります。

条件A0 <D1を満たすように割り当てられているAddCycleフラグが設定されている場合、ExtraTick状態になります。 この状態では、ALUは有益なアクションを実行しません。 サイクルが1ビート長くなるだけです。 さらに、すべてのパスは遅延状態で収束します。

この条件は、パルスの持続時間を測定します。 レジスタA1(ロード状態のままロードされる)は、ゼロに達するまで減少します。

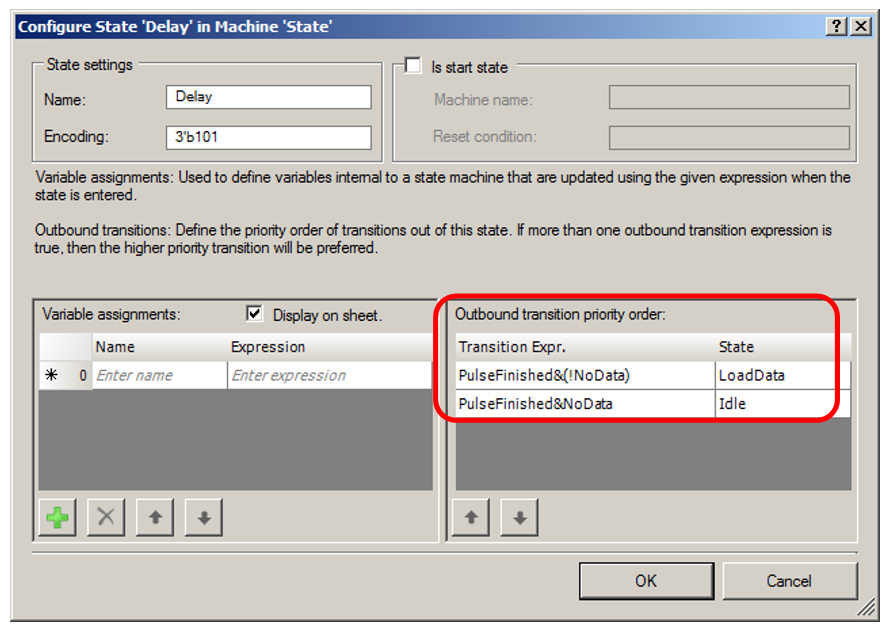

さらに、FIFOに追加データがあるかどうかに応じて、マシンはロード状態またはアイドル状態の次の部分のフェッチに切り替わります。 これは図ではなく(長い矢印があり、すべてが小さくなります)、テーブルの形で、 遅延状態をダブルクリックして見てみましょう:

UDBを終了します。 オプティマイザーが最良の結果を示したため、 アイドル状態のフラグを非同期比較に変換しました(以前のバージョンでは、さまざまな状態でトリガーおよびリセットされるトリガーがありました)。 さらに、 ハングリーフラグが追加され、データを受信する準備ができたことをDMAユニットに通知します。 「FIFO1は混雑していません」というフラグにまとめられています。 混雑していない場合、DMAは次のデータワードをそこにロードできます。

自動部分について-それだけです。

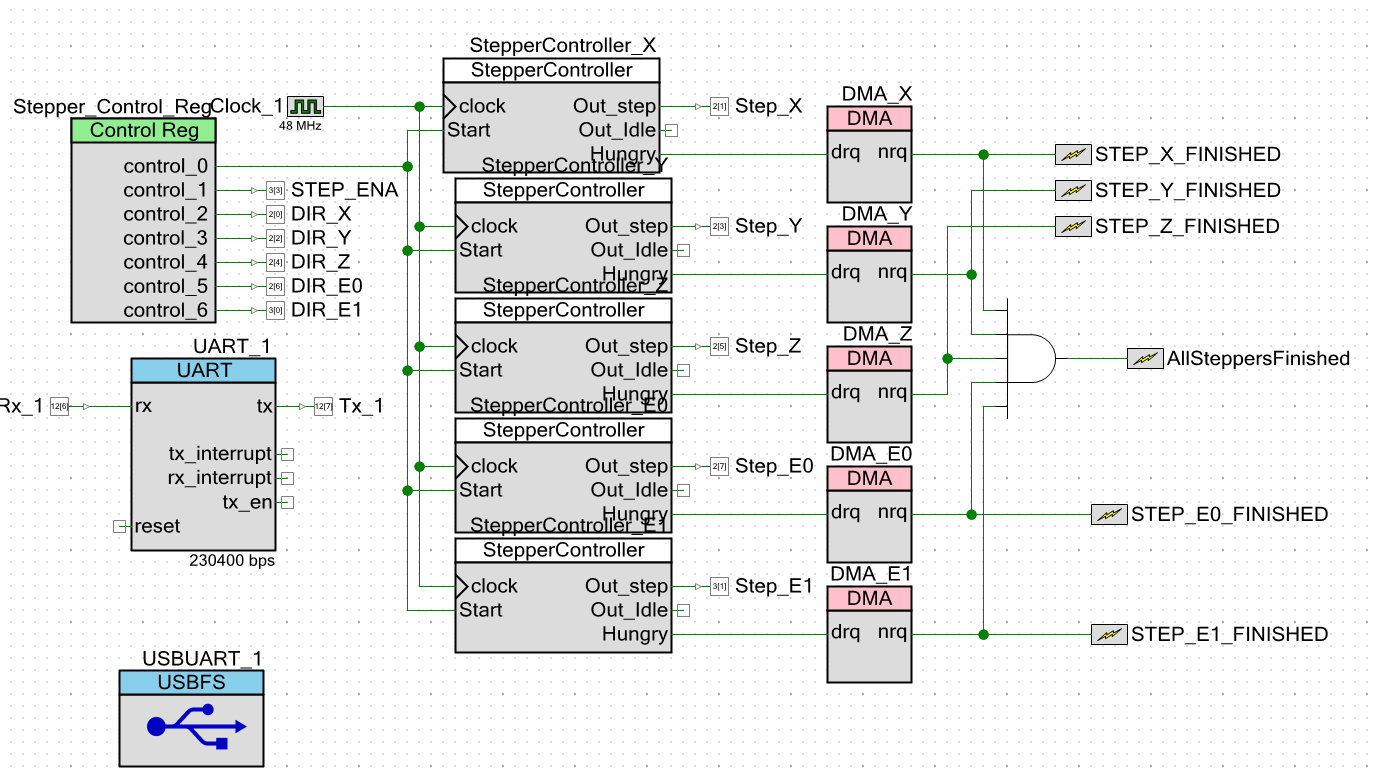

メインプロジェクト図にDMAブロックを追加します。 当分の間、DMA終了フラグの割り込みを開始しましたが、これが正しいという事実ではありません。 メモリへの直接アクセスのプロセスが完了すると、同じセグメントに関連する新しいプロセスを開始できますが、新しいセグメントに関する情報の入力を開始することはできません。 FIFOには、まだ3〜4個の要素があります。 現時点では、UDBに基づいてブロックのレジスタD0およびD1を再プログラムすることはまだ不可能です。これらは操作に必要です。 したがって、 Out_Idle出力に基づく割り込みが後で追加される可能性があります。 ただし、そのキッチンはUDBブロックプログラミングとは関係ないため、ここでは言及します。

ソフトウェア実験

今ではすべてがわかっていないので、特別な関数は作成しません。 すべてのチェックは「額に」実行されます。 次に、成功した実験に基づいて、API関数を作成できます。 だから。 main()関数を最小限にします。 彼女はシステムをセットアップし、選択したテストを呼び出します。

int main(void) { CyGlobalIntEnable; /* Enable global interrupts. */ // isr_1_StartEx(StepperFinished); StepperController_X_Start(); StepperController_Y_Start(); StepperController_Z_Start(); StepperController_E0_Start(); StepperController_E1_Start(); // TestShortSteps(); TestWithPacking (); for(;;) { }

関数を呼び出して、追加のパルスを挿入したことを確認して、パルスのパケットを送信してみましょう。 関数呼び出しは簡単です:

TestShortSteps();

しかし、体には説明が必要です。

最初に機能全体を提供します

void TestShortSteps() { // , // // , DMA !!! // , !!! StepperController_X_SingleVibrator_WritePeriod (6); // // — CY_SET_REG16(StepperController_X_Datapath_1_D0_PTR, 4); CY_SET_REG16(StepperController_X_Datapath_1_D1_PTR, 2); // . // static const uint16 steps[] = { 0x0001,0x0001,0x0001,0x0001,0x0001,0x0001,0x0001,0x0001,0x0001,0x0001, 0x0001,0x0001,0x0001,0x0001,0x0001,0x0001,0x0001,0x0001,0x0001,0x0001 }; // DMA , uint8 channel = DMA_X_DmaInitialize (sizeof(steps[0]),1,HI16(steps),HI16(StepperController_X_Datapath_1_F1_PTR)); CyDmaChRoundRobin (channel,true); // , uint8 td = CyDmaTdAllocate(); // . , . CyDmaTdSetConfiguration(td, sizeof(steps), CY_DMA_DISABLE_TD, TD_INC_SRC_ADR | TD_AUTO_EXEC_NEXT); // CyDmaTdSetAddress(td, LO16((uint32)steps), LO16((uint32)StepperController_X_Datapath_1_F1_PTR)); // CyDmaChSetInitialTd(channel, td); // CyDmaChEnable(channel, 1); }

次に、重要な部分を検討します。

パルスの正の部分の長さが92クロックサイクルに等しい場合、オシロスコープは負の部分にシングルサイクル挿入があるかどうかを識別できません。 スケールは同じではありません。 合計パルスが挿入されたビートとスケールで比較できるように、正の部分をできるだけ短くする必要があります。 したがって、パルスの正の部分の持続時間を設定するカウンターの周期を強制的に変更します。

// , // // , DMA !!! // , !!! StepperController_X_SingleVibrator_WritePeriod (6);

しかし、なぜ6つの全体的な対策があるのでしょうか? なぜ3つではないのですか? なぜ2つではないのですか? 結局のところ、1つではないのはなぜですか? これは悲しい話です。 正のパルスが6サイクルより短い場合、システムは機能しません。 テストラインを外部に出力するオシロスコープでの長時間のデバッグでは、DMAは高速ではないことが示されました。 マシンが一定の時間より短い時間動作している場合、 遅延状態から抜け出すまでに、FIFOはほとんどの場合空のままです。 まだ1つの新しいデータワードが配置されていない可能性があります。 そして、パルスの正の部分の持続時間が6サイクルである場合にのみ、FIFOはロードする時間があることが保証されます...

遅延脱線

私の頭の中にある別の修正案は、RTOS MAXのカーネルの特定の機能のハードウェアアクセラレーションです。 しかし、悲しいかな、それらの同じレイテンシーに関する私の最高のアイデアはすべて壊れています。

ケースがあり、Cyclone V SoCのベアメタルアプリケーションの開発を研究しました。 しかし、単一のFPGAレジスタを使用して(交互に書き込み、読み取りを行う)場合、コアの作業が数百(!!!)回削減されることがわかりました。 あなたは正しく聞いた。 それは数百単位です。 さらに、これらはすべて不十分に文書化されていますが、最初は内に感じて、文書のフレーズの断片から、リクエストを多数の橋を通過させるときに遅延が有罪であることを証明しました。 大きなアレイをドライブアウトする必要がある場合、レイテンシーも発生しますが、1つのポンプされたワードに関しては重要ではありません。 要求が単一の場合(およびOSカーネルのハードウェアアクセラレーションはそれらだけを意味します)、スローダウンは正確に数百回進みます。 プログラムが途方もない速度でキャッシュを介してメインメモリを操作する場合、純粋にプログラム的な方法ですべてを実行する方がはるかに高速です。

PSoCでは、特定の計画もありました。 外観では、DMAとUDBを使用して、配列内のデータを驚くほど探すことができます。 本当にそこにあるもの! DMA記述子構造により、これらのコントローラーはリンクリストで完全にハードウェア検索を実行できます。 しかし、上記のプラグを受け取った後、私はそれがレイテンシーにも関連していることに気付きました。 ここで、このレイテンシはドキュメントに詳しく説明されています。 ファミリTRMおよび別のドキュメントAN84810-PSoC 3およびPSoC 5LP Advanced DMA Topicsの両方 。 そこにはセクション3.2があります。 したがって、次のハードウェアアクセラレーションはキャンセルされます。 残念。 しかし、Semyon Semyonovich Gorbunkovが言ったように:「我々は検索します。」

継続的なソフトウェア実験

次に、ブレゼンハムアルゴリズムのパラメーターを設定します。

// // — CY_SET_REG16(StepperController_X_Datapath_1_D0_PTR, 4); CY_SET_REG16(StepperController_X_Datapath_1_D1_PTR, 2);

それから、DMAを介してエンジンコントロールユニットXのFIFO1にワードの配列を転送する通常のコードがあります。

結果には説明が必要です。 ここにあります:

マシンがOne状態の場合、カウンターA0の値は赤で表示されます。 緑色のアスタリスクは、マシンがExtraTick状態にあるために遅延が挿入された場合を示しています。 また、 ClearA0状態にあるために遅延が発生するバーもあり、それらは青いグリッドでマークされています。

ご覧のとおり、最初に入力すると最初の遅延は失われます。 これは、A0がアイドル状態のときにリセットされるが、 LoadDataに入ると増加するためです 。 したがって、分析の時点まで( Oneの状態からの出口)、それはすでに単一に等しいです。 アカウントは彼女から始まります。 しかし、一般的に、これは中間周波数に影響しません。 念頭に置いておく必要があります。 A0をリセットすると、メジャーも挿入されることに注意してください。 平均頻度を計算するときは、これを考慮する必要があります。

しかし、一般的に、パルスの数は正しいです。 その期間も信じられます。

より現実的な記述子のチェーンをプログラムしてみましょう。

加速、直線運動、ブレーキングのフェーズで構成されます。

void TestWithPacking(int countOnLinearStage) { // , // . // , DMA !!! // , !!! StepperController_X_SingleVibrator_WritePeriod (6); // // — CY_SET_REG16(StepperController_X_Datapath_1_D0_PTR, 4); CY_SET_REG16(StepperController_X_Datapath_1_D1_PTR, 2); // static const uint16 accelerate[] = {0x0010,0x0008,0x0004}; // static const uint16 deccelerate[] = {0x004,0x0008,0x0010}; // . . static const uint16 steps[] = {0x0001}; // DMA , uint8 channel = DMA_X_DmaInitialize (sizeof(steps[0]),1,HI16(steps),HI16(StepperController_X_Datapath_1_F1_PTR)); CyDmaChRoundRobin (channel,true); // uint8 tdDeccelerate = CyDmaTdAllocate(); CyDmaTdSetConfiguration(tdDeccelerate, sizeof(deccelerate), CY_DMA_DISABLE_TD, TD_INC_SRC_ADR | TD_AUTO_EXEC_NEXT); CyDmaTdSetAddress(tdDeccelerate, LO16((uint32)deccelerate), LO16((uint32)StepperController_X_Datapath_1_F1_PTR)); // uint8 tdSteps = CyDmaTdAllocate(); // !!! // !!! CyDmaTdSetConfiguration(tdSteps, countOnLinearStage, tdDeccelerate, /*TD_INC_SRC_ADR |*/ TD_AUTO_EXEC_NEXT); CyDmaTdSetAddress(tdSteps, LO16((uint32)steps), LO16((uint32)StepperController_X_Datapath_1_F1_PTR)); // // !!! uint8 tdAccelerate = CyDmaTdAllocate(); CyDmaTdSetConfiguration(tdAccelerate, sizeof(accelerate), tdSteps, TD_INC_SRC_ADR | TD_AUTO_EXEC_NEXT); CyDmaTdSetAddress(tdAccelerate, LO16((uint32)accelerate), LO16((uint32)StepperController_X_Datapath_1_F1_PTR)); // CyDmaChSetInitialTd(channel, tdAccelerate); // CyDmaChEnable(channel, 1); }

まず、同じ10ステップを呼び出します(DMAでは、実際には20バイトがなくなります)。

TestWithPacking (20);

結果は期待どおりです。 最初は加速が見えます。 そして、 IDLE (青線)への出口は、最後のパルスからの大きな遅延で発生し、最後のステップが完全に完了し、その値は最初の値にほぼ等しくなります。

通常の条件下での本物の馬

機器を改造するとき、私はどういうわけか24ビットのパルス幅から16ビットのジョブにジャンプしたことが有名です。 しかし、これができないことがわかりました。最小パルス周波数が高すぎることになります。 意図的にやった。 事実、16ビットカウンターのビット容量を拡張する手法は非常に複雑であることが判明したため、メインマシンと一緒に説明し始めた場合、すべての注意をそらすことになります。 したがって、個別に検討します。

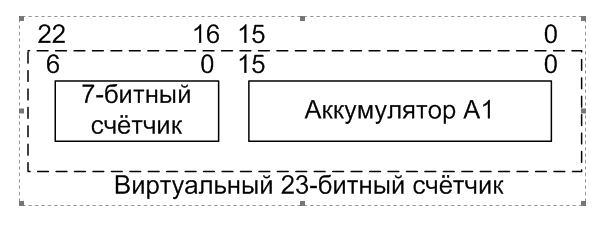

16ビットのバッテリーがあります。 上位ビットに通常の7ビットカウンターを追加することにしました。 この7ビットカウンターとは何ですか? これは、各UDBブロックで使用可能な設計です(ベースUDBブロックはすべての8ビットレジスタのビット幅を持ち、ビット深度の増加はグループ内のブロックの組み合わせによって決まります)。 同じリソースのうち、 制御/ステータスレジスタを実装できます。 これで、単一のControl / Statusペアではなく、16ビットのデータに対して1つのカウンターができました。 そのため、システムに別のカウンターを追加しても、余分なリソースは遅延しません。 すでに割り当てられているものを使用します。 いいね! このメカニズムによりパルス幅カウンターの上位バイトを作成し、23ビットに等しいパルス幅カウンターの合計幅を取得します。

最初に私が考えていたことを言います。 遅延状態を終了した後、この追加カウンターのカウントの完了を確認すると思いました。 彼がカウントを終了していない場合、その値を減らし、再び遅延状態に切り替えます。 カウントすると、余分なサイクルを追加することなく、ロジックは同じままになります。

さらに、このカウンターのドキュメントには、私が正しいと書かれています。 文字通り言う:

期間人生はすべてが異なっていることを示しています。 オシロスコープのターミナルカウントラインの状態を推測し、 期間およびプログラムのロード中に、プリロードされたゼロでその値を監視しました。 ああ、ああ。 常に高い状態はありませんでした!

初期期間レジスタ値を定義します。 Nクロックの期間では、期間値はN-1の値に設定する必要があります。 カウンタはN-1から0までカウントし、Nクロックサイクル期間になります。 期間レジスタ値0はサポートされていないため、ターミナルカウント出力は一定のHigh状態に保持されます。

試行錯誤によって、システムを正常に機能させることができましたが、これを実現するには、カウンターから少なくとも1回減算する必要があります。 「減算」の新しい状態は側にありません。 必要なパスに押し込まれなければなりませんでした。 遅延状態の前にあり、 Next65536と呼ばれます 。

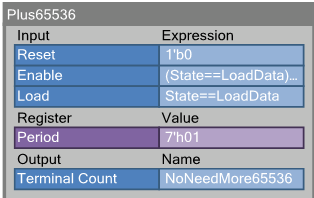

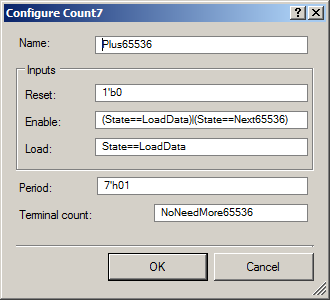

この状態のALUは、有用なアクションを実行しません。 実際、この状態にあるという事実に反応するのは新しいカウンターだけです。 これは図にあります:

プロパティの詳細は次のとおりです。

一般に、以前の記事を考慮すると、このカウンターの本質は明らかです。 有効になっている行のみが影響を受けています。 繰り返しになりますが、マシンがLoadData状態にあるときにオンにする必要がある理由を完全には理解していません(カウンターが周期値を再読み込みします)。 私は、LEDを制御するカウンターのプロパティから、このLEDのコントロールユニットの英国の著者からこのトリックを借りました。 これがないと、期間のゼロ値は機能しません。 彼女は彼女と一緒に働いています。

APIコードに、新しいカウンターの初期化を追加します。 開始関数は次のようになります。

void `$INSTANCE_NAME`_Start() { `$INSTANCE_NAME`_SingleVibrator_Start(); //"One" Generator start `$INSTANCE_NAME`_Plus65536_Start(); }

新しいシステムをチェックしてみましょう。 テスト用の機能コードは次のとおりです

(その中で、最初の行のみが既知の行と異なります):

void JustTest(int extra65536s) { // 65536 StepperController_X_Plus65536_WritePeriod((uint8) extra65536s); // // — CY_SET_REG16(StepperController_X_Datapath_1_D0_PTR, 4); CY_SET_REG16(StepperController_X_Datapath_1_D1_PTR, 2); // . // static const uint16 steps[] = { 0x1000,0x1000,0x1000,0x1000 }; // DMA , uint8 channel = DMA_X_DmaInitialize (sizeof(steps[0]),1,HI16(steps),HI16(StepperController_X_Datapath_1_F1_PTR)); CyDmaChRoundRobin (channel,true); // , uint8 td = CyDmaTdAllocate(); // . , . CyDmaTdSetConfiguration(td, sizeof(steps), CY_DMA_DISABLE_TD, TD_INC_SRC_ADR | TD_AUTO_EXEC_NEXT); // CyDmaTdSetAddress(td, LO16((uint32)steps), LO16((uint32)StepperController_X_Datapath_1_F1_PTR)); // CyDmaChSetInitialTd(channel, td); // CyDmaChEnable(channel, 1); }

次のように呼び出します。

JustTest(0);

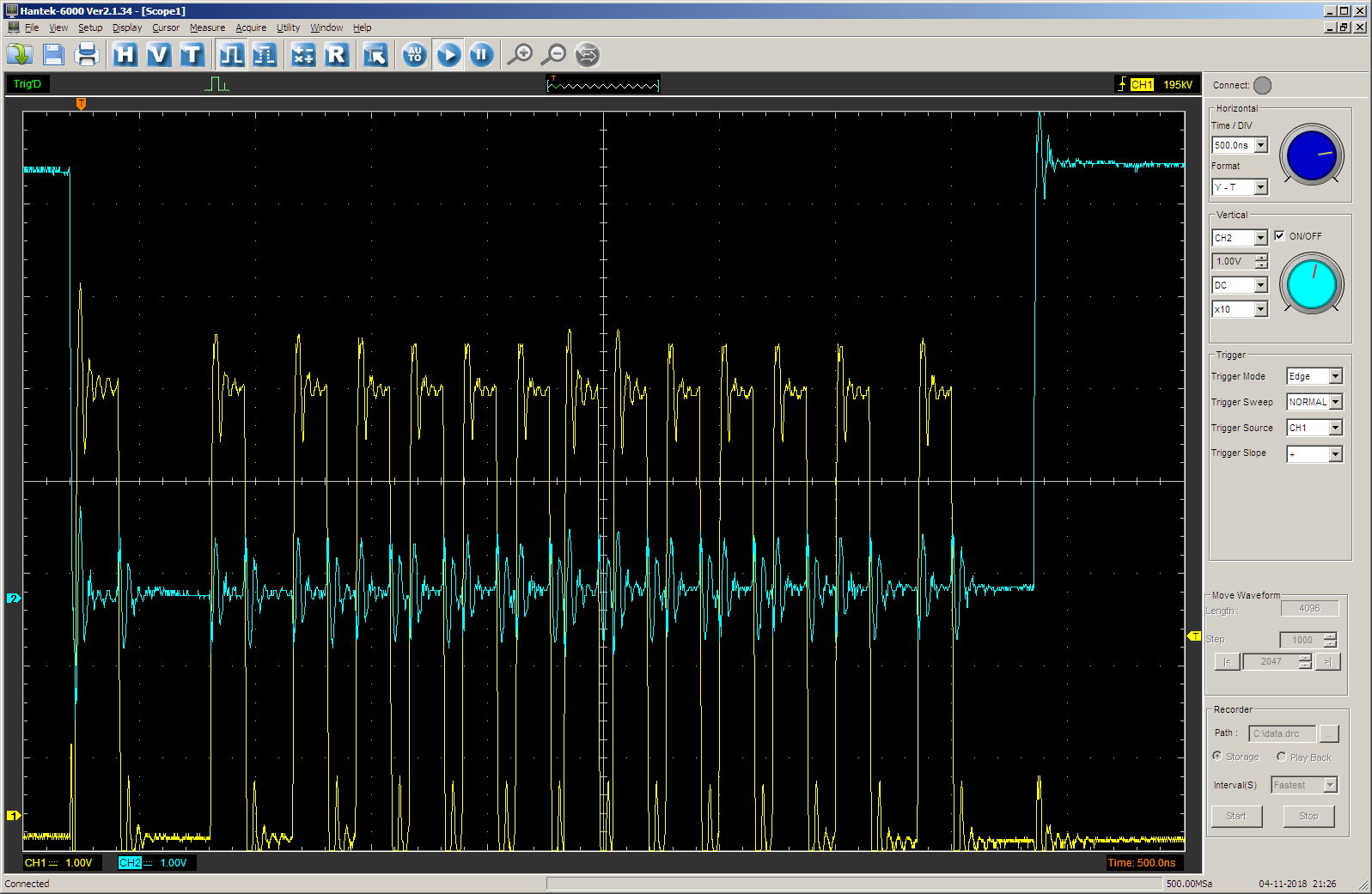

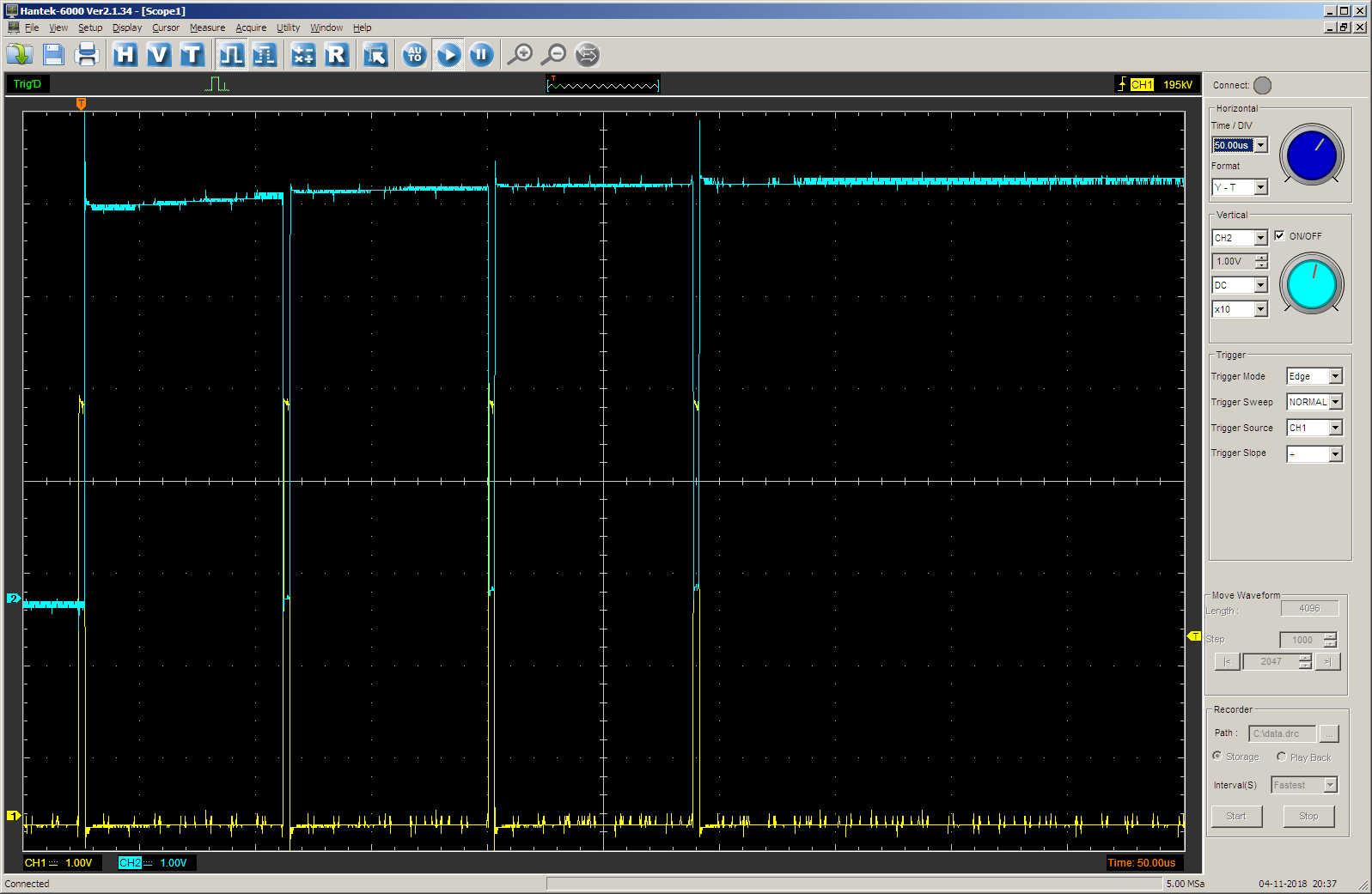

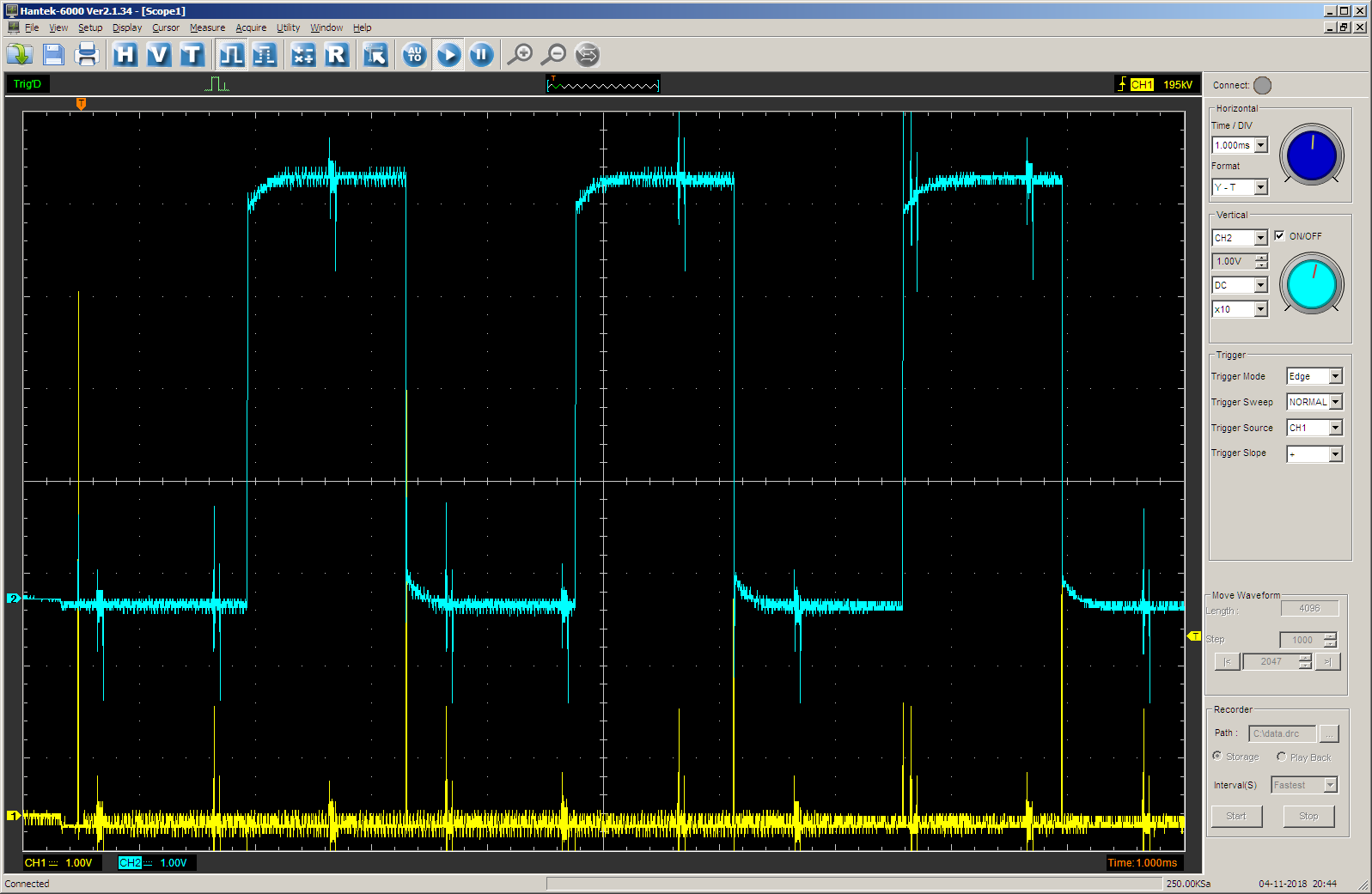

オシロスコープでは、次のように表示されます(黄色のビーム-STEP出力、青色-プロセス制御用のカウンターTC出力の値)。 パルス幅はステップ配列によって設定されます 。 各ステップで、期間は0x1000メジャーです。

別の結果に互換性があるように、別のスキャンに切り替えます。

関数呼び出しをこれに変更します。

JustTest(1);

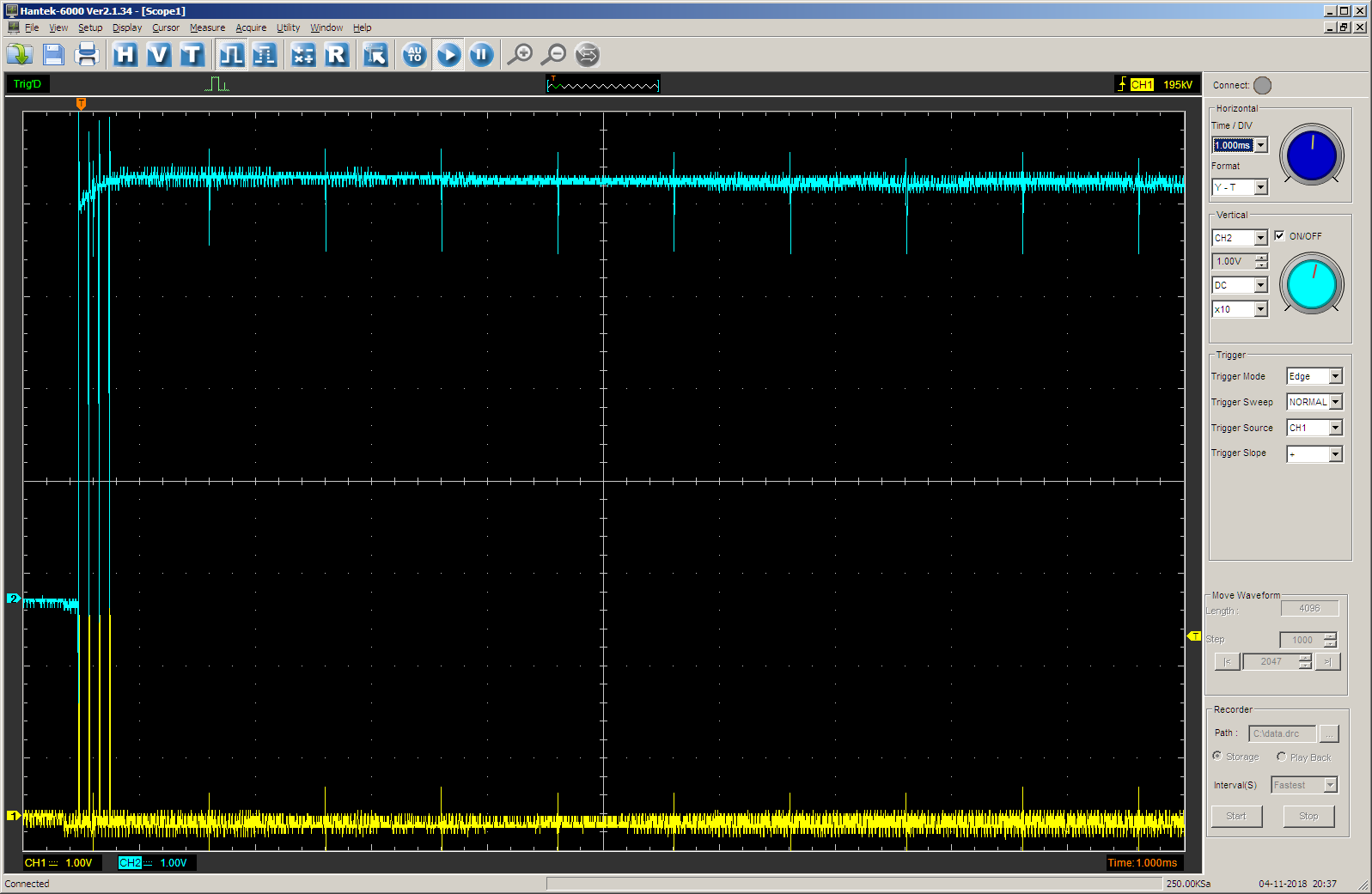

結果は期待どおりです。 まず、TC出力は0x1000ティックではゼロ、次に0x10000(65536d)ティックの単位です。 周波数はおおよそ700ヘルツに等しいので、記事の最後の部分でわかったので、すべてが正しいです。

さて、デュースを試してみましょう:

JustTest(2);

取得するもの:

そうです。 TC出力は、最後の65536クロックサイクルで1に反転します。 その前に、彼は0x1000 + 0x10000クロックサイクルの間ゼロでした。

もちろん、このアプローチでは、すべてのパルスは新しいカウンターの同じ値で行く必要があります。 加速中に最高バイト、たとえば3、1、0で1つのパルスを作成することは不可能です。しかし、実際、そのような低周波数(700ヘルツ未満)では、加速には物理的な意味がないため、この問題は無視できます。 この頻度で、エンジンを直線的に操作できます。

軟膏で飛ぶ

PSoC5LPファミリのTRMドキュメントには次のように記載されています。

各トランザクションは1〜64 KBです。しかし、すでに述べたAN84810には、次のようなフレーズがあります。

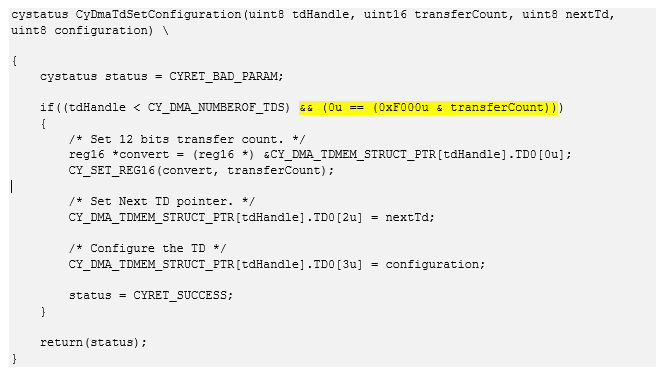

1. DMAを使用して4095バイト以上をバッファするにはどうすればよいですか?誰が正しい? 実験を行う場合、結果は最悪のステートメントを支持する傾向がありますが、動作は完全に理解できません。 全体の欠点は、APIのこのチェックです:

TDの最大転送カウントは4095バイトに制限されています。 単一のDMAチャネルを使用して4095バイト以上を転送する必要がある場合は、複数のTDを使用し、例5に示すようにそれらをチェーンします。

同じテキスト。

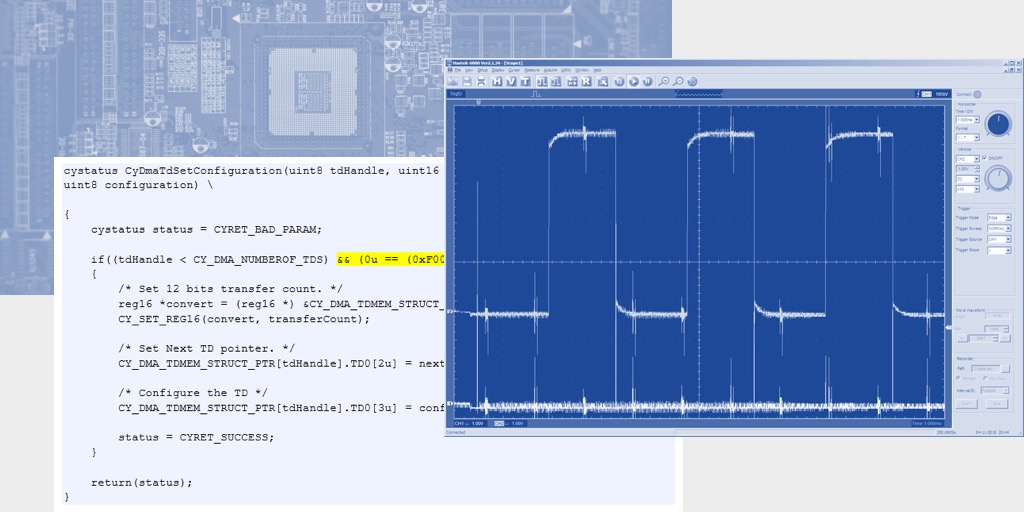

cystatus CyDmaTdSetConfiguration(uint8 tdHandle, uint16 transferCount, uint8 nextTd, uint8 configuration) \ { cystatus status = CYRET_BAD_PARAM; if((tdHandle < CY_DMA_NUMBEROF_TDS) && (0u == (0xF000u & transferCount))) { /* Set 12 bits transfer count. */ reg16 *convert = (reg16 *) &CY_DMA_TDMEM_STRUCT_PTR[tdHandle].TD0[0u]; CY_SET_REG16(convert, transferCount); /* Set Next TD pointer. */ CY_DMA_TDMEM_STRUCT_PTR[tdHandle].TD0[2u] = nextTd; /* Configure the TD */ CY_DMA_TDMEM_STRUCT_PTR[tdHandle].TD0[3u] = configuration; status = CYRET_SUCCESS; } return(status); }

トランザクションが4095バイトより長く指定されている場合、前の設定が使用されます。 はい、エラーコードをチェックすることを考えていませんでした...

実験では、このチェックを削除すると、マスク0xfff(4096= 0x1000)を使用して実際の長さが切り捨てられることが示されました。 ああ、ああ。 楽しい仕事へのすべての希望は崩壊した。 もちろん、4Kで関連する記述子のチェーンを作成できます。 しかし、64Kは16チェーンです。 3つのアクティブエンジン(押出機のステップが少なくなります)-48チェーン。 最悪の場合、各セグメントの前に正確に多くの情報を入力する必要があります。 おそらくそれは時間内に受け入れられます。 少なくとも127個の記述子が使用可能であるため、確実に十分なメモリがあります。

必要に応じて不足データを送信できます。 DMAチャネルが作業を完了したという割り込みが発生し、別のセグメントを転送しています。 この場合、計算は不要で、セグメントはすでに形成されているため、すべてが高速になります。 また、パフォーマンス要件はありません。割り込み要求が発行されると、FIFOにはさらに数百または数千のクロックサイクルでサービスされる要素が4つ追加されます。 つまり、すべてが本物です。 特定の戦略は、実際の作業中に選択しやすくなります。 しかし、ドキュメンテーション(TRM)の誤りが気分全体を台無しにしました。 これが前もってわかっていれば、方法論をチェックしなかっただろう。

おわりに

外観では、開発された補助ファームウェアツールが受け入れられるようになったため、ステッピングモーターの割り込みハンドラーに常に存在しない「ファームウェア」、たとえばMarlinのバージョンを作成できるようになりました。 私の知る限り、これは特にコンピューティングリソースの需要が非常に高いデルタプリンターに当てはまります。 おそらくこれは、頭が止まる場所で私のデルタに発生する流入を排除します。 これらの同じ場所のMZ3Dでは、流入は観察されません。 真実かどうかにかかわらず、時間が経てばわかるので、これに関するレポートは完全に異なるブランチに投稿する必要があります。

それまでの間、UDBブロックでは、その単純化のために、メインプロセッサと連携して動作し、アンロードできるコプロセッサを実装することが非常に可能です。 そして、これらのユニットが多数ある場合、コプロセッサーは並行して動作できます。

DMAコントローラーのドキュメントのエラーにより、結果がぼやけています。 それにも関わらず、中断は必要ですが、同じ頻度ではなく、元のバージョンにあった時間的な重要性もありません。 したがって、ムードは損なわれますが、UDBに基づく「コプロセッサー」の使用は、純粋なソフトウェア作業と比較して、かなりの利益をもたらします。

途中で、DMAがかなり低速で動作することが明らかになりました。 この結果、PSoC5LPとSTM32の両方でいくつかの測定が実行されました。 結果は別の記事を引き出します。 トピックが興味深い場合、おそらくいつかそれを行うでしょう。

実験の結果、2つのテストプロジェクトが同時に取得されました。 最初の方が理解しやすいです。 ここで取ることができます 。 2番目は1番目から継承されますが、7ビットカウンターと関連するロジックを追加すると混乱します。 ここで取ることができます 。 もちろん、これらの例はテスト用です。 本当の「ファームウェア」に組み込む自由な時間はまだありません。 しかし、これらの記事の枠組みの中で、UDBとの連携を実践することがより重要です。