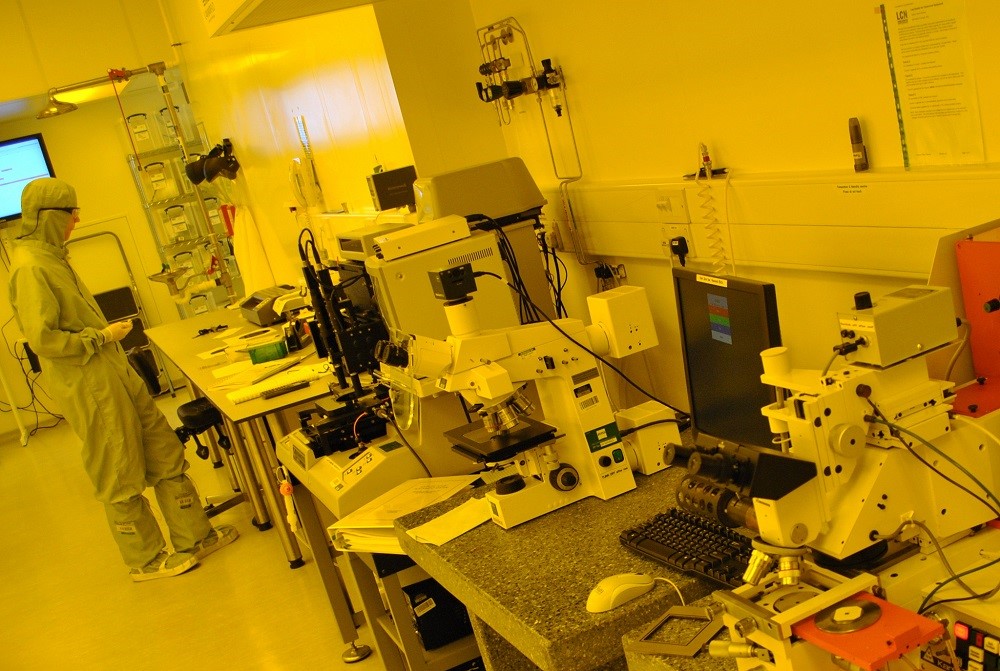

/写真UCL CC

7nm TSMCプロセス技術

月の初めにTSMCが印刷したチップは、第2世代の7nmプロセステクノロジに基づいており、前世代と比較して多くの変更が加えられています。

第1世代TSMCの7 nmプロセステクノロジーは、「深部」紫外線放射によるDUVリソグラフィに基づいています。 この場合、液浸リソグラフィと波長193 nmのスキャナーが使用されます。 同社のこのテクノロジーの最初のチップは、今年の4月に印刷されました。 また、5月にTSMC は Apple向けに7nmチップの生産を開始しました。 A12 Bionicチップシステムには新しいチップが付属していました。 彼女はすでにITの巨人であるiPhone XR、XS、XS Maxの最新スマートフォンの仕事を担当しています。

合計で、Bitmain、NVIDIA、およびQualcommを含む20の企業から注文が寄せられています。 AMDはTSMCの主要クライアントでもあります。Vega20プロセッサとEpycサーバーCPUは、7 nmプロセステクノロジーに基づいて構築されています。

今月初め、TSMCは、7nmプロセステクノロジーを改善できたと報告しました。 エンジニアは、「ハード」紫外線( EUV )でフォトリソグラフィを使用してチップを開発しました。 この場合、波長は20倍短く、13.5 nmです。 EUVに切り替えると(欠陥やその他のプロセスのモデリングおよび検出方法の開発とともに)、製造された超小型回路の消費電力が8% 削減され、トランジスターの密度が20%向上しました。

これまでのところ、チップの4つの重要ではない層のみがEUVで実装されています。 まず、技術を習得し、それを大量の製品の製造に使用したいと考えています(一方、適切なデバイスの出力は非常に低いです)。

メーカーは、誰が新しいチップを最初に受け取ったのかを明らかにしませんでしたが、 Appleは同じであるという仮定があります。 同社はまた、自動車業界向けに最新のプロセス技術の専門バージョンを開発しています。

5nmチップを待つタイミング

TSMCは、2019年に危険な5 nmチップの生産を開始する予定です。 同社はEUVを使用して5ナノメートルのマイクロ回路を作成していますが、チップの14層は、4層ではなくこのフォトリソグラフィー法を使用して製造されます。

それまでに、台湾の企業はEUVテクノロジーを打ち破り、生産能力を増強する予定です。 同社はすでに、チップを製造する新しい工場の建設開始を発表しています。 台湾の南サイエンスパークに建設されます。

5nmチップには、7nmよりもいくつかの利点があります。 同じ複雑さで、更新されたチップのトランジスタ密度は1.8倍になり、クロック周波数は15%増加します。 この場合、5 nmプロセッサの消費エネルギーは7 nmより20%少なくなります。 ただし、生産を開始する前に、会社は多くの困難を解決する必要があります。

これらの最初のものは、開発ツールの不足です 。 5nmプロセス技術に必要なEDA設計パッケージは、今年11月に準備されます。 ただし、PCIe 4.0およびUSB 3.1ユニットのライブラリは、来年の夏にのみ準備が整います。

別の問題は、高い開発コストです。 専門家によると、7 nmテクノロジを使用したチップ上のシステムの開発には約1億5,000万ドルの費用がかかります 。 5nmプロセステクノロジーの場合、コストは2億5000万ドルに上昇します。 これは、最終製品の価格が最終的に上昇し、これらのチップの使用に興味を持つクライアント企業が少なくなることを意味します。 したがって、5 nmプロセステクノロジを使用した超小型回路の生産が成果を上げるという保証はありません。

他の会社はどうですか?

以前の投稿の1つで、集積回路のメーカーであるGlobalFoundriesは、財政難のため7、5、3 nmプロセス技術の開発を停止したと述べました。 代わりに、組織は14nmの改善と組み込みストレージデバイスの作成に切り替えました。

/写真Mr Seb CC / 22nmシリコンウェーハIntel

インテルはまた、新しい技術プロセスの開発速度でTSMCを失います。 同社は再び10-nmチップのリリースを延期し、 9月に生産能力を「オフロード」するために22-nmチップに戻ることを発表しました(チップセットの実装にもかかわらず)。 ただし、TSMCの7 nmとIntelの10 nmは、トランジスタの密度とサイズに関して同じ設計基準と見なされていると言っても過言ではありません。

これまでのところ、サムスンは 7および5ナノメートルの分野でTSMC の唯一の競争相手です。 韓国の巨人は来年上半期に7nmチップの発売を計画している。 5-nm Samsungの設計基準に準拠したチップも2019年に生産が開始されますが、販売が開始された時点ではまだ知られていません。

PS仮想インフラストラクチャとPDとの連携について- テレグラムチャネルで :