みなさんこんにちは!

最近、FPGAの読み込みを高速化するという課題が生じました。 電力の出現から動作状態まで、100ミリ秒以下です。 このチップは最新のものではないため(Altera Cyclone IV GX)、EPCQなどの高速フラッシュドライブを接続しても機能しません。 そして、FPP(高速並列並列)モードを使用し、CPLD Intel MAXVを外部からFPL(フラッシュ並列ローダー)で使用することにしました。 起動時に、CPLDはUSBフラッシュドライブからデータをダウンロードし、出力でFPP信号を生成します。

しかし、計画を完了する前に、彼らは手元にあるもののDIYモックアップを組み立て、「猫で」の実験を開始しました。 残念なことに、ボード上の節のために、動作周波数を下げる必要がありましたが、FPPの本質は変わりませんでしたが、デバッグは簡素化されました。 何が起こったのか、そしてFPGAがどのように構成されているのかについて、私はこの記事を書くことにしました。 誰も気にしない、猫へようこそ。

私が話したいこと:

- FPGAの構成について簡単に説明します。 典型的なタイミングチャート、モードは何ですか

- FPGAをロードする手順は何ですか

- FPPとは

- FPLについてその役割は何ですか

- EPCQおよびFPLのサポートについて

- 写真付きの実験結果について

FPGAはどのように構成されますか?

FPGAダウンロードには、アクティブとパッシブの2つのタイプがあります。 アクティブは、FPGAが外部フラッシュをクロックし、そこからファームウェアを読み取ることを意味します。 パッシブ-ファームウェアをFPGAにロードする特定のホスト(プロセッサー、FPGA、コントローラー)があること。

アクティブは誰にでもよく知られています。おそらく、EPCS / EPCQフラッシュドライブを接続し、JTAGを介してファームウェアをアップロードし、電源を入れるとFPGAが残りのデータ読み取りを行うため、人生を楽しみます。

パッシブは追加のロジックの実装を必要とするため、もう少し面倒です。プロセッサはどこかからファームウェアをロードする必要があり、誰かがこのファームウェアをそこに配置する必要があるなどです。 ただし、多くの場合、パッシブモードの方が高速です。 たとえば、アクティブシリアルモードのCyclone IVでは、DCLK 40 MHzと1データビットがサポートされ、FPP(高速パッシブパラレル)モードでは100 MHzと8データビットで、20倍高速です。

FPGAを構成する主な信号は、nCONFIG、nSTATUS、CONF_DONEです。

- nCONFIG入力を使用すると、FPGAをリセットし(1から0に差分)、ファームウェアのダウンロードを開始できます(0から1に差分)

- nSTATUS出力により、FPGAがデータを受信する準備ができているか(レベル1)、構成またはFPGAの動作中にエラーが発生したか(ゼロの差)を確認できます。

- CONF_DONE出力により、FPGAが構成されていることを理解できます。 正確には-FPGAがすべての構成データを受信したこと

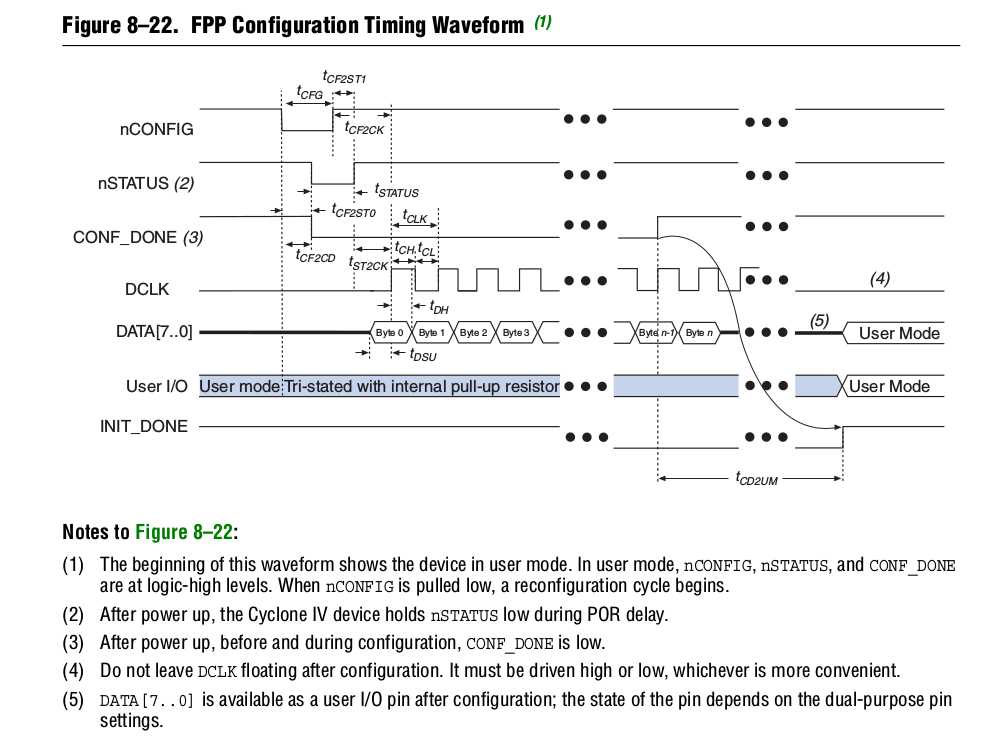

これらのモードのタイミング図はそれほど変わりません。 ここに私たちの場合の典型的な受動的な並列があります:

その中で次のことが起こります。

- 外部ホストがFPGAをリセットします(nCONFIG:1-> 0)

- FPGAは、nSTATUSを最初にゼロに設定してから1にリリースすることにより、準備ができていることを確認します。また、CONF_DONE信号は0にリセットされます。

- 外部ホストがFPGAコンフィギュレーションを開始します(nCONFIG:0-> 1)

- CONF_DONE信号が表示されるまで、外部ホストはデータ(ファームウェア)を書き込みます(CONF_DONEの後、まだ2、3のダミーサイクルが必要です)

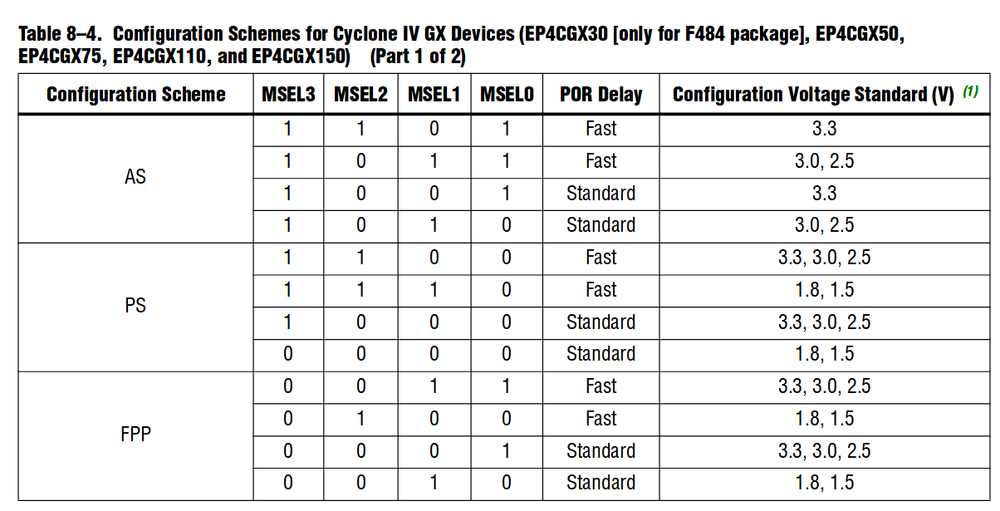

コンフィギュレーションモードの選択は、特別なレッグFPGA-MSELによって行われます。 異なるファミリでは、モードの数が異なります。 たとえば、Cyclone Vでは、アクティブ/パッシブに加えて、ファームウェアの圧縮モードと暗号化モードが選択されます 。 Cyclone IVでは、アクティブ/パッシブおよびPOR高速/標準のみ

FPPの仕組み

FPP(高速パッシブシリアル)は、DCLK信号のクロックサイクルに従って、コンフィギュレーションがワード(1バイト以上)で同期的にFPGAにロードされるパッシブモードです。

このモードの「ライトバージョン」はパッシブシリアルであり、ファームウェアはビットごとにダウンロードされます。

このモードでは、専用ピンが使用され、そのうちのいくつか(データの高ビット)は通常のI / Oになります。

- DCLK

- データ[7:0]

古いチップ(Stratix Vなど)では、1クロックあたり2(FPPx16)および4(FPPx32)バイトでファームウェアをダウンロードできます。

FPGAダウンロード時間

パッシブモードでFPGAのロード時間を計算してみましょう。 始まりはチップ上の電圧の出現(特定の値に達したとき)であり、終わりはCONF_DONE信号の出現です。

拡大時間は、次の段階で構成されます。

- tPOR:パワーオンリセット。 高速モードでは数ミリ秒かかり、標準モードでは数百ミリ秒(!)かかります。 ただし、起動にはより多くのエネルギーが必要なため、Fastには電力システムに対するより厳しい要件があります

- 構成ハンドシェイク:ホストはnSTATUS = 1を待機し、FPGAをリセットし(nCONFIG:1-> 0)、開始します(nCONFIG:0-> 1)。 この段階は1ミリ秒の何分の1かを要し、安全に無視できます。

- tCFG:FPGAにデータを送信し、CONF_DONEを監視します。 この部分には、ファームウェアのサイズに比例し、データが記録されるDCLKの周波数に反比例するメイン時間がかかります

- tINIT:データをロードしてチップを初期化します。 この段階が完了すると、FPGAは完全に動作できる状態になります(ユーザーモードにあります)。 所要時間が1ミリ秒未満なので、無視する

tPORはMSEL設定のみに依存します。 当然、起動時間が重要であり、電源設定が許可されている場合は、高速モードを設定する必要があります(上記のMSELの表を参照)。

時間の経過とともに、tCFGは次の要素に依存するため、少し複雑になります。

- DCLK周波数。 これは、FPGAと外部ホストの機能によって決まります。 サイクロンIVの場合、Fmaxは100 MHz

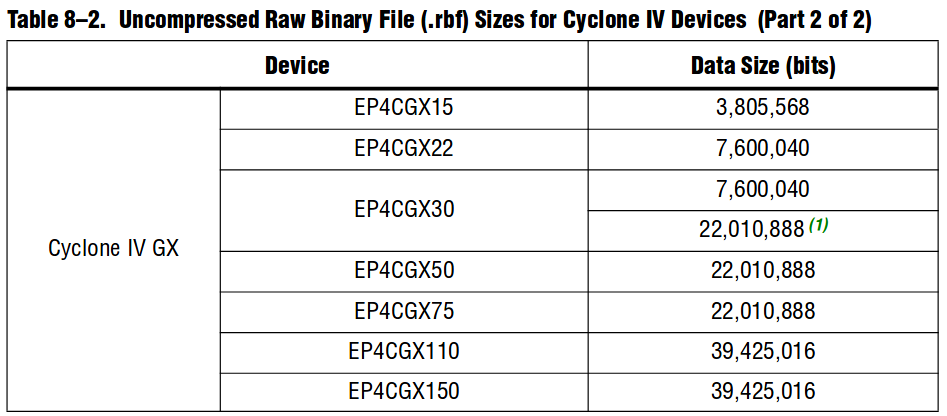

- ファームウェアサイズ。 FPGAファミリと特定のチップのロジックセルの数によって決まります。 各ファミリには、常に各チップの最大ファームウェアサイズのテーブルがあります。 たとえば、Cyclone IVについては、リンクを参照してください。

- ファームウェア圧縮。 一部のチップ(Cyclone V)ではMSEL設定によって決定され、一部のチップ(Cyclone IV)ではファームウェアコンバーターの設定のみによって決定されます。 圧縮による典型的な利益は50〜70%ですが、設計で100%保証されることを保証する保証はありません。 したがって、この番号を「置く」のは危険です

Cyclone IVのファームウェアサイズに関するドキュメントの表8-2は次のとおりです。

たとえば、EP4CGX75チップの場合、圧縮なしの最大ファームウェアサイズは22.010.888ビット= 2.751.361バイトです。 外部ホストが100 MHzの周波数で動作する準備ができていると仮定すると、最大ファームウェアのダウンロードには2.7e6 / 100e6 = 0.027秒= 27ミリ秒が必要です。 また、圧縮を使用する場合、受信時間は15ミリ秒未満であるため、この時間を約半分に短縮できます。

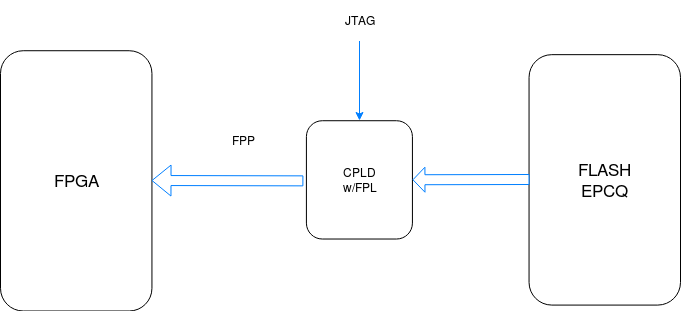

ただし、周波数DCLK = 100 MHzを取得するには、少なくとも同じ周波数でファームウェアを読み取ることができる必要があります。 Intel / Alteraが提供するオプションの1つは、この目的でCPLD MAX II / Vを使用することです。 一方ではCPLDがフラッシュを読み取り、他方ではFPGAに書き込みます。

Fpl

このタスクのために、既製のIPコアのコレクションにはFlash Parallel Loaderがあります。 このカーネルは、さまざまなインターフェイス(QSPI、NxQSPI、CFIなど)を備えたフラッシュチップのセットをサポートしているため、ファームウェアを読み取るだけでなく、JTAGを介して接続することで書き込むことができます。

また、1つのファームウェアではなく複数のファームウェアにFlashを書き込むことができるため、更新で問題が発生した場合に安定したイメージに「ロールバック」を編成できます。

Flash Programming&FPGA ConfigurationモードとEPCQをFlashとして選択しました。 これにより、必要なロード時間を満たし、同時に異なるホストを使用してJTAGとEPCQの両方をフラッシュできます。

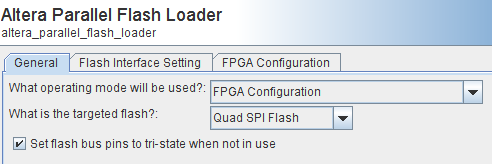

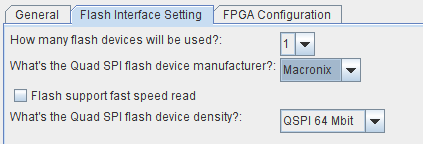

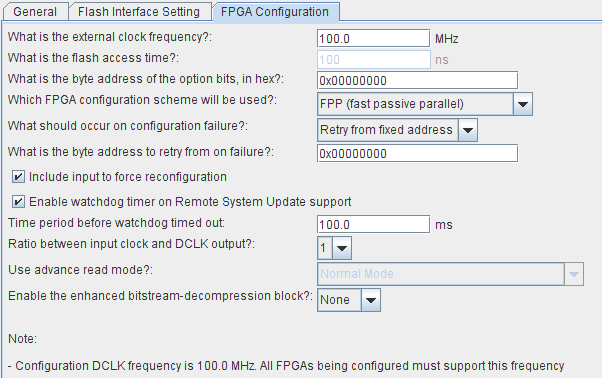

使用した設定のスクリーンショット:

ファームウェアCPLDには1267 LEが必要で、ほぼ100%にEPM1270F256C5(MAX II)または5M1270ZT144C5(MAX V)が必要です。 Flashファームウェアオプションを使用しない場合(他のホストがこれを実行できる場合など)、リソースの使用量は大幅に少なくなり、754 LEのマージンがあります。

CPLDの有効化スキームは次のとおりです。

FPL(例示的なアルゴリズム)の仕組み:

- FPGAからのレディ信号(nSTATUS = 1)により、上の図に従ってnCONFIGをアクティブにします。

- FPGAがデータを受信する準備ができたら(nSTATUSが0から1に変化した)、FPLはフラッシュからサービスデータブロックを読み取ります。 ファームウェア(または複数ある場合はファームウェア)のアドレスは、このブロックに登録されます

- FPLはファームウェアのダウンロードを開始し、入力ポートfpga_pgm [2:0]がファームウェアを示します。 2つのファームウェアを使用したため、1

- ダウンロード中にエラーが発生した場合(これは、イメージが完全にアップロードされていない、「壊れている」、または別のチップ/ファミリで発生する可能性があります)、FPLは工場出荷時のデフォルトのファームウェアに「切り替わり」ます。

- FPLはヌルイメージをFPGAにアップロードします。 彼とのすべてがうまくいかない場合、彼はさらにいくつかの試みをして停止します

1つのEPCQを使用して、説明した構成からどのパフォーマンスを絞り出すことができるかを見てみましょう。 これを行うには、EPCQがどのように機能するかについての少しのアイデアが必要です。

EPCQの仕組み

EPCQ(アドバンストEPCS)は、ほとんどのチームと一部のチーム(QuadSPI)用のSPIインターフェイスを備えたNORフラッシュです。 非常に高速で読み取られ、非常にゆっくりと書き込まれ、消去されます。

コマンド(消去、読み取り、書き込み)は常に通常のSPIを使用してフラッシュに到着し、フラッシュドライブの動作はコマンドに依存します。 例:

- READ / FAST_READコマンドを記述すると、読み取りはシングルビットモードで実行されます。

- FASTDTRDの場合、DDRを使用したシングルビットモード

- 4READの場合、4ビットモード

- など

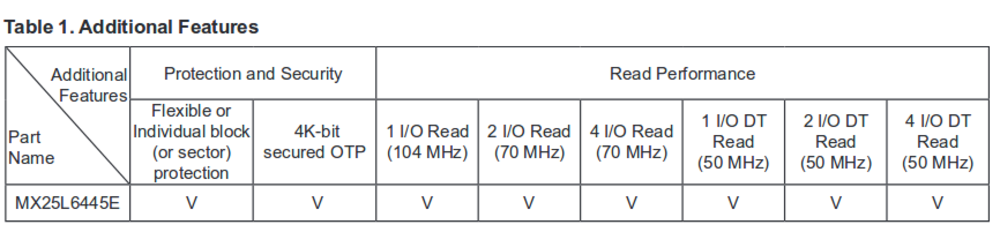

フラッシュマクロニクスの説明の例を参照してください

最大のEPCQ読み取りパフォーマンスは、DDRで最大周波数で4ビットすべてを使用することで達成されます。 ただし、この場合、時間的特性は非線形に変化します。

つまり、上記の例では、スループットは次の場合になります。

- 読み取り-104 Mbps

- FASTDTRD-100 Mbps

- 4READ-280 Mbps

- 4DTREAD-400 Mbps

S25FL064Lなどのフラッシュドライブとそれより高速なドライブがあり、それらは読み取り容量を増やしても周波数は低下しません。 したがって、「最大速度を絞る」ためには、それらに焦点を合わせることをお勧めします。

Cyclone IVのファームウェアの読み取りに必要な時間に4READ / 4DTREADモードを再計算すると、78ミリ秒/ 55ミリ秒になります。 FPPに「追いつく」ためには、27ミリ秒以内に維持する必要があることを思い出させてください(上記参照)。

タスクのボトルネックはファームウェア読み取りインターフェイスであり、FPP自体ではないことがわかりました。 また、100ミリ秒ではなく、はるかに短い時間を取得する必要がある場合は、2つのEPCQフラッシュドライブを使用する必要があります。 しかし、私たちの場合、通常の4READモードで十分です。

サポートされているEPCQのリストについては、 PFLドキュメントのセクション1.2.1を参照してください。

Intel / AlteraがEPCQのリリースを拒否したのは今からですが、現在では独自のものではなくMicronを公式にサポートしています。

DIYの時間は今!

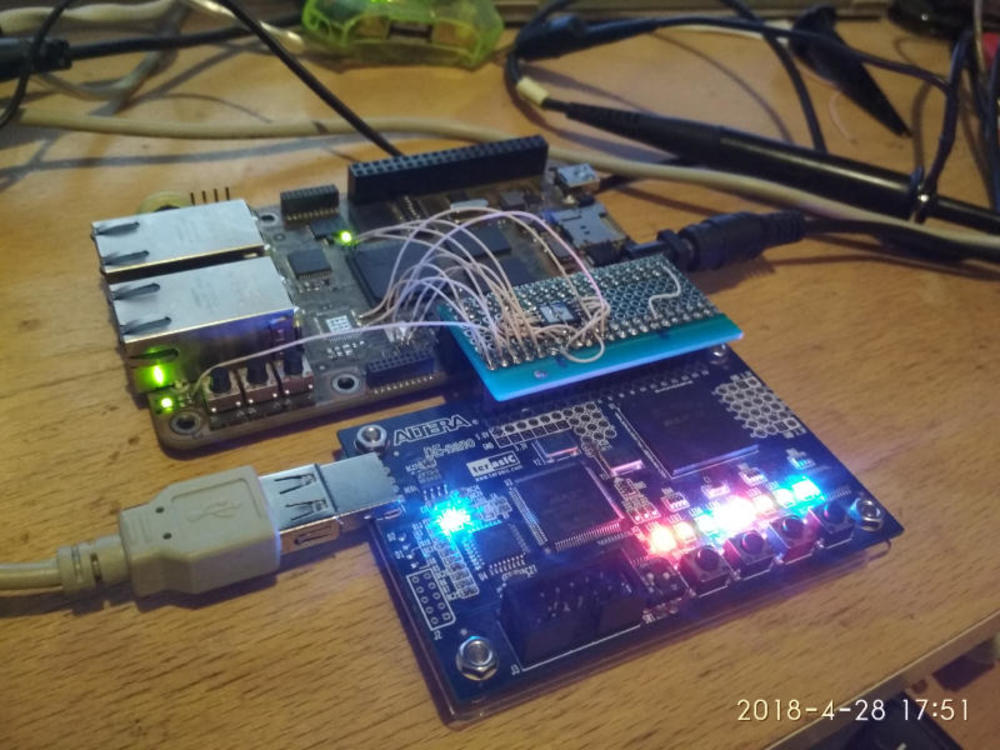

理論と実践を組み合わせるために、次のものを取り上げました。

- Cyclone V SoC(5CSEBA4U19C8SN)付きキットEthond

- MAXII EPM2210f324を搭載した古代のテラシックキット

- EPCQ Micron N25Q256A13EF840

- はんだごて、ワイヤー、モグラネズミ

- 黄金の手、はんだ、フラックスを持つ男

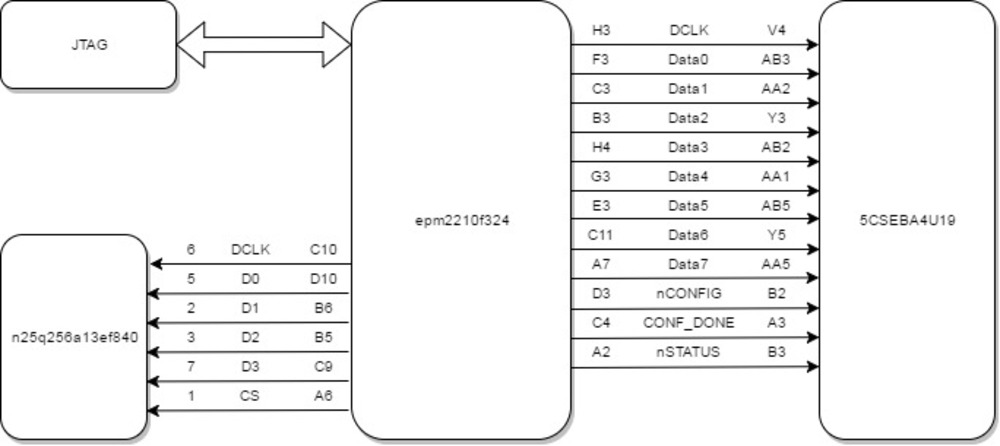

チップは次のように接続されます。

モグラネズミでは、マウントされたインストールがQSPIフラッシュドライブをはんだ付けし、レイアウトを取得しました。

PFL(リンク)を介してEPCSにアップロードするために使用されるファームウェアを作成するための短いクエスト( ドックのセクション1.4.1を参照)を通過した後、「タイムアウト」の測定を開始しました。 ファームウェアを作成する場合、EPCQが使用されている場合でも、CFI-flashをターゲットとして指定する必要があることに注意してください。

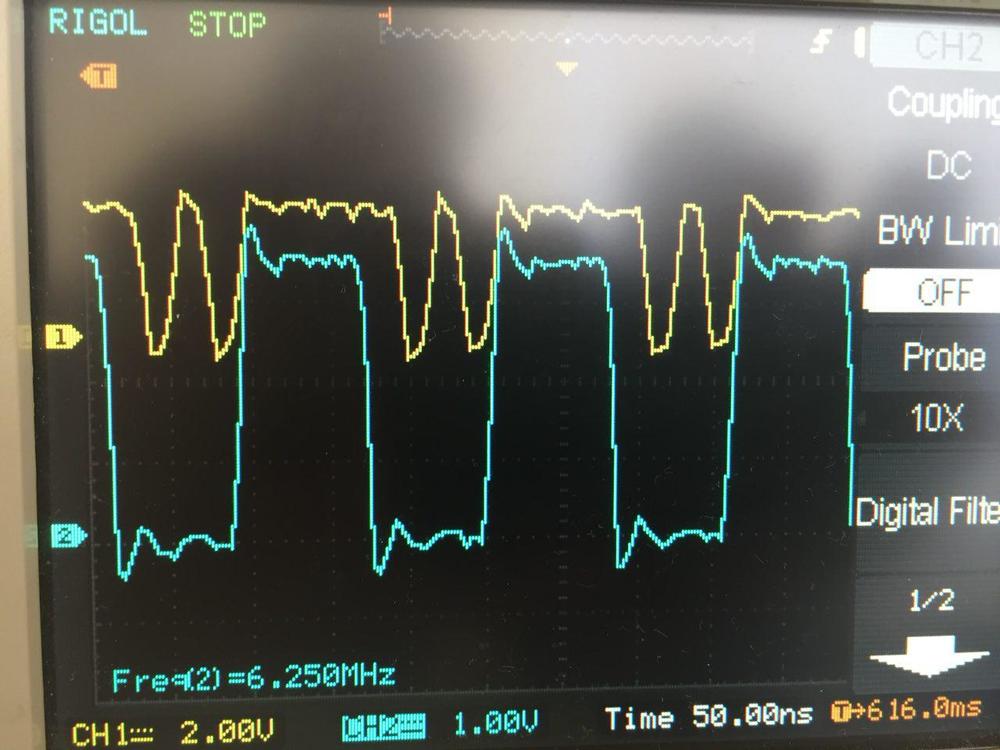

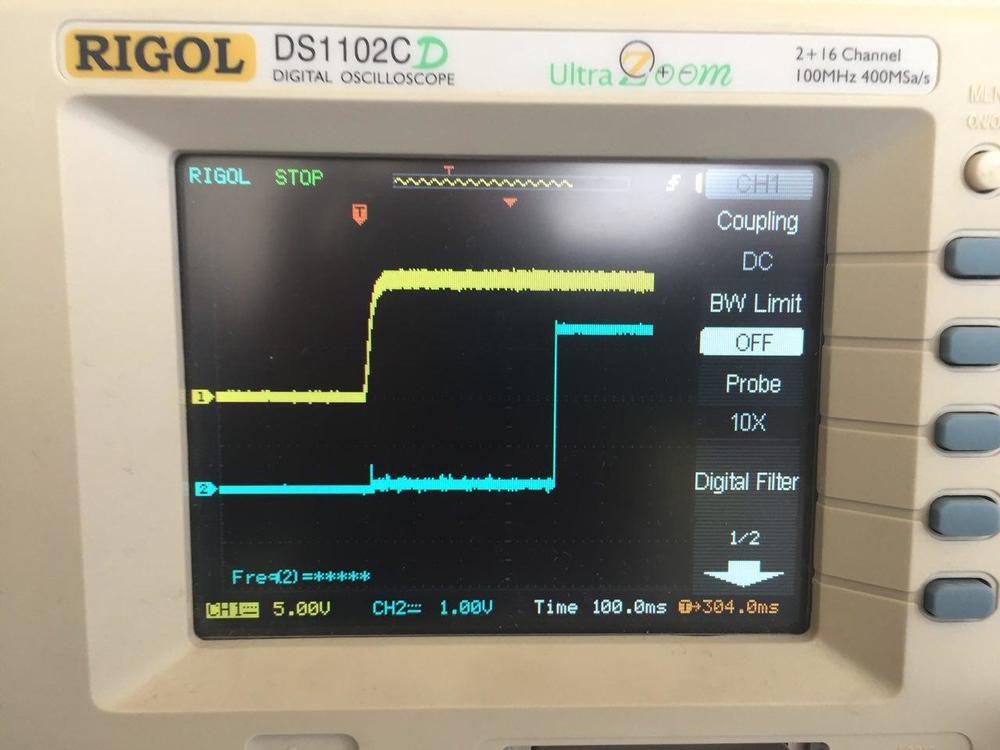

残念ながら、取り付けられた設置と「ひげ」のために、FPLの動作周波数は6.25 MHzであり、EPCSでは25 MHzのままです。 「入力クロックとDCLKの比率」オプションを使用してこのクロックを調整し、値を8に設定しました(入力クロック= 50 MHz)。 FPP(青)とEPCQ(黄色)のブロック図の図を次に示します。FPP容量はEPCQの2倍(8対4)であるため、各FPPサイクルには2つのEPCQ DCLKサイクルがあります。

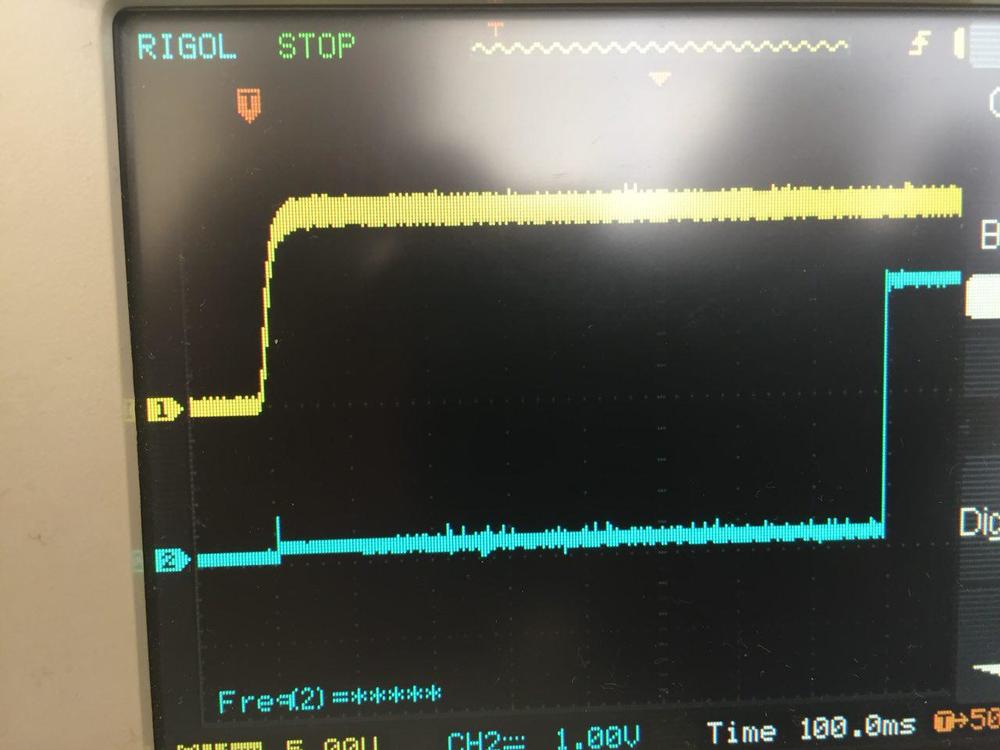

これは、標準PORモードで圧縮なしの供給電圧(黄色)とCONF_DONE信号(青)の図です:合計負荷時間は780 msです。

電源の出現とnSTATUS信号の間で約100ミリ秒が経過します。これは、チップが構成データを受信する準備ができていることを示します。

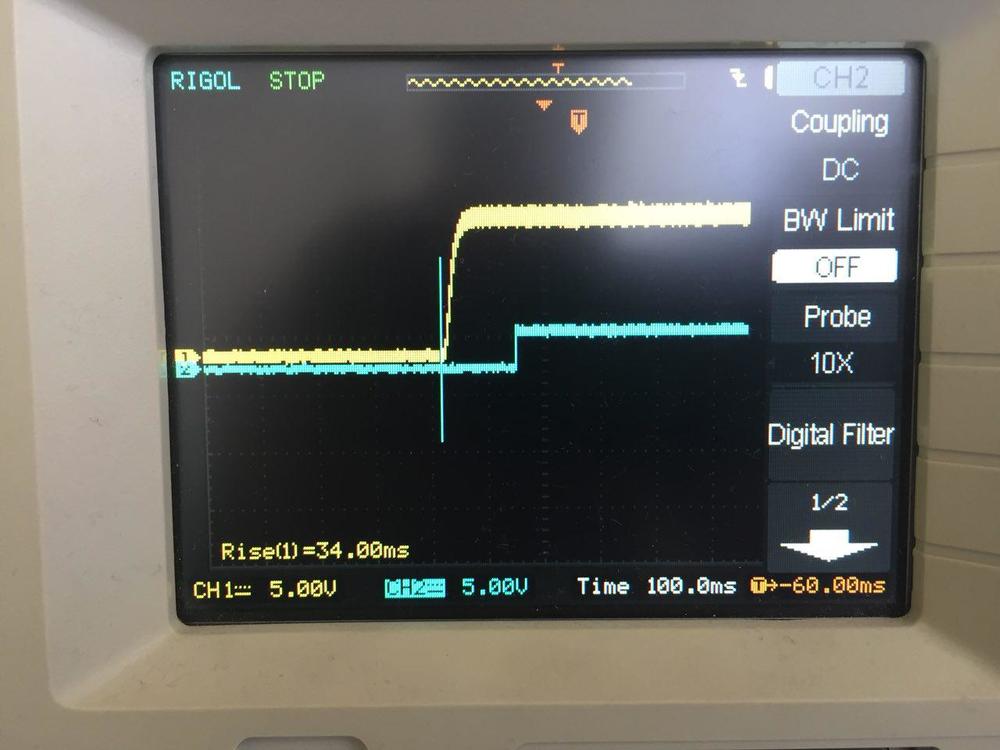

また、高速モードを有効にすると(MSELを変更するだけで、上記の表を参照)、PORが数ミリ秒で発生し、ダウンロードにはすでに約680ミリ秒かかります。

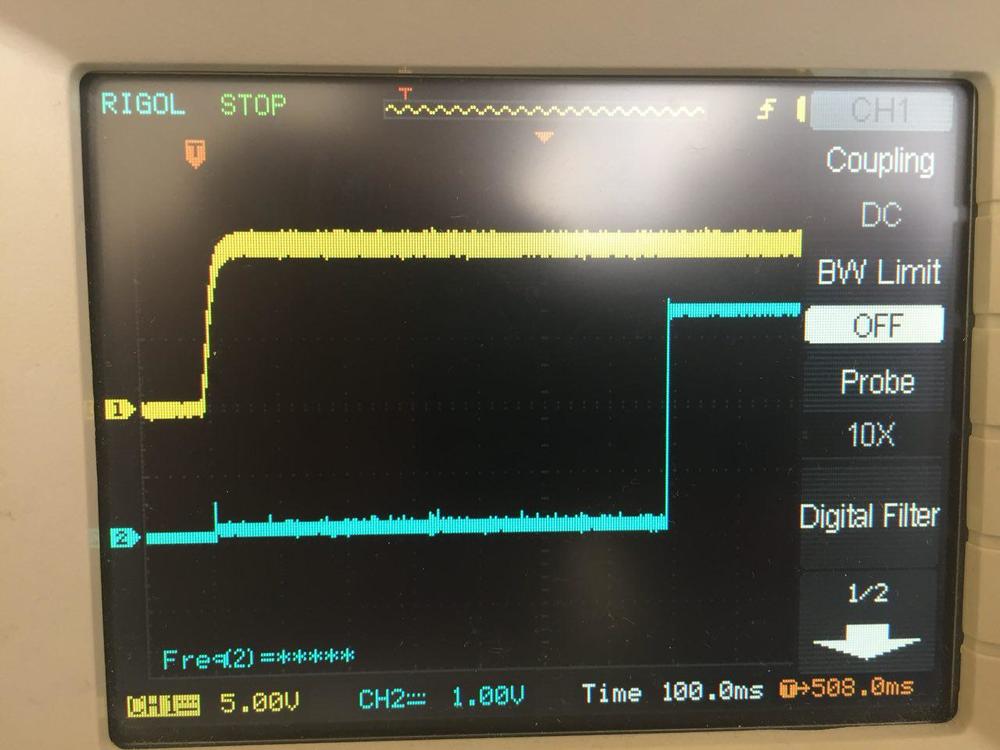

そして最後のステップは、圧縮を有効にすることです。 これを行うには、ファームウェアファイルをPFLに追加するときにQuartusボックスをオンにし、MSELを切り替えます(Cyclone IVでMSELに触れないでください)。 そして、私たちは完全に異なる絵を取得します

圧縮および高速PORなしの元のバージョンと比較して、2倍のゲイン(約400ミリ秒)があります。

理論と実践の組み合わせ

オシロスコープで行った測定値が計算と一致するかどうかを計算しましょう。 時間tPORはゼロであると想定されます。 Fast PORを使用します。 したがって、ダウンロード時間680ミリ秒がファームウェアのサイズとFPP DCLKの周波数にどの程度収束するかを計算することしかできません。

Cyclone Vのファームウェアのサイズは、約4メガバイト(32メガバイト)です。 FPP DCLKクロック周波数は6.25 MHzです。 クロックサイクルごとに8ビット、つまり1バイトが送信されます。 したがって、推定時間は4 / 6.25 = 0.64秒です。 うわぁ!

たとえば、FPP DCLKの周波数を8倍(最大50 MHz)に比例的に増加させると、80ミリ秒の時間が得られます。 圧縮も含めると、さらに少なくなります。

結論

理論的には、Cyclone IVの計算によると、FPGAは数十ミリ秒で、約30ミリ秒でロードできます。 ただし、このためには、データのロード元であるフラッシュなどのFPGAにデータをロードするホストが帯域幅と一致する必要があることに留意する必要があります。

最近のFPGAチップでは、EPCQフラッシュドライブを直接接続してアクティブモードを使用できます。デザインに新しいファミリに切り替える機会がない場合は、外部ローダーをインストールしてパッシブモードを使用することができます。 このために、レイアウトで使用したFlash Parallel Loaderが使用されます。

FPLと1つのEPCQで説明したアプローチを使用すると、FPGAのロード時間を50ミリ秒に近づけることができます。

最後まで読んでくれた皆さんに感謝します!