おそらく「純粋なサイン」というフレーズがあった広告を見たか、記事を読んだのではないでしょうか。 マーケティングコンポーネントについてではなく、技術的な実装のみについて説明します。 私は、仕事自体の原理、標準的な(そうではない)回路ソリューションについて、そして最も重要なこととして、可能な限り明確に説明しようとします-私たちのために必要な信号を生成するSTM32マイクロコントローラ用のソフトウェアを書いて分析します。

STM32を選ぶ理由 はい、現在はCISで最も人気のあるMKであるため、ロシア語のトレーニングに関する多くの情報があり、多くの例があります。そして最も重要なのは、これらのMKとデバッグツールが非常に安いことです。 直接言う-商業プロジェクトではTMS320F28035またはTI Piccoloシリーズの同様のDSPのみを配置しますが、これはまったく別の話です。

1つ重要なのは、STM32を使用すると

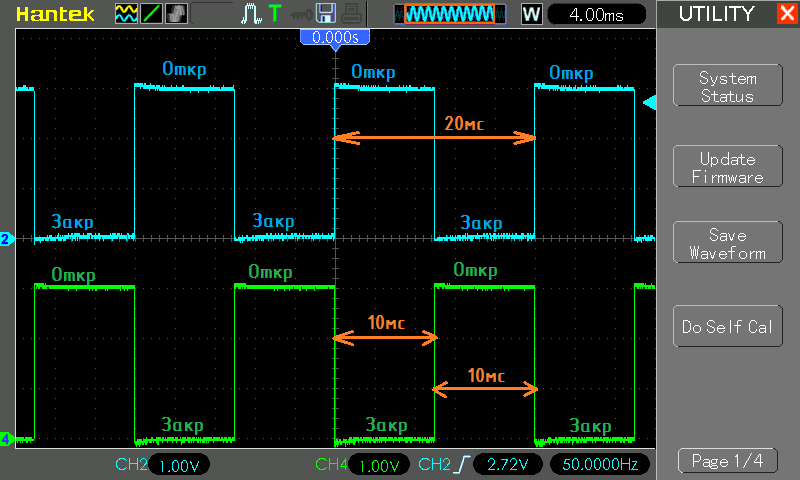

これは、定電流を交流に変えるために取得する必要がある制御信号の写真です。 そして、はい-ここにサインがあります! その映画のように:「ゴーファーを見る?」 -いいえ。 「でも彼は...」

副鼻腔がどのように形成されるかを知ることは興味深いですか? それでも、キロワットのエネルギーポンプ

1.正弦波信号を生成するためのトポロジ

多くの電子技術者に「どうやって正弦波信号を生成できますか?」と尋ねると、何十もの異なる方法の提案が当てはまりますが、どれが必要ですか? 最初のタスクから始めましょう-たとえば、380V 10Aを230Vの交流電圧に変換する必要があります。 一般に、これは「古典的な」ケースであり、優れたオンラインUPSまたはインバーターで見ることができます。 約4 kWの電力を変換する必要があり、弱いものではなく、効率が良い場合でも、正しいことがわかります。 同様の条件は、サインを「描く」ためのオプションの数を減らすと思います。 それで、私たちには何が残っていますか?

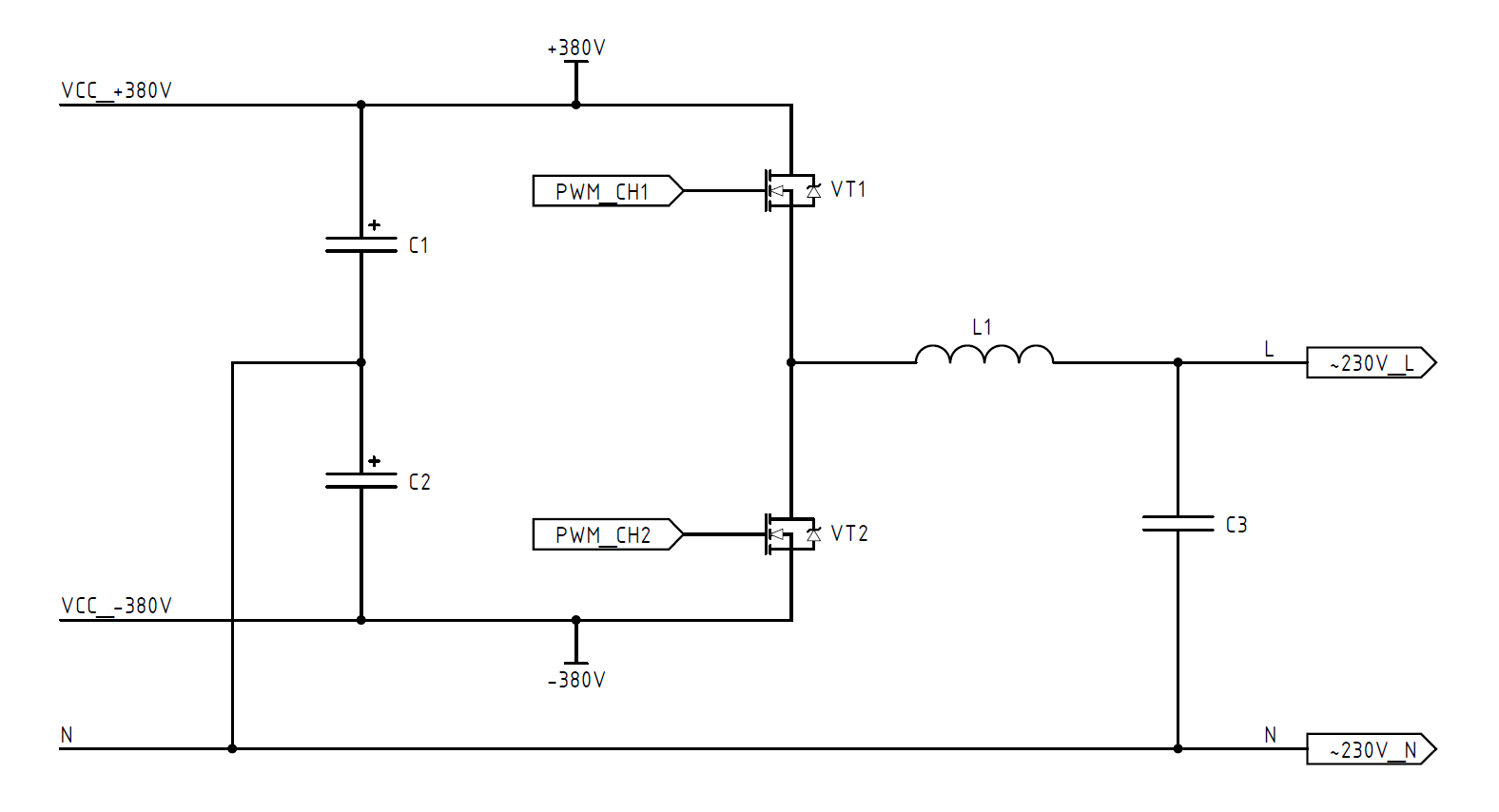

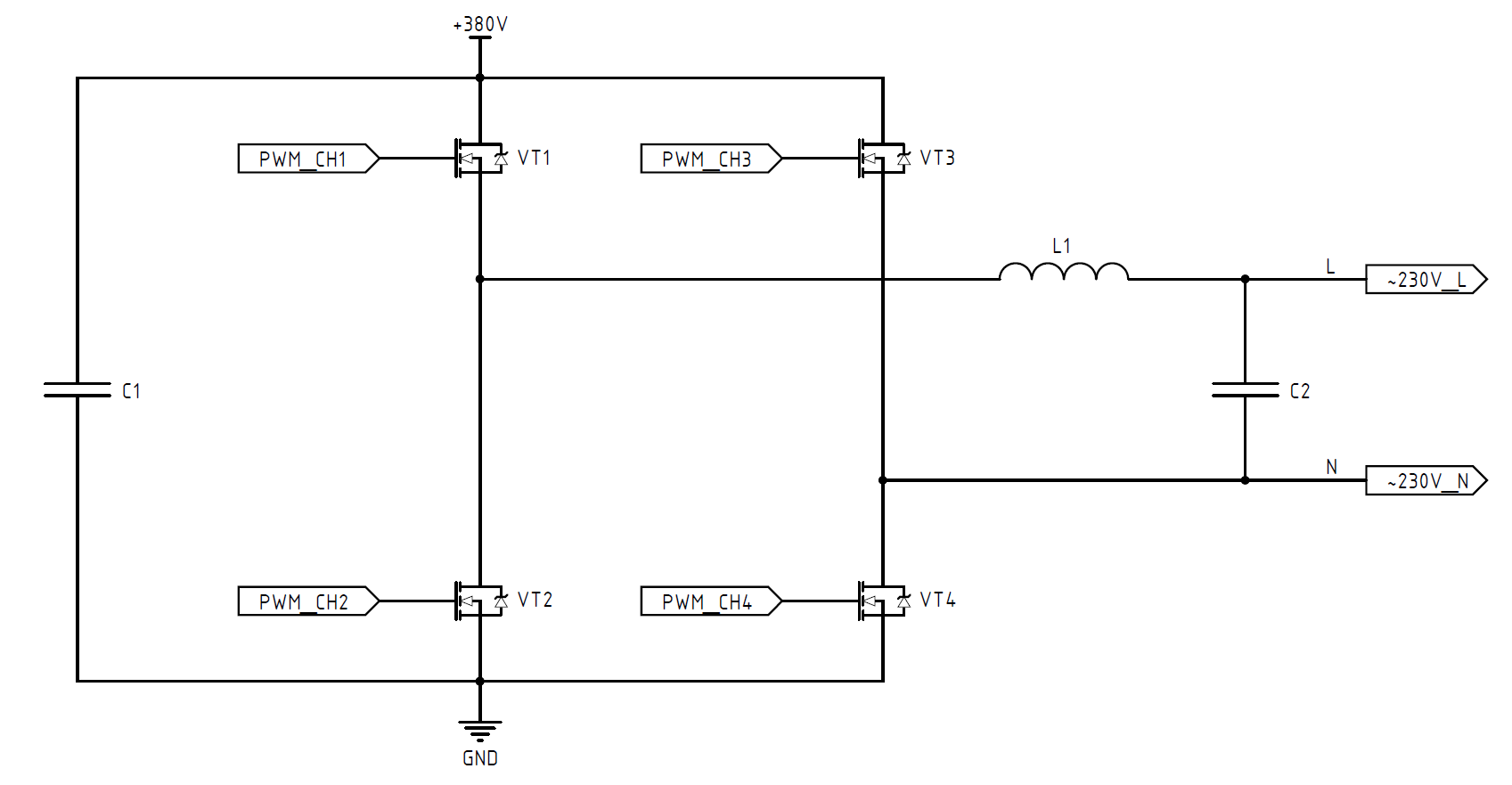

最大6〜10 kWの電力変換器では、フルブリッジとスルーニュートラルのハーフブリッジの2つの主要なトポロジが使用されます。 彼らは次のように見えます :

1)エンドツーエンドニュートラルのトポロジ

このトポロジは、正弦波出力を備えた予算のUPSで最もよく見られますが、APCやGEなどの当局は、十分な容量であってもそれを使用することを軽notしていません。 何が彼らにこれを促しますか? このトポロジの長所と短所を見てみましょう。

長所:

- パワートランジスタの可能な最小数。これは、損失が2倍少なくなり、デバイスのコストも低くなることを意味します。

- ゼロを介して。 これにより、認証プロセス、特にCEおよびATEXが簡素化されます。 これは、コンバータの後に出力回路で事故が発生した場合、ゼロを介して入力保護システム(RCDなど)が同じように動作できるためです。

- 製品のコストを最小限に抑えられるシンプルなトポロジー

および中バッチ生産

短所:

- バイポーラ電源の必要性。 ご覧のように、インバータ回路に±380Vと別のゼロを適用する必要があります

- 高電圧コンデンサの数の2倍。 3〜4 kWの電力で大きな静電容量と小さなESRを備えた高電圧コンデンサは、20〜40%を作り始めます。

部品コスト - 「分周器」での電解コンデンサの使用。 それらは乾燥しており、同じパラメータを持つコンデンサを選択することはほとんど不可能であり、操作中に電解質パラメータが変化することを考慮すると、意味がありません。 フィルムとの交換は可能ですが、高価です

主な長所と短所が特定されているので、このトポロジはいつ必要ですか? 私の主観的な意見:500-1000 Wまでの電力で、基本的な要件は信頼性ではなくコストです。 そのような消費財の代表的なものは、A-Electronicsの安定剤です。安価で、どういうわけか機能し、大丈夫です。 わが国の消費者の60%にとって、これは十分で手頃な価格です。 結論を導きます。

2)ブリッジトポロジ

ブリッジトポロジ...おそらく、電力変換器で最も理解可能で最も一般的なトポロジであり、経験がほとんどなくても開発者が利用できる最も重要なトポロジです。 10 kWを超えると、単相または三相ブリッジ以外のものは見つかりません。 なぜ彼はそんなに愛されているのですか?

長所:

- 非常に高い信頼性。 これは主にパワートランジスタ制御システムの品質によるもので、コンポーネントの劣化に依存しません

- 入力容量が必要な場合もあれば、1桁も少ない場合もあります。 計算されたESRを提供するだけです これにより、コストを維持しながらフィルムコンデンサを使用できます。 フィルムコンデンサ-乾燥しないでください。過酷な温度でも良好に伝導します。使用寿命は電解質の寿命よりも1桁高くなります。

- トランジスターの最小電圧リップル、つまり、より低い電圧にトランジスターを適用できることを意味します

- 作業アルゴリズムのシンプルさとわかりやすさ これにより、製品の開発にかかる時間が大幅に短縮され、試運転も可能になります。

短所:

- パワートランジスタの数が増えたため、より深刻な冷却が必要になります。 トランジスタの価格は上昇しますが、コンデンサの数が少ないため、これはかなり有利です

- 特にガルバニック絶縁要件により、ドライバーの複雑さが増す

ブリッジトポロジの実際の欠点からわかるように、トランジスタの冷却に対する要件は増加しているだけです。 多くの人が考えるだろう:「より多くの熱が放出される-それはより低い効率を意味する!」 それほどそうではありません... EMFエミッションの低減と、より「剛性の高い」制御システムにより、2つのトポロジーの効率はほぼ同等です。

70%のケースでは、DC / ACインバーターだけでなく、他のコンバーターでもブリッジ回路を使用する必要があります。 これは、私が主に産業用ソリューションを設計し、ヨーロッパの顧客向けに設計することが多いためです。高価な産業用デバイスには5〜15年の保証を与えるのが慣例です。 古典的な要件:「10年間の保証を提供できるように、鉄片が必要です」、もう選択する必要はありません。 もちろん、最低価格のデバイスが必要な場合は、トポロジを選択するときに特定のタスクから開始する必要があります。

簡単な要約 :この記事では、ブリッジコンバーター(Hブリッジまたはフルブリッジ)の動作用のソフトウェアを紹介しますが、正弦波形成の原理はすべてのトポロジで同じです。 コードは1番目のトポロジーに適合させることもできますが、それはあなた自身です。

2.ブリッジコンバーターを使用した交流電流の形成

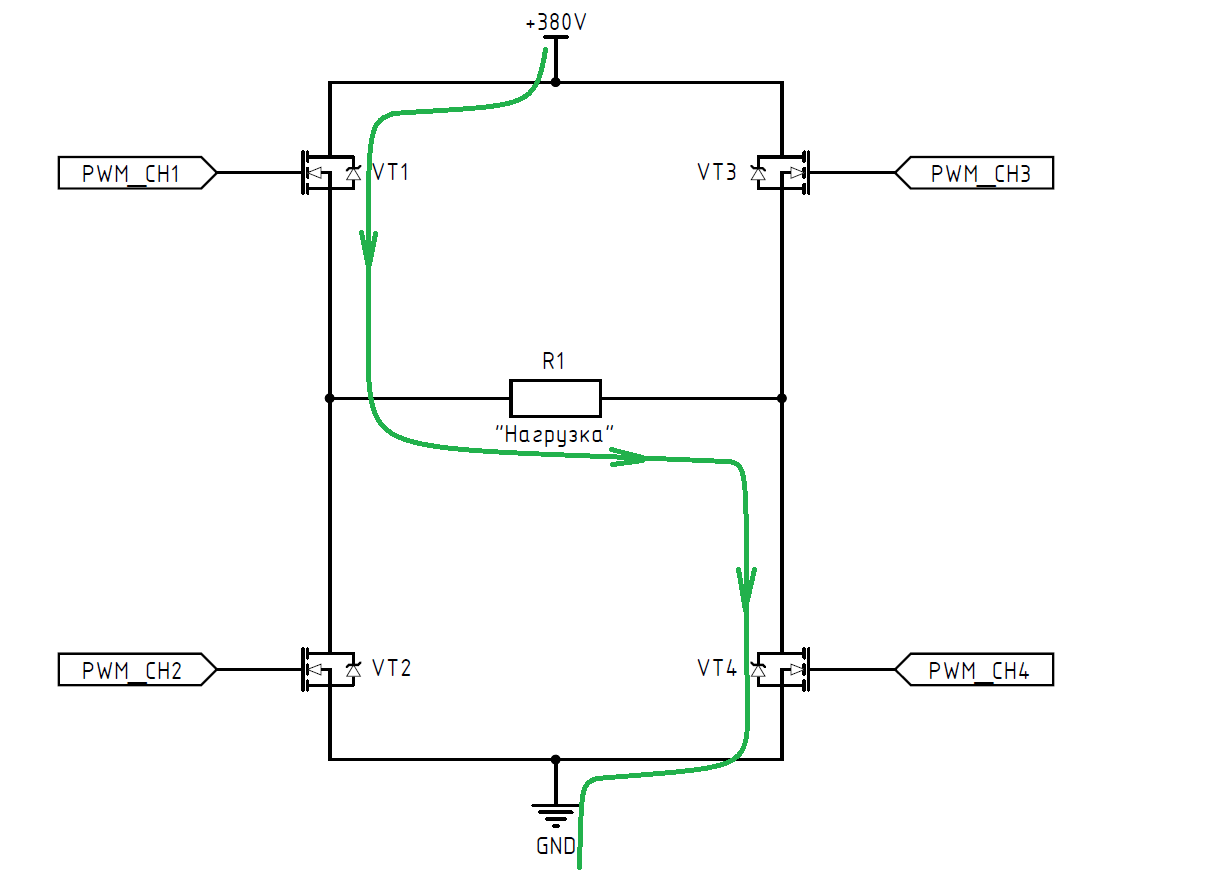

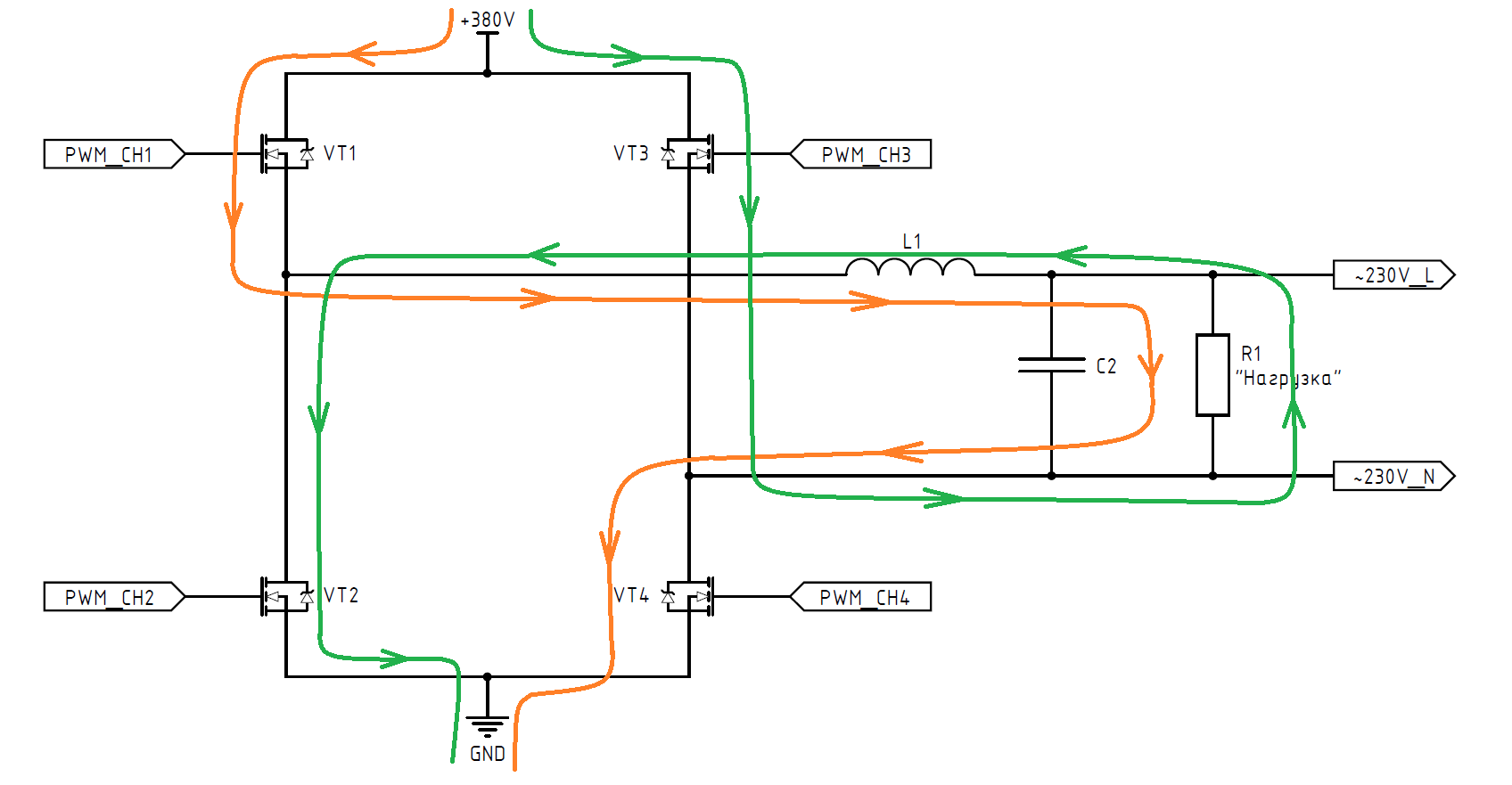

まず、ブリッジコンバーターの一般的な動作を見てみましょう。 回路を見て、トランジスタVT1-VT4を確認します。 これにより、抽象負荷(抵抗など)に1つまたは別の可能性を適用できます。 トランジスタVT1とVT4を開くと、次のことがわかります。VT4は負荷の一端をマイナス(GND)に接続し、トランジスタVT1は+ 380Vに接続し、電位差「380V-0V」が負荷に現れます。負荷は電流を流し始めます。 科学者が同意したことを誰もが覚えていると思います-電流は「プラスからマイナスへ」流れます。 次の図が表示されます。

VT1とVT4を開くと何が得られましたか? 負荷をネットワークに接続しました! 抵抗器を電球に交換すると、点灯します。 そして、負荷をオンにするだけでなく、負荷に流れる電流の方向を決定しました。 これは非常に重要です! そして、その時にVT2とVT3に何が起こったのですか? それらは閉じられていました...完全に...きつい...すべて同じVT2またはVT3も開いていたらどうでしょうか? 私たちは見ます:

トランジスタVT1、VT4、およびVT2が開いたとします。 オームの法則を思い出してください。たとえば、IPP60R099P7XKSA1などの高電圧トランジスタのチャネル抵抗を見ると、0.1オームがあり、直列に2つあります。つまり、VT1およびVT2回路の抵抗は約0.2オームです。 次に、この回路を流れる電流を計算してみましょう:380V / 0.2 Ohm = 1900A。 私は誰もがこれが短絡であることを理解していると思いますか? また、VT2とVT3を閉じる必要がある理由は誰もが理解していると思いますか?

この「現象」は、 -through currentと呼ばれます。 そして、パワーエレクトロニクスに大きな戦争があるのは彼と一緒です。 それを避ける方法は? アルゴリズムが追加トランジスタの同時オープンを厳密に禁止する制御システムを作成します。

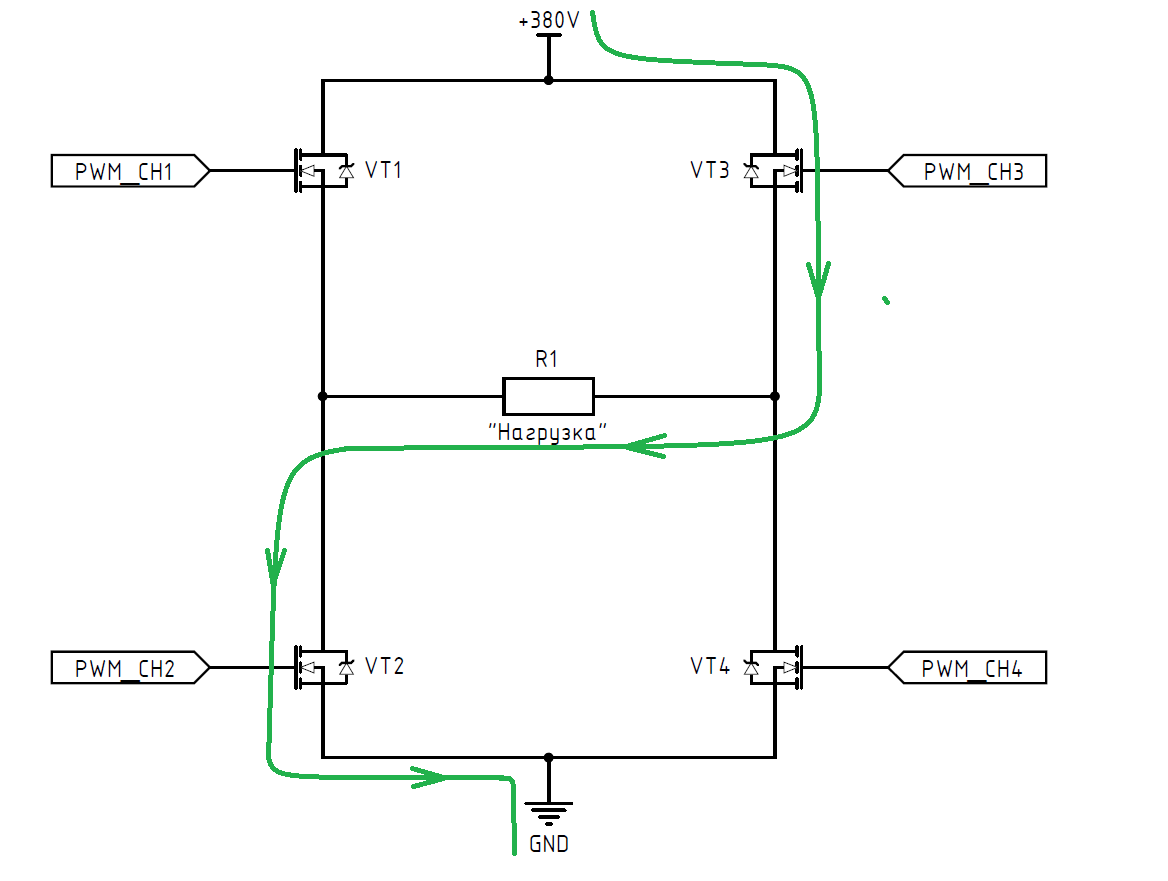

なぜトランジスタVT2とVT3が必要なのですか? 電流の方向が非常に重要だと書いたのを覚えていますか? AC変数とは何かを思い出しましょう。 実際には、これは何か可変の電流、この場合は電流の方向です。 コンセントに電流が流れ、1秒間に100回方向を変えます。 VT1とVT4を閉じてから、トランジスタVT2とVT3を開いて、次の図を取得してみましょう。

ご覧のとおり、電流の方向(矢印で表示)が逆になっています。 ブリッジを使用すると、電流の方向を変えることができましたが、これはどういう意味ですか? はい、交流が流れました!

ブリッジには2つの対角線があることに注意してください。最初の対角線はVT1 + VT4によって形成され、2番目の対角線はVT2 + VT3によって形成されます。 これらの対角線は順番に機能し、電流を最初に一方の方向に通し、次にもう一方の方向に通します。

交流電流が流れたとおっしゃいましたが、それほど簡単ではありません...標準電圧があります。 これは、電圧と周波数の2つの主要なパラメーターによって正規化されます。 電圧の問題は単純で純粋な回路であるため、ここで周波数を把握しましょう。

そして、周波数...それについて知られていること-それは50 Hzです(米国では60 Hzになります)。 信号周期は20 msです。 この場合、正弦波は対称です。つまり、2つの半波(正と負)の持続時間は同じ、つまり10 ms + 10 msになります。 ここですべてが明確であることを願っています。

物理的な意味でこれはどういう意味ですか? はい、10ミリ秒ごとに負荷の電流の方向を変更する必要があります。 まず、VT1 + VT4の対角線を10ミリ秒間開いた後、閉じて、次の10ミリ秒でVT2 + VT3の対角線を開きます。

トランジスタを開くとはどういう意味で、どの信号を適用するのか

トランジスタ制御の原理について少し話しましょう。 Nチャネル絶縁ゲートトランジスタ(Mosfet)を使用します。

「オープントランジスタ」とは、ゲート(G)がソース(S)に対して正の電位(+ 10..18V)であり、トランジスタがチャネル抵抗(SD)を無限に大きい(2-100MΩ)から小さい(通常)に変更したトランジスタです。 0.1-1オーム)。 つまり、トランジスタは電流を流し始めました。

「クローズドトランジスタ」とは、ゲート(G)がソース(S)に引き寄せられ、その抵抗が小さい値から無限に大きい値に変化したトランジスタです。 つまり、トランジスタは電流の伝導を停止しています。

電界効果トランジスタまたはIGBTの動作原理をよく理解するには、Semenovの本「Fundamentals of Power Electronics」または別のソースのいくつかの章を読むことをお勧めします。Wikipediaを使用して開始することもできます。

制御のために、パルス幅変調またはより一般的な略語-PWMを使用して信号を与えます。 この信号の特徴は、低電圧(GND)と高電圧(VCC)の2つの状態があることです。つまり、トランジスタのゲートにそれを適用するか、それを開くか閉じるかのいずれかです。他に方法はありません。怠 alsoな人のために表面的に説明したので、PWMについても読むことをお勧めします。

「オープントランジスタ」とは、ゲート(G)がソース(S)に対して正の電位(+ 10..18V)であり、トランジスタがチャネル抵抗(SD)を無限に大きい(2-100MΩ)から小さい(通常)に変更したトランジスタです。 0.1-1オーム)。 つまり、トランジスタは電流を流し始めました。

「クローズドトランジスタ」とは、ゲート(G)がソース(S)に引き寄せられ、その抵抗が小さい値から無限に大きい値に変化したトランジスタです。 つまり、トランジスタは電流の伝導を停止しています。

電界効果トランジスタまたはIGBTの動作原理をよく理解するには、Semenovの本「Fundamentals of Power Electronics」または別のソースのいくつかの章を読むことをお勧めします。Wikipediaを使用して開始することもできます。

制御のために、パルス幅変調またはより一般的な略語-PWMを使用して信号を与えます。 この信号の特徴は、低電圧(GND)と高電圧(VCC)の2つの状態があることです。つまり、トランジスタのゲートにそれを適用するか、それを開くか閉じるかのいずれかです。他に方法はありません。

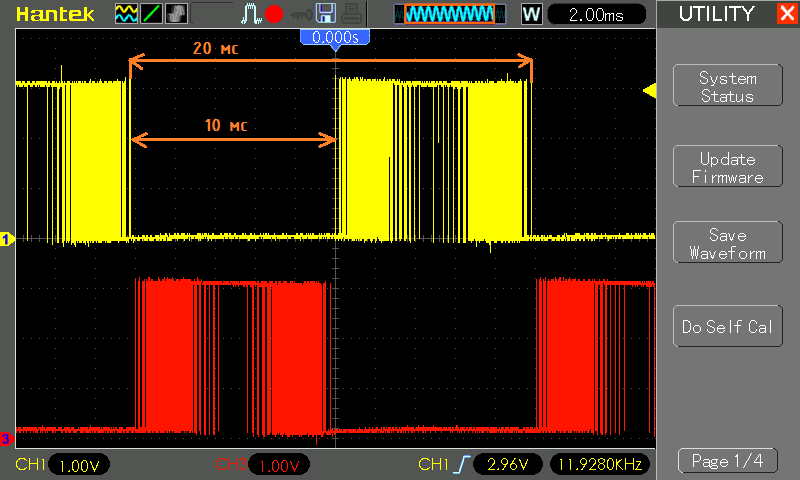

したがって、ブリッジが10ミリ秒ごとに電流の方向を変更するには、20ミリ秒の周期でデューティサイクルが50%のPWM信号を送信する必要があります。 これは、20ミリ秒のうち、肩は半分の時間(10ミリ秒)開いて電流を流し、残りの半分は閉じていることを意味します。 このようなPWMをすべてのキーに適用する必要がありますが、1つの条件があります-VT1 + VT4対角線に直接PWMを適用し、すでにVT2 + VT3対角線に逆相を適用します。 よりインテリジェントに言えば、対角線に供給される信号には180 0のシフトが必要です。 私はこの瞬間にあなたの頭がテキストを理解しようとして沸騰し始めたと思うので、視覚的な表現を見ます:

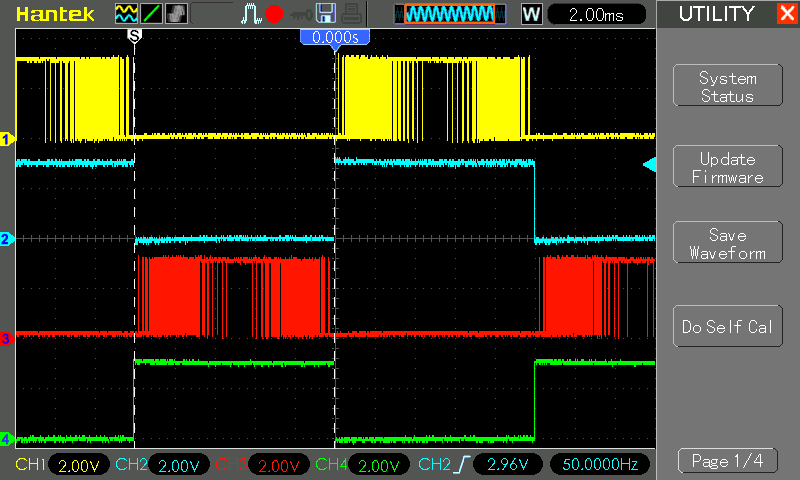

今、すべてが明確になっていますか? いや? その後、より詳細に...ご覧のとおり、トランジスタの開閉の瞬間に特に注意しました。プラスで開き、マイナスで閉じます。 また、信号は逆、つまり逆です。青信号が「プラス」の場合、緑信号は「マイナス」です。 ある対角線上の青信号と別の対角線上の緑信号を与えます-波形に見られるように、対角線が同時に開くことはありません。 ACの準備ができました!

期間を見てください。 私の言葉が抽象化されないように、彼は特にコントローラー出力からのオシログラムを示しました。 信号周期は20ミリ秒で、一方の対角線は10ミリ秒開いて正の半波を作成し、もう一方の対角線も10ミリ秒開いて負の半波を作成します。 今、私は皆が理解し、まだ理解していないことを願っています-PMに書いて、私はあなたのためにあなたの指で個人レッスンを行います。 私の言葉を確認すると、オシログラムは私たちの大切な50 Hzを示しています! 早くリラックスするためだけに...

50 Hzの周波数の交流電流を受信しましたが、ソケットに正弦波があり、ここでは蛇行はありません。 正式には、蛇行を出力に適用し、ほとんどの負荷に供給することができます。たとえば、パルス電源は、サインまたは蛇行のいずれでもかまいません。 つまり、すでにラップトップ、電話、テレビ、電話などをオンにするのに十分なものがありますが、ACモーターを接続すると、すべてが非常に悪くなります-ウォームアップが開始され、その効率は著しく低下しますが、最終的には燃え尽きます。 自宅にエンジンがないと思いますか? 冷蔵庫のコンプレッサーはどうですか? 円形加熱ポンプ? 後者は一般的に木でできているかのように燃えます。 井戸用の深井戸ポンプでも同じ状況があり、実際には多くのものがあります。 インバーター、スタビライザー、またはUPSの出力での正弦波信号が依然として重要であることがわかりました。 さて、あなたはそれを作成する必要があります! 今、脳の爆発が始まります...

3. PWMを使用して正弦波を生成する

率直に言って、このセクションをアクセシブルな言語で表示する方法がわかりません。 突然、わからない人は、追加でグーグルで検索するか、コメントやドラッグを書くように頼みます。個人的に説明しようと思います。 目は怖いが、手はやっている...

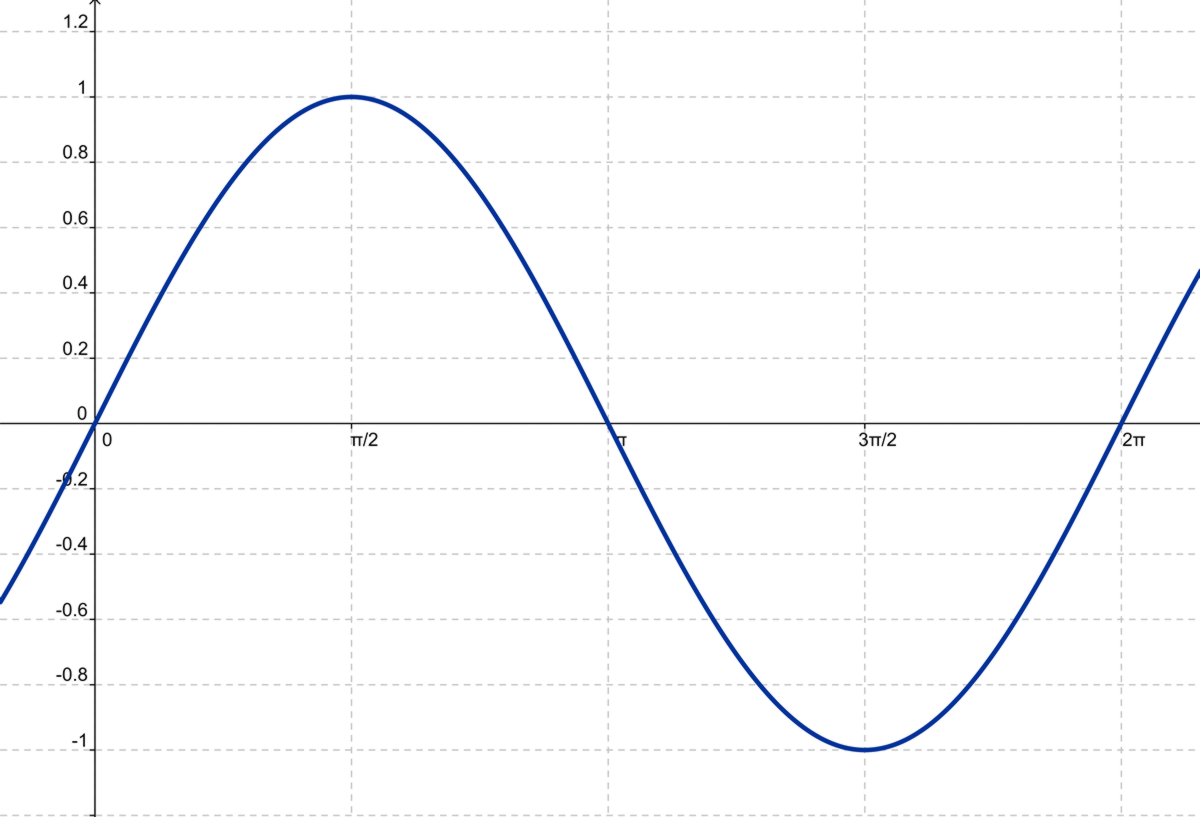

通常のサイングラフがどのように見えるか見てみましょう:

2つの軸があります。1つの軸には周期pi、pi / 2以上があり、2番目の軸には-1〜+1の振幅があります。 このタスクでは、周期は秒単位で測定され、半波ごとに20ミリ秒または10ミリ秒です。 ここではすべてがシンプルで明確ですが、振幅があればもっと楽しくなります-振幅が0から1000であるという公理として受け入れてください。これは、マイクロコントローラが設定するデューティサイクルの値、つまり100は10%、500-50%、900-90です。 % 論理は明確だと思います。 次の章では、0〜1000の理由を理解しますが、今のところは、グラフを値に再構築します。

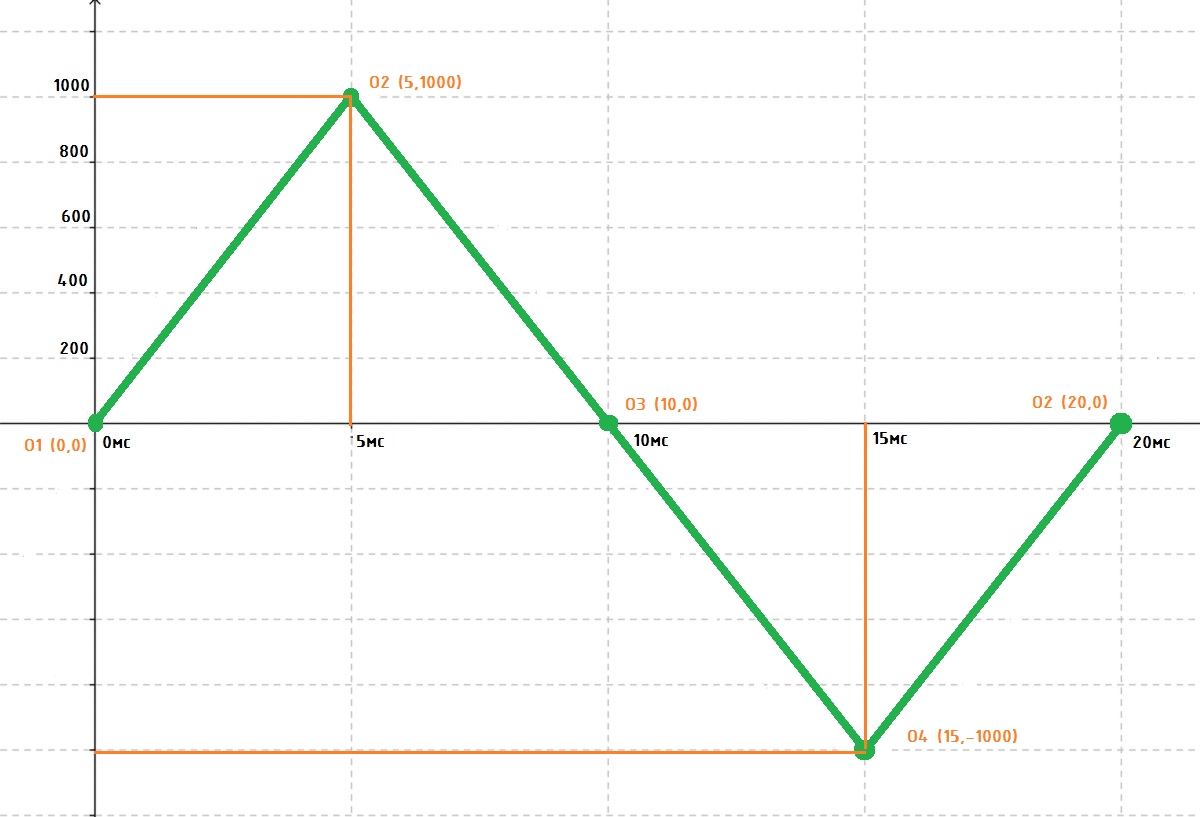

これは

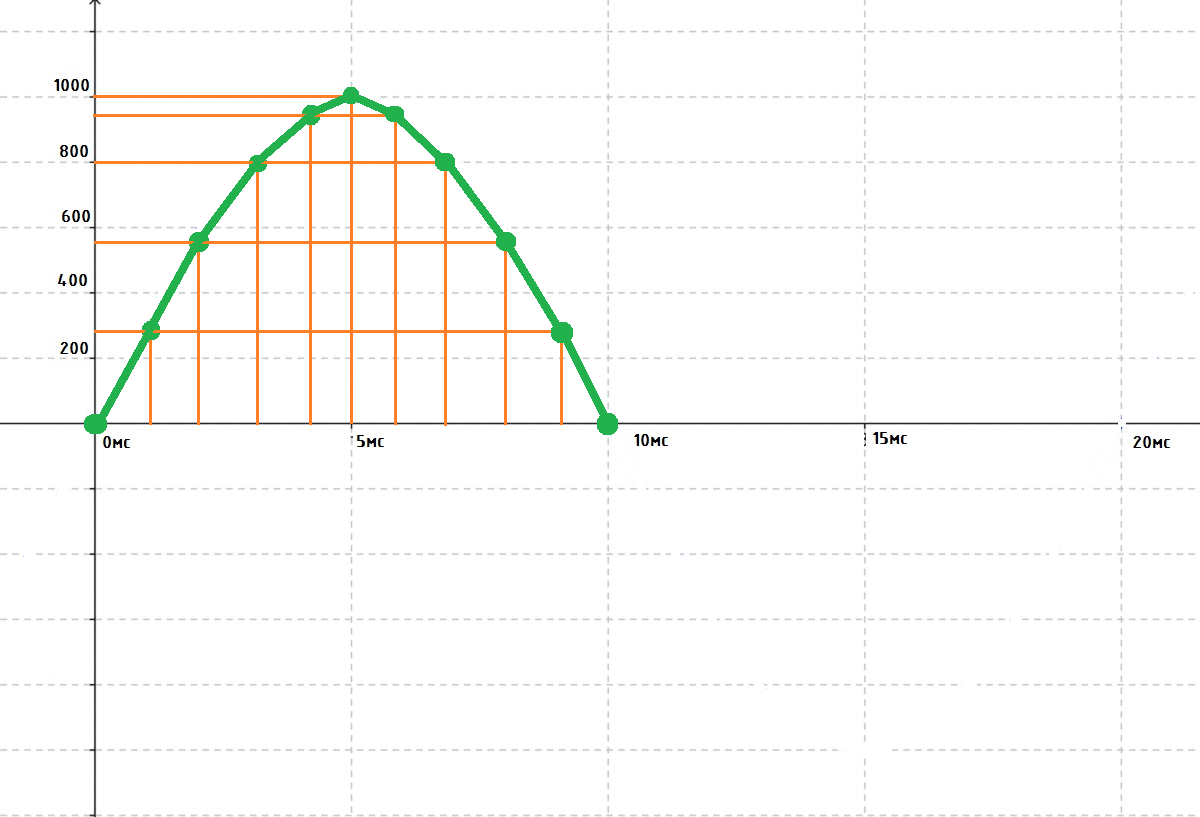

X軸に沿って時間があり、Y軸に沿ってPWM信号のデューティサイクルがあります。 PWMを使用してサインを描く必要があります。 学校でジオメトリを思い出してください。グラフィックをどのように作成しましたか? そう、ポイントで! そして何点ですか? いくつかのポイントでサインを作成してみましょうO1(0,0)+ O2(5,1000)+ O3(10,0)+ O4(15、-1000)+ O5(20、0):そのようなサインを取得します:

私たちはそれを構築し、原則として、この信号は通常の蛇行よりも正弦波に近いことを確認しましたが、今のところまだ正弦波ではありません。 ポイントの数を増やしましょう。 ちなみに、これは「信号離散性」またはこの場合「PWM離散性」と呼ばれます。 そして、これらの点の座標をどのように知っていますか? 極端なことはただでした...

サインの形成の値の計算

上で言ったように、私たちのサインは非常に対称的です。 期間の1/4、つまり0から5ミリ秒を作成し、この部分をさらに複製すると、無限に長いサインを作成できます。 したがって、式は次のとおりです。

そして順番に:

- nは、特定の離散点でのデューティサイクルです。

- Aは信号振幅、つまり最大デューティサイクル値です。 1000個あります

- pi / 2-正弦周期の1/4はpi / 2になります。周期の1/2を考慮すると、pi

- x-ステップ番号

- N-ポイント数

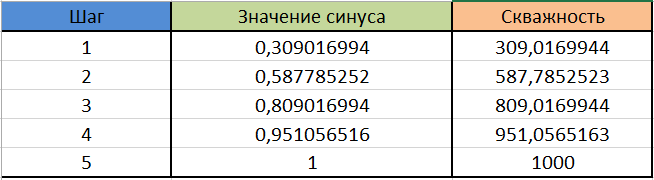

たとえば、5つのポイントがあるという条件を簡単に作成してみましょう。 1ステップ= 1ミリ秒であることがわかります。これにより、グラフを簡単に作成できます。 サンプリングのステップは単純であると考えられます。プロットする期間(5 ms)をポイント数で除算します。 式を人間の心に持ち込もう。

1 msのサンプリングステップを取得します。 たとえば、デューティサイクルを計算するための式をExcelで定式化し、次の表を取得します。

次に、サイングラフに戻って再度作成しますが、さらに多くのポイントについて、それがどのように変化するかを確認します。

あなたが見ることができるように、信号はサインのようです、描画の私のスキルを考慮しても、むしろ、怠lazのレベルで)結果は説明を必要としないと思いますか? 構築結果に基づいて、公理を導き出します。

ドットが多いほど、信号のサンプリングレートが高くなり、正弦波の形状がより理想的になります。

だから、私たちはいくつのポイントを使用しますか...より良いことは明らかです。 カウント方法:

- この記事では、古いマイクロコントローラーSTM32F100RBT6(STM32VL-Discoveryのデバッグ)を使用しています。その周波数は24 MHzです。

- 20ミリ秒の期間が何クロックサイクル続くかをカウントします:24,000,000 Hz / 50 Hz = 480,000ティック

- したがって、周期の半分は24万ティックであり、これは24 kHzの周波数に相当します。 キャリア周波数を上げたい場合は、石をより速く取ります。 24 kHz、私たちの耳にはまだ聞こえますが、テストや地下室の鉄片には聞こえます。 少し後にF103C8T6に転送する予定で、すでに72 MHzあります。

- 240,000ティック...半期間で240ポイントが論理的にここに頼みます。 タイマーは、1000ティックまたは41.6μsごとにデューティサイクルを更新します。

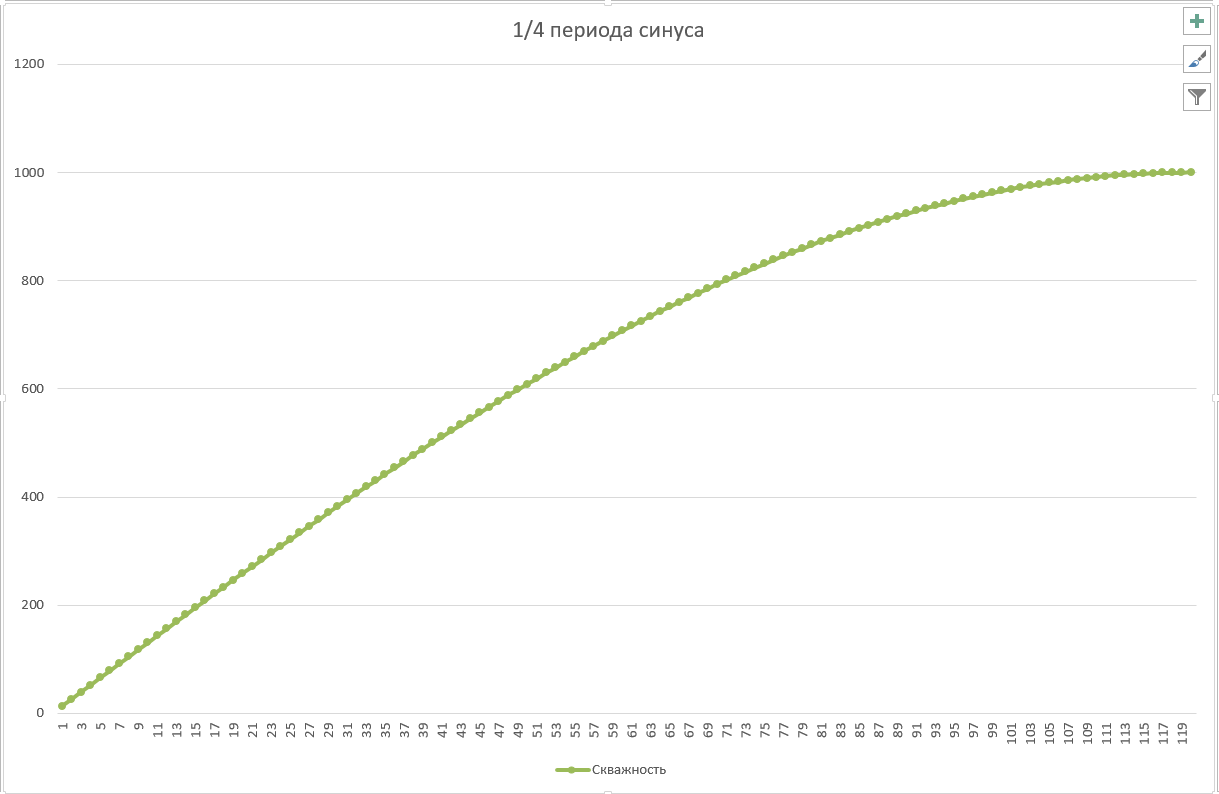

PWMの離散性を決定しました。ネットワーク内と少なくとも同等の波形を得るには、半周期あたり240ポイントでマージンがあれば十分です。 ここで、Excelのテーブルを最も簡単なオプションと見なします。 次のチャートを取得します。

テーブルのソースと値は、リンクから取得できます 。

4.洞形成のためのブリッジコンバーターの管理

サインテーブルがあり、それをどうするか? これらの値を特定のサンプリングステップで送信する必要があります。 それはすべて、タイマーが初期化されたという事実から始まります-時間0、デューティサイクルゼロ。 次に、サンプリングステップ41.66μsをカウントし、テーブル13からPWM値(0.13%)をタイマーに書き込み、別の41.66μsをカウントして26(0.26%)を書き込み、240の値すべてについて同様です。 なぜ240ですか? 1/4周期で120ステップあり、1/2周期を描画する必要があります。 デューティサイクル値は同じです。1000に達した後のみ、逆の順序で書き込み、サインドロップを取得します。 出力には、まさにそのようなオシログラムがあります。

ご覧のとおり、明確に定義された期間に多数のPWM値が得られ、その持続時間は240ステップx 41.66(!)Μs= 9998.4μs= 9.9984 ms〜10 msです。 50 Hzのネットワーク周波数では、期間の半分が得られました。 さらに2つの信号があり、それらは逆位相にあります。ブリッジの対角線を制御するために必要なものです。 しかし、すみません、サインはどこにありますか? 真実の瞬間が来ました! 次に、マイクロコントローラーの出力からの信号をローパスフィルターに適用し、公称値1.5 kOhmと0.33μF(手元にある)のRCチェーン用のシンプルなローパスフィルターを作成し、この結果を得ました。

出来上がり! こちらが待望のサインです! オシロスコープの赤いビームはローパスフィルターの前の信号で、黄色のビームはフィルタリング後の信号です。 ローパスフィルターは、321 Hzを超えるすべての周波数を遮断します。 50 Hzの主信号と、もちろん小さな振幅の高調波があります。 信号を完全にクリアしたい場合は、約55-60 Hzのカットオフ周波数でローパスフィルターを作成しますが、これまでは問題ではありません。サインがあるかどうかを確認する必要がありました。 ちなみに、私のオシロスコープの同期は黄色のビーム(画面右側の矢印)によってオンになり、画面の下部にその周波数(理想的な50 Hz)が表示されます。 さらに何を求めることができますか? おそらく、どの信号とどこに与えるかを決定するためにすべてが残っています。 この写真を見てみましょう:

この記事の最初の波形を見ると、黄色と青色の信号の位相が同じであることがわかります。つまり、同時に正になり、トランジスタが開きます。 これらの2つの信号は、対角線のVT1 + VT4を開きます。 したがって、他の2つの信号も同じ位相を持ち、異なる対角線を開きます。 ここで、電流の方向を変更するだけでなく、正弦波の法則に従って変化するようにPWMを使用して振幅を設定します。 次に、同じ回路を考えますが、電流があります:

ご覧のように、電流は負荷を逆方向に流れ、50 Hzの周波数で方向を変え、トランジスタVT1およびVT2に供給される変調PWMにより、半波で正弦波を描くことができます。

インダクタンスL1とコンデンサC2にローパスフィルター(ローパスフィルター)が作成されます。 このフィルターのカットオフ周波数を100 Hz未満と見なすことをお勧めします。これにより、出力電圧リップルが最小限に抑えられます。

デザートについては、類似のトポロジとフィルターを備えた実際のデバイスのスキームの一部を示します 。サイズが大きいため、 こちらからPDFをダウンロードしてください 。

5.潮流との戦い

完璧なものがないのは秘密ではないと思いますか? Mosfetsでも同じことが言えますが、それらには多くの欠点があり、そのうちの1つである大きなシャッター容量を検討します。 つまり、トランジスタを開くためには、電圧を供給するだけでなく、この電圧でコンデンサを充電する必要があるため、信号の前部と減衰が遅れます。 これにより、信号の境界で、一方のトランジスタがまだ完全に閉じられておらず、もう一方のトランジスタがすでに開き始めている時点が発生する場合があります。

この現象については、たとえばこの記事でさらに読むことをお勧めします。 対処方法を説明します。 トランジスタが次のアームが開く前に正常に閉じるために、制御信号間にデッドタイム、またはより簡単には時間遅延が導入されます。 トランジスタVT3とVT4の制御信号間にこのような遅延が導入されます。 スイッチング半波を提供します。 変調されたPWM(VT1およびVT2)を備えたトランジスタには、すでにこのような遅延があります。正弦は、0%のデューティサイクルで始まり、0%で終わります。 この遅延は1サンプリング時間、つまり41.6μsです。

そしてそう-青と緑の光線/信号間のデッドタイムを実現する必要があります。 どのコントローラーでも、このような遅延はプログラムで行うことができますが、これは良くありません。プログラムはフリーズするか、デバイス

TIM1タイマーが必要です。信号間にハードウェア遅延を挿入できるのは、ソフトウェアの作成に関するセクションでその方法を説明するだけです。次に、結果とその結果を確認します。

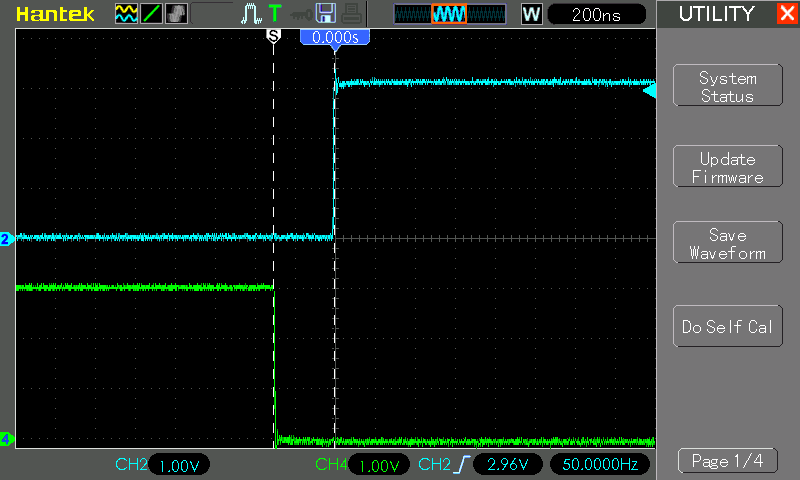

遅延を確認するには、オシロスコープで信号を「ストレッチ」します。持続時間は約300 nsです。トランジスタを貫通電流から保護するために、特定のタスクごとに必要なデッドタイム期間を計算する必要があります。遅延時間は、TIM1タイマーを初期化(設定)するときに設定されます。この遅延は、信号の前部と端部の両方に存在します。

6. STM32マイクロコントローラーのファームウェアの作成

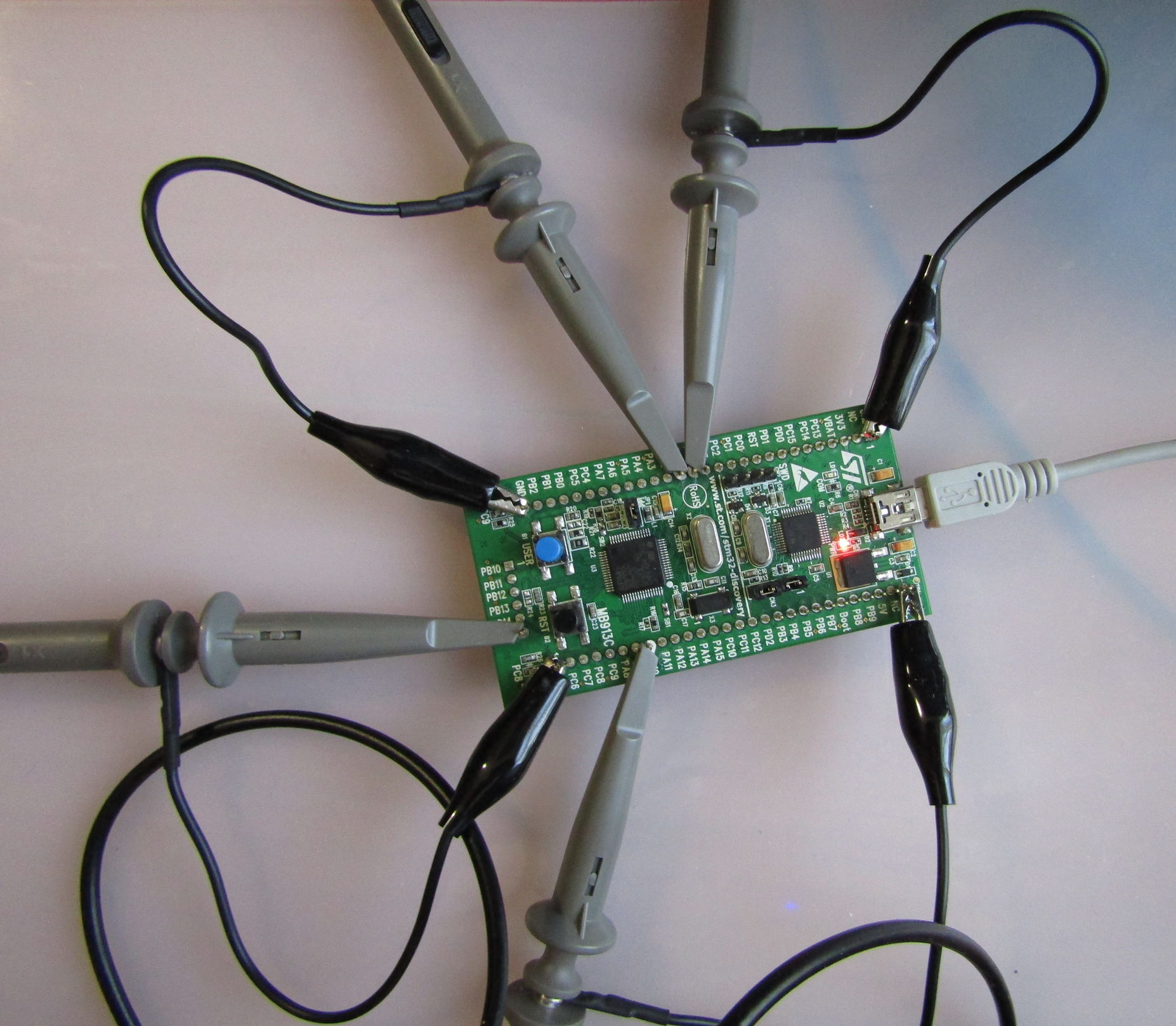

だから、おそらく最も重要で興味深い部分に来ました。プロセスの物理を調べ、動作の原理は明らかであるように見え、必要な最小限の保護も決定されます-これはすべて、実際のハードウェアで実装するだけです。これを行うには、STM32VL-Discoveryスカーフを使用します。2011年に、STが会議で無料でデバッグを配布し、それ以来パッケージ化されました。数か月前にパッケージを開封し、有効期限が切れなかったようです)コードを書くための私の「スタンド」は次のようになります。

それでは接続を行ってみましょう。異なる周波数の2つの信号を生成する必要があるため、異なるタイマーでPWM出力を使用する必要がありました。TIM1は、50 Hzの基本周波数を設定する信号を生成し、それらをトランジスタVT3およびVT4に供給します。使用されているチャネルPWM No. 3 +その相補出力。はい、はい、STM32ハードウェアでは、デッドタイムは1つのチャネルの通常の出力と補完的な出力の間でのみ構成できますが、これは私は本当に好きではありませんでした。サインを形成するプロセスはTIM2タイマーに転送され、遅延の必要はなく(理由は前に書きました)、VT1およびVT2で変調信号を生成するのに非常に適しています。

使用される出力:

- PA10-通常のPWM出力、TIM1タイマーのチャネル#3、50 HzからVT3トランジスタを生成

- PB15-トランジスタVT4に供給されるタイマーTIM1のチャネル3の相補出力

- PA0 — №1 TIM2. VT1

- PA1 — №2 TIM2. VT2

このプロジェクトはKeil 5環境に実装されており、記事の最後にアーカイブに添付されます。プロジェクトの作成方法や同様の明白なことを説明するつもりはありません。そのような質問が発生した場合は、Googleまたはyoutubeでそれを行う方法を確認することをお勧めします。すべてのコードはCMSIS(レジスタ)で記述されています。コンバーター制御システムで追加の抽象化レベルを使用することは、単に罪です! STでは、これらはSPLライブラリと最新のHALです。興味を持って、私はそれらとそれらの両方で働きました、結論は完全なゴミです。 HALは一般にめちゃくちゃ遅いので、ハードリアルタイムを使用するアプリケーションの場合は、まったく言葉に合いません。いくつかの重要な瞬間に、インターネット上で複数の記事を見つけたために、レジスタは何倍も高速になりました。

「なぜDMAを使用しないのですか?」DMAは優れていますが、潜在的な問題なしにDMAなしで実行できます。プログラムで何をする必要があるかを明確にしましょう。

- 240個のサインポイントを含む配列を作成する

- 外部水晶振動子ソースを選択して、クロック回路を24 MHzの周波数に調整します

- デッドタイムを有効にして50 Hz PWMを生成するようにTIM1を設定します

- TIM2を設定して、24 kHzの搬送周波数でPWMを生成します

- 24 kHzの周波数で割り込みを生成するタイマーTIM6を設定します。その中で、次のデューティサイクル値をテーブルからTIM2タイマーに送信し、半波の生成も交互に行います

複雑なことはありませんか?それでは行こう...

6.1。 サインテーブルの作成

それは単純な、普通の配列です。覚えておく価値がある唯一のことは、0から1000までの120ポイントがあることです。テーブルにさらに120ポイントを追加する必要がありますが、逆の順序です。

uint16_t sin_data[240] = {13,26,39,52,65,78,91,104,117,130,143,156,169,182,195,207,220,233,246,258, 271,284,296,309,321,333,346,358,370,382,394,406,418,430,442,453,465,477,488,500, 511,522,533,544,555,566,577,587,598,608,619,629,639,649,659,669,678,688,697,707, 716,725,734,743,751,760,768,777,785,793,801,809,816,824,831,838,845,852,859,866, 872,878,884,891,896,902,908,913,918,923,928,933,938,942,946,951,955,958,962,965, 969,972,975,978,980,983,985,987,989,991,993,994,995,996,997,998,999,999,999,1000, 999,999,999,998,997,996,995,994,993,991,989,987,985,983,980,978,975,972,969,965, 962,958,955,951,946,942,938,933,928,923,918,913,908,902,896,891,884,878,872,866, 859,852,845,838,831,824,816,809,801,793,785,777,768,760,751,743,734,725,716,707, 697,688,678,669,659,649,639,629,619,608,598,587,577,566,555,544,533,522,511,500, 488,477,465,453,442,430,418,406,394,382,370,358,346,333,321,309,296,284,271,258, 246,233,220,207,195,182,169,156,143,130,117,104,91,78,65,52,39,26,13};

6.2。クロックシステムのセットアップ

STM32でのクロックの設定は非常に柔軟で便利ですが、いくつかの微妙な違いがあります。シーケンス自体は次のとおりです

。1)内蔵RCチェーン(HSI)から外部クオーツ(HSE)へのクロッキングに切り替えてから、準備完了フラグを待ちます

RCC->CR |= ((uint32_t)RCC_CR_HSEON); // Enable HSE while (!(RCC->CR & RCC_CR_HSERDY)); // Ready start HSE

2)コントローラーのフラッシュメモリはカーネルよりわずかに遅いため、フラッシュのタイミングを構成します。これを行わないと、プログラムは起動しますが、定期的に低下します。数キロワットと不安定なソフトウェアは互換性がありません。

FLASH->ACR = FLASH_ACR_PRFTBE | FLASH_ACR_LATENCY; // Cloclk Flash memory

3)システムクロックバス(AHB)およびペリフェラルバスの分周器を設定します。これらのバスにはすでにAPB1とAPB2の2つの部分があります。最大頻度が必要なので、何も除算せず、係数を1で除算します。

RCC->CFGR |= RCC_CFGR_HPRE_DIV1; // AHB = SYSCLK/1 RCC->CFGR |= RCC_CFGR_PPRE1_DIV1; // APB1 = HCLK/1 RCC->CFGR |= RCC_CFGR_PPRE2_DIV1; // APB2 = HCLK/1

4)周波数逓倍器(PLL)を設定し、その前に立って水晶周波数を2で除算するプリディバイダーを設定します。8MHzを2で除算し、4 MHzを受信しました。次に、出力が24 MHzになるように6を掛ける必要があります。レジスタを書き込む前に、念のため最初にその内容を消去してください。

RCC->CFGR &= ~RCC_CFGR_PLLMULL; // clear PLLMULL bits RCC->CFGR &= ~RCC_CFGR_PLLSRC; // clearn PLLSRC bits RCC->CFGR &= ~RCC_CFGR_PLLXTPRE; // clearn PLLXTPRE bits RCC->CFGR |= RCC_CFGR_PLLSRC_PREDIV1; // source HSE RCC->CFGR |= RCC_CFGR_PLLXTPRE_PREDIV1_Div2; // source HSE/2 = 4 MHz RCC->CFGR |= RCC_CFGR_PLLMULL6; // PLL x6: clock = 4 MHz * 6 = 24 MHz

5)次に、周波数逓倍器(PLL)をオンにして、準備完了フラグを待つ必要があります。

RCC->CR |= RCC_CR_PLLON; // enable PLL while((RCC->CR & RCC_CR_PLLRDY) == 0) {} // wait till PLL is ready

6)最後に、周波数逓倍器のシステムバス(AHB)出力のクロックソースを構成します。まず、レジスタの内容をクリアし、目的のビットを設定して、準備完了フラグを待ちます。

RCC->CFGR &= ~RCC_CFGR_SW; // clear SW bits RCC->CFGR |= RCC_CFGR_SW_PLL; // select source SYSCLK = PLL while((RCC->CFGR & RCC_CFGR_SWS) != RCC_CFGR_SWS_1) {} // wait till PLL is used

その結果、クロックを設定するための次の関数を取得します。

void RCC_Init (void){ RCC->CR |= ((uint32_t)RCC_CR_HSEON); // Enable HSE while (!(RCC->CR & RCC_CR_HSERDY)); // Ready start HSE FLASH->ACR = FLASH_ACR_PRFTBE | FLASH_ACR_LATENCY; // Cloclk Flash memory RCC->CFGR |= RCC_CFGR_HPRE_DIV1; // AHB = SYSCLK/1 RCC->CFGR |= RCC_CFGR_PPRE1_DIV1; // APB1 = HCLK/1 RCC->CFGR |= RCC_CFGR_PPRE2_DIV1; // APB2 = HCLK/1 RCC->CFGR &= ~RCC_CFGR_PLLMULL; // clear PLLMULL bits RCC->CFGR &= ~RCC_CFGR_PLLSRC; // clearn PLLSRC bits RCC->CFGR &= ~RCC_CFGR_PLLXTPRE; // clearn PLLXTPRE bits RCC->CFGR |= RCC_CFGR_PLLSRC_PREDIV1; // source HSE RCC->CFGR |= RCC_CFGR_PLLXTPRE_PREDIV1_Div2; // source HSE/2 = 4 MHz RCC->CFGR |= RCC_CFGR_PLLMULL6; // PLL x6: clock = 4 MHz * 6 = 24 MHz RCC->CR |= RCC_CR_PLLON; // enable PLL while((RCC->CR & RCC_CR_PLLRDY) == 0) {} // wait till PLL is ready RCC->CFGR &= ~RCC_CFGR_SW; // clear SW bits RCC->CFGR |= RCC_CFGR_SW_PLL; // select source SYSCLK = PLL while((RCC->CFGR & RCC_CFGR_SWS) != RCC_CFGR_SWS_1) {} // wait till PLL is used }

6.3。TIM1タイマーとデッドタイムの設定

一般的なタイマー設定について説明します。詳細はリファレンスマニュアルに記載されています。各レジスタの目的を読むことをお勧めします。はい。インターネットでPWMを操作するための基本的な記事があります。コード自体は非常によくコメントされているので、すぐにタイマー初期化関数TIM1のコードを提供し、最も興味深い点を分析します。

void PWM_50Hz_Init (void){ RCC->APB2ENR |= RCC_APB2ENR_TIM1EN; // enable clock for TIM1 RCC->APB2ENR |= RCC_APB2ENR_IOPAEN; // enable clock for port A RCC->APB2ENR |= RCC_APB2ENR_IOPBEN; // enable clock for port B RCC->APB2ENR |= RCC_APB2ENR_AFIOEN; // enable clock for alternative gpio /****************************** Setting PA10 **************************************/ GPIOA->CRH &= ~GPIO_CRH_CNF10; // setting out alternative push-pull for PWM GPIOA->CRH |= GPIO_CRH_CNF10_1; GPIOA->CRH &= ~GPIO_CRH_MODE10; GPIOA->CRH |= GPIO_CRH_MODE10; // gpio speed 50 MHz /***************************** Setting PB15 ***************************************/ GPIOB->CRH &= ~GPIO_CRH_CNF15; // setting complementary for CH3N GPIOB->CRH |= GPIO_CRH_CNF15_1; GPIOB->CRH &= ~GPIO_CRH_MODE15; GPIOB->CRH |= GPIO_CRH_MODE15; // gpio speed 50 MHz /************************** Config PWM channel ************************************/ TIM1->PSC = 480-1; // div for clock: F = SYSCLK / [PSC + 1] TIM1->ARR = 1000; // count to 1000 TIM1->CR1 &= ~TIM_CR1_CKD; // div for dead-time: Tdts = 1/Fosc = 41.6 ns TIM1->CCR3 = 500; // duty cycle 50% TIM1->CCER |= TIM_CCER_CC3E | TIM_CCER_CC3NE; // enable PWM complementary out TIM1->CCER &= ~TIM_CCER_CC3NP; // active high level: 0 - high, 1 - low TIM1->CCMR2 &= ~TIM_CCMR2_OC3M; TIM1->CCMR2 |= TIM_CCMR2_OC3M_2 | TIM_CCMR2_OC3M_1; // positiv PWM TIM1->BDTR &= ~TIM_BDTR_DTG; // clear register TIM1->BDTR |= TIM_BDTR_DTG_2 | TIM_BDTR_DTG_1 | TIM_BDTR_DTG_0; // value dead-time TIM1->BDTR |= TIM_BDTR_MOE | TIM_BDTR_AOE; // enable generation output /*******************************************************************************/ TIM1->CR1 &= ~TIM_CR1_DIR; // count up: 0 - up, 1 - down TIM1->CR1 &= ~TIM_CR1_CMS; // aligned on the front signal TIM1->CR1 |= TIM_CR1_CEN; // start count }

当社の信頼性は固定されており、周波数のように変化することはありません。対角線の時間とシーケンスを設定するのはこのタイマーです:

TIM1->CCR3 = 500; // duty cycle 50%

「デッドタイム」の一時停止の期間は、ここで設定されるTDTS時間パラメータに大きく依存します。

TIM1->CR1 &= ~TIM_CR1_CKD; // div for dead-time: Tdts = 1/Fosc = 41.6 ns

その期間は1ティックのクロック周波数です。リファレンスマニュアルを見ると、CKDビットによって、たとえば、Tdtsが2、8ティックなどに等しくなることがわかります。

非常に一時停止する時間はここで設定されます:

TIM1->BDTR |= TIM_BDTR_DTG_2 | TIM_BDTR_DTG_1 | TIM_BDTR_DTG_0;

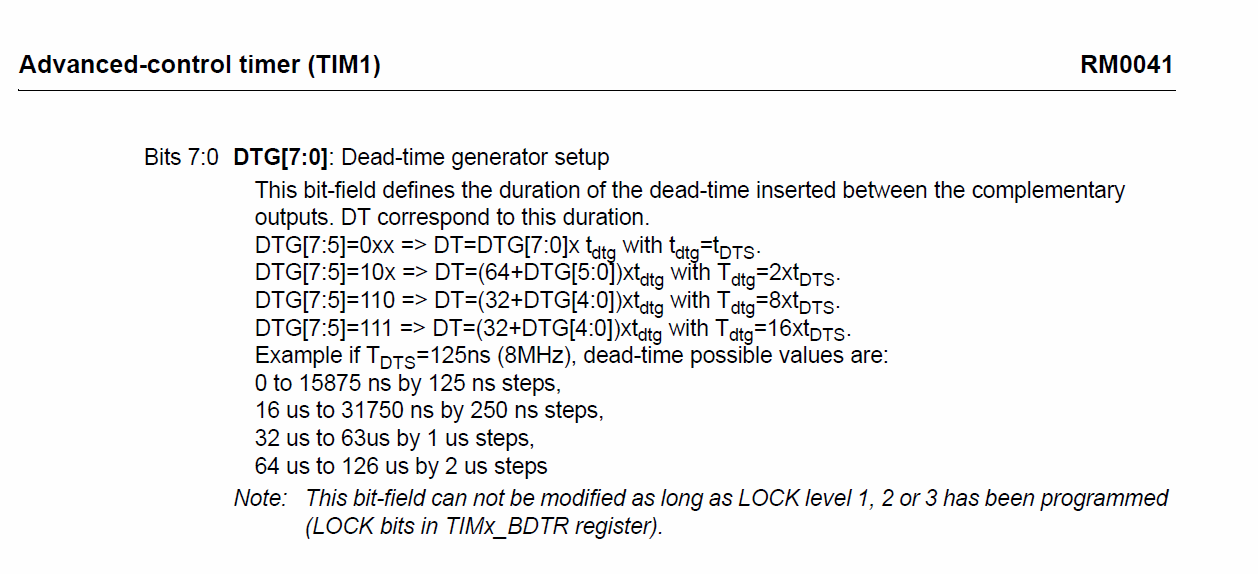

リファレンスマニュアルRM0041を開くと、DTを計算するためのそのような式が表示されます。ご覧のとおり、Tdtsパラメーターは基本的なものです。

6.4。サインを形成するためのTIM2タイマーの設定

ここではまだ簡単です。コメントはすでに冗長であるため、セットアップで何かを説明する理由はおそらくないでしょう。ご質問がある場合は、コメントでお待ちしています。

void PWM_Sinus_Init (void){ RCC->APB1ENR |= RCC_APB1ENR_TIM2EN; // enable clock for TIM2 RCC->APB2ENR |= RCC_APB2ENR_IOPAEN; // enable clock for port A RCC->APB2ENR |= RCC_APB2ENR_AFIOEN; // enable clock for alternative gpio /****************************** Setting PA0 ***************************************/ GPIOA->CRL &= ~GPIO_CRL_CNF0; // setting out alternative push-pull for PWM1_CH1 GPIOA->CRL |= GPIO_CRL_CNF0_1; GPIOA->CRL &= ~GPIO_CRL_MODE0; GPIOA->CRL |= GPIO_CRL_MODE0; // gpio speed 50 MHz /****************************** Setting PA1 ***************************************/ GPIOA->CRL &= ~GPIO_CRL_CNF1; // setting out alternative push-pull for PWM1_CH1 GPIOA->CRL |= GPIO_CRL_CNF1_1; GPIOA->CRL &= ~GPIO_CRL_MODE1; GPIOA->CRL |= GPIO_CRL_MODE1; // gpio speed 50 MHz /*************************** Config PWM channel ***********************************/ TIM2->PSC = 0; // div for clock: F = SYSCLK / [PSC + 1] TIM2->ARR = 1000; // count to 1000 TIM2->CCR1 = 0; // duty cycle 0% TIM2->CCR2 = 0; // duty cycle 0% TIM2->CCER |= TIM_CCER_CC1E; // enable PWM out to PA8 TIM2->CCER &= ~TIM_CCER_CC1P; // active high level: 0 - high, 1 - low TIM2->CCER |= TIM_CCER_CC2E; // enable PWM complementary out to PA9 TIM2->CCER &= ~TIM_CCER_CC1P; // active high level: 0 - high, 1 - low TIM2->CCMR1 &= ~(TIM_CCMR1_OC1M | TIM_CCMR1_OC2M); TIM2->CCMR1 |= TIM_CCMR1_OC1M_2 | TIM_CCMR1_OC1M_1 | TIM_CCMR1_OC2M_2 | TIM_CCMR1_OC2M_1; // positiv PWM1_CH1 and PWM1_CH2 /*******************************************************************************/ TIM2->CR1 &= ~TIM_CR1_DIR; // count up: 0 - up, 1 - down TIM2->CR1 &= ~TIM_CR1_CMS; // aligned on the front signal: 00 - front; 01, 10, 11 - center TIM2->CR1 |= TIM_CR1_CEN; // start count }

6.5。TIM6タイマー割り込みの設定

タイマー自体を24 kHzの周波数で構成します。

void TIM6_step_init (void){ RCC->APB1ENR |= RCC_APB1ENR_TIM6EN; // enable clock for basic TIM6 TIM6->PSC = 1-1; // div, frequency 24 kHz TIM6->ARR = 1000; // count to 1000 TIM6->DIER |= TIM_DIER_UIE; // enable interrupt for timer TIM6->CR1 |= TIM_CR1_CEN; // start count NVIC_EnableIRQ(TIM6_DAC_IRQn); // enable interrupt TIM6_DAC_IRQn }

6.6。基本的な制御アルゴリズムの実装

主要なイベントは、TIM6タイマーによって生成された割り込みで発生します。これがサンプリング手順であることを覚えていれば、41.66μsごとに割り込みが生成されます。したがって、割り込みでは、デューティサイクル値がテーブルからCCRxレジスタに書き込まれます。また、この割り込みでは、各半周期後にsin_statusフラグを反転することにより、現在どの対角線が描画されているかが決定されます。240ポイントを表示し、フラグを反転します。これにより、コントロールが別のチャネルに切り替えられます。すでに描画されている場合、フラグは再び反転され、すべてが繰り返されます。メインアルゴリズムのコード:

void TIM6_DAC_IRQHandler(void){ TIM6->SR &= ~TIM_SR_UIF; if(sin_status == 0){TIM2->CCR1 = sin_data[sin_step];} if(sin_status == 1){TIM2->CCR2 = sin_data[sin_step];} sin_step++; if(sin_step >= 240){ sin_step=0; sin_status = sin_status ? 0 : 1; } }

まとめ

プロジェクトをダウンロードし、コンパイルしてマイクロコントローラーに入力し、動作するインバーターを取得します。ブリッジを作成して信号を送信する

だけです。以前のPDFのブリッジ回路の1つに好きなだけ置くことができます。パワーエレクトロニクスの習得に役立つことを願っています。

また、FreeRTOSをプロジェクトに取り込みました。もちろん、RTOSを使用してこのような管理タスクを実装することはできません。タスク間の単純な切り替えは4〜18マイクロ秒続きます。これは、コードが適切に記述されていて、スケジューラに干渉するものがない場合です。これにより、ハードリアルタイムで動作する制御システムを取得できません。 FreeRTOSを別の通信インターフェイス(RS-485 Modbus RTU)、電圧出力振幅調整、テーブル変換、230Vネットワークとの同期などに設定しました。また、これらすべてのバンをSTM32に実装しようとします。興味深い結果が得られ、共有できるものがある場合は、おそらく記事のトピックの続きを作成します。

記事をお楽しみください。このコードを実際のハードウェアで使用することについて質問がある場合は、喜んでお答えします。また、このコードを準備ができたものとして受け取らないようにお願いします。これは、メイン関数を実装するコンバーターのコアです。すべての「バン」およびその他の冗長性を自分で追加できます。プロジェクトのコアは、コードの分解に多くの時間を費やすことなく、プロジェクトの仕組みを理解できるようにします。

素材

UPD1:主に正弦テーブルで見つかった多くのエラーについて、ユーザーsleipに感謝します-変更されました。コードまたはテーブル自体を使用した人は、もう一度コピーしてください。記事にはすでに修正版があります。