半導体産業は、「System on Crystal」レベルの超小型回路の集積度を達成した標準0.18μm以下の技術プロセスを習得してきたため、このような超小型回路に実装された機能ブロックの内部ジョイントについて多くの仕様が登場しました。 ほとんどの場合、これらのジョイントは、AMBA APB、AHB、AXI、ウィッシュボーン、OCP [1、2、3、4、5、6]などの同期システムバスで表されます。 バスとは関係のない元のトポロジも提案されました。たとえば、クリスタルネットワーク-NOC(Networks-On-Chip)[7]です。

この出版物の主題領域は、VLSIまたはFPGAチップの境界を超えることなく、コンピューティングデバイスの機能ブロックの関係の構築に限定されています。 このような接続の特徴は、交換プロトコルに関係する信号線の数に大きな制限がないことです。 この機能は、水晶ボリュームに追加の信号を導入すると、トランジスタリソースを占有する論理回路が大幅に簡素化される一方、トレースリソースはそれほど多くないためです。 また、RTLレベルモデルで明示的に記述された一部の信号は、組み合わせロジックの最適化により、合成回路および技術要素のレベルの接続リストで利用できない場合があることに注意してください。

チップ内システムバスの既存の仕様のほとんどは、遅延トランザクション、ブロック転送(バーストモード)、プリフェッチ可能な読み取り、トランザクションの中止、要求の再試行を定義する高度なプロトコルを使用しています。 この機能には、すべてのバスエージェントからのサポートが必要であり、制御マシンのスイッチングアルゴリズムが大幅に複雑になりますが、多くの場合は使用されません。 特に、水晶の低速または単純な周辺ブロックへのアクセスを整理する場合は冗長です。

たとえば、Wishboneバス[5]などの仕様では、エージェントを相互に接続する原理は規制されておらず、イニシエーター(イニシエーター)とエグゼキューター(ターゲット)のインターフェースのみが定義されています。

既存のインターフェースの主な利点は、開発および検証された幅広い機能ブロック(IPコア)です。

西洋でずっと前に開発された水晶バスシステム用の標準プロトコルを使用することに慣れている多くの開発者が疑問を抱く可能性があります。 最初に、新しい仕様を作成する主な目標は、すべてのジョイント、バスへの接続に関するエージェントの内部組織、およびバス自体のインフラストラクチャの構築方法を管理する最も単純な同期システムインターフェイスを記述することでした。 第二に、元の仕様は英語ではなくロシア語で作成する必要があります。

開発目標を定義し、サブジェクト領域を制限した後、インターフェイス仕様の直接調査に移ります。

バージョン1.0の単純なエグゼキューター-Simple Target Interface v.1.0(以降-STI)のジャンクションは、1つのFPGA構成プロジェクトまたはVLSIチップ(以降-プロジェクト)のボリューム内のいくつかの機能ブロックの接続を提供する論理信号と対話プロトコルのセットです。

プロジェクト記述のRTLモデルでは、STIインターフェイスの数に制限はなく、同時に、互いに独立して並行して動作できます。 これらの各インターフェイスは、以降STIセグメントと呼ばれます。

同じSTIセグメント内の相互作用は1つのプロジェクト同期ドメインに実装されます。つまり、1つのSTIセグメントで接続されたイニシエーターとすべてのアーティストに単一のクロック信号(CLK)を使用します。

共通STIセグメントによって接続されたプロジェクト機能ブロックのセットには、1つ(および1つのみ)の交換イニシエーターと交換エグゼキューターのセットが含まれ、これらはこのセットの残りのブロックによって表されます。

STIインタラクション方式は、コンピューティングデバイスのプロセッサのアドレススペースの1つにある特定のアドレスで利用可能なデータワードの書き込みと読み取りで構成されます。 ワード幅は、特定のSTIセグメント用に選択されたインターフェイス実装のデータパスのビット深度によって決定され、8、16、32、または64ビットにすることができます。

データの単一ワードの書き込みまたは読み取りは、STIインターフェースを介した交換サイクル(以降、サイクルと呼びます)です。

STIデータ交換は、セグメント内の交換を開始する唯一のブロック(以降、イニシエーターと呼びます)から始まります。 共通STIセグメントに接続された交換エグゼキューター(以下、エグゼキューターと呼ぶ)のいくつかのブロックが存在する場合があります。 実行者の最大数は、開発者によるVLSIプロジェクトの実装に依存し、このプロトコルによって規制されません。 ただし、パフォーマンスの最適化のため、8人を超えるアーティストを1つのSTIセグメントに接続することはお勧めしません。 STIセグメントに2つ以上のパフォーマーが存在する場合、読み取りパスでのデータ切り替えと制御信号の切り替えは、組み合わせ回路を組み合わせて実行されます。 複数のアーティストが、選択されたアドレススペース(STIコマンド)に基づいて、または合計アドレススペースの量で選択されたアドレス範囲に基づいて切り替えられます。

書き込みサイクルでは、イニシエーターからエグゼキューターにデータが転送され、読み取りサイクルでは、反対方向にデータが転送されます。 同時読み取りおよび書き込み操作の複合サイクル、このSTIプロトコルは許可しません。

アドレス空間の選択は、STIコマンド(S_CMD)でエンコードされます。 選択したアドレス空間の量のアドレスは、アドレスパス(S_ADDR)に沿ったすべてのサイクルでイニシエーターからエグゼキューターに転送されます。

アドレスパスの幅は、開発者によるプロジェクトの実装に依存し、このプロトコルによって規制されません。 一部の機能ブロックでは、請負業者がシステムアドレス空間の1つの組み合わせ(書き込み用に1つのレジスターおよび/または読み取り用に1つのレジスター)を使用する場合、STIジャンクションのアドレスパスが存在しない場合があります。

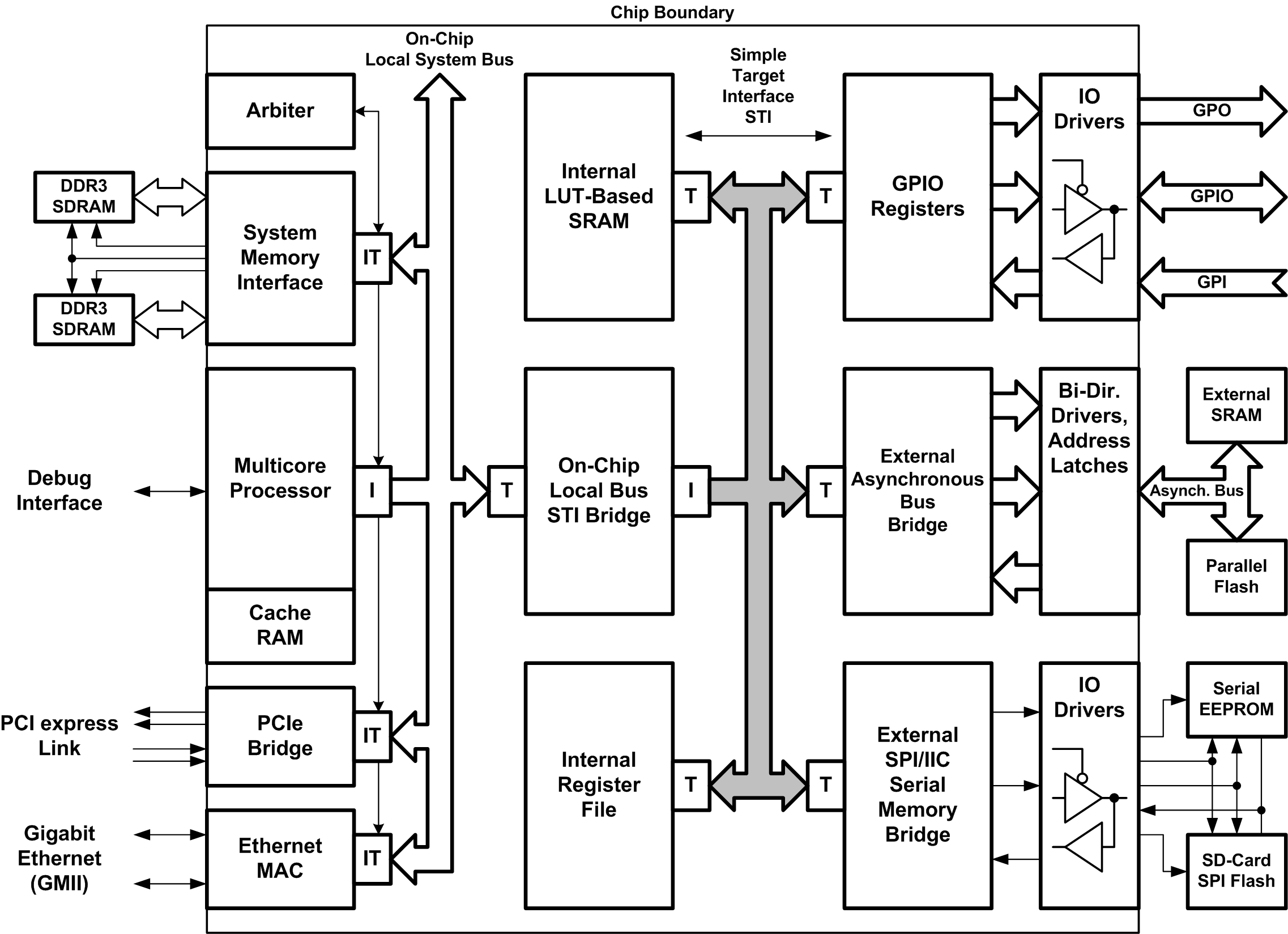

「システムオンチップ」クラス(SoC)のVLSIチップの例でのSTIインターフェイスの場所は、図2に示すブロック図に示されています。 1. STIセグメントに関連する関係は灰色で強調表示されます。

図 1. VLSIチップのボリューム内のSTIインターフェイスの場所

STIジャンクションを使用すると、ローカルバスイニシエーター機能のサポートを必要としないプロジェクト機能ブロックを簡単に接続できます。 STIプロトコルは、各クロックサイクルでデータワードを読み書きする機能を提供し、同じビット深度とクロック周波数で、完全に機能するシステムバスのレベルで帯域幅を提供します。

STIエグゼキューターの参加によるデータ配列のブロック転送は、STIセグメントブリッジの一部として実装されるダイレクトメモリアクセスプロセッサ-DMAによって、またはSTIセグメントブリッジにアクセスするローカルシステムバスに接続されたイニシエーターを持つ他のブロックによって実行できます。

STIセグメントのボリューム内のエージェントの通信トポロジーを考慮してください。

STIセグメントの相互作用は、表1に示す信号セットを使用します。

表1

| 8ページ データパス | 16ページ データパス | 32ページ データパス | 64ページ データパス | イニシエーター | 出演者 |

|---|---|---|---|---|---|

| S_EX_REQ | S_EX_REQ | S_EX_REQ | S_EX_REQ | クエリリクエスト | 入力をリクエスト |

| S_ADDR [n-1:0] / S_ADDR_0 | S_ADDR [n-1:1] / S_ADDR_1 | S_ADDR [n-1:2] / S_ADDR_2 | S_ADDR [n-1:3] / S_ADDR_3 | アドレス出力 | 住所入力 |

| いや | S_NBE [1:0] | S_NBE [3:0] | S_NBE [7:0] | バイト解像度出力 | バイト解像度入力 |

| S_CMD [2:0] | S_CMD [2:0] | S_CMD [2:0] | S_CMD [2:0] | コマンドコード出力 | コマンドコード入力 |

| S_D_WR [7:0] | S_D_WR [15:0] | S_D_WR [31:0] | S_D_WR [63:0] | 書き込みデータ出力 | 記録用データ入力 |

| S_EX_ACK | S_EX_ACK | S_EX_ACK | S_EX_ACK | 確認ログイン | 確認出力 |

| S_D_RD [7:0] | S_D_RD [15:0] | S_D_RD [31:0] | S_D_RD [63:0] | データ入力の読み取り | データ出力の読み取り |

| CLK | CLK | CLK | CLK | クロック入力 | クロック入力 |

| Rst | Rst | Rst | Rst | システムリセット入力 | システムリセット入力 |

STIエグゼキューターによるハードウェア割り込み要求のシグナルには、STIセグメントに関連しないサイドバンド信号を使用できます。その制御順序は、各プロジェクトの開発者によって制御されます。

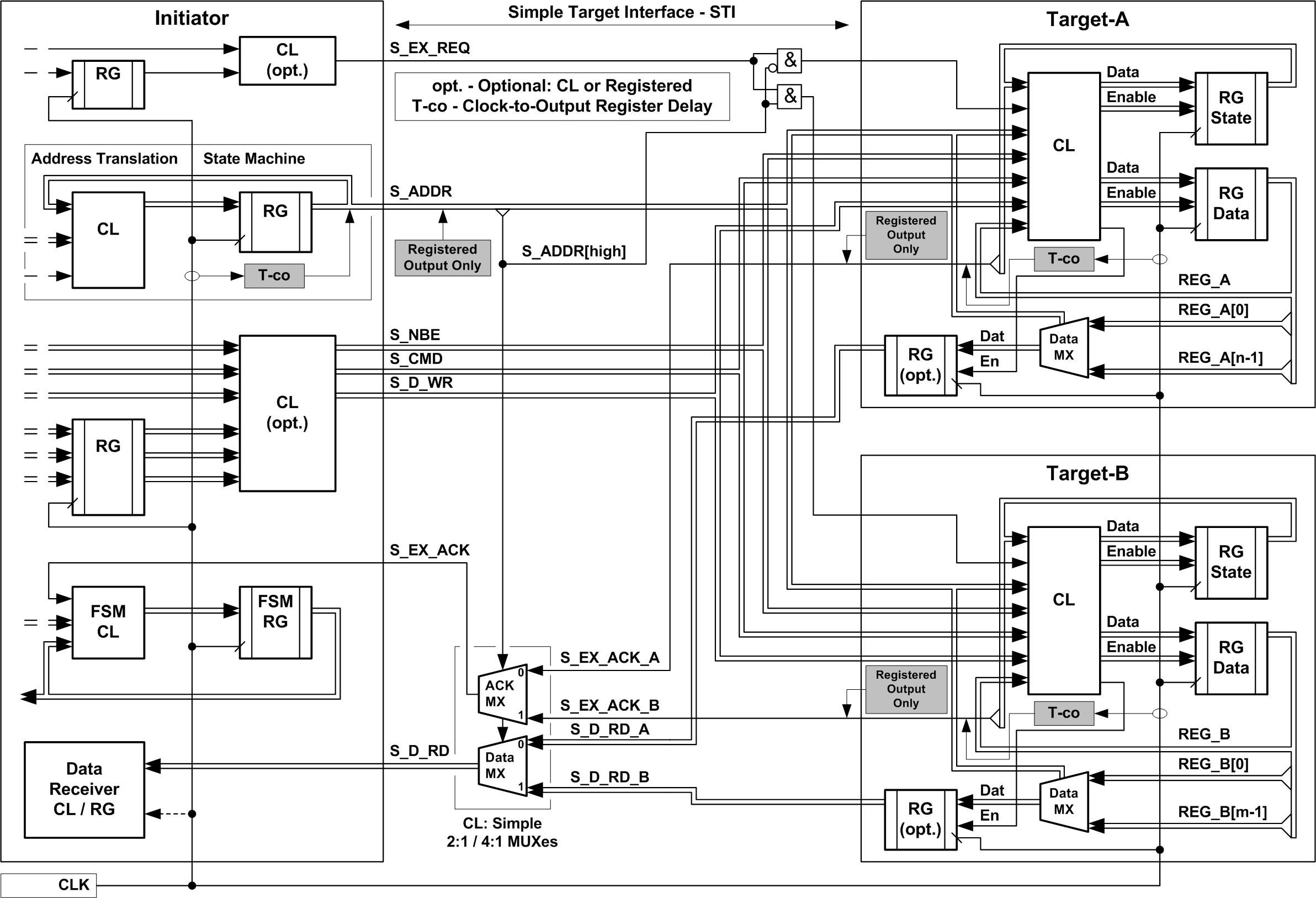

1つのSTIセグメントのボリューム内の論理信号の接続のトポロジを図5に示します。 2.この例では、2人のパフォーマーの切り替え、およびパフォーマーとイニシエーターの入力と出力の構成が示されています。 パフォーマーの転流は、アドレススペースを2つの等しい部分に分割することによって行われます。 したがって、S_ADDR [n-1]アドレスの高位ビットの低レベルでは、ターゲットAエグゼキューターが選択され、高レベルでは、ターゲットBが選択されます。 アドレスの組み合わせだけでなく、アドレススペースを分離するためのコマンドコードも、パフォーマーを選択するロジックに含めることができます。

図 2. STIセグメントの接続トポロジ

STIインターフェイスイニシエーターインターフェイスのトポロジには、次の制限が課されます。

- S_ADDRアドレスの出力には、CLK信号に同期したレジスタ出力の形式のソースが必要です。 したがって、クロック信号の動作エッジからのS_ADDRの出力の遅延は、トリガーT-coの出力遅延(Clock-to-Output遅延)に等しくなります。

- イニシエーター出力信号の残りは、入力信号S_EX_ACKおよびS_D_RDに応答しない組み合わせ回路、またはレジスターによって生成できます。

STIインターフェイスエグゼキューターインターフェイスのトポロジには、次の制限が課せられます。

- ループ確認出力S_EX_ACKには、CLK信号によって同期化されたレジスタ出力の形式のソースが必要です。 したがって、クロック信号の動作エッジからの出力遅延S_EX_ACKは、T-coトリガーの出力遅延(Clock-to-Output遅延)に等しくなります。 書き込み交換サイクルと読み取り交換サイクルで待機サイクルを導入しない実行者の場合、高レベル定数の形式でS_EX_ACK信号を生成することができます。

- S_D_RDバスに出力レジスタがない場合、データ読み取りパスのマルチプレクサは、エグゼキュータのボリューム内の内部レジスタの出力(CLK信号に同期)、またはアドレスバスS_ADDR [n-1:k]の入力ビットのサブセットによって制御する必要があります。

STIジャンクションでのイニシエーターおよびエグゼキューターインターフェイスのトポロジーのリストされた要件は、複雑な組み合わせループの生成を除外する必要があるために発生します。

同じSTIセグメント内で複数のパフォーマーを切り替える組み合わせ回路の接続は、S_EX_REQ要求回路の「AND」論理ゲートと、イニシエーターの共通入力へのパフォーマー出力のマルチプレクサーによって表されます。 リンク論理構築の例を図に示します。 2。

プロジェクトの合成モデルでは、組み合わせ論理の最適化と論理回路を介したレジスタの転送により、個々のSTIセグメントの特定の論理信号が存在しない場合があります。 合成結果は、開発者(CAD)が使用する設計ツールで指定されたユーザー設定にも依存します。

1つのSTIセグメントのエージェントの相互作用プロトコルを検討してください。

システム同期ラインCLKおよび初期インストール(リセット)RSTを除くSTIインターフェイスのすべてのロジック信号は、クロック信号CLKの動作エッジに関連する同期の要件を満たさなければなりません。 このプロトコルでは、作業面は昇順であると想定されます。この場合、低レベルが高レベルに置き換えられます。

信号S_NBEは、現在のサイクルで書き込まれたまたは読み取られたアクティブなバイトに関する情報を搬送します。 8ビットSTIインターフェイスの場合、この信号は使用されません。これは、すべてのサイクルで1バイトしか送信されず、無効にできないためです。 8ビットSTIセグメントの無効なバイトは、ループがないことです。

16ビットSTIでは、S_NBE信号のビット深度は2ビットです。 低レベルS_NBE [0]は、ビットS_D_WR [7:0]またはS_D_RD [7:0]のデータの有効性を示します。 低レベルS_NBE [1]は、ビットS_D_WR [15:8]またはS_D_RD [15:8]に有効なデータが存在することを示します。 S_NBE [x]の高レベルは、対応するビットにデータがないことを示します。 したがって、これらのバイトを書き込んだり、読み取りと見なしたりしないでください。

32ビットSTIでは、S_NBE信号のビット深度は4ビットです。 2つの追加ビットS_NBE [3:2]は、データバスの上半分を制御します。 低レベルのS_NBE [2]は、ビットS_D_WR [23:16]またはS_D_RD [23:16]のデータの有効性を示します。 低レベルS_NBE [3]は、ビットS_D_WR [31:24]またはS_D_RD [31:24]に有効なデータが存在することを示します。 同様に、ビットS_NBE [7:4]は64ビットインターフェイスの上位バイトを制御し、ビット4はバイト[39:32]、ビット5-バイト[47:40]、ビット6-バイト[55:48]を制御します。ビット7は上位バイト[63:56]です。

S_CMD [2:0]行で、現在の交換サイクルのタイプを決定するコマンドが送信されます。 STIコマンドを表2にリストします。

表2。

| S_CMD [2] | S_CMD [1] | S_CMD [0] | サイクルタイプ |

|---|---|---|---|

| 0 | 0 | 0 | IO書き込み-最終的なエグゼキューター(データレシーバー)の準備が整っていることを期待するIOレコード

|

| 0 | 0 | 1 | メモリ書き込み-最後のエグゼキュータ(データレシーバ)の準備が整うまでメモリに書き込みます

|

| 0 | 1 | 0 | ポストされたIO書き込み-遅延書き込みIO

|

| 0 | 1 | 1 | ポストメモリ書き込み-遅延書き込みメモリ

|

| 1 | 0 | 0 | IO読み取り-IOの読み取り(データのプリフェッチなし)

|

| 1 | 0 | 1 | メモリー読み取り-メモリーの読み取り(データのプリフェッチなし)

|

| 1 | 1 | X | Programm Memory Read-プログラムメモリの読み取り(データプリフェッチなし)

|

STIインターフェイスは、3種類のアドレススペースをサポートしています。

- IOスペースI / Oポートスペース。

- メモリ空間(またはデータメモリ)メモリ空間。

- プログラムメモリ空間(個別のプログラムメモリとデータメモリを備えたプロセッサアーキテクチャ用)プログラムメモリ空間。

S_ADDRバスは、任意のアドレススペースのアドレスの組み合わせを伝送します。 STIの8ビットバージョンでは、アドレスの最下位ビットはS_ADDR [0]で示され、16ビットバージョンではS_ADDR [1]で示され、32ビットバージョンではアドレスの最下位ビットはS_ADDR [2]であり、64ビットバージョンではS_ADDR [ 3]。 これは、STIジャンクションでアドレス可能な最小データ値がバイトであり、16、32、64ビットバージョンでは、アドレスS_ADDR [0]、S_ADDR [1:0]、S_ADDR [2:0]の下位ビットがそれぞれ置き換えられるためです。バイト選択コード:S_NBE [1:0]、S_NBE [3:0]、S_NBE [7:0]。

S_D_WRバスは書き込み用のデータワードを伝送し、記録パスです。

S_D_RDバスは読み取りデータワードを搬送し、読み取りパスを表します。

S_EX_REQサイクル要求信号はアクティブHighで、書き込みまたは読み取りサイクルの有無を通知します。

ループ確認信号S_EX_ACKは、エグゼキューターによって生成され、アクティブな高レベルを持っています。 低レベルは、請負業者が記録されたデータを受け入れる準備ができていないか、読み取りパスに有効な読み取りデータがないことを通知します。

STIジャンクションでの交換サイクルは、クロック信号のワーキングエッジのS_EX_REQおよびS_EX_ACKラインにハイレベルが同時に存在するという事実を修正した後、完了したと見なされます。

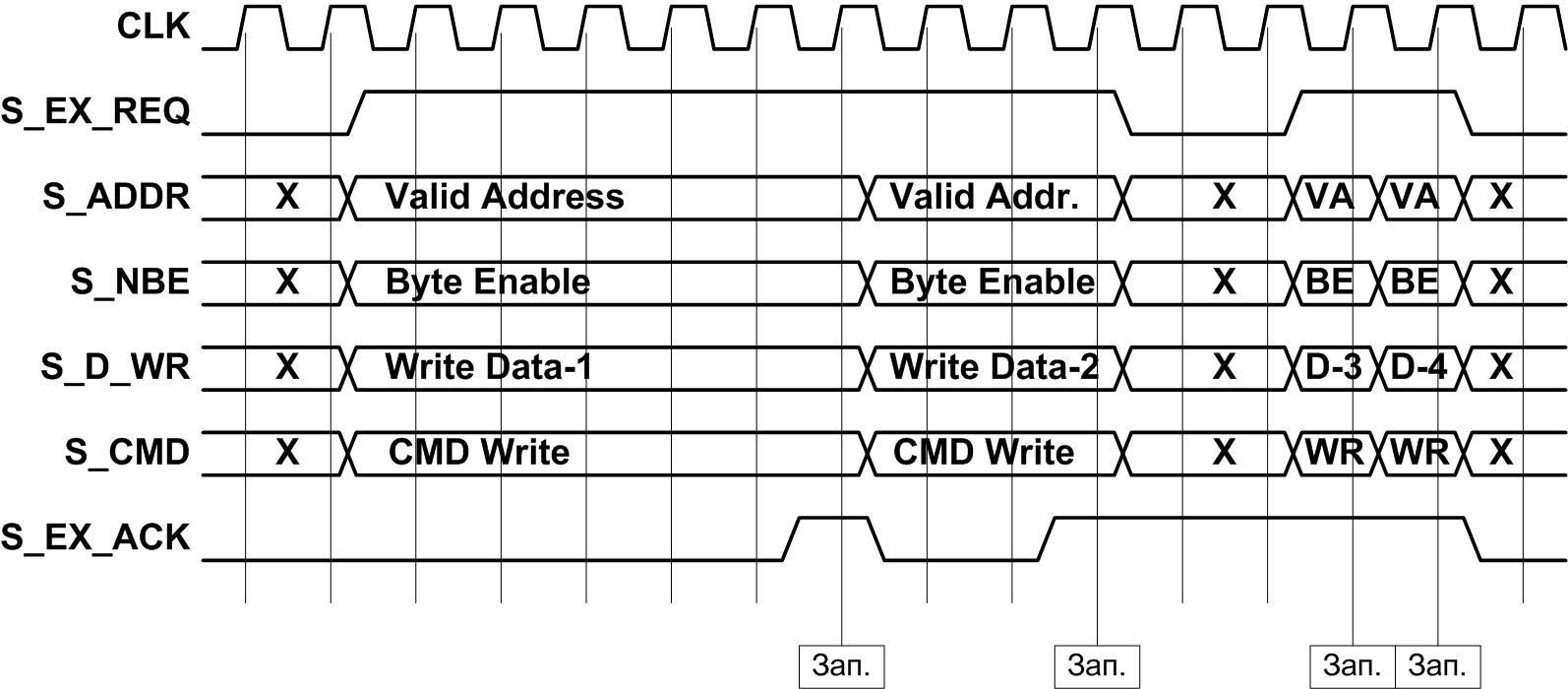

記録サイクルを説明するタイミング図を図1に示します。 3。

図 3.記録タイミングチャートの例

読み取りサイクルを説明するタイミング図を図5に示します。 4。

図 4.タイミングチャートの読み取り例

STIジャンクションで信号の状態を変更する手順は、次の一連の規則によって規制されています。

ルールIn-1

イニシエーターは、サイクル要求がアクティブなすべてのクロックサイクル(高信号レベルS_EX_REQ)で信号S_ADDR、S_NBE、S_CMDの有効な値を提供する必要があります。

ルールIn-2。

イニシエーターは、サイクル要求がアクティブで(高信号レベルS_EX_REQ)、すべての書き込みコマンドの組み合わせがS_CMDラインに設定されているすべてのクロックサイクルでS_D_WR信号の有効な値を提供する必要があります。

ルールイン-3。

イニシエーターは、信号S_EX_REQおよびS_EX_ACKの高レベルの同時固定(クロック信号の動作エッジで)後の次のサイクルの間、および信号レベルS_EX_REQが低い場合にのみ、信号S_ADDR、S_NBE、S_CMD、S_D_WRの状態を変更できます。

ルールイン-4。

イニシエーターは、S_EX_REQおよびS_EX_ACK信号の高レベルを同時に(クロック信号の動作エッジで)固定した後の次のクロックサイクル中にのみ、S_EX_REQ信号を低レベルに設定できます(低レベルの保持と混同しないでください)。

ルールIsp-1

請負業者は、S_EX_ACKサイクルの高レベルの確認信号とS_CMDラインでの読み取りコマンドの存在により、S_D_RDラインで有効な読み取りデータ値を提供する必要があります。 (S_EX_REQ要求信号の高レベルを待たずに、S_EX_ACKサイクルの高レベルの確認信号を事前に発行するエグゼキューターは、クロック信号の最も近い作業エッジが到着するまで、1クロックサイクル中に入力の組み合わせを変更するときにデータを読み取る機能を提供する必要があります)

ルールIsp-2。

請負業者は、S_EX_ACKサイクルの確認信号の高レベル、入力S_EX_REQの高レベル、およびS_CMDライン上の書き込みコマンドの組み合わせの存在とともに、クロック信号の作業エッジに沿ってS_D_WRラインから記録用のデータを受信して保存する必要があります。 (S_EX_REQ要求信号の高レベルを待たずに、S_EX_ACKサイクルの高レベルの確認信号を事前に発行する実行者は、クロック信号の最も近い作業エッジが到着するまで、1クロックサイクル内で入力の組み合わせを変更するときにデータを記録する機能を提供する必要があります)

ルールIsp-3。

エグゼキュータは、S_EX_REQおよびS_EX_ACK信号の高レベルを同時に(クロック信号の動作エッジで)固定した後、次のクロックサイクル中にのみ、その出力でS_EX_ACKサイクルの確認信号の低レベルを設定できます。 (S_EX_ACK信号の状態を、図4の図のようにローからハイ、イニシエーター側からハイからローの両方に変更することは、組み合わせ回路を接続することによるアーティストの整流によって引き起こされる可能性があります。)

ルールIsp-4。

請負業者は、次のいずれかの条件の下でのみS_D_RDラインの信号の状態を変更できます。

- 高レベルの信号S_EX_REQおよびS_EX_ACKを(クロック信号の動作エッジに沿って)同時に修正した後、

- S_ADDRアドレスの状態を変更した直後、クロック信号の最も近い作業エッジが到着するまでS_NBEバイトまたはS_CMD命令コードを解決します。

- 低信号レベルS_EX_ACKのサイクルで、

- 同時に(1ステップで)S_EX_ACKの出力で高レベルを設定し、

- 読み取りサイクルに対応しないS_CMD命令コードの組み合わせによるサイクル。

STIパフォーマーの内部組織の原則を説明するために、単純な機能ブロックの例をいくつか考えてみましょう。

上記のすべてのルールを満たすSTIインターフェースを備えたパフォーマーは、最新のエレメントベースに実装された簡単な回路ソリューションに基づいています。

STIエグゼキューターを編成する最も簡単な例は、汎用のディスクリート入力/出力-GPIO(汎用入出力)を実装するI / O拡張ユニットです。 そのような機能ブロックの図を図に示します。 5。

図 5. I / O拡張ユニットの機能図

このブロックを使用すると、論理信号の入力または出力用に32チャネルをビットごとに構成できます。 2つの32ビットレジスタがデータ用に提供されています:RG_O [31:0]およびRG_I [31:0]。 レジスタRG_T [31:0]は制御に使用され、ベースアドレス(S_ADDR_2 = 0)での読み取りと書き込みに使用できます。 レジスタRG_I [31:0]は、オフセット+1(S_ADDR_2 = 1)のアドレスでの書き込みに使用でき、レジスタRG_O [31:0]は、オフセット+1(S_ADDR_2 = 1)のアドレスでの読み取りに使用できます。

レジスタへの書き込みは、バイト解像度S_NBE [3:0]の組み合わせを考慮して、ビットごとに実行されます。

以下は、Verilog言語で記述された、検討中のI / O拡張ユニットの合成モデルです。

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////// // Engineer: FPGA-Mechanic // // Create Date: 11:12:38 07/24/2014 // Design Name: STI Design // Module Name: MSTI_32b_GPIO_REG_V10 - 32-bit STI GPIO Expander // Project Name: Any // Target Devices: FPGA // Tool versions: Xilinx DS 14.4 // // Revision: 1.0 (24.07.2014) // Revision 1.0 - File Created ////////////////////////////////////////////////////////////////////////// module MSTI_32b_GPIO_REG_V10( input CLK, input RST, input S_EX_REQ, input S_ADDR_2, input [3:0] S_NBE, input [2:0] S_CMD, input [31:0] S_D_WR, output S_EX_ACK, output [31:0] S_D_RD, output [31:0] GP_O, output [31:0] GP_T, input [31:0] GP_I ); // Internal signals declaration: wire IO_WR_CMD; reg [31:0] RG_T, RG_O, RG_I; //------------------------------------------ assign IO_WR_CMD = ~S_CMD[0] & ~S_CMD[2] & S_EX_REQ; //------------------------------------------ // Internal Data Registers: always @ (posedge CLK, posedge RST) if(RST) begin RG_T <= 32'hFFFFFFFF; // All Outputs Tri-Stated RG_O <= 32'h00000000; RG_I <= 32'h00000000; end else begin RG_I <= GP_I; if(~S_NBE[0] & ~S_ADDR_2 & IO_WR_CMD) RG_T[7:0] <= S_D_WR[7:0]; if(~S_NBE[1] & ~S_ADDR_2 & IO_WR_CMD) RG_T[15:8] <= S_D_WR[15:8]; if(~S_NBE[2] & ~S_ADDR_2 & IO_WR_CMD) RG_T[23:16] <= S_D_WR[23:16]; if(~S_NBE[3] & ~S_ADDR_2 & IO_WR_CMD) RG_T[31:24] <= S_D_WR[31:24]; if(~S_NBE[0] & S_ADDR_2 & IO_WR_CMD) RG_O[7:0] <= S_D_WR[7:0]; if(~S_NBE[1] & S_ADDR_2 & IO_WR_CMD) RG_O[15:8] <= S_D_WR[15:8]; if(~S_NBE[2] & S_ADDR_2 & IO_WR_CMD) RG_O[23:16] <= S_D_WR[23:16]; if(~S_NBE[3] & S_ADDR_2 & IO_WR_CMD) RG_O[31:24] <= S_D_WR[31:24]; end //------------------------------------------ assign S_EX_ACK = 1'b1; //------------------------------------------ assign GP_T = RG_T; assign GP_O = RG_O; //------------------------------------------ assign S_D_RD = S_ADDR_2 ? RG_I : RG_T; //------------------------------------------ endmodule

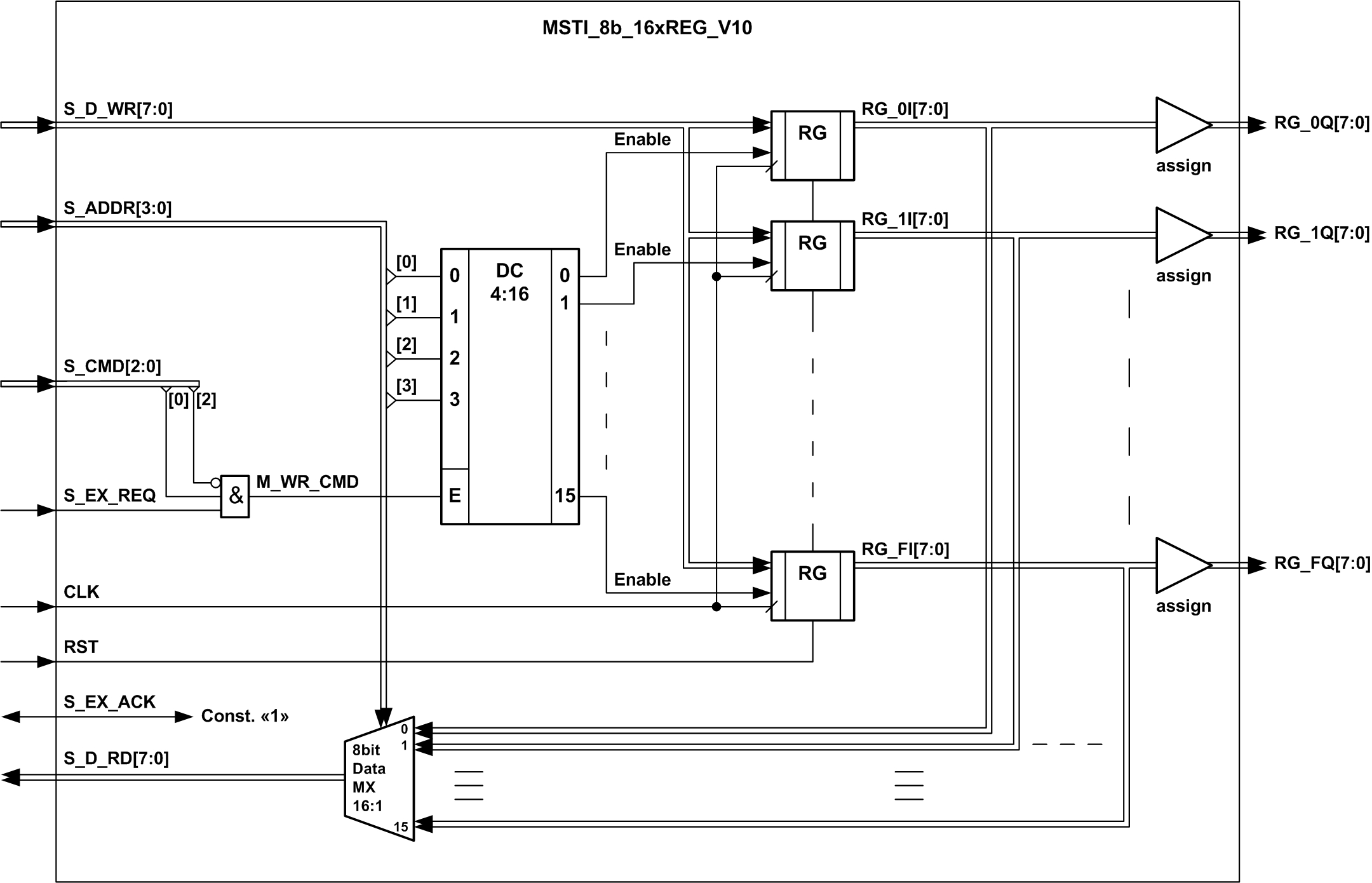

エグゼキュータの別の例は、8ビットのビット容量を持つ16個のレジスタの容量を持つレジスタファイルで表されます。 レジスタファイルの機能図を図に示します。 6。

16個のレジスタはそれぞれ、STIインターフェイスでの書き込みおよび読み取りに使用でき、プロジェクト階層の最上位で使用される個別の出力信号RG_xQ [7:0]を備えています。

機能レジスタファイルは、FPGA FPGAアーキテクチャのLUT-4テーブルコンバーターに基づく4つのシングルビット分散メモリブロックに似ています(たとえば、Xilinx社のFPGAライブラリのRAM16X1Dプリミティブ)。

検討されたパフォーマーの例は両方ともシングルサイクルの書き込みおよび読み取りサイクルをサポートしているため、S_EX_ACK出力は静的に高レベルを生成します。

レジスタファイルの合成モデルは、Verilogで次のように記述されています。

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////// // Engineer: FPGA-Mechanic // // Create Date: 11:40:08 07/24/2014 // Design Name: STI Design // Module Name: MSTI_8b_16xREG_V10 - 16x8bit Register File // in STI Memory Space // Project Name: Any // Target Devices: FPGA // Tool versions: Xilinx DS 14.4 // // Revision: 1.0 (24.07.2014) // Revision 1.0 - File Created ////////////////////////////////////////////////////////////////////////// module MSTI_8b_16xREG_V10( input CLK, input RST, input S_EX_REQ, input [3:0] S_ADDR, //input [1:0] S_NBE, input [2:0] S_CMD, input [7:0] S_D_WR, output S_EX_ACK, output reg [7:0] S_D_RD, output [7:0] RG_0Q, output [7:0] RG_1Q, output [7:0] RG_2Q, output [7:0] RG_3Q, output [7:0] RG_4Q, output [7:0] RG_5Q, output [7:0] RG_6Q, output [7:0] RG_7Q, output [7:0] RG_8Q, output [7:0] RG_9Q, output [7:0] RG_AQ, output [7:0] RG_BQ, output [7:0] RG_CQ, output [7:0] RG_DQ, output [7:0] RG_EQ, output [7:0] RG_FQ ); // Internal signals declaration: wire M_WR_CMD; reg [7:0] RG_0I, RG_1I, RG_2I, RG_3I, RG_4I, RG_5I, RG_6I, RG_7I; reg [7:0] RG_8I, RG_9I, RG_AI, RG_BI, RG_CI, RG_DI, RG_EI, RG_FI; //------------------------------------------ assign M_WR_CMD = ~S_CMD[2] & S_CMD[0] & S_EX_REQ; //------------------------------------------ // Internal Data Registers: always @ (posedge CLK, posedge RST) if(RST) begin RG_0I <= 8'h00; RG_1I <= 8'h00; RG_2I <= 8'h00; RG_3I <= 8'h00; RG_4I <= 8'h00; RG_5I <= 8'h00; RG_6I <= 8'h00; RG_7I <= 8'h00; RG_8I <= 8'h00; RG_9I <= 8'h00; RG_AI <= 8'h00; RG_BI <= 8'h00; RG_CI <= 8'h00; RG_DI <= 8'h00; RG_EI <= 8'h00; RG_FI <= 8'h00; end else begin if(M_WR_CMD) case(S_ADDR) 4'h0 : RG_0I <= S_D_WR; 4'h1 : RG_1I <= S_D_WR; 4'h2 : RG_2I <= S_D_WR; 4'h3 : RG_3I <= S_D_WR; 4'h4 : RG_4I <= S_D_WR; 4'h5 : RG_5I <= S_D_WR; 4'h6 : RG_6I <= S_D_WR; 4'h7 : RG_7I <= S_D_WR; 4'h8 : RG_8I <= S_D_WR; 4'h9 : RG_9I <= S_D_WR; 4'hA : RG_AI <= S_D_WR; 4'hB : RG_BI <= S_D_WR; 4'hC : RG_CI <= S_D_WR; 4'hD : RG_DI <= S_D_WR; 4'hE : RG_EI <= S_D_WR; default: RG_FI <= S_D_WR; endcase end //------------------------------------------ // Output MUX: always @ (S_ADDR, RG_0I, RG_1I, RG_2I, RG_3I, RG_4I, RG_5I, RG_6I, RG_7I, RG_8I, RG_9I, RG_AI, RG_BI, RG_CI, RG_DI, RG_EI, RG_FI) case(S_ADDR) 4'h0 : S_D_RD <= RG_0I; 4'h1 : S_D_RD <= RG_1I; 4'h2 : S_D_RD <= RG_2I; 4'h3 : S_D_RD <= RG_3I; 4'h4 : S_D_RD <= RG_4I; 4'h5 : S_D_RD <= RG_5I; 4'h6 : S_D_RD <= RG_6I; 4'h7 : S_D_RD <= RG_7I; 4'h8 : S_D_RD <= RG_8I; 4'h9 : S_D_RD <= RG_9I; 4'hA : S_D_RD <= RG_AI; 4'hB : S_D_RD <= RG_BI; 4'hC : S_D_RD <= RG_CI; 4'hD : S_D_RD <= RG_DI; 4'hE : S_D_RD <= RG_EI; default: S_D_RD <= RG_FI; endcase //------------------------------------------ assign S_EX_ACK = 1'b1; //------------------------------------------ // Regs Outputs: assign RG_0Q = RG_0I; assign RG_1Q = RG_1I; assign RG_2Q = RG_2I; assign RG_3Q = RG_3I; assign RG_4Q = RG_4I; assign RG_5Q = RG_5I; assign RG_6Q = RG_6I; assign RG_7Q = RG_7I; assign RG_8Q = RG_8I; assign RG_9Q = RG_9I; assign RG_AQ = RG_AI; assign RG_BQ = RG_BI; assign RG_CQ = RG_CI; assign RG_DQ = RG_DI; assign RG_EQ = RG_EI; assign RG_FQ = RG_FI; //------------------------------------------ endmodule

レジスタファイルは、次元配列の精神を使用して、よりコンパクトに記述できます。

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////// // Engineer: FPGA-Mechanic // // Create Date: 11:40:08 07/24/2014 // Design Name: STI Design // Module Name: MSTI_8b_16xREG_V11 - 16x8bit Register File // in STI Memory Space // Project Name: Any // Target Devices: FPGA // Tool versions: Xilinx DS 14.4 // // Revision: 1.1 (24.07.2014) Array Coding // Revision 1.0 - File Created ////////////////////////////////////////////////////////////////////////// module MSTI_8b_16xREG_V11( input CLK, input RST, input S_EX_REQ, input [3:0] S_ADDR, //input [1:0] S_NBE, input [2:0] S_CMD, input [7:0] S_D_WR, output S_EX_ACK, output [7:0] S_D_RD, output [7:0] RG_0Q, output [7:0] RG_1Q, output [7:0] RG_2Q, output [7:0] RG_3Q, output [7:0] RG_4Q, output [7:0] RG_5Q, output [7:0] RG_6Q, output [7:0] RG_7Q, output [7:0] RG_8Q, output [7:0] RG_9Q, output [7:0] RG_AQ, output [7:0] RG_BQ, output [7:0] RG_CQ, output [7:0] RG_DQ, output [7:0] RG_EQ, output [7:0] RG_FQ ); // Internal signals declaration: wire M_WR_CMD; reg [7:0] RG_I [15:0]; // Array 16 x 8bit //------------------------------------------ assign M_WR_CMD = ~S_CMD[2] & S_CMD[0] & S_EX_REQ; //------------------------------------------ // Internal Data Registers: always @ (posedge CLK, posedge RST) if(RST) begin RG_I[0] <= 8'h00; RG_I[1] <= 8'h00; RG_I[2] <= 8'h00; RG_I[3] <= 8'h00; RG_I[4] <= 8'h00; RG_I[5] <= 8'h00; RG_I[6] <= 8'h00; RG_I[7] <= 8'h00; RG_I[8] <= 8'h00; RG_I[9] <= 8'h00; RG_I[4'hA] <= 8'h00; RG_I[4'hB] <= 8'h00; RG_I[4'hC] <= 8'h00; RG_I[4'hD] <= 8'h00; RG_I[4'hE] <= 8'h00; RG_I[4'hF] <= 8'h00; end else if(M_WR_CMD) RG_I[S_ADDR] <= S_D_WR; //------------------------------------------ // Output MUX: assign S_D_RD = RG_I[S_ADDR]; //------------------------------------------ assign S_EX_ACK = 1'b1; //------------------------------------------ // Regs Outputs: assign RG_0Q = RG_I[0]; assign RG_1Q = RG_I[1]; assign RG_2Q = RG_I[2]; assign RG_3Q = RG_I[3]; assign RG_4Q = RG_I[4]; assign RG_5Q = RG_I[5]; assign RG_6Q = RG_I[6]; assign RG_7Q = RG_I[7]; assign RG_8Q = RG_I[8]; assign RG_9Q = RG_I[9]; assign RG_AQ = RG_I[4'hA]; assign RG_BQ = RG_I[4'hB]; assign RG_CQ = RG_I[4'hC]; assign RG_DQ = RG_I[4'hD]; assign RG_EQ = RG_I[4'hE]; assign RG_FQ = RG_I[4'hF]; //------------------------------------------ endmodule

図 6.レジスタファイルの機能図

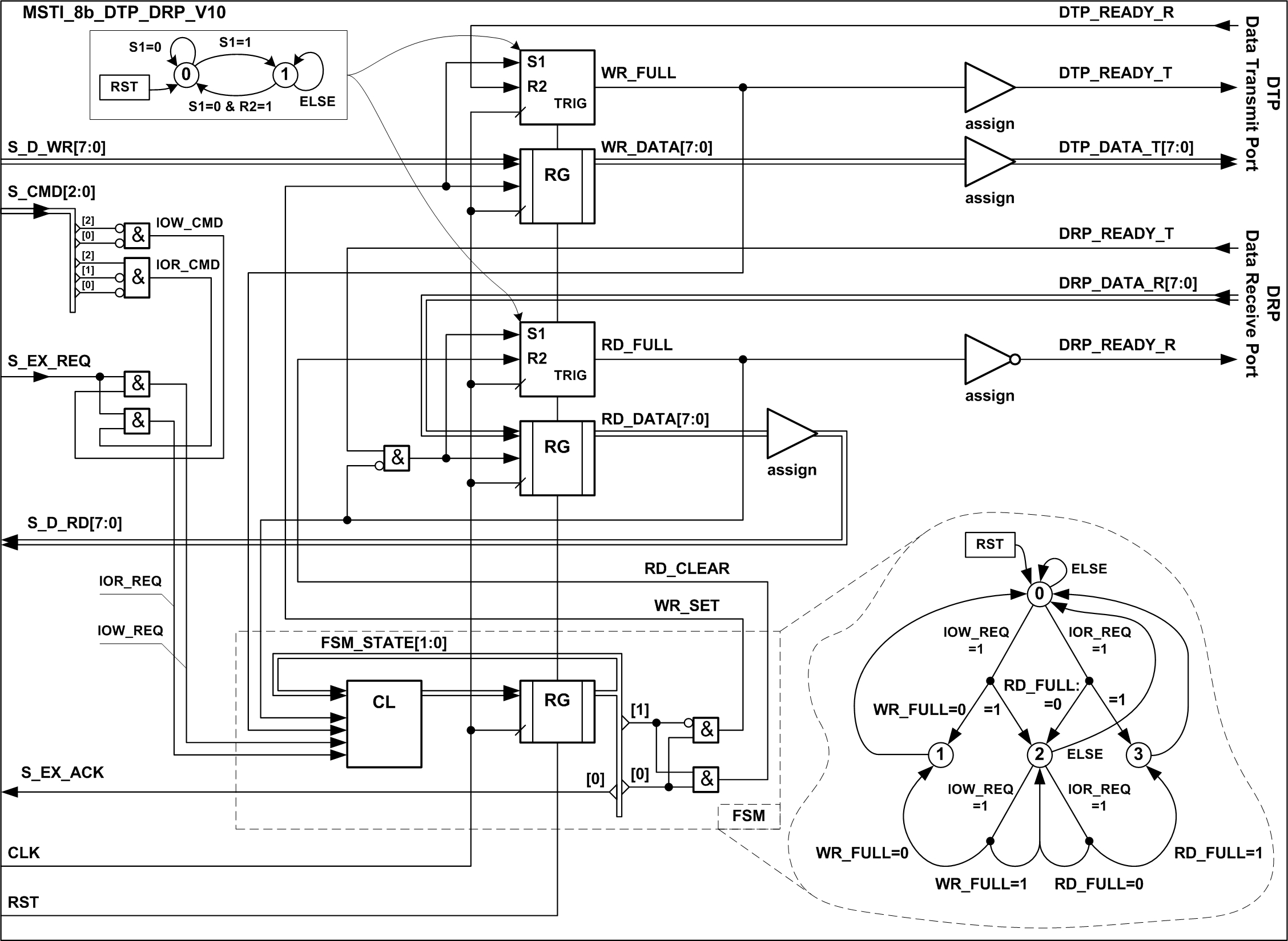

STI executorの3番目の例は、記事[8、9、10]で説明されているDTPおよびDRPデータの送信および受信ポートとのインターフェースのバリエーションを示しています。 この例では、ループ確認信号S_EX_ACKと内部レジスタビジーセマフォを制御する有限状態マシンの合成が必要になりました。

バイトをDTPデータポートに転送するには、バッファレジスタWR_DATA [7:0]を使用します。このレジスタのビジー状態はWR_FULLセマフォによって制御されます。

DRPデータ受信ポートからバイトを受信するには、バッファレジスタRD_DATA [7:0]が使用され、その占有率はRD_FULLセマフォによって制御されます。

両方のセマフォは、図の左上隅に示されているグラフ(図7)に従って機能する同一のトリガーで構築されています。 インストール入力S1は、リセット入力R2より高い優先度を持っています。 これにより、このレジスタに書き込むことで、1サイクルでバッファレジスタから読み取ることができます。

FSMステートマシンの主な機能は、読み取りレジスタビジーセマフォのリセットまたは書き込みレジスタビジーセマフォの設定と同時に、ループ確認信号S_EX_ACKを高レベルに設定することです。 メイン表示オートマトンの遷移グラフは右下です。 オートマトンの状態のエンコードは、出力S_EX_ACKが現在の状態レジスタによって形成されるステータスビットの1つによって制御されるように選択されます。

オートマトンWR_SETおよびRD_CLEARの残りの出力は、組み合わせ要素によってムーアスキーム(ムーアFSM)に従って形成されます。

サイクルS_EX_ACKの確認信号は、レコードの空のバッファレジスタの事実に基づいて、書き込みサイクルでマシンによってアクティブな高レベルに自動的に設定されます。 読み取りサイクルでは、読み取りバッファレジスタがビジーであるという事実に基づいて、ループ確認信号S_EX_ACKがアクティブなハイレベルに設定されます。

Verilogで説明されているデータ送信ポートと受信ポートを備えたインターフェイスブリッジの合成モデルを以下に示します。

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////// // Engineer: FPGA-Mechanic // // Create Date: 12:37:39 07/24/2014 // Design Name: STI Design // Module Name: MSTI_8b_DTP_DRP_V10 8-bit STI to DTP & DRP Bridge // Project Name: Any // Target Devices: FPGA // Tool versions: Xilinx DS 14.4 // // Revision: 1.0 (24.07.2014) // Revision 1.0 - File Created ////////////////////////////////////////////////////////////////////////// module MSTI_8b_DTP_DRP_V10( input CLK, input RST, input S_EX_REQ, //input S_ADDR_0, //input [1:0] S_NBE, input [2:0] S_CMD, input [7:0] S_D_WR, output S_EX_ACK, output [7:0] S_D_RD, output DTP_READY_T, output [7:0] DTP_DATA_T, input DTP_READY_R, input DRP_READY_T, input [7:0] DRP_DATA_R, output DRP_READY_R ); // Internal signals declaration: wire IOW_CMD, IOR_CMD; wire IOW_REQ, IOR_REQ; reg [7:0] WR_DATA, RD_DATA; reg WR_FULL, RD_FULL; reg [1:0] FSM_STATE; wire WR_SET, RD_CLEAR; //------------------------------------------ assign IOW_CMD = ~S_CMD[0] & ~S_CMD[2]; assign IOR_CMD = ~S_CMD[0] & ~S_CMD[1] & S_CMD[2]; assign IOW_REQ = IOW_CMD & S_EX_REQ; assign IOR_REQ = IOR_CMD & S_EX_REQ; //------------------------------------------ // Internal Data Registers: always @ (posedge CLK, posedge RST) if(RST) begin WR_DATA <= 8'h00; RD_DATA <= 8'h00; end else begin if(WR_SET) WR_DATA <= S_D_WR; if(~RD_FULL & DRP_READY_T) RD_DATA <= DRP_DATA_R; end assign S_D_RD = RD_DATA; assign DTP_DATA_T = WR_DATA; //------------------------------------------ // Internal Data Semaphores: always @ (posedge CLK, posedge RST) if(RST) begin WR_FULL <= 1'b0; RD_FULL <= 1'b0; end else begin if(WR_SET) WR_FULL <= 1'b1; else if(DTP_READY_R) WR_FULL <= 1'b0; if(~RD_FULL & DRP_READY_T) RD_FULL <= 1'b1; else if(RD_CLEAR) RD_FULL <= 1'b0; end assign DTP_READY_T = WR_FULL; assign DRP_READY_R = ~RD_FULL; //------------------------------------------ // Finite State Machine: always @ (posedge CLK, posedge RST) if(RST) FSM_STATE <= 2'd0; else begin case(FSM_STATE) 2'd0 : if(IOW_REQ) if(WR_FULL) FSM_STATE <= 2'd2; else FSM_STATE <= 2'd1; else if(IOR_REQ) if(RD_FULL) FSM_STATE <= 2'd3; else FSM_STATE <= 2'd2; else FSM_STATE <= 2'd0; 2'd1 : FSM_STATE <= 2'd0; 2'd2 : if(IOW_REQ) if(WR_FULL) FSM_STATE <= 2'd2; else FSM_STATE <= 2'd1; else if(IOR_REQ) if(RD_FULL) FSM_STATE <= 2'd3; else FSM_STATE <= 2'd2; else FSM_STATE <= 2'd0; default: FSM_STATE <= 2'd0; endcase end //------------------------------------------ // Moore Outputs assign WR_SET = ~FSM_STATE[1] & FSM_STATE[0]; assign RD_CLEAR = &(FSM_STATE); //------------------------------------------ assign S_EX_ACK = FSM_STATE[0]; //------------------------------------------ endmodule

図 7.インターフェイスブリッジSTIインターフェイスとデータ送受信ポートDTPおよびDRPの機能図

結論

シンプルなSTIエグゼキューターのジャンクションにより、FPGA構成プロジェクトまたはVLSIチップのシステムインターフェース用のエグゼキューターのモデルを構築できます。

説明されているインターフェイスは、水晶の周辺コントローラで使用できるだけでなく、I2C、SPI、QSPI、SRAM、FLASH、Microwireなどの従来の通信チャネルや古いモデルの外部システムバスとのインターフェイスでも使用できます。

参照:

1. AMBA APBプロトコル。 バージョン:2.0。 仕様。 ARM IHI 0024C(ID041610)2003-2010、ARM。

2. AMBA Specification Rev 2.0。 ARM IHI 0011A。 ARM Limited 1999。

3. AMBA AXIプロトコル。 バージョン:2.0。 仕様。 ARM IHI 0022C(ID030510)2003-2010、ARM

4. AMBA 4 AXI4-Streamプロトコル。 バージョン:1.0。 仕様。 ARM IHI 0051A(ID030510)。 2010年、ARM。

5.ポータブルIPコア用のWISHBONEシステムオンチップ(SoC)相互接続アーキテクチャ。 2010、OpenCores。

6. Open Core Protocol(OCP)仕様リリース2.1。 2005年、OCP-IP協会。

7. VHDLを使用したRTLハードウェア設計:効率、移植性、およびスケーラビリティのためのコーディング。 ポンP.Chu。 ジョン・ワイリー・アンド・サンズ 2006年。

8. Borisenko N. V.プログラマブルロジックのさまざまなファミリに実装された統合された一連の合成FIFOバッファモデルを編成するアプローチ。 パート1.「コンポーネントとテクノロジー」第12.2012。

9. Borisenko N. V.情報のソースとレシーバーの間のデータパスに統合されたインターフェイスを持つFIFOバッファーを組み込むためのスキーム。 「コンポーネントとテクノロジー」No. 2.2013。

10. Borisenko N.V.プログラマブルロジックチップの量の汎用レジスター上に構築された、統合インターフェースを備えた同期FIFOバッファーの構成。 「コンポーネントとテクノロジー」No. 8.2016。