- はじめに(KrsteAsanović) ビデオ スライド

- ツールチェーンRISC-V(Andrew Waterman) ビデオ スライド

- RISC-V SoCジェネレーター「ロケットチップ」チゼル(Yunsup Lee)のビデオ スライド

- RISC-Vソフトウェアスタック構造(Sagar Karandikar) ビデオ スライド

- RISC-V(Albert Ou) ビデオ スライドのデバッグ

- OpenEmbedded(Martin Maas) ビデオ スライドを使用した新しいRISC-Vコードの移植

- RISC-Vテスト環境(Stephen Twigg) ビデオ スライド

RISC-Vカーネルの現在のハードウェア実装を記述するために使用されるScalaベースの言語であるChisel(Rocketカーネルにはインオーダーパイプラインがあり、BOOMにはアウトオブオーダーがある)および将来の実装に興味がある場合の別のリンク 。

Chisel(Jonathan Bachrach) ビデオ スライドのクイックガイド

Rocket Chipと連携し、拡張機能、ASICインフラストラクチャ、およびFPGA(Colin Schmidt) ビデオ スライドを追加します

RISC-Vとコミュニティ開発に深く興味がある場合は、 ワークショップに参加することをお勧めします。

ParallellaのRISC-Vポートは、ChiseのソースからRocket Chipを使用して生成された完全に標準的なカーネルを使用します( 記事で非常に良い紹介が与えられています )。 最終結果はVerilog RTL(読み取り不可、Chiselのソースのみ読み取り可能)になり、 Parallella OH(オープンハードウェア) リポジトリで利用可能なParallellaのFPGAプロジェクトに含めることができます 。 ただし、ここでは詳しく説明しません。これについては、以下の投稿で説明します。

このカーネル用のソフトウェアをコンパイルするには、RISC-V GNUツールチェーンを使用できます 。これはここから入手できます 。 コンパイルオプションは2つあります。 プロキシカーネル (プロキシカーネル、pk)で実行されるプログラムに使用されるNewlib Cライブラリを使用するか、LinuxおよびLinuxプログラムをコンパイルするGNU Cライブラリ(glibc)を使用してコンパイルします。 添付の手順を使用して両方のバージョン( Linuxカーネル 、リリース4.1)をコンパイルしましたが、RISC-V ISAリファレンスシミュレーターであるSpikeでシミュレートすると、期待どおりに機能しました。

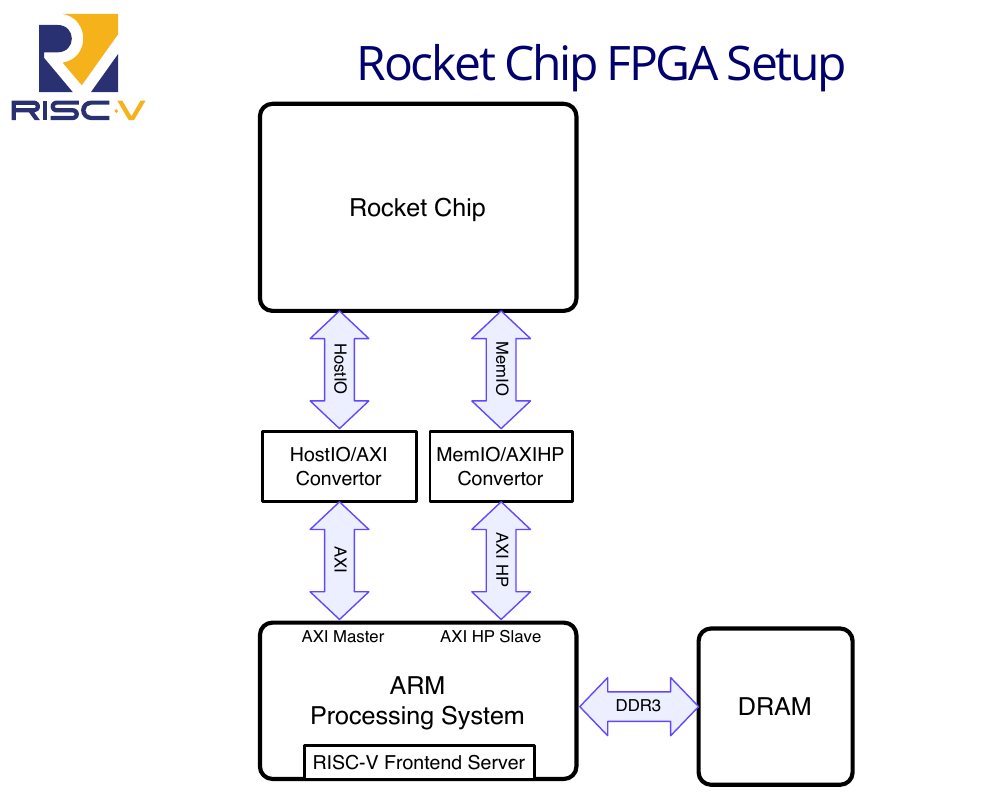

メインのRocket Chip リポジトリは、ソース(主にChisel)を含むすべてのリポジトリとGitサブモジュールを使用して接続されます。これらのソースは、src / main / scala /にあるラッパーファイルを使用した適切な生成に必要です。 各サブモジュールは特定のコミットに関連付けられており、明らかに動作しています。その結果、アセンブリは安定しています。 個人的には、デフォルトのRV64Gカーネルの生成時にエラーは発生しませんでした(64ビット、[I] nteger、[M] ultiply / Division、[A] tomic、[F] Single Floating、[D] ouble Floating)。 (一般)、命令とデータのL1キャッシュ、外部世界との通信用のMemIOおよびHostIOインターフェイスを備えたTLBおよびFPUが含まれます。

典型的なFPGAシステム(Rocket ChipのY.Lee プレゼンテーションの図に示されている)では、これら2つのインターフェイスがメインメモリにアクセスし、RISC-Vカーネル(ブートストラップ)をロードするために必要です。 後者は、CSR(制御ステータスレジスタ)を制御し、ターゲットマシン(プロキシカーネルまたはLinuxカーネルを実行する)からホストマシン(つまり、デュアルコアARMプロセッサ)へのシステムコール(I / O操作用)をサポートするために使用されますZynq FPGA)、 riscv-fesvr (フロントエンドサーバー)インスタンスを実行して、システムコールをオペレーティングシステム(つまり、ARM Linux)にディスパッチします。

カーネルを構成するために、 Config.scalaファイル内の値を変更することもできます 。 このファイルには、さまざまなアプリケーション(C ++モデル、レギュラーサイズFPGA、小型FPGA、VLSIなど)の構成セットが含まれています。 CONFIG = XXX変数(つまり、DefaultFPGAConfig)を受け入れるスクリプトは、C ++シミュレーターまたはFPGAまたはVLSI向けのVerilog RTLを構築するために必要な構成を設定します。 これは、利用可能なさまざまなオプションを試し、ソフトウェアまたはハードウェアですばやく生成およびテストする場合に非常に便利です。

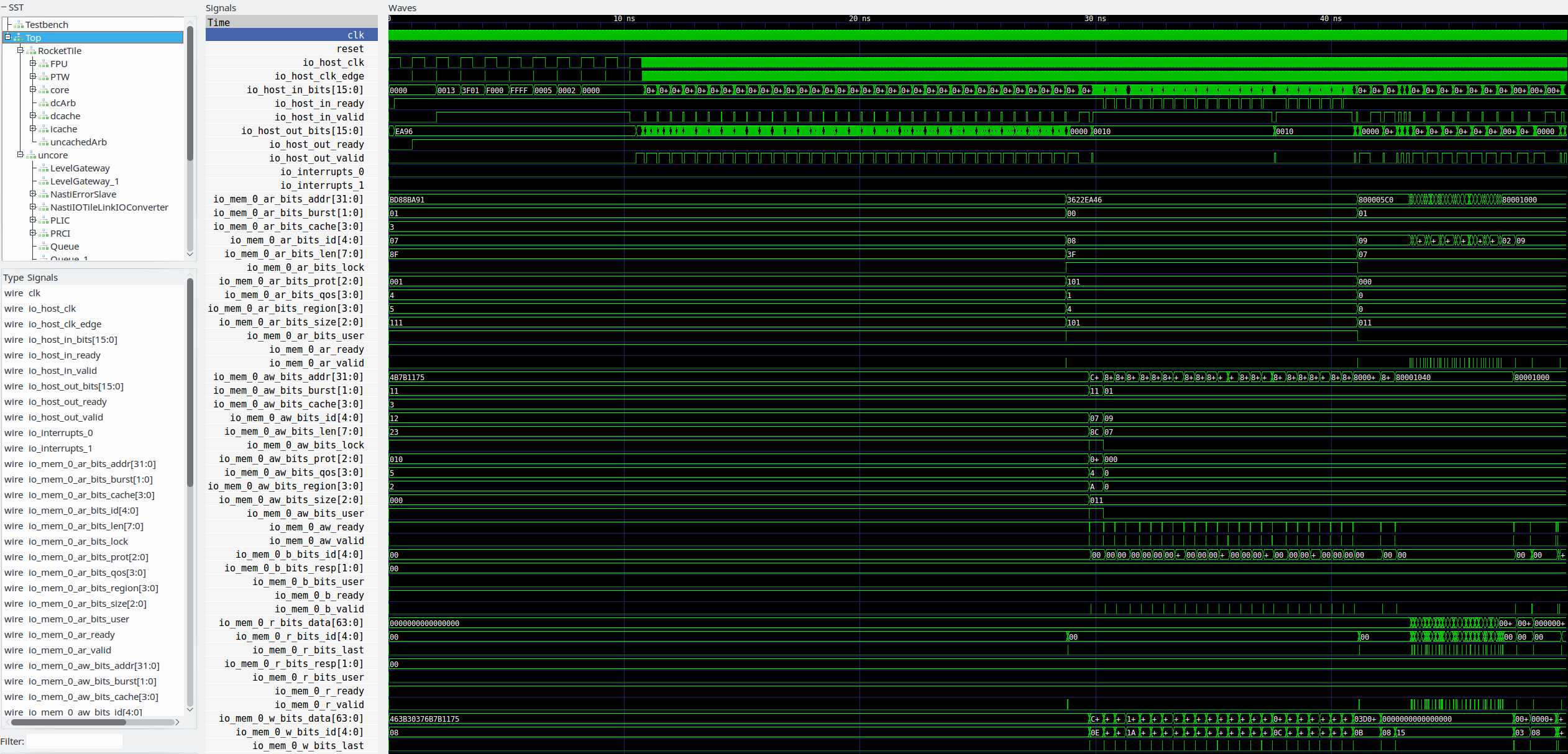

C ++シミュレーターまたはSynopsys VCSを使用してカーネルを検証するテストをコンパイルおよび実行する必要があるため、カーネルを生成する前にツールチェーンを(Newlibで最適に)コンパイルすることをお勧めします。 残念ながら、最初のものだけを使用できましたが、最後のものは使用できませんでした。 テストベンチではDirectC関数(Verilogテストベンチと任意のC / C ++コードのリンク)が使用されるため、Verilogシミュレーター(Verilator、Icarus Verilog、Modelsim、QuestSimなど)は使用できません。 幸いなことに、C ++シミュレーターはVCD出力を提供し、GTKWaveを使用して、生成されたテストタイミングチャートを表示することができました。

また、RISC-Vツールチェーンを構築し、FPGA用のRV64Gコアを生成するために必要な簡単なコマンドのセッションを追加しました。 これらのコマンドは最終的なコンパイルスクリプトに追加され、Parallella Zynqチップ内でRISC-Vコアを動作させるために必要なすべてを完全に自動化するために開発しています。

# Rocket Chip git clone https://github.com/ucb-bar/rocket-chip.git cd rocket-chip git submodule update --init export TOP=$(pwd) # (Ubuntu) sudo apt-get install autoconf automake autotools-dev curl \ libmpc-dev libmpfr-dev libgmp-dev gawk build-essential bison flex \ texinfo gperf libtool patchutils bc # RISC-V ( Newlib ) export RISCV=$TOP/riscv-tools # , , ) export PATH=$PATH:$RISCV/bin cd $RISCV git submodule update --init --recursive # build.common # JOBS = / , ./build.sh # RISC-V, # Spike ( ISA) # - (pk) cd $TOP echo -e '#include <stdio.h>\n int main(void) \ { printf("Hello world!\\n"); return 0; }' > hello.c riscv64-unknown-elf-gcc -o hello hello.c spike pk hello # : Rocket Chip # -j8 -jN ( / ) cd $TOP/emulator make # (: ) # make -j8 run-asm-tests # make -j8 run-bmark-tests # : make output/rv64ui-p-add.out # : Rocket Chip VCD # -j8 -jN cd $TOP/emulator # vcd2vpd, src/main/scala/Testing.scala # .vpd .vcd (6 ) make debug # (: ) # make -j8 run-asm-tests-debug # make -j8 run-bmark-tests-debug # # vcd2vpd: make output/rv64ui-p-add.vcd # Rocket Chip Verilog RTL FPGAs ( fsim/generated-src/) # "DefaultFPGAConfig", # , "SmallFPGAConfig" FPU # . make CONFIG=ConfigName verilog # (src/main/scala/Configs.scala) # Verilog RTL Top.ConfigName.v cd $TOP/fsim make verilog

次の投稿では、生成されたRV64GカーネルからIPブロックを取得し、ZedboardでのテストやParallellaでの大規模プロジェクトでの使用のために、プロジェクトに簡単に接続できるようにする方法を検討します。