以下の長いテキストの詳細。 非常に興味深いが、あまりにも多くの文字を読むのが面倒な場合は、詳細な20分間のビデオを見るとタスクを簡素化できます。

それでは、問題に戻りましょう。

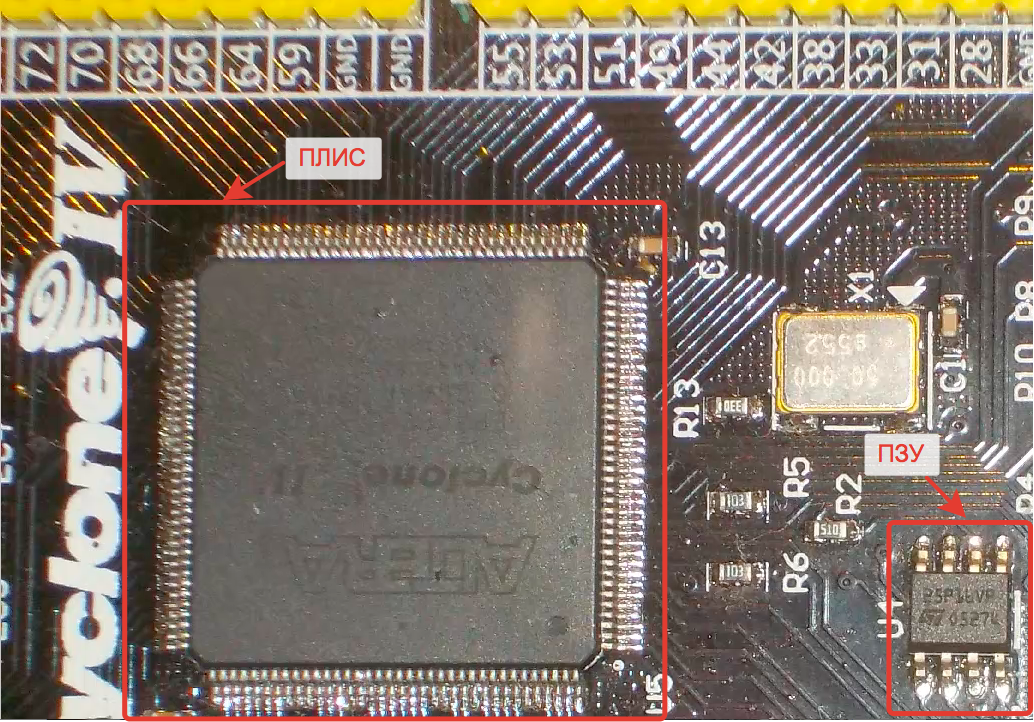

Cyclone IVファミリのクリスタルを搭載したブレッドボードを手にすると、非常に驚くべきことがわかります。

これはPLISinaで、構成ROMは次のとおりです。

奇妙なことに、これはEPCSではなく、通常の25番目のフラッシュドライブです。 このようなフラッシュドライブは安価で、誰でもかなり多く販売されています。

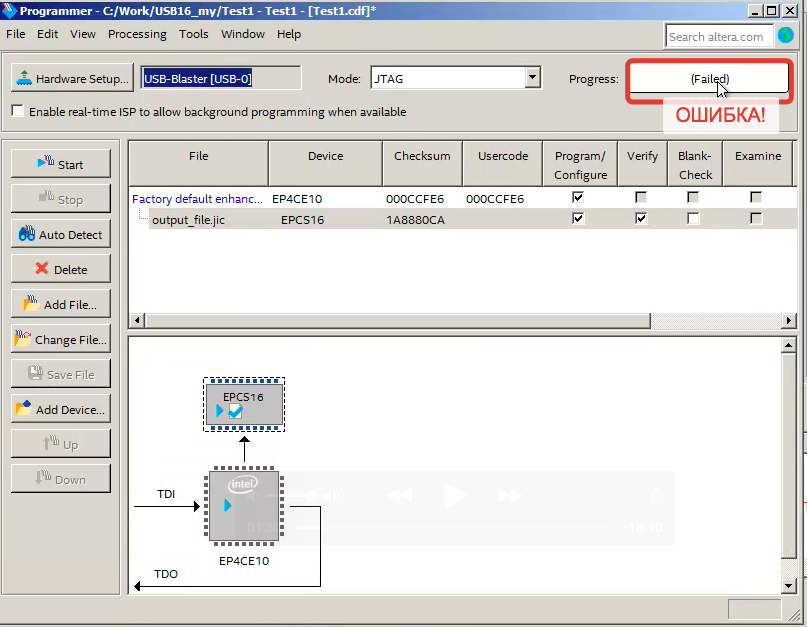

しかし、彼らが言うように、すべてのヨーグルトが同じように役立つわけではありません。 特に、お客様はこのようなフラッシュドライブを喜んで購入し、ボードにはんだ付けし、世界的な問題に直面しました。 プログラマーに入り、ファームウェア用に準備されたファイルをロードし、フラッシュを開始してエラーを取得します。

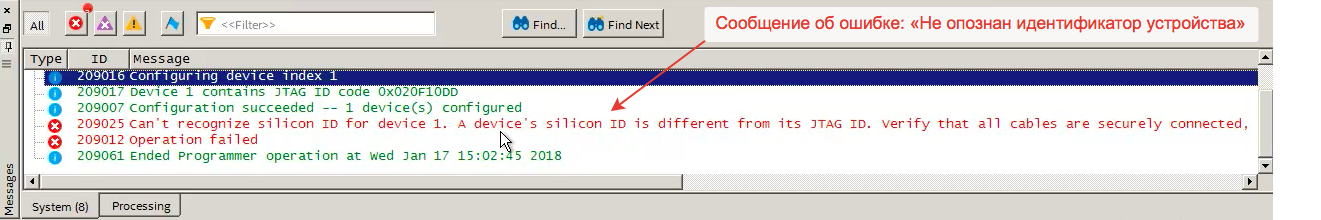

エラーメッセージは次のとおりです。

エラー(209025):デバイス1のシリコンIDを認識できません。デバイスのシリコンIDはJTAG IDと異なります。 すべてのケーブルがしっかりと接続されていることを確認し、別のデバイスを選択するか、ターゲットシステムの電源を確認します。 デバイスのピンが正しく接続および構成されていることを確認してください。

デバイス識別子が認識されません。 つまり、フラッシュドライブには、クォートについて不明な識別子があります。 具体的には、25P32クリスタルがお客様から購入されました。これは原則として原則的にサポートされていませんが、実際にはもっとありふれた状況があるかもしれません。 特に、STのフラッシュドライブは上の写真ではんだ付けされており、MICRONとして定義されています。 中国の売り手はそうマークすることができ、バッチが購入されて動作しないとき-何ができますか?

私はフォーラムに登りました。 検査することができたロシア語を話すものはすべて、どのサプライヤーと同様の問題に遭遇しないために何をすべきかとの議論で一杯でした。 しかし、私たちの場合、誰も新しいバッチを買いたくありませんでした。 英語の情報源では、ソリューションに関する記事は1つしか見つかりませんでしたが、現代のQuartus Prime環境では、このソリューションは「額に」機能しません。 そのため、この問題を現代環境向けにロシア語およびビデオ形式で文書化することに取り組みました。

それでは、ROMは一般的にどのようにプログラムされていますか?

特別な構成がFPGAに注がれ、それに応じてJTAGを介してフラッシュドライブに接続することが可能になります。 そして、この構成を使用して、データを入力します。 同様の設定を行うと、USBフラッシュドライブにアクセスし、IDに関係なく、独自のコードを1行も書くことなくフラッシュできるようになり、ユーティリティはすべてQuartus Prime(またはQiartus II、古い開発環境のバージョン)。

つまり、次の3つの手順を実行する必要があります。

- フラッシュドライブをノックする構成を作成します。

- フラッシュドライブが記述されているファイルを書き込みます。

- フラッシュします。

やってみましょう。 コードを1行も書かずに、独自の「ファームウェア」(同じ構成)を開発することから始めましょう。

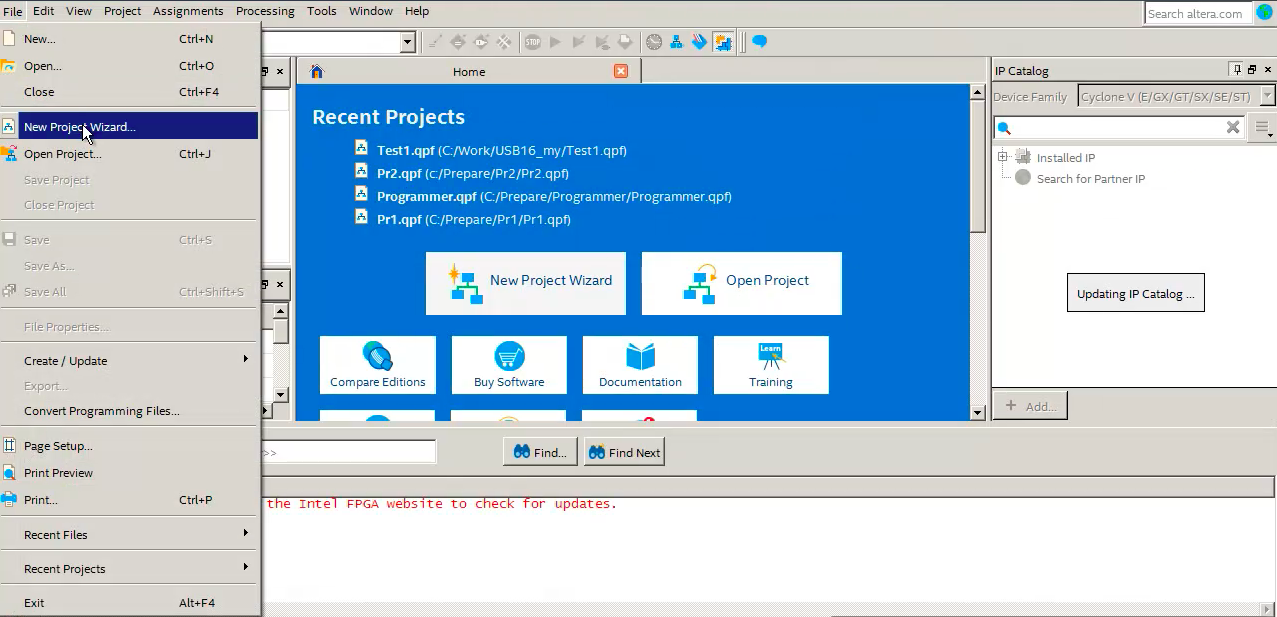

Quartusに移動します。

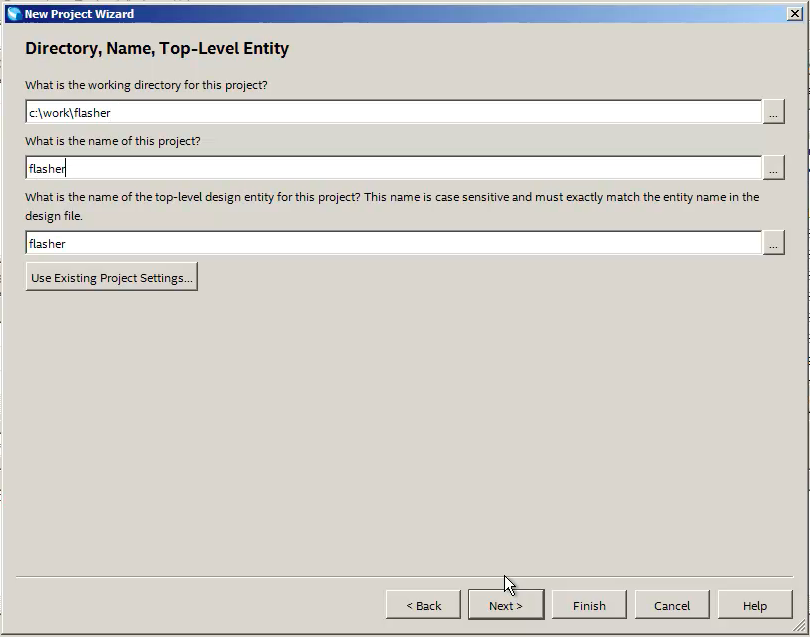

新しいプロジェクトを作成します。

たとえば、フラッシャーと呼びましょう:

この名前は覚えておく必要があります-まだ必要です。

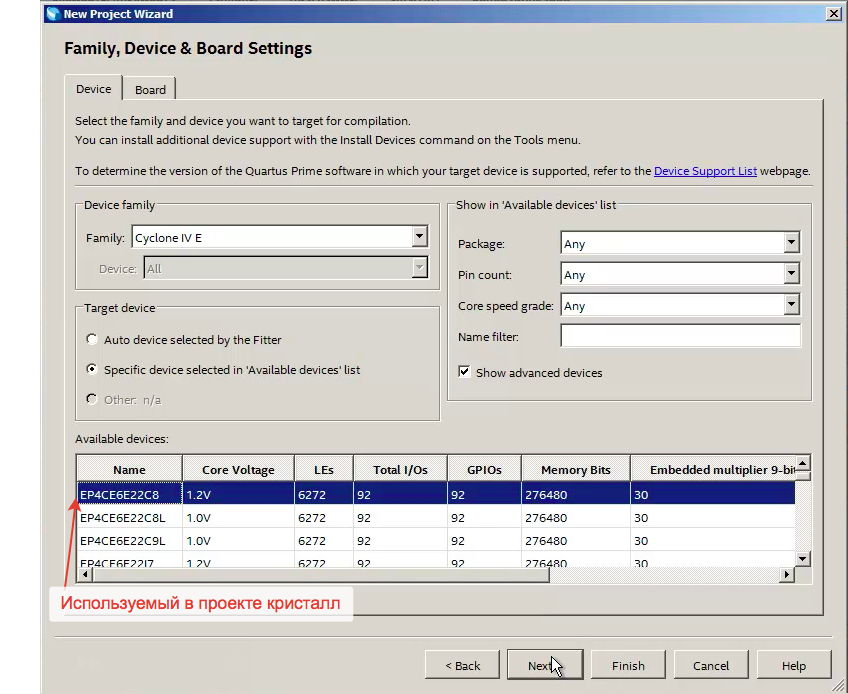

空のプロジェクトを作成します。私の家族はCyclone IV Eです。プロジェクトで使用される水晶は次のとおりです。

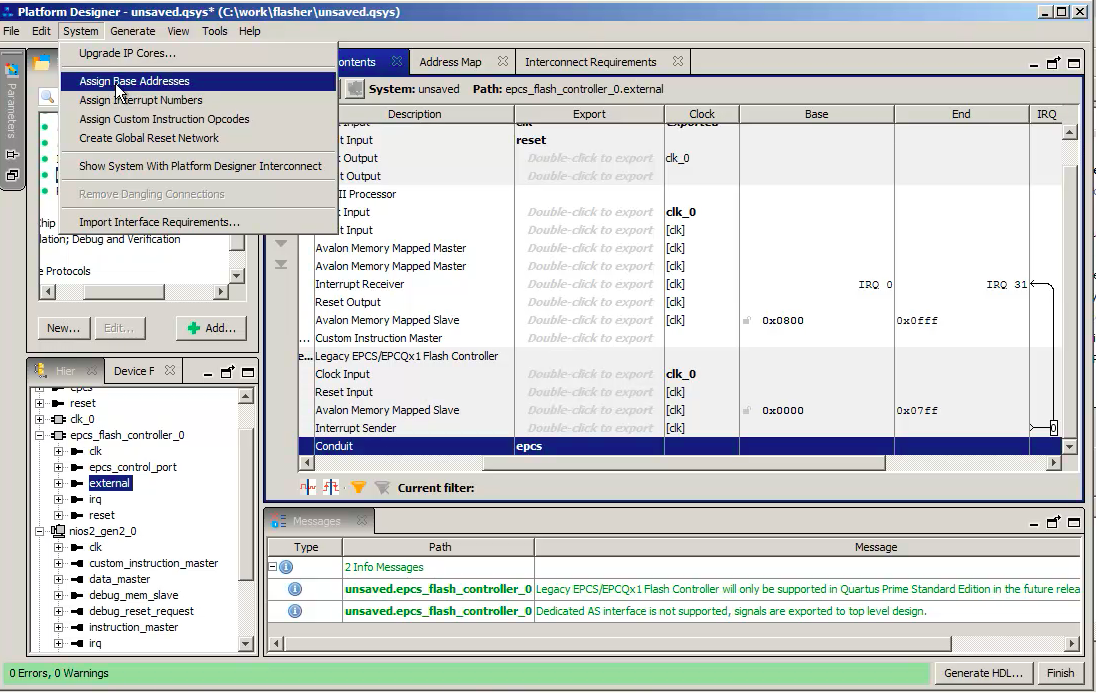

だから プロジェクトの作成を終了し、[完了]をクリックします。 プロジェクトが作成されます。 既に述べたように、コードを1行も記述しません。 しかし、あなたはまだ環境に何かをさせる必要があります。 これを行うには、ツール-プラットフォームデザイナーに移動します。

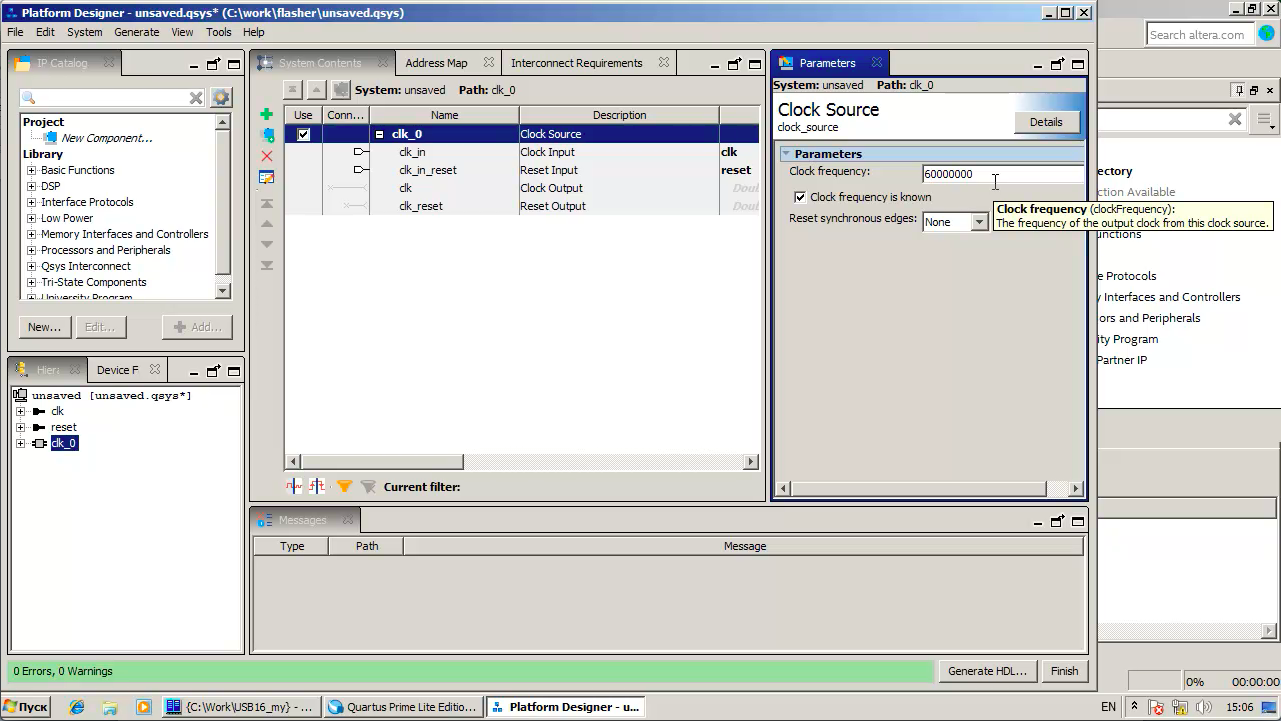

ここで起動しました。 具体的には、このボードに60 Hzの水晶があるので、周波数設定を修正します。

私が今やっていることは、プラットフォームのために一度だけです。 つまり、ある種のボードが作成された場合、このブートローダーはどのプロジェクトでも機能します。

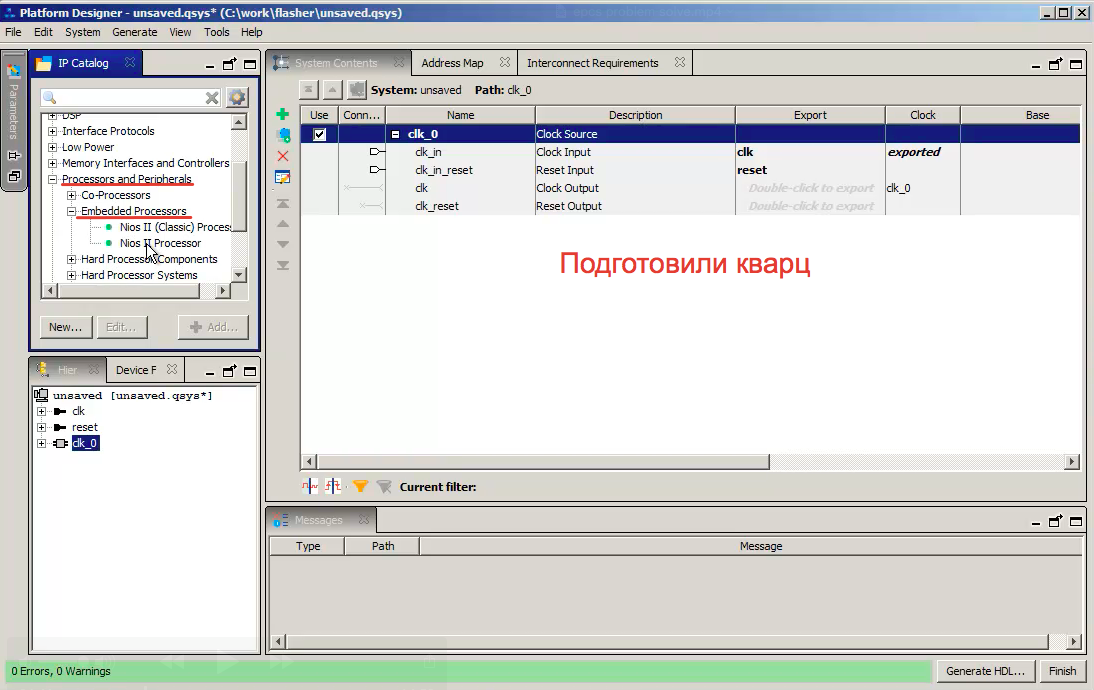

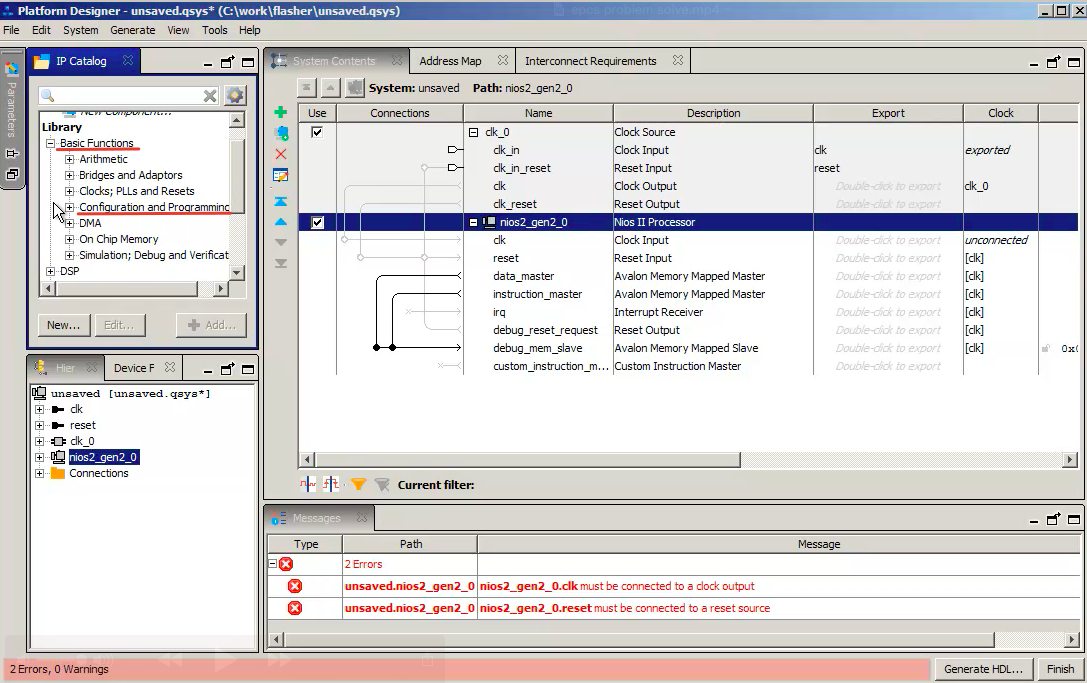

クォーツを準備しました-プロセッサを配置します。 左側のライブラリには、「Processors and Peripherals」、「Embedded Processors」、そして-Nios II Processorがあります。

それを選択して、「追加」をクリックします。

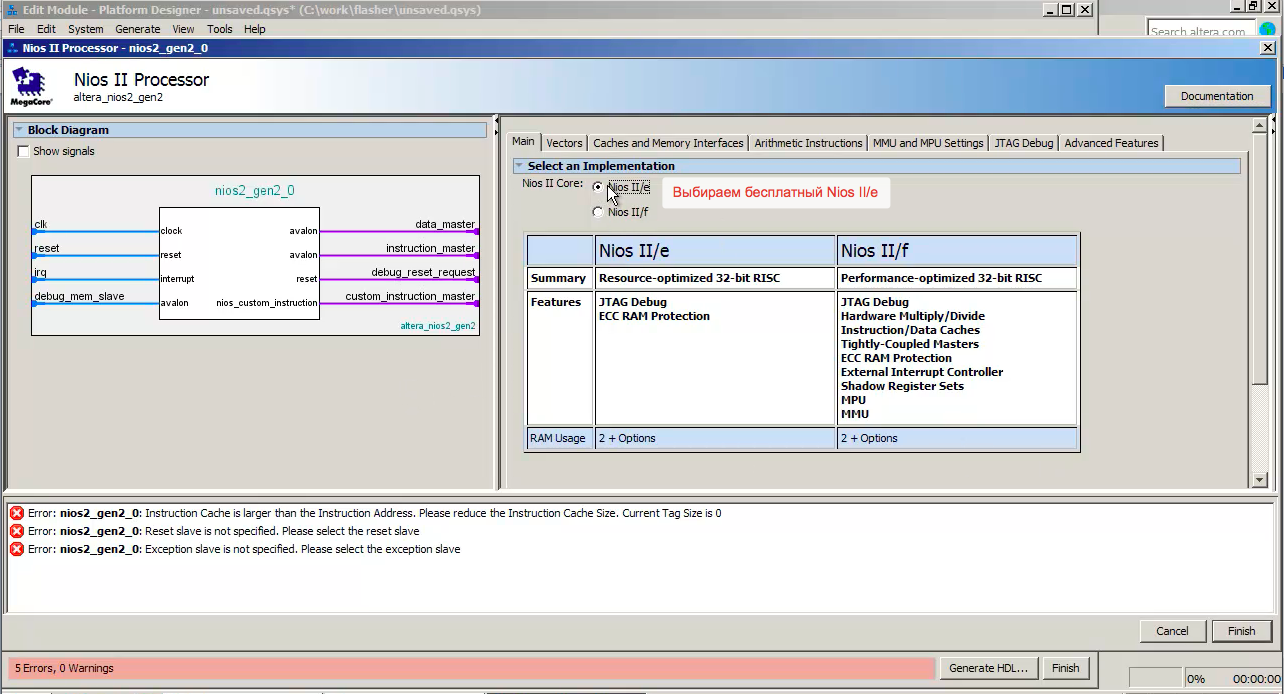

開いたウィンドウのプロパティで、Nios II / eを選択します。これは完全に無料であり、ライセンスが必要ないためです。

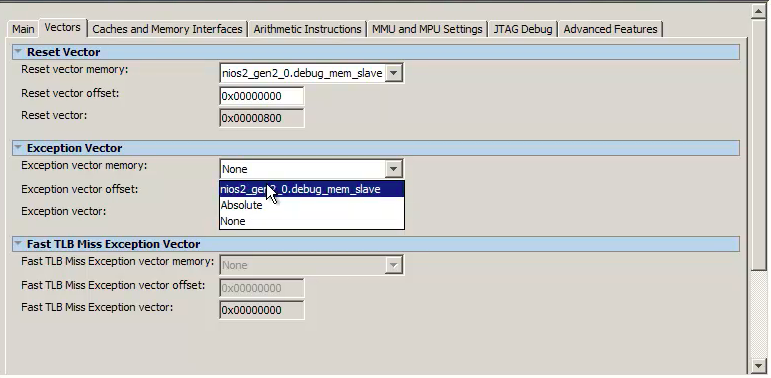

エラーは、ベクターが構成されていないことを示しています。 このプロセッサには何もプログラムしません。 したがって、ベクターをリストから最初に利用可能な場所に向けるだけです。

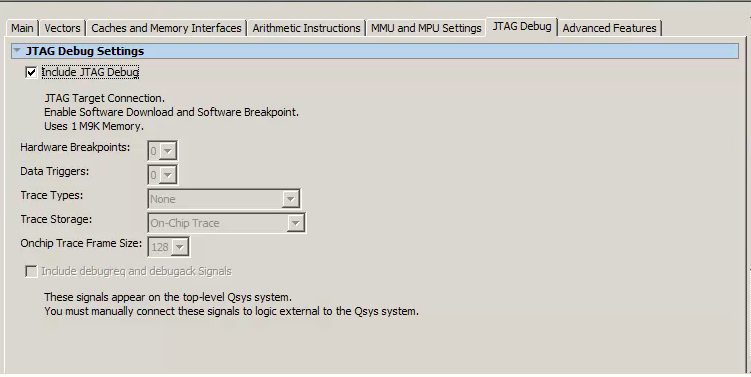

JTAGモジュールがプロセッサ上で動作することは非常に重要です。

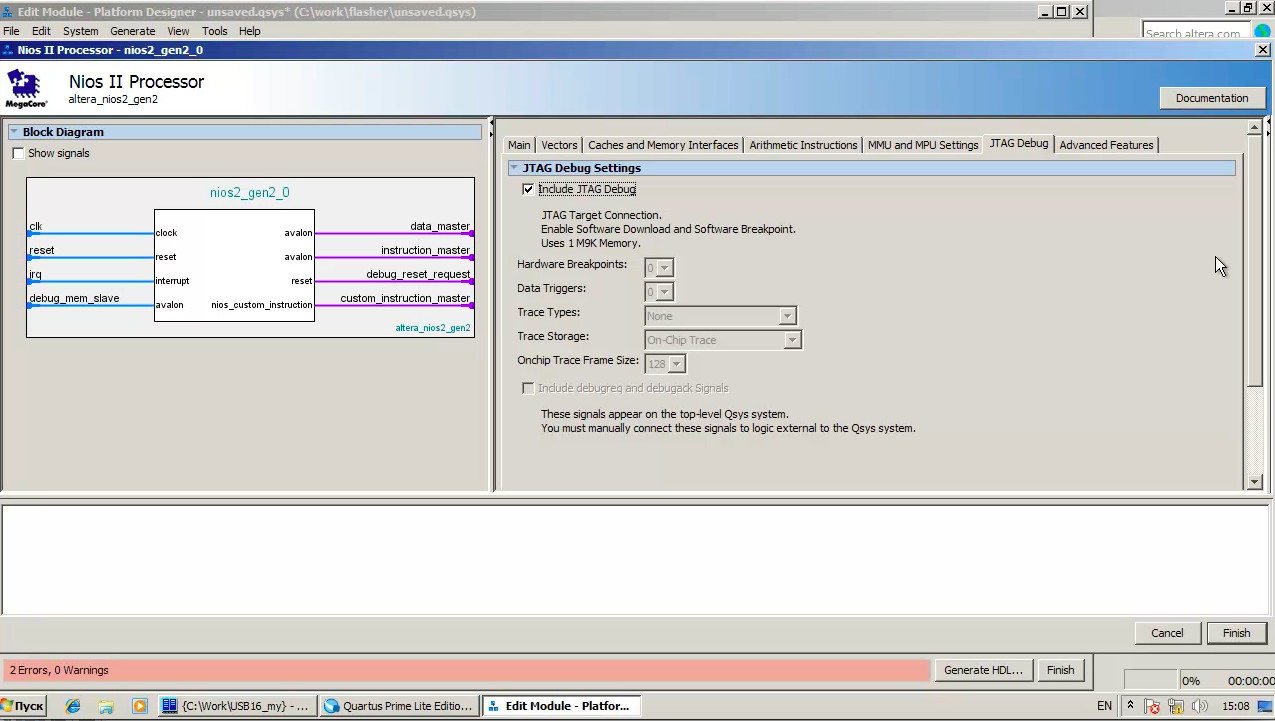

操作後、エラーはなくなりました。

プロセッサを使用します。 [完了]をクリックして先に進みます。

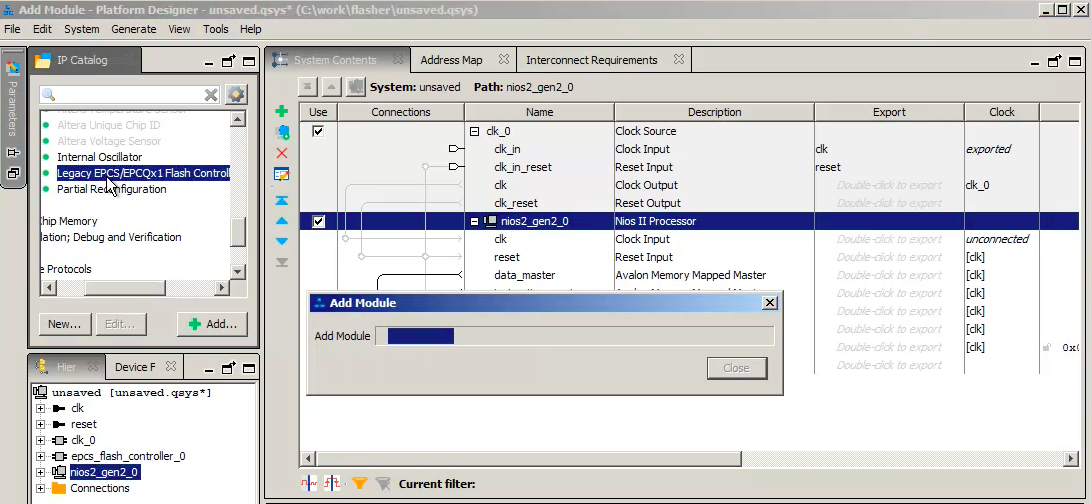

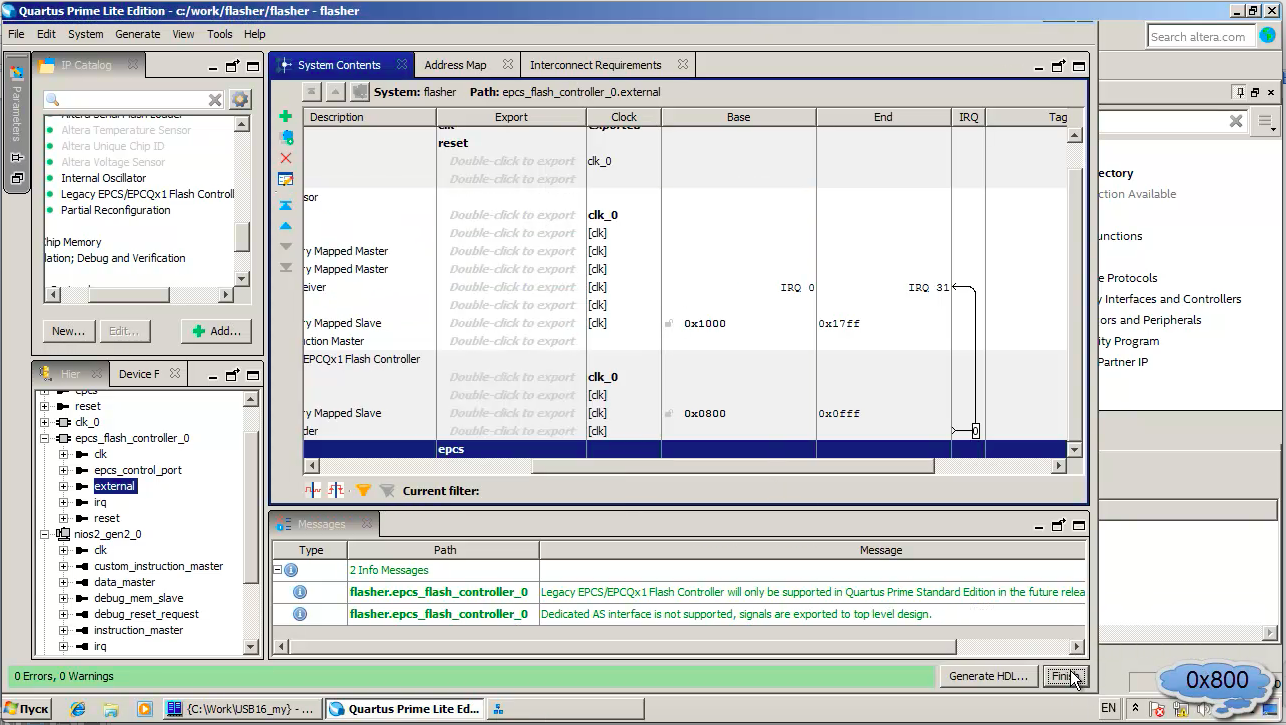

次に、主な機能に進みます。 ここにはコンフィギュレーターがあります:

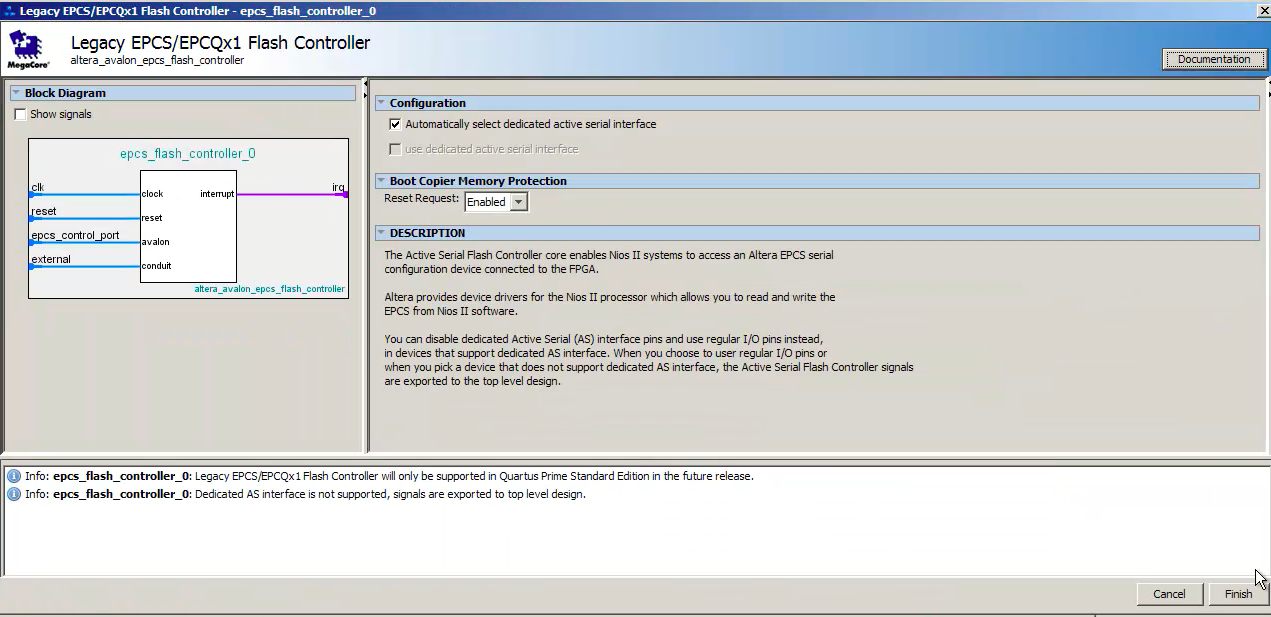

コンフィギュレーターのリストを開きます-EPCSが見つかりました-コンフィギュレーター:

デフォルトではすべてを残します:

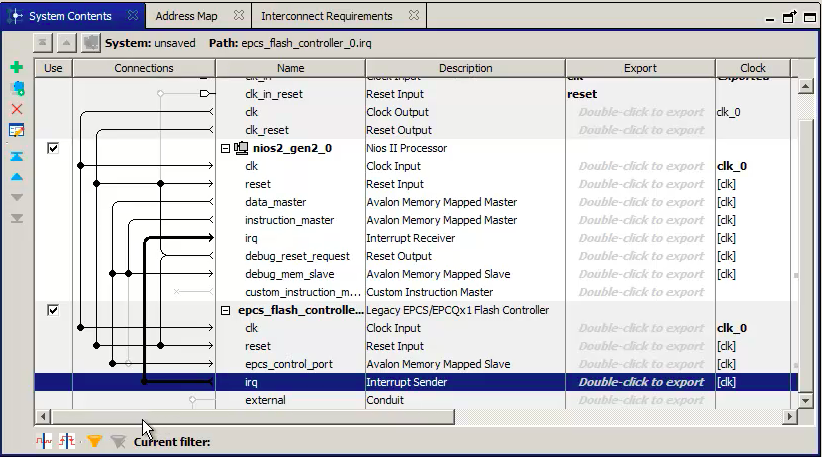

今、それらを接続し始めます。 両方のモジュールにクロック信号を渡し、両方のモジュールにリセット信号を渡します。 JTAGハードウェアから出力されるリセット信号-debug_reset_request-両方のモジュールにも渡します。 次に、両方のモジュールでdata_masterをスキップします。 Instruction_masterはデバッガーにのみ渡されます。 また、割り込み要求もスキップします。

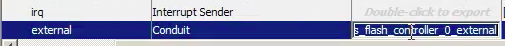

次に、外部の足に行きます-外部。 それらをエクスポートし、[エクスポートするダブルクリック]フィールドでダブルクリックします。

簡単にするために、長さが短くなるようにepcsを呼び出します。

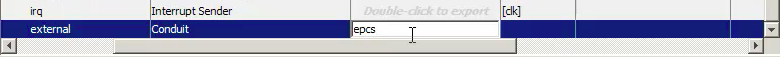

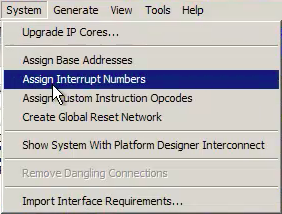

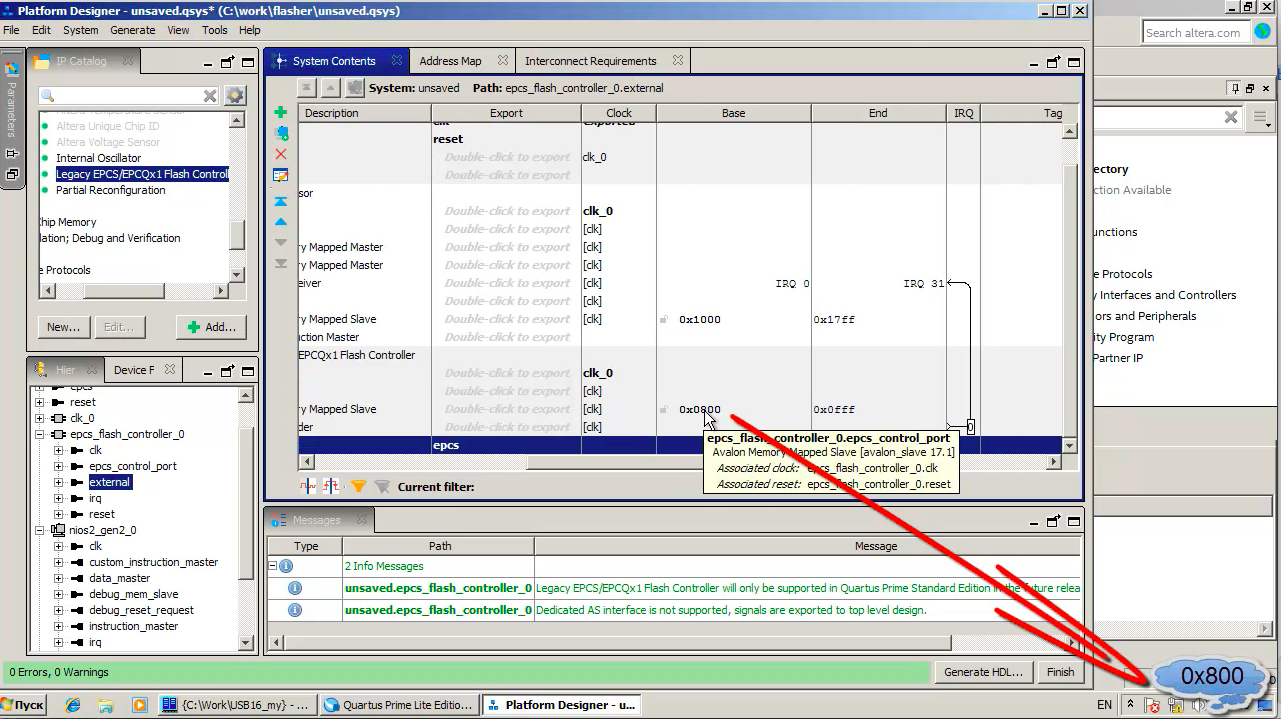

さて、通常の手の動きで、ベースアドレスを割り当てます:

そして、割り込みを割り当てます。

フラッシュコントローラーに自動的に割り当てられるアドレスは0×800です。覚えておく必要があります。

彼はまだ私たちにとって有用です。 そして、他のすべては、原則として、機能し、機能します。

プロセッサシステムの名前がプロジェクトの名前と一致するようにコードを1行も記述しないため、これは非常に重要です。 私たちが持っていたプロジェクトはもっと派手でした。

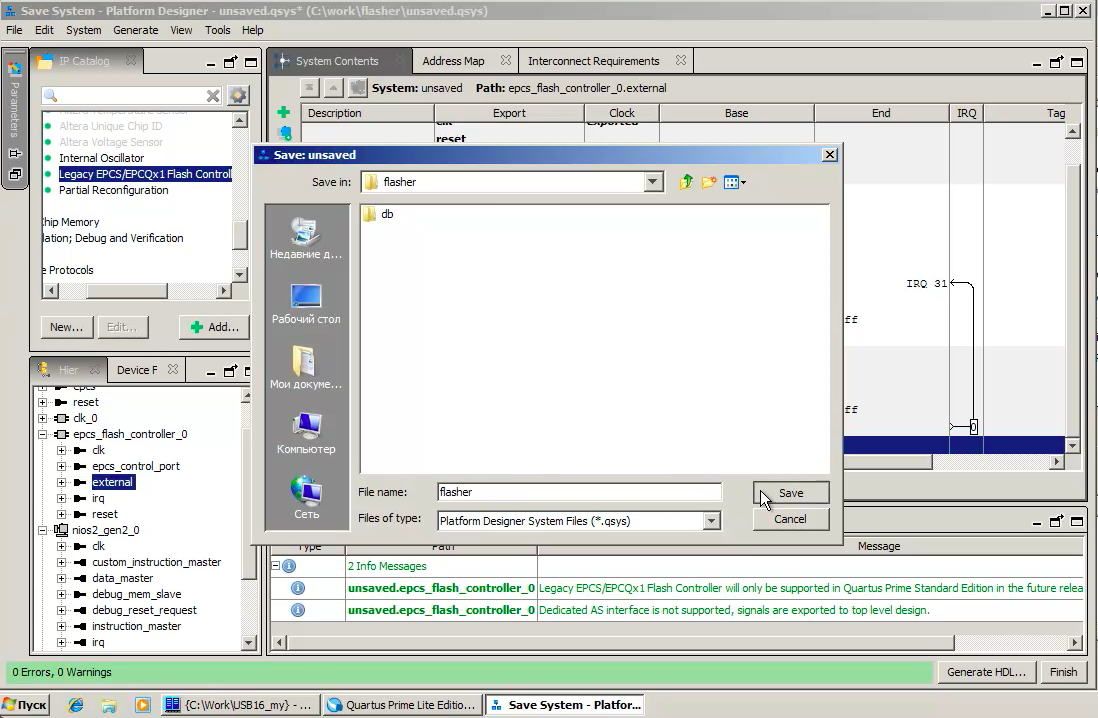

システムを保存し、フラッシャーを呼び出します。

その場合、最上位のモジュールがこのプロセッサとまったく同じになるため、何もする必要はありません。

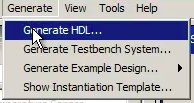

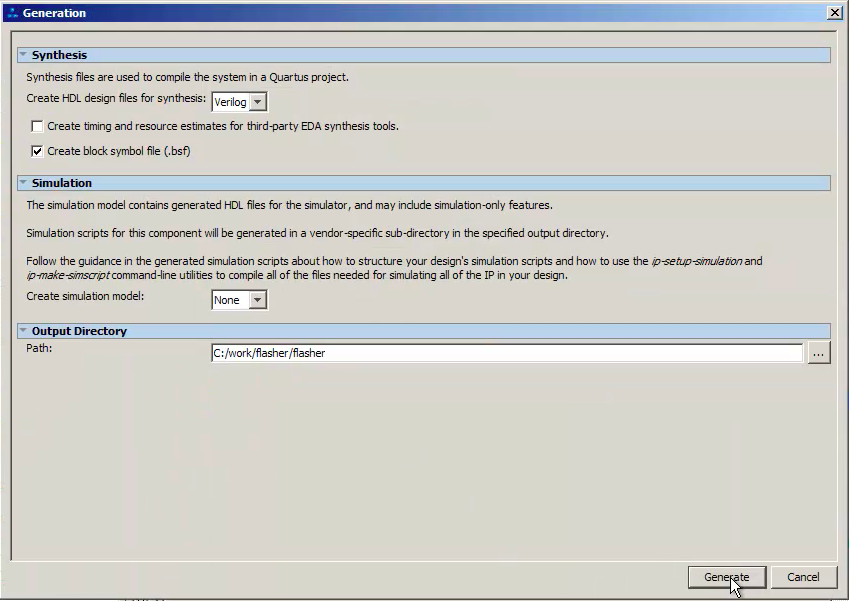

次のステップ:

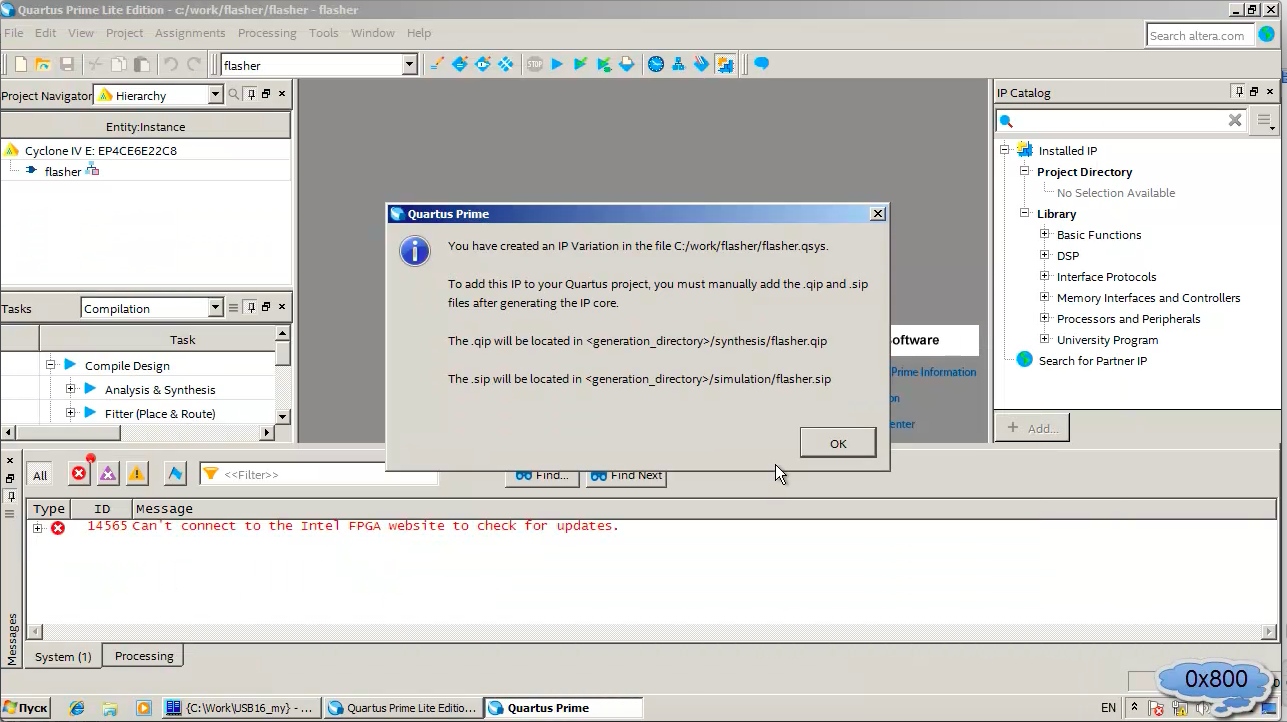

すでに用意されているものを使用するため、デフォルトではすべてを残します。

結論:

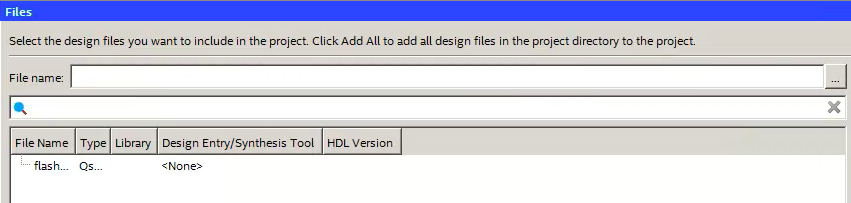

ファイルをプロジェクトに追加することを覚えておく必要があるというメッセージがありました。

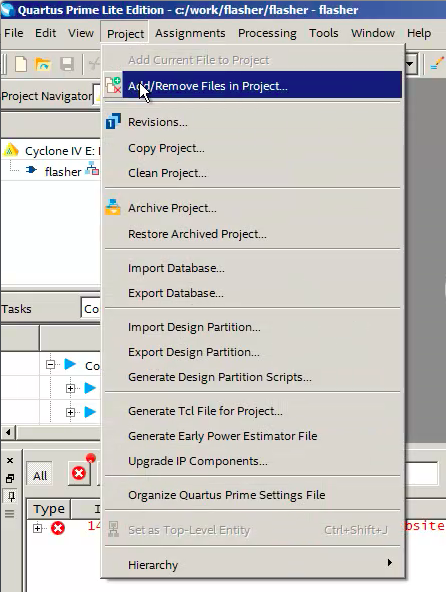

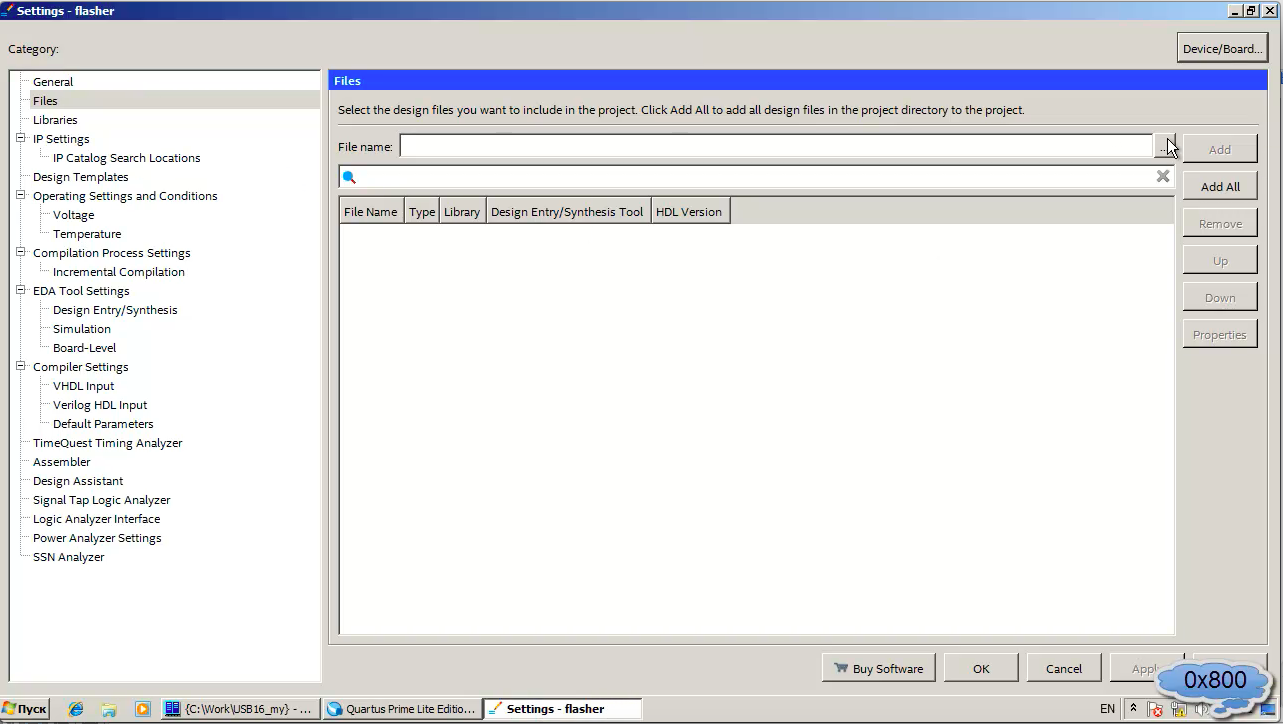

追加してみましょう。 プロジェクトに移動-プロジェクトでファイルを追加/削除:

ファイルはコンピューター上にあります。

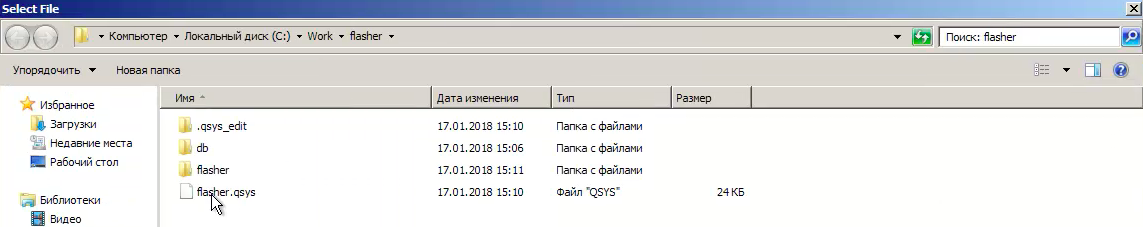

ここに、qsys拡張子を持つフラッシャーファイルがあります。

追加しました:

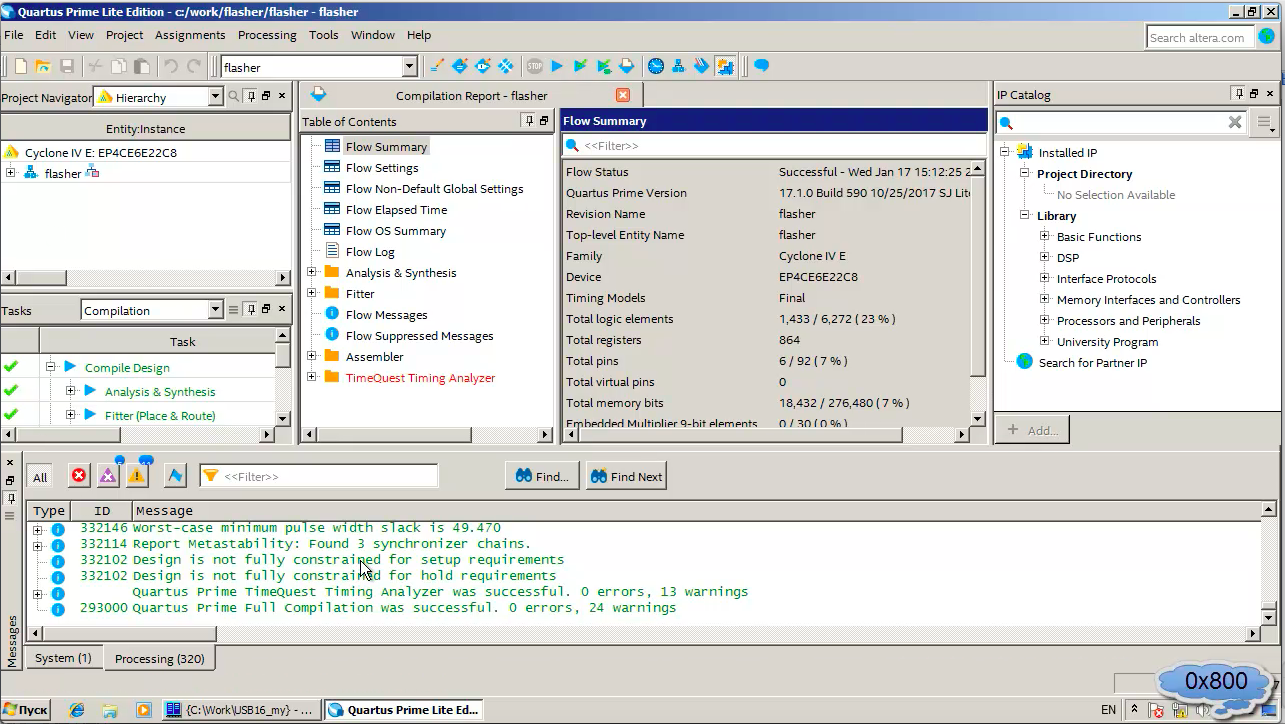

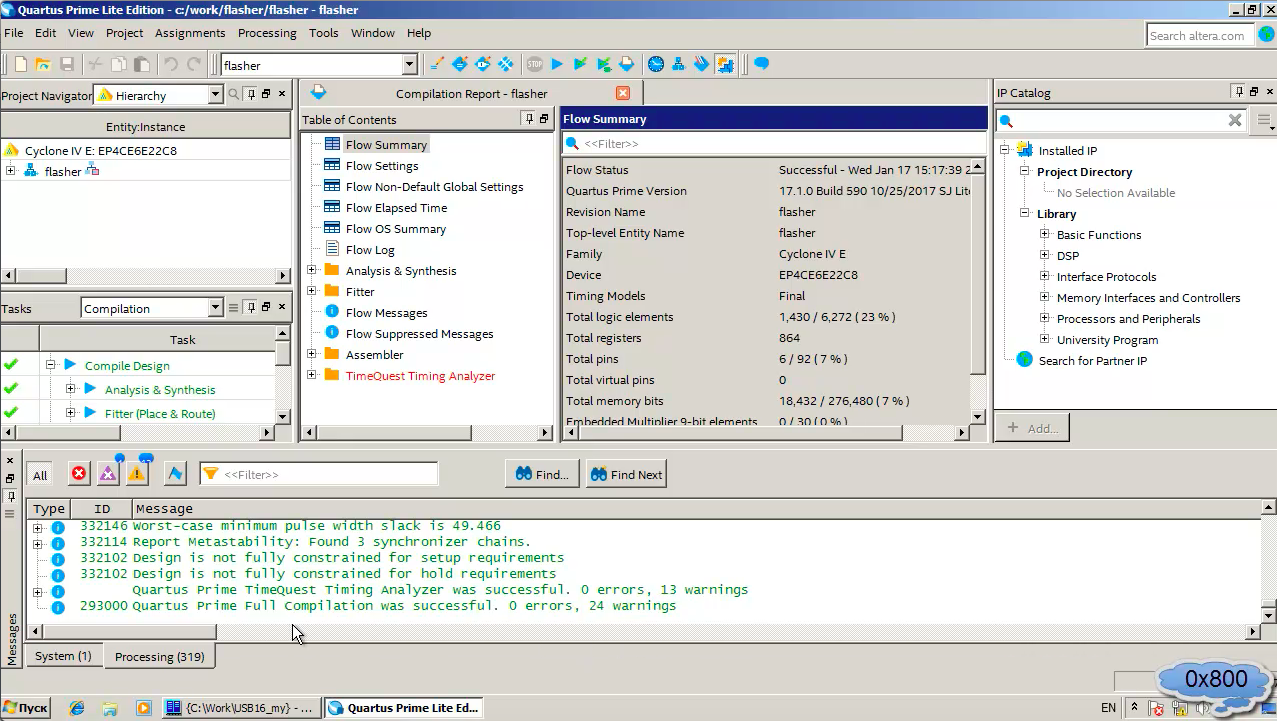

次に、大まかなコンパイルを行います。

彼女は正常に完了しました。

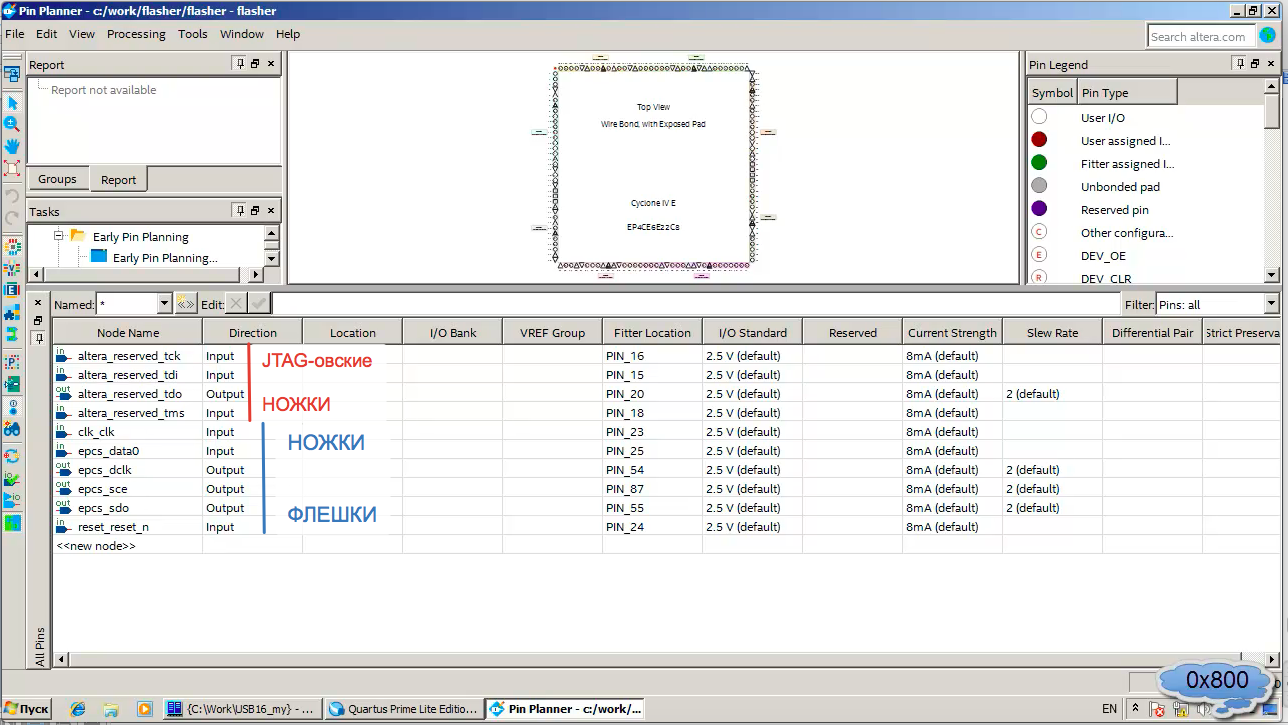

彼女が合格したので、結論を出すことができます。 ピンプランナーに移動します。

JTAGレッグを割り当てる必要はありません-フラッシュドライブのレッグを割り当てます。

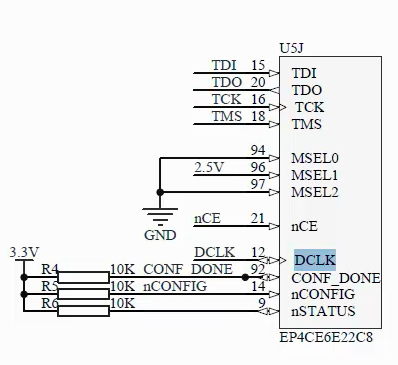

チップごと、ケースごとに異なります。 原則として、チップまたはボード上のドキュメントを見ることができます。 たとえば、DCLKの12番目のレッグは次のとおりです。

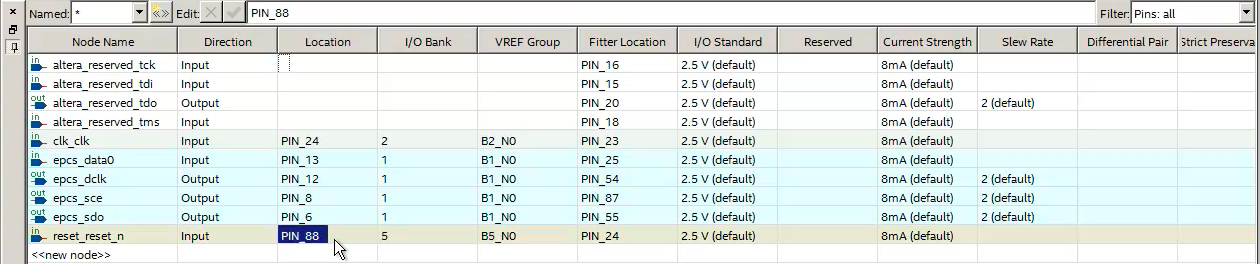

私のリストはすでに準備されています-ただそれを運転してください。

したがって、epcs_data0、場所:PIN13、epcs_dclk-PIN12、epcs_sce-PIN8、epcs_sdo-PIN6。 特にお客様のボードでは、クロック周波数はPIN24、reset_n-PIN88です。

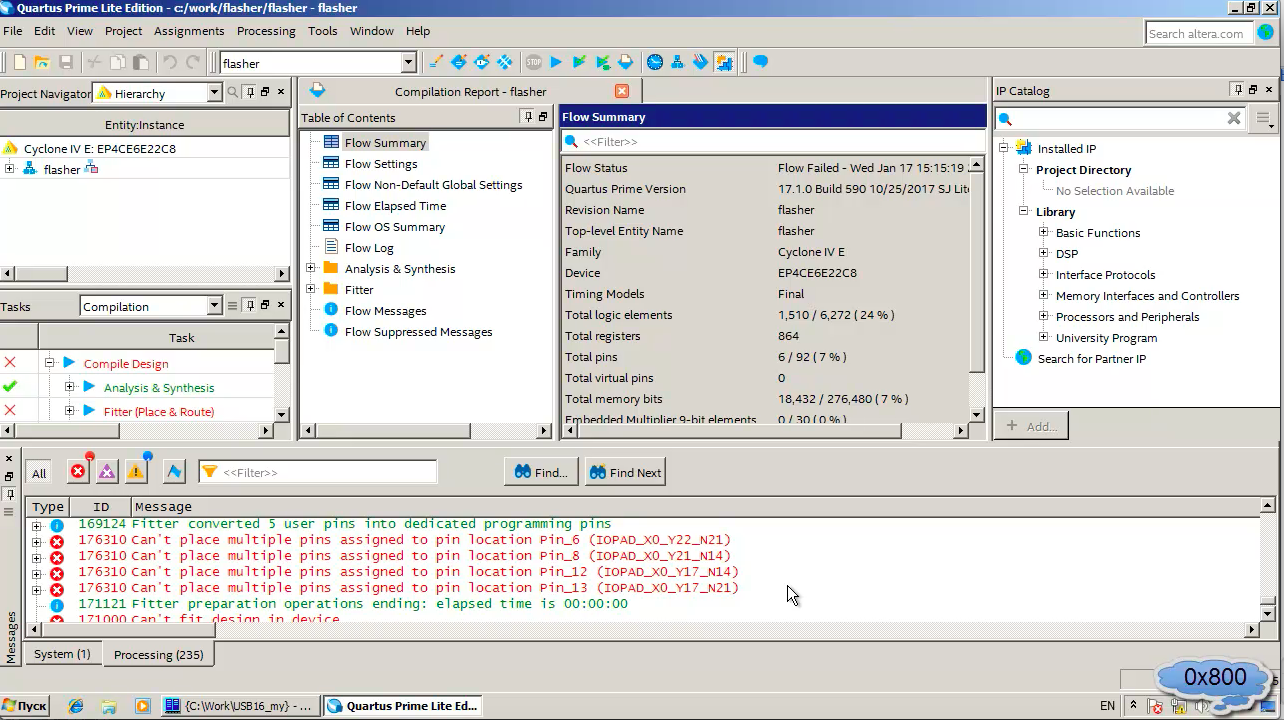

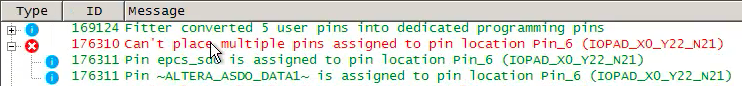

脚が指定されています。 コンパイルを開始します。 エラーが発行されます:

それは、私が非常に重要なセットアップをするのを忘れるふりをしたからです。 これで、USBフラッシュドライブがサービス回線に接続されました。 また、構成の最後に、これらの行の一部はまったく使用できず、一部は公式の目的で使用されます。 したがって、競合があるというメッセージが表示されました。

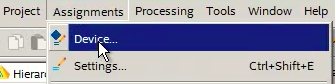

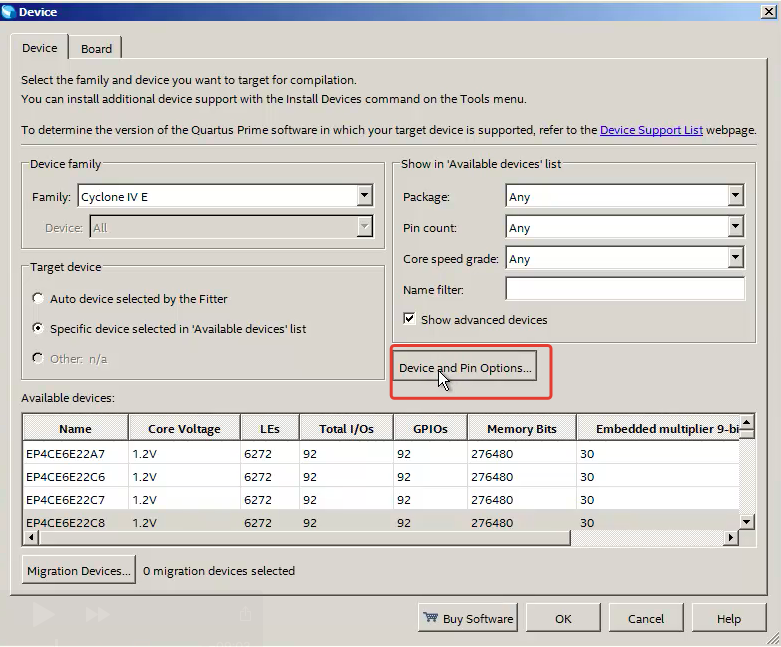

これを修正するには、割り当て-デバイスに移動します。

デバイスとピンのオプション:

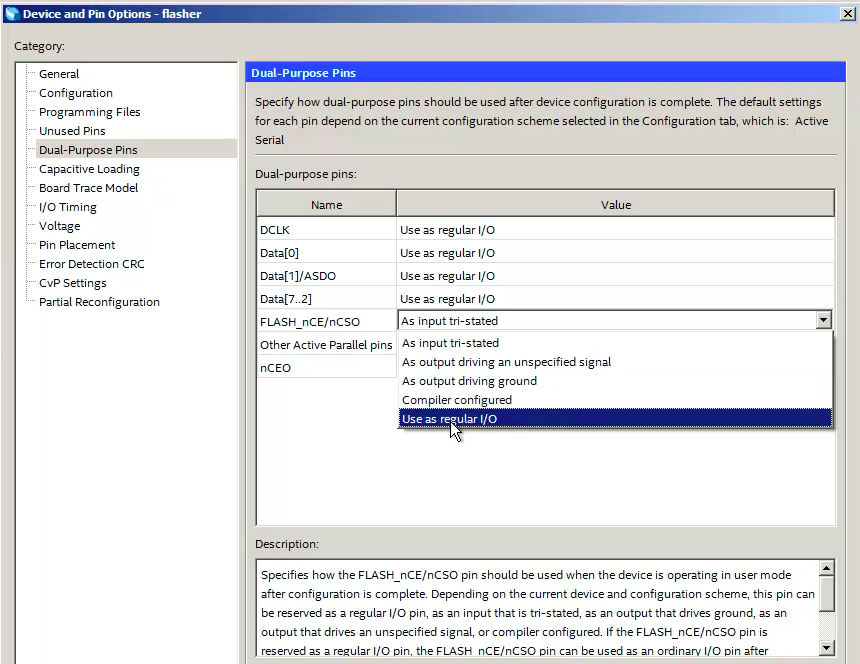

ここでは、デュアルパーパスピンを選択します。 プログラミングの最後に、これらの行をすべて通常のI / O行にするようにお願いします。

[OK]をクリックして、コンパイラを実行します。 そして、すべてうまくいきました。

これで、最初のステップが完了しました。 フラッシュドライブをタップできる構成を取得しました。

ここでのタスクは、システムがUSBフラッシュドライブを認識するファイルを作成することです。

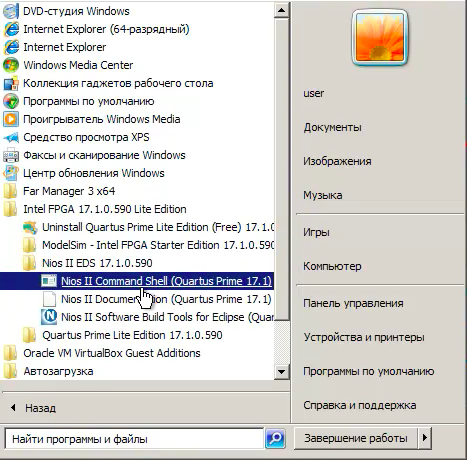

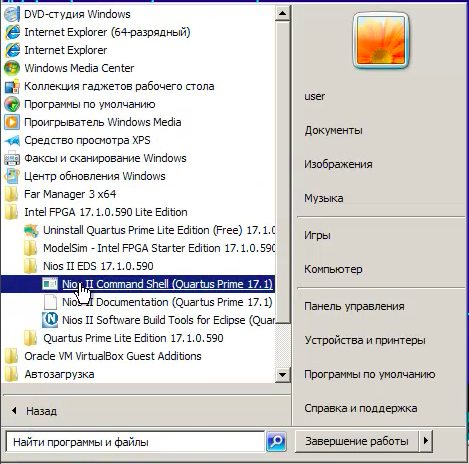

すべてのプログラム、Intel FPGA(旧バージョンの場合はアルテラ)、Nios II Command Shellにアクセスします。

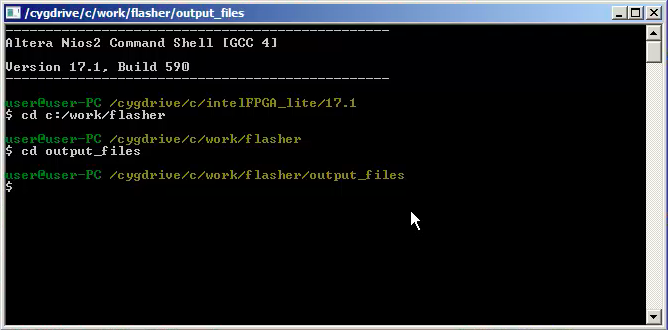

ここで、すべてを収集したディレクトリに移動します。 同時に、ここのスラッシュは逆ではなく、直接であること、および結果のflasher.sofファイルがoutput_filesディレクトリにあることを忘れないでください。

今、私たちは魔法の呪文を唱え始めます。 そのため、新しく形成された構成を挿入する必要があります。 これを行うには、次のように記述します。

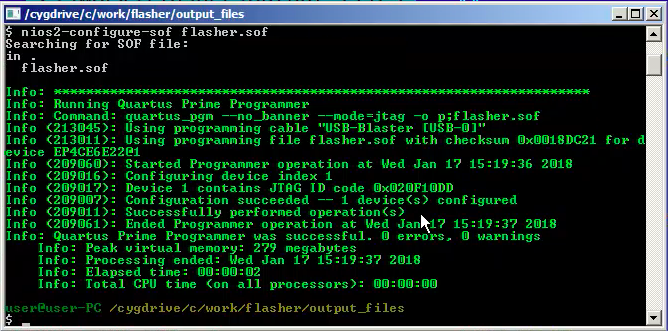

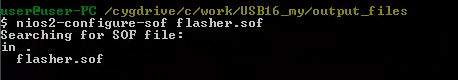

nios2-configure-sof flasher.sof

Enterを押します。

ファイルがアップロードされました-これでフラッシュドライブにアクセスできます。 フラッシュドライブへのアクセスに関するすべてを判断するには、次のプログラムを実行する必要があります。

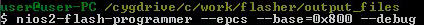

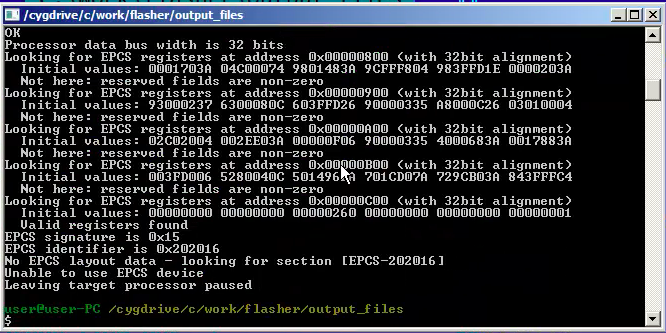

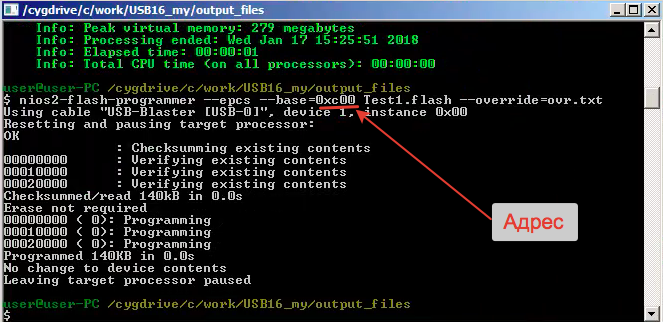

nios2-flash-programmer --epcs --base = 0x800-デバッグ。

0x800は、epcsブロックに自動的に割り当てられた同じアドレスであり、忘れてはなりません。

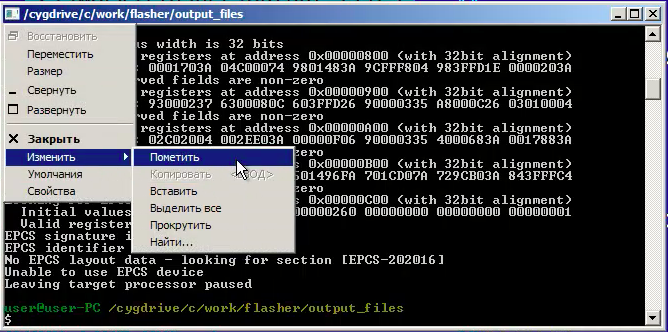

Enterを押します。

彼は私たちに何を伝えましたか? 彼は私たちが命名したエリアを調べようとしました。 800のオフセット0では、何も見つかりませんでした。 c00で、彼は必要なものを見つけました。

ここで、ベースアドレス800だけでなく、特定のアドレスc00を覚えています-将来的にはそれを使用します。

彼はフラッシュドライブを見つけました、その識別子は202016です、しかし彼はそれを知らないので、彼はそれをどうするかわからないと言いました。

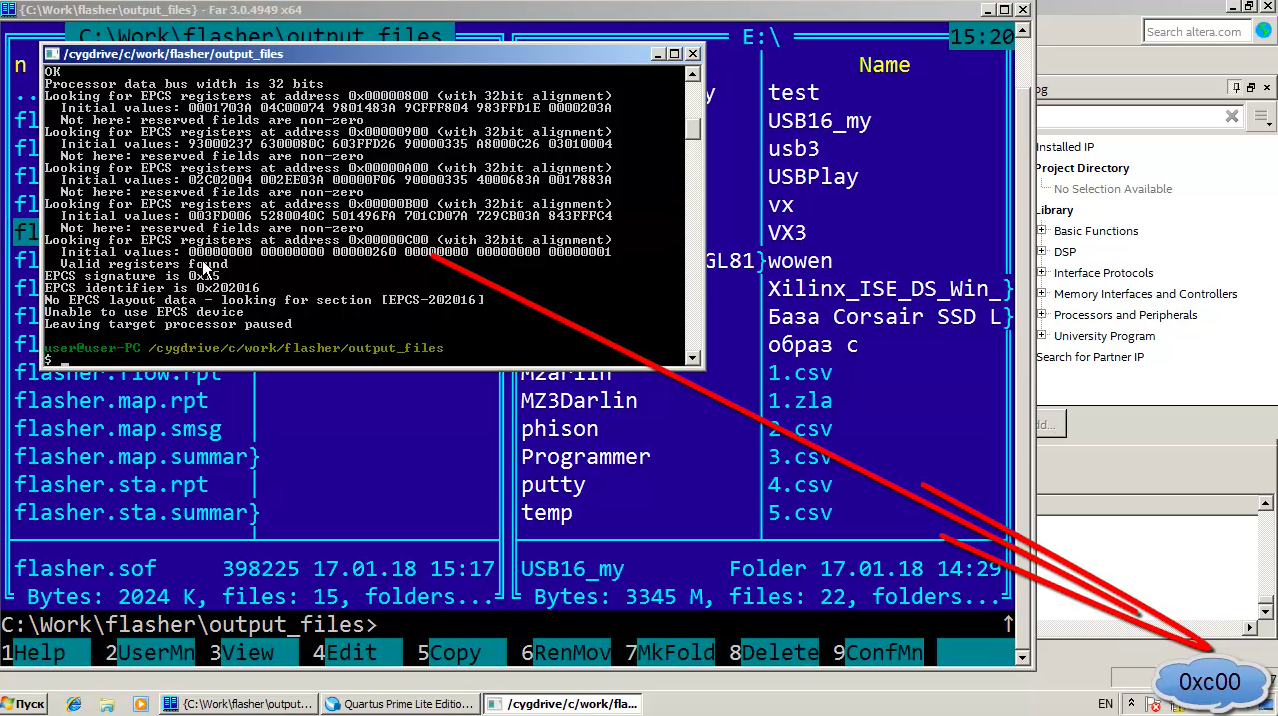

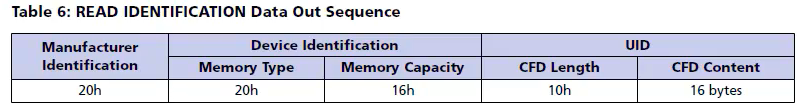

フラッシュドライブのドキュメントは次のとおりです。

その完全な識別子は202016です-コードを要求するコマンドに応答して返されるということです。

すべてが正しいので、フラッシュドライブが正しいことがわかりました。

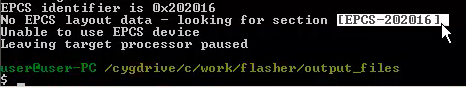

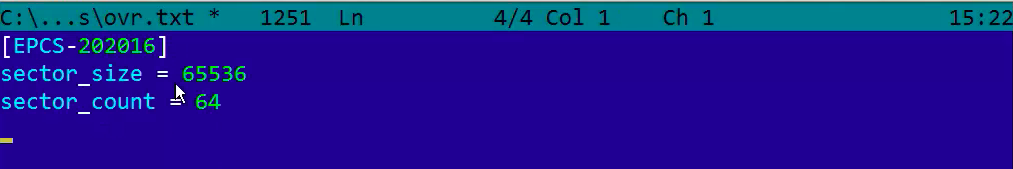

彼はEPCS-202016セクションのファイルがあるべきだと言っています。

いいね 編集-マーク。 彼女の名前を選択して、クリップボードに移動します。

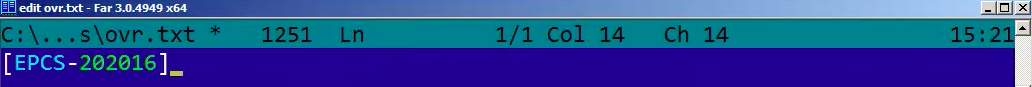

ovr.txtファイルと、コピーした名前のセクションを作成します。

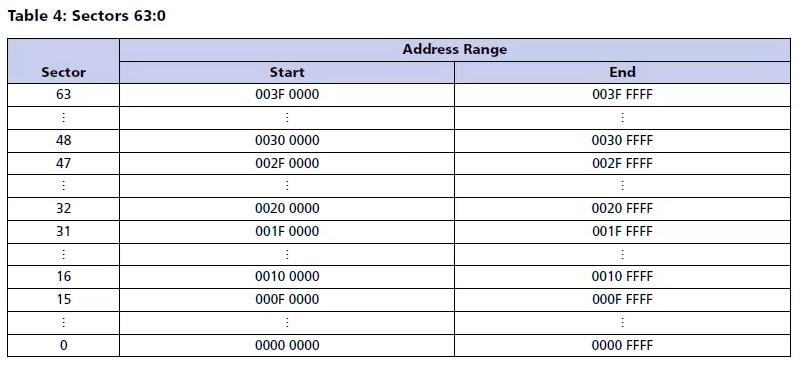

フラッシュドライブのドキュメントの「メモリマップ」セクションで、64セクターで構成されていることがわかります。 0000からFFFFであるため、各セクターのサイズは64 KBです。

したがって、作成した構成ファイルは次のようになります。

64 KBの64セクター、またはそれぞれ65536バイト。

2番目のステップの準備ができました。 flasher.sofファイルとovr.txtファイルには、フラッシュドライブ構成が含まれています。

3番目のステップに進みます。

作業ドラフトはUSB16_myだったことを思い出させてください。 そして、ファームウェアファイルはTest1.sofと呼ばれていました。 flasher.sofとovr.txtをコピーします。

これですべての準備手順が完了しました-直接戦闘作戦に進みます。 準備と仕事の間につながりがないことを強調するために、あたかも翌日、1週間、1か月、または準備が完了した後であればいつでも、ターミナルに再び入ります。

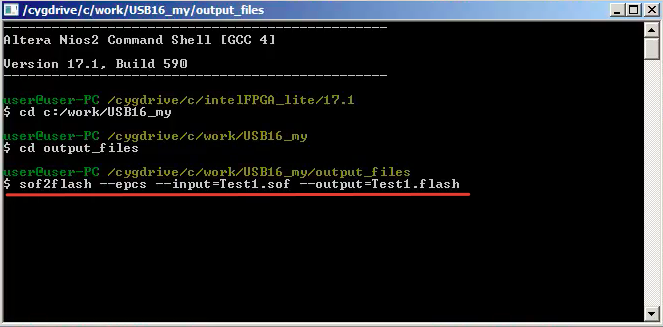

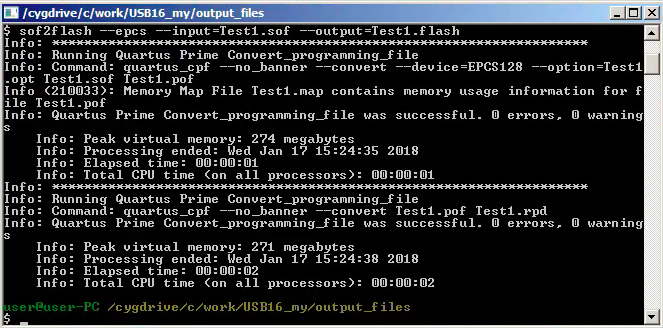

最初に行う必要があるのは、出力ファイルを生成することです。 sofファイルはROMに縫製されていないため、わずかに異なるファイルが縫製されています。 それを形成するために、次のように書きます:

ファイルTest1.flashが判明しました:

さて、純粋に形式的には、ボードビルダーが行うべきアクションに変わりました。 まず、同じようにフラッシャーをロードする必要があります。つまり、

その後、ROMをフラッシュする必要があります。

実際、それだけです。 この問題は解決され、フラッシュドライブがフラッシュされます-メインパスがIDシュニックの不一致について話していたとしても、それを使用できます。 また、高価なコンフィギュレーターを購入したり、25番目のフラッシュドライブに互換性のあるIDを持つベンダーを探す必要はありません。 特定のボード用に「フラッシャー」を用意し(同じチップが配置され、ジェネレーターでリセットされるものはすべて同じ出力に接続されます)、コンフィギュレーター用のテキストファイルを用意し、キットに含まれるユーティリティを使用して「ファームウェア」を追加しました標準のQuartus Prime環境の配信(Quartus II環境にも付属)。