なぜプログラマーはこれを必要としますか? 結局のところ、電子工学は(はるかに少ない)電子工学の学部で教えられており、学生は最初に電気の物理学、アナログ回路を研究し、マルチプレクサを備えたいくつかのラボを作ります。その後、これはすべて忘れられ、プログラマとして働くようになります。

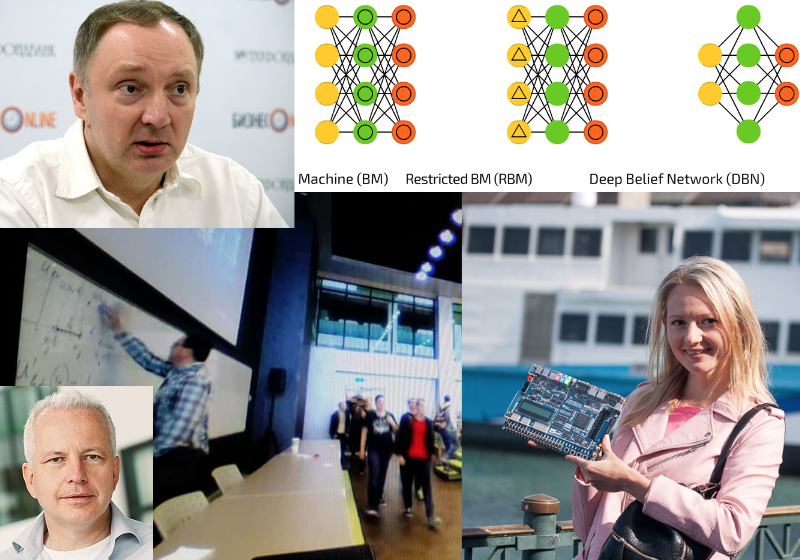

プログラマーにデジタル回路が必要な理由の1つは、最近のニューラルネットワークの台頭です。 複雑なネットワークのトレーニングに数週間/日/時間ではなく、時間/分/秒かかる場合は、ハードウェアアクセラレータなしでは実行できません。 メモリの海への同時トランザクションで低精度の多数の乗算を実行するために並列化された専用ハードウェアのみ。 将来的には、AI用の専用ASIC(特定用途向け集積回路)をあらゆる場所で待っています。 従来のプロセッサと大規模なAIブロックの両方を搭載し、部分的な再構成が可能です。

GoogleとMicrosoftからSkolkovoとInnopolisまで、このようなコプロセッサーを構築できる専門家が必要であるという理解が高まっています。 ソフトウェアエコシステムとアルゴリズムを理解しながら、ハードウェアマイクロアーキテクチャを所有する必要があります。 また、マイクロアーキテクチャーの所有権は、レジスター転送のレベルの理解に基づいています。 Innopolisでの実装方法:

イノポリスのコンピューターアーキテクチャのコースは、彼のカザンに招待された外国の専門家とともに、その指導者アレクサンドルトルマソフと、イノポリスの学部長として働くイタリア人のジャンカルロスッチ教授、およびイノポリス以前に韓国とパキスタンの大学で働いたムハンマドファヒムによって開発されています。

イノポリスの前のトルマソフ学長は、モスクワ物理技術研究所のコンピューターサイエンス部門の責任者であり、SWsoft(後のParallels)の先進開発部門の責任者として、仮想化に従事していました。 Paralellsは、アメリカで広く知られている数少ないロシア企業の1つです。Parallelsはロシア企業であり、米国企業だと思ったと少なくとも2、3人のアメリカ人エンジニアが驚きました。 さらに、トルマソフはIEEE Computer Societyのロシア支部を率いています。

Tormasovは30年前にあらゆる種類の新しい小さなことを紹介するのが大好きでした。それから彼はMIPTの学生にUnix、シェル、awkなどを使うように教えました。 その時点ではLinuxは存在せず、UnixはNational Semicondustor NS32000プロセッサを搭載したオーストラリアのLabtamコンピュータ上にありました。 Tormasovの前、学生はBESM-6でFortranカードとパンチカードを使って働いていました。

そこで、最近Tormasovから、彼のコンピューターアーキテクチャのコースでのHDL、RTL、FPGAについてのいくつかの講義をスカイプするように頼まれました。 200人以上の学生がこれらの講義に参加しているため、実験には適切な選択があります。 トルマソフは、1)イノポリスに外国人学生がいること、2)ジャンカルロ・スッチとムハンマド・ファヒムも英語を読んでいること、3)学生が私のウクライナの強調を含む理解を訓練する必要があるため、英語で講義をするように頼んだ。

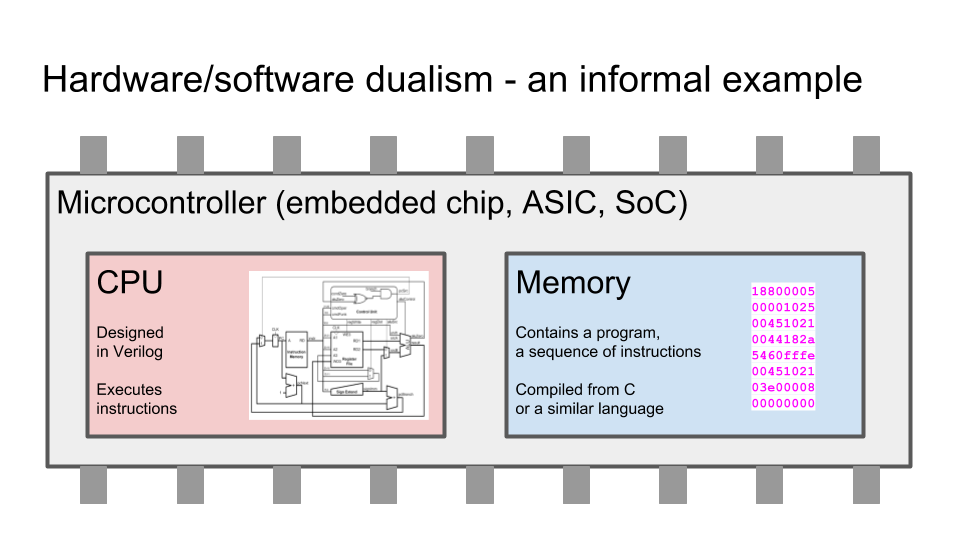

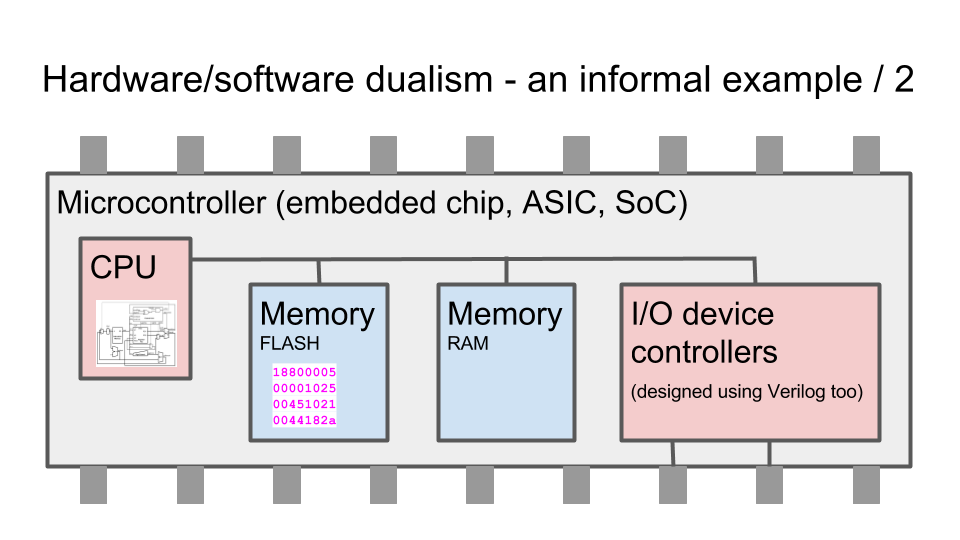

最初の講義の目的は、学生がソフトウェアシミュレータで最も単純な回路をシミュレートし、この回路を合成してFPGAを構成できるように十分な情報を提供することでした。 回路がプログラムではないことを明確に示すことも必要でした:

PDF形式の最初の講義のスライド。

2回目の講義の目的は、デジタルロジックのトピックをさらに深く掘り下げたい場合に、彼らを待っているものの概要を説明することでした。 彼らは、Dフリップフロップ、シーケンシャルロジック、ステートマシン、およびパイプラインの概念を理解する必要があります。 その後、アクションを繰り返したり、センサーから情報を送信したりする興味深い回路を作成できます。 -プロセッサコアまで。

PDF形式の2番目の講義のスライド。

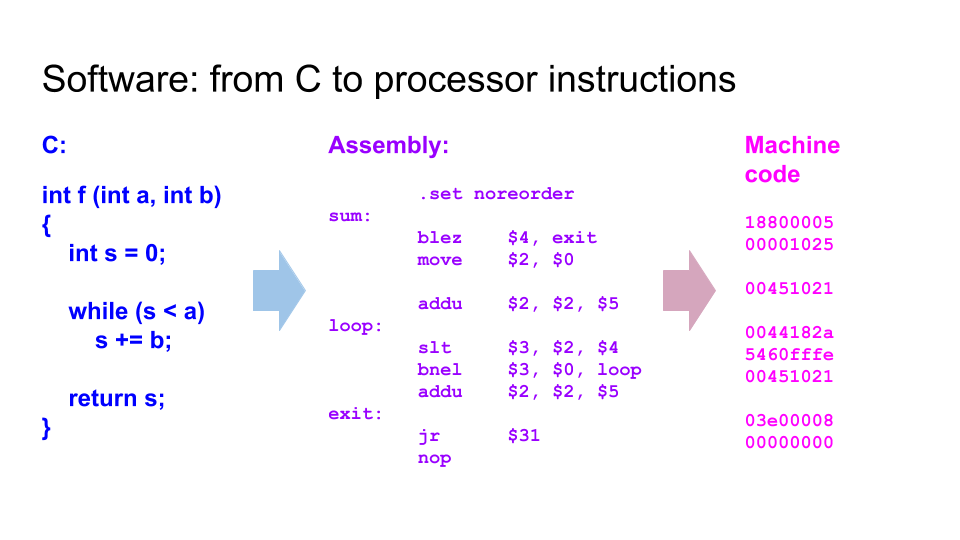

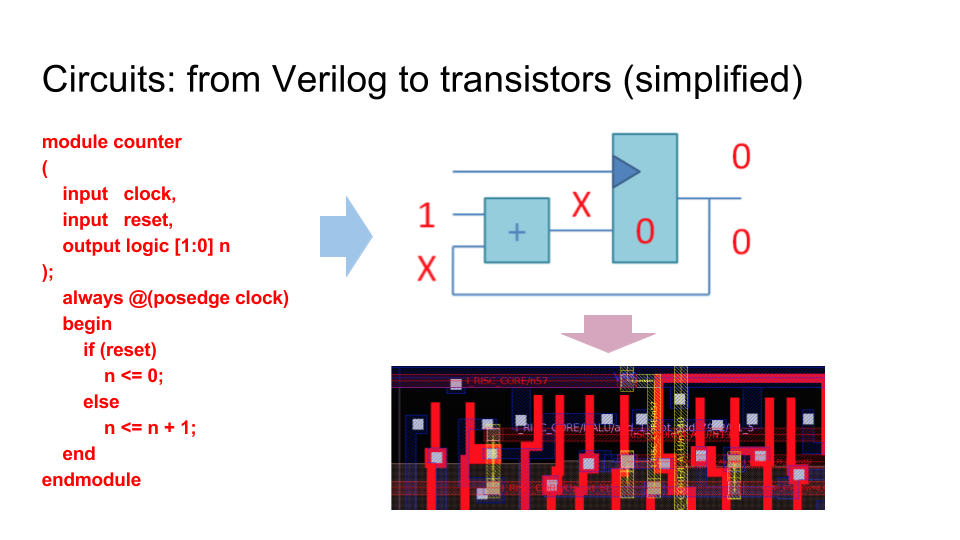

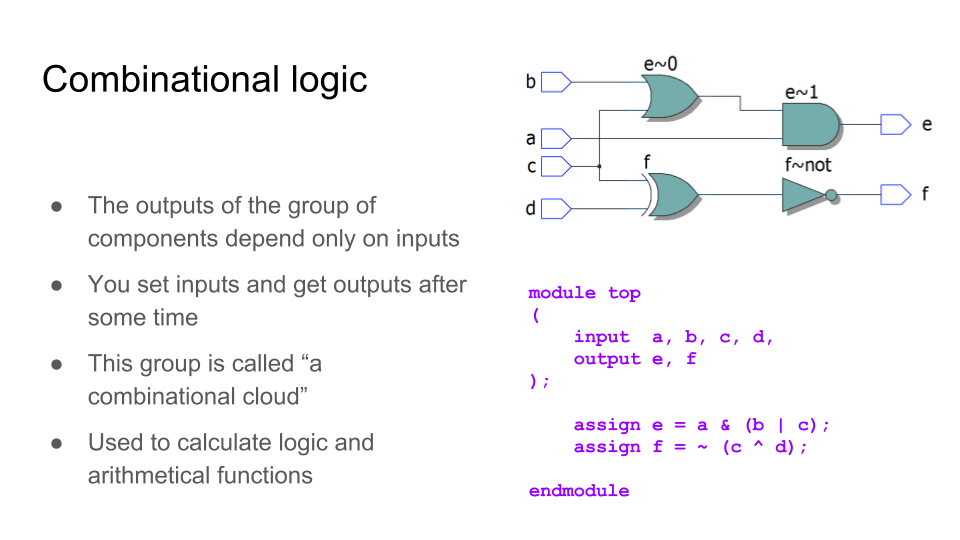

いくつかの重要なスライド。 スキームとプログラムの違い。 プログラミング言語(Cなど)は、プロセッサがメモリから選択する一連の命令にコンパイルされます。 ハードウェア記述言語(Verilogなど)は、工場で焼かれたチップ上のトランジスタとトラックに最終的に変わる論理要素からグラフに合成されます。

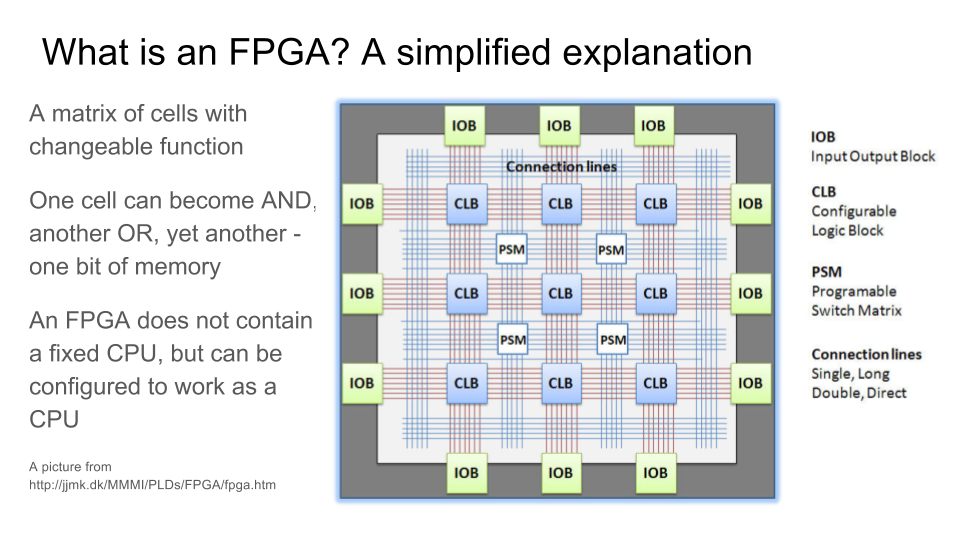

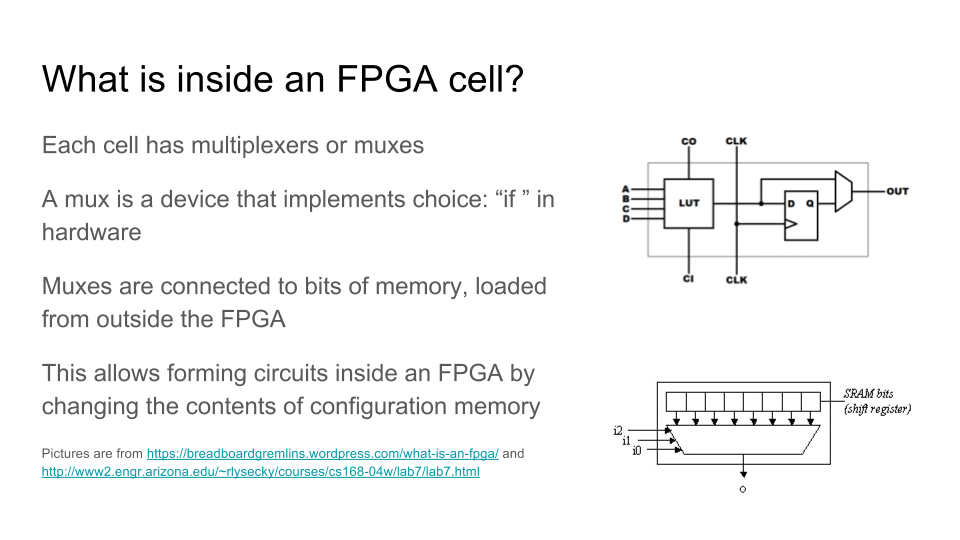

FPGA / FPGAの仕組み-構成要素のビットに接続されたマルチプレクサーを使用して機能を変更できる論理要素のマトリックス:

最も単純なスキーム。 組み合わせロジック-入力にデータを入力し、しばらくしてから(伝播遅延を伴って)出力で答えを取得します。

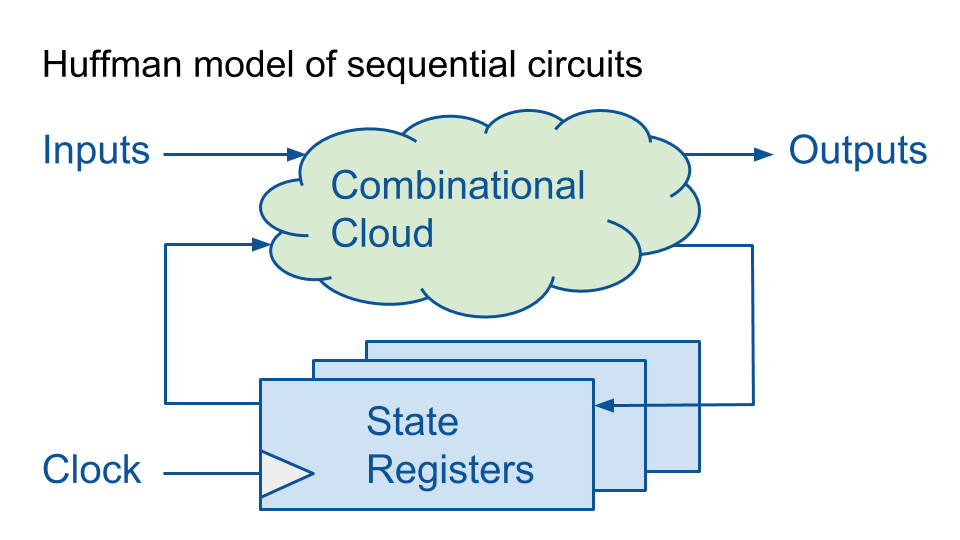

ハフマンモデルは、シーケンシャルロジックを導入するのに便利です。 組み合わせロジックは、レジスター(メモリー要素)に接続されています。

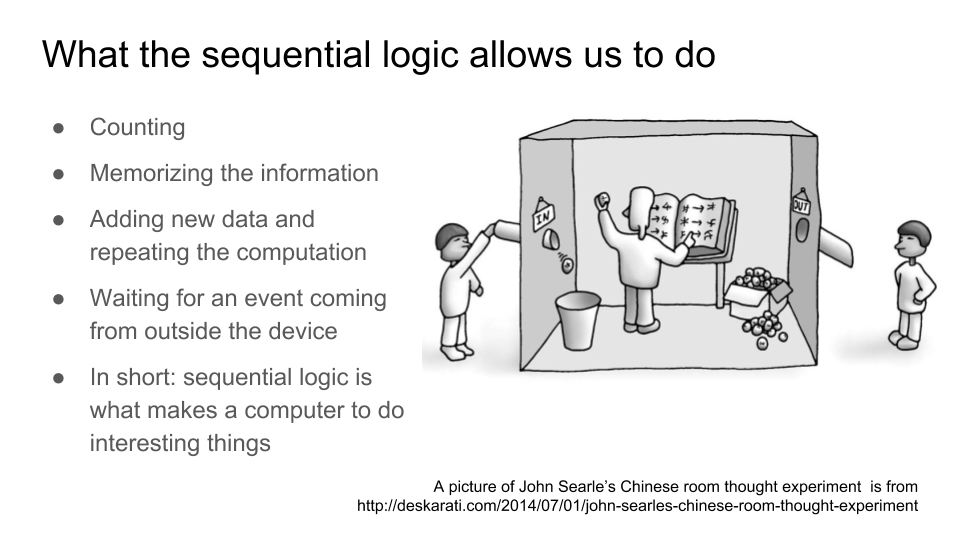

シーケンシャルロジックにより、コンピューティングデバイスは重要なことを実行できます。 それがなければ、組み合わせ論理でのみ、引数から値が一意に決定される関数のテーブルしか計算できませんでした。 シーケンシャルロジックは、現在の状態を回路に追加します。その結果、読み取り、イベントの待機、古いデータと新しいデータに基づく操作の繰り返しなどが可能になります。 ここで私は「中国の部屋」について言及します-「機械が考えることができますか?」というトピックを議論する際に浮かび上がる人気のパラドックス中国の部屋は、本質的に有限状態機械の一般化であるハフマンモデルの実装の1つです。

デジタル回路の入門コースで理解する必要がある主な概念は、基本的な状態要素であるDトリガーの機能です。 論理要素AND-OR-NOTが原則として幼稚園の子供にも説明できる場合、Dトリガーを使用すると、学生は精神的な障壁を抱えることになります。 そして、学童だけでなく、デジタルロジックを理解するのを妨げられた経験のあるプログラマーの間でもあります。デジタルロジックは、命令の連鎖として頭の中にしっかりと成長したプログラム実行の精神モデルです。 代わりに、数千または数百万のDトリガーの同時記録など、多くのイベントが同時に発生するメンタルモデルを使用する必要があります。

Dトリガーは、クロック信号の1サイクル中に1ビットの情報を保存するデバイスです。 クロック信号(クロック、CLK)、書き込み用の入力(D)、読み取り用の出力(Q)の3つの主な外部信号があります。 出力Qでは、Dトリガーの保存された状態が出力され、ほぼ全サイクル中の入力DはDトリガーを無視します。 入力Dは、クロックCLKが0から1に変化すると、短いアパーチャの現在の状態に書き込まれます。 クロック信号の正しい周波数で、アパーチャの瞬間までに、Dトリガーの入力に、組み合わせロジックの計算の定常状態の結果があります。 そして、この時点まで、機器内の計算は即座に行われないため、ごみは入り口に置かれます。

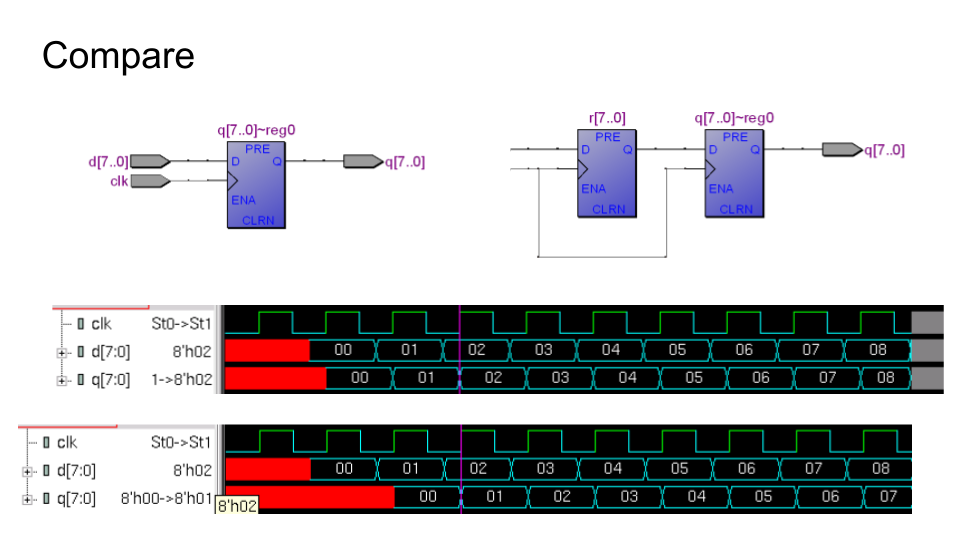

レジスタ、数ビットのセットのストレージは、Dトリガーから構築されます。 レジスタの出力では、サイクル全体が前のサイクルでレジスタに書き込まれた値です。 レジスタを1つずつ配置すると、この組み合わせの出力は、前のサイクルの値になります。

組み合わせ加算器とレジスタを組み合わせると、カウンターが得られます。 このアニメーションでは、Xは「止められない値」を意味します。 クロック信号の周波数は、ユニットへの追加が終了することが保証されているときにレジスターへの書き込みが発生するように選択され、その量をレジスターに書き込む必要があります。 この金額は、次のサイクルの用語の1つとして使用されます。

次に、有限状態マシンに関するスライドがあります。これは、デジタル回路とコンピューターアーキテクチャの本に基づいて作成しました。 デビッド・M・ハリス、サラ・L・ハリス。 そして、コンベア処理の原理についてのいくつかのスライド。

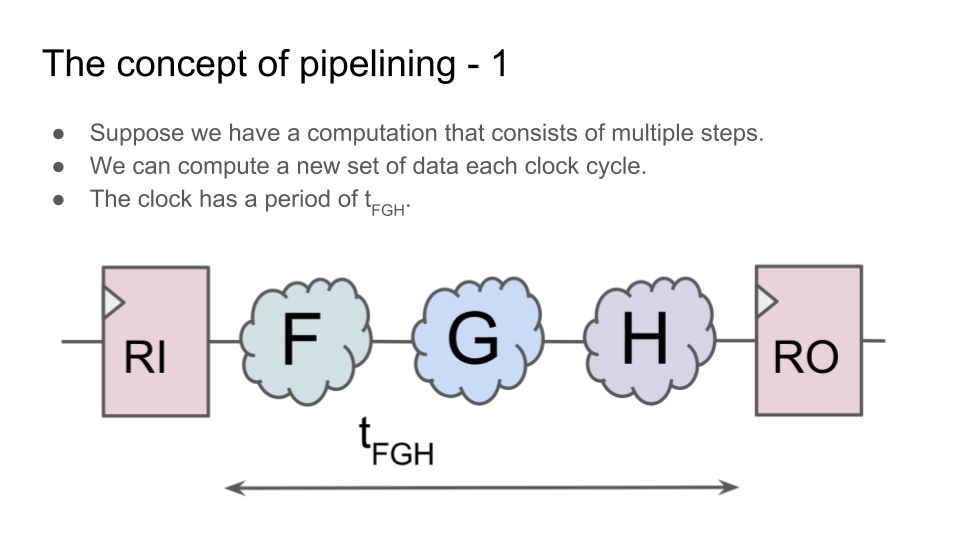

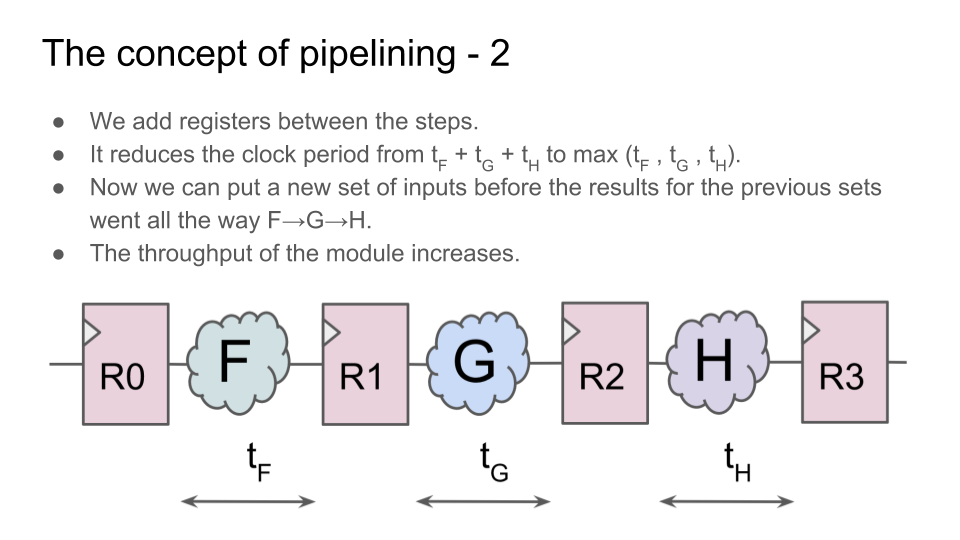

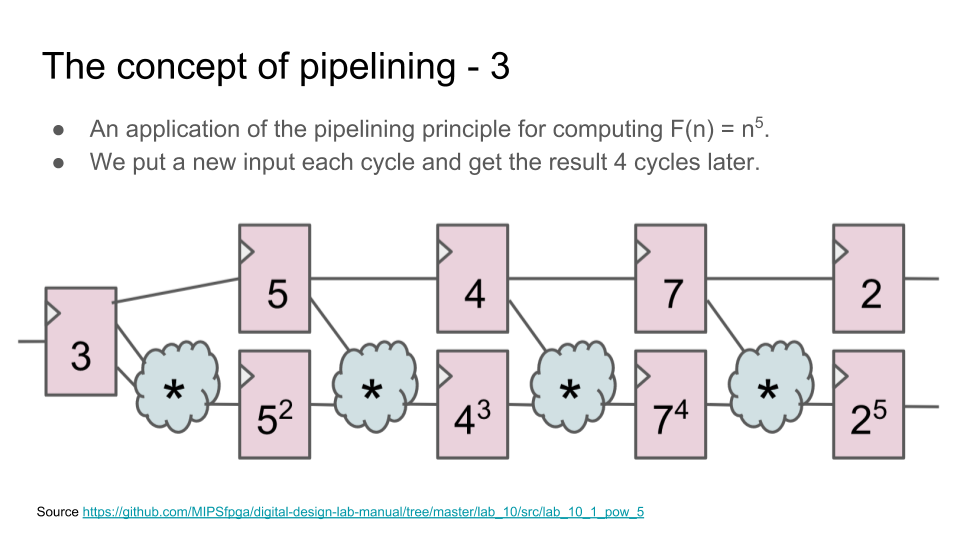

コンベアは、デジタルエレクトロニクスの現代開発における重要な概念の1つです。 パイプラインは、プロセッサーの設計(実行パイプ)だけでなく、演算ブロックの設計、メモリへのトランザクションのブロック、ルーターチップ内のパケットの処理、3次元グラフィックスのシェーダーでも発生します。 最も簡単な方法は、演算ブロック、たとえば累乗するブロックを例として使用して、パイプラインの基本的な考え方を説明することです。

いくつかの連続したステップに分割できる操作を実行します。 ここで、すべてのステップを1サイクルで実行する代わりに、ステップ間にレジスタを配置します。 今では、操作は1サイクルではなく、いくつかのサイクルで実行されますが、

1)回路はより高いクロック周波数で動作できます。

2)新しい計算のオペランドは、前の計算のすべてのサイクルの終了を待たずに、前の計算の最初のサイクルの直後に入力できます。

3)したがって、ブロックの合計スループットは、1サイクルで計算が実行されるブロックのスループットよりも高くなります。

2回目の講義のビデオ:

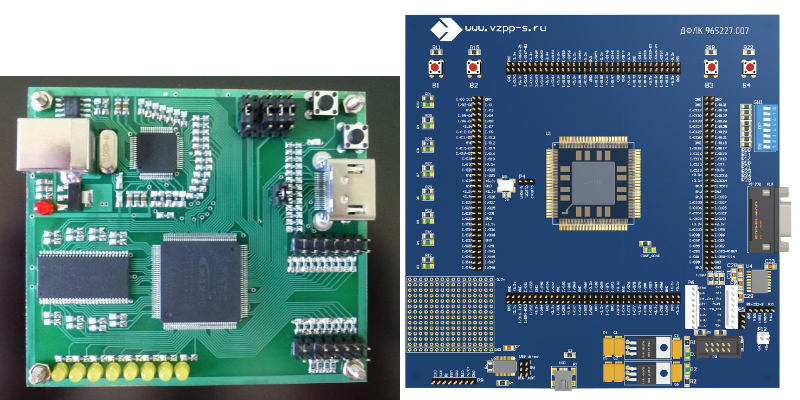

今、実験室の仕事のためのボードについて。 このコースは実験として導入されたばかりなので、イノポリスのFPGAボードに予算は割り当てられませんでした。 私は自分のお金で買った10枚のボードをイノポリスにリースしましたが、ボードは非常に不足しています(コースの210人の学生)。 「より多くのボードを与えてください!」は、FPGAを備えたラボへの学生の最も頻繁な応答です。

原則として、Intel / Alteraのボードは教師に配布されますが、ザイリンクスはそれほど頻繁ではありませんが、少量です。 大学はザイリンクスとアルテラから独自の資金でボードを購入していますが、これは多くの場合、官僚主義と赤字によるものです。 Yevgeny Korotkyの人物であるKiev Polytechnic Instituteは、FPGAの学生を教えるために、キエフ市から助成金を受けてFPGAボードを最近購入しました。 Zelenogradの企業であるElvis-NeoTek、モスクワの会社NauTech、サンクトペテルブルクマクログループ、カリフォルニアMIPSは、教育のニーズに応じてFPGAボードを大学に割り当てました(モスクワ州立大学、MIET、ITMO、MPEI、KPIなど)。 しかし、中央および地方の大学のすべてのプログラムを更新し、RTLをハイテクの一般教育の一部にするには(アメリカの大学で行われているように、中国で中国が行う速度も)、2桁の追加料金が必要です。 一方ではこれは問題ですが、他方では、地域の企業や個人が地元の大学や物理学学校に関連して慈善活動に従事する機会です。 これらの技術の大規模な所有権は、ロシアや同地域の他の国々に広範な影響を与える可能性があります-およそ1985年にソビエトの学校にコンピューターサイエンスが導入された結果、21世紀にYandexなどのロシアのソフトウェア企業が誕生しました。

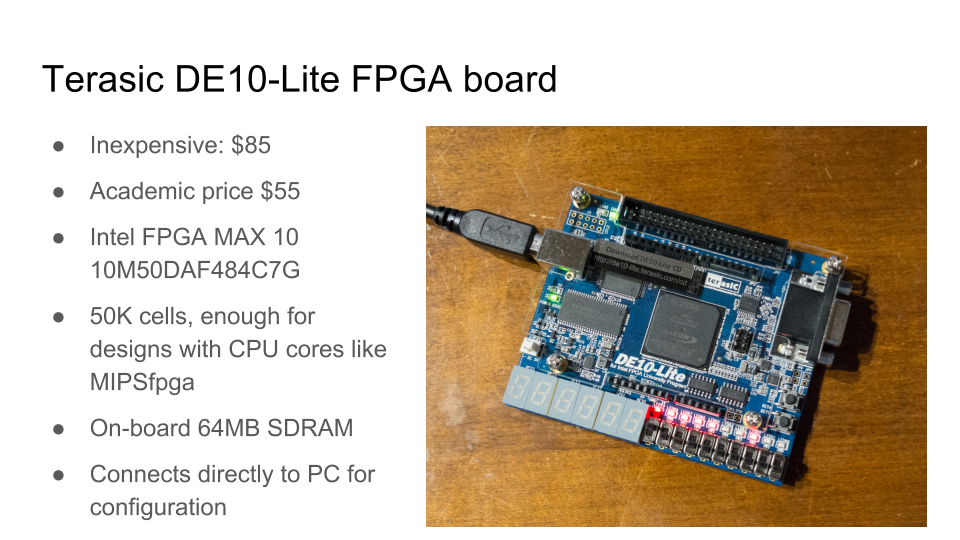

ほとんどすべてのボード(ザイリンクス、アルテラ、ラティスなど)は、レジスタ転送レベルでのデジタルロジック開発の基本的な演習に適していますが、Innopolisでは、現在Terasic DE10-Liteボードを使用しています。 安価であり、小規模な産業用プロセッサコアの合成にも適しています(これを試してみたい場合は、これが次のレベルです)。

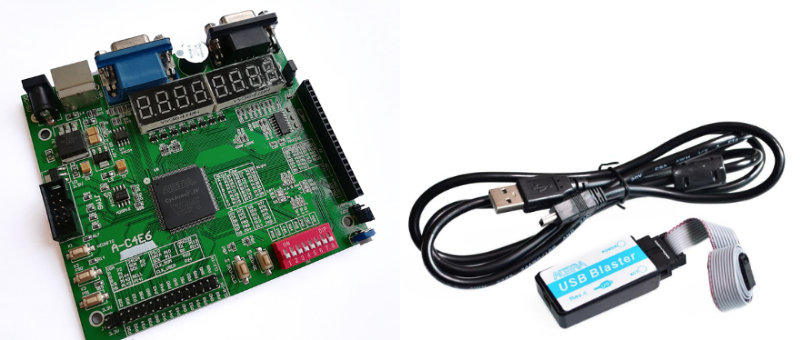

しかし、お金の不足に直面して数百ものボードを購入する場合、解決策の1つは最新のFPGAではなくアリエクスプレスを備えたボードを取ることです。 確かに、それらのいくつかについては、合成にソフトウェアの最新バージョンではなく使用する必要がありますが、概してそれは重要ではありません。 また、それらは最も便利なスイッチではなく、少数ですが、約20ドル(数千ルーブル)かかります。 Intel / Altera FPGAボードにはUSB Blasterアダプターが必要です。別途購入することをお勧めします-AliExpressの一部のUSB Blasterは最新のIntel Quartusソフトウェアバージョン17.1で動作しますが、他のバージョンは2013バージョン13.0sp1とのみ互換性があります。

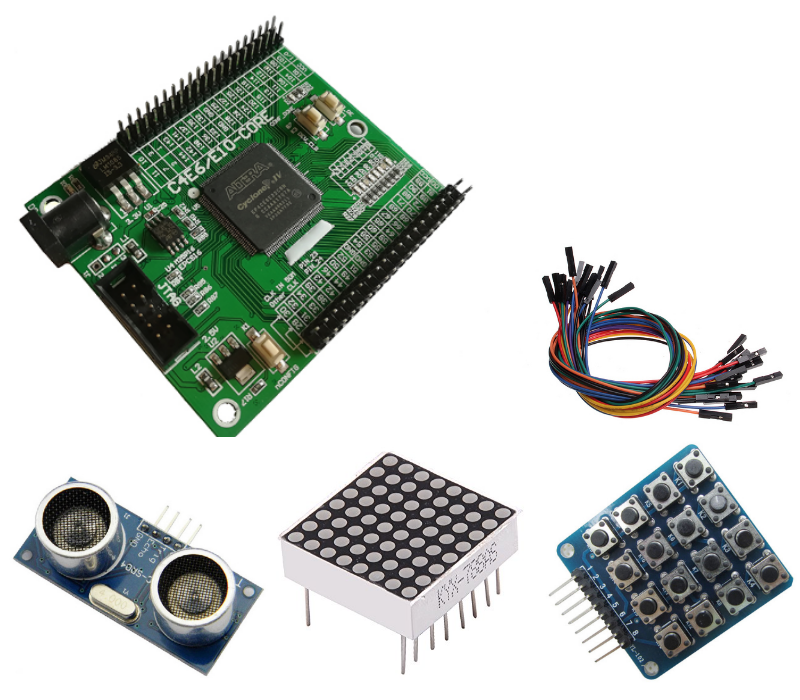

さらに安いのは、周辺機器なしでFPGAボードを購入することです。 これは、特にFPGAボードに接続して魅力的なプロジェクトを作成できるあらゆる種類のセンサー、レンジファインダー、LEDアレイ、スピーカー、その他のデバイスにがれきがある場合、学童にとっては興味深いかもしれません。 学童にとって、最初に同じプロジェクトを小さな集積度のマイクロ回路で、次にFPGAで、次にマイクロコントローラーで行うことは興味深いかもしれません。

最後に、Terasic、Digilent、およびその他のアジア、アメリカ、ヨーロッパのマザーボードメーカーに加えて、ロシアのメーカーもあります。火星探査機とVoronezhのFPGA工場です。 火星探査機のサイトには、教育プロジェクトに関する適切な指示があります。 彼らはこの地域のロシア人コミュニティの中心の一つに発展することができます。 ヴォロネジのFPGAは高価ですが、ヴォロネジの工場がそれらを大学に配布する場合は、これらのすべての演習を行うこともできます。