シーズン2:ボードには、2〜3週間以上動作しない4つのXC7K160Tクリスタルが含まれています。 拒否の理由は何ですか? 整理

1.ソフトウェア。

トリガー間のLUT要素の数のチェックが行われました。 彼女はそれを示した

量は12に達しますが、これは大きな時間遅延を引き起こさず、簡単です

4 nsに収まり、ほとんどの場合3 nsに収まります。 組み合わせ操作の結果を取得するプロセス(複数桁の数字を追加および比較する)では、パルスの伝播時間の大幅な広がりにより、消費電流が増加し、局所加熱の危険性があり、その結果、最大1 GHzの制限スイッチング周波数が出現します。 下の図1では、各サイクルで1回のスイッチングではなく、複数のスイッチングが発生していることがわかります。

図1

そのため、コンベアを使用しようとしました 計算および評価用

GATEレベルでシミュレーションを使用します。 スイッチが多すぎず、

パイプライン化は消費電流の増加につながるだけであったため、使用されなくなりました。 コードの評価により、可能な限り最適に記述されていることが示されました。 特定のアルゴリズムおよびアルゴリズム(たとえば、固定定数で除算するときに適用される乗算による近似)の変更は、使用されるリソースを増やすだけです。 したがって、さらに、主にチップの故障の理由の検索に関係しています。

2.温度を確認します。

水晶が故障する理由の1つは、過熱です。 結晶の臨界温度は80度を超える温度と見なすことができます。 専門家(Novomar)によると、シリコンは「劣化」します。 通常、これは結晶の結晶欠陥のテスト方法です;短時間で、通常の条件下で結晶がどのくらいの時間動作するかを推定することができます。 温度測定により、最悪の条件および長期間の動作では、温度が70度を超えて上昇しないことが示されました。 (図2を参照)300 MHzのクロック周波数でも、水晶の寿命はほとんど短縮できないことがわかります。 この図は、計算が長続きしない場合のグラフを示しています。 連続モードでは、温度が70度を超えて上昇しないことが確認されました。

図2

3.コア消費電流とビア。

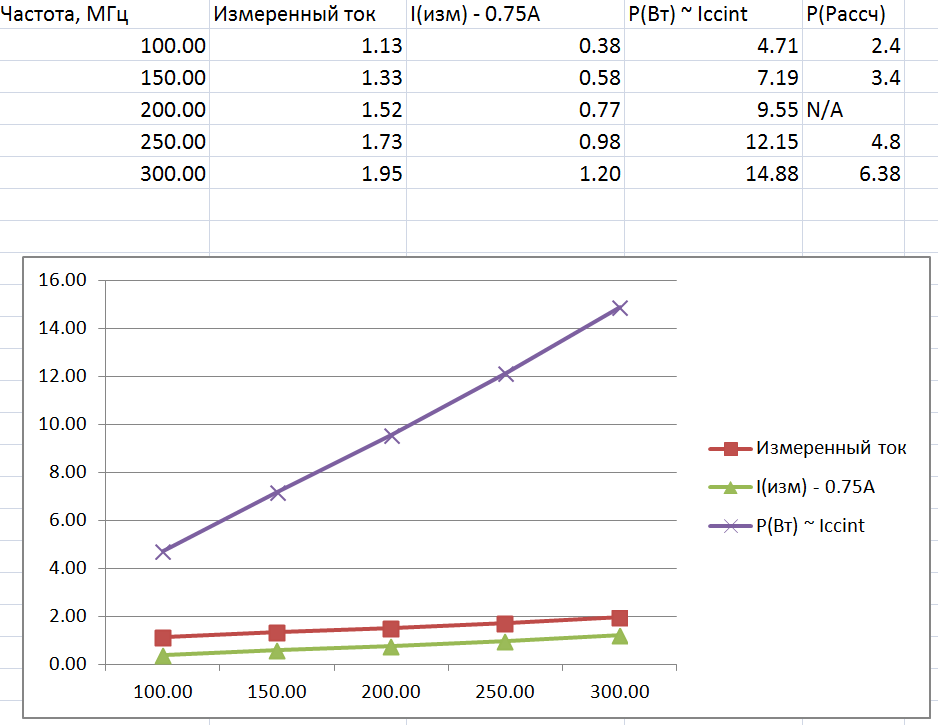

FPGAのコア消費電流(VCCINTおよびVCCBRAM)が測定されました。 電源電圧は1.0Vです。

図3は、処理ユニットのクロック周波数からのコアの消費電流のグラフを示しています

データ。 実際の計算された。 計算の不在モードと

計算モードは平均化されます。 電流は最大15 Aの値に達する可能性がありますが、

FPGA 21個の電源接点。 かくして 各ピンの電流は約0.7 Aです。プレスには2つの場所(M14、N13およびL13、K12)があり、アダプター穴ごとに2つのピンがあります。 T.O. 現在の

スルーホールの計算値は1.5 Aであり、開発者が推奨する値は1 Aです。これらのホールは現在の損傷についてテストされています。

4 A(数時間)の電流での長時間のテストは、ビアにいかなる影響も与えませんでした。 その抵抗は数ミリオームに達しました。 さらに、FPGAが取り外されたボードでは、すべての開口部で検出されなかったブレークがチェックされました。 結論は、この理由により、取締役会は再配線を必要としないということです。 結晶の故障の理由はこれではありません。 図3は、コアの消費電力のグラフを示していますが、

電源コア1 Vの場合、電流は数値的に電力に等しくなります。

図3

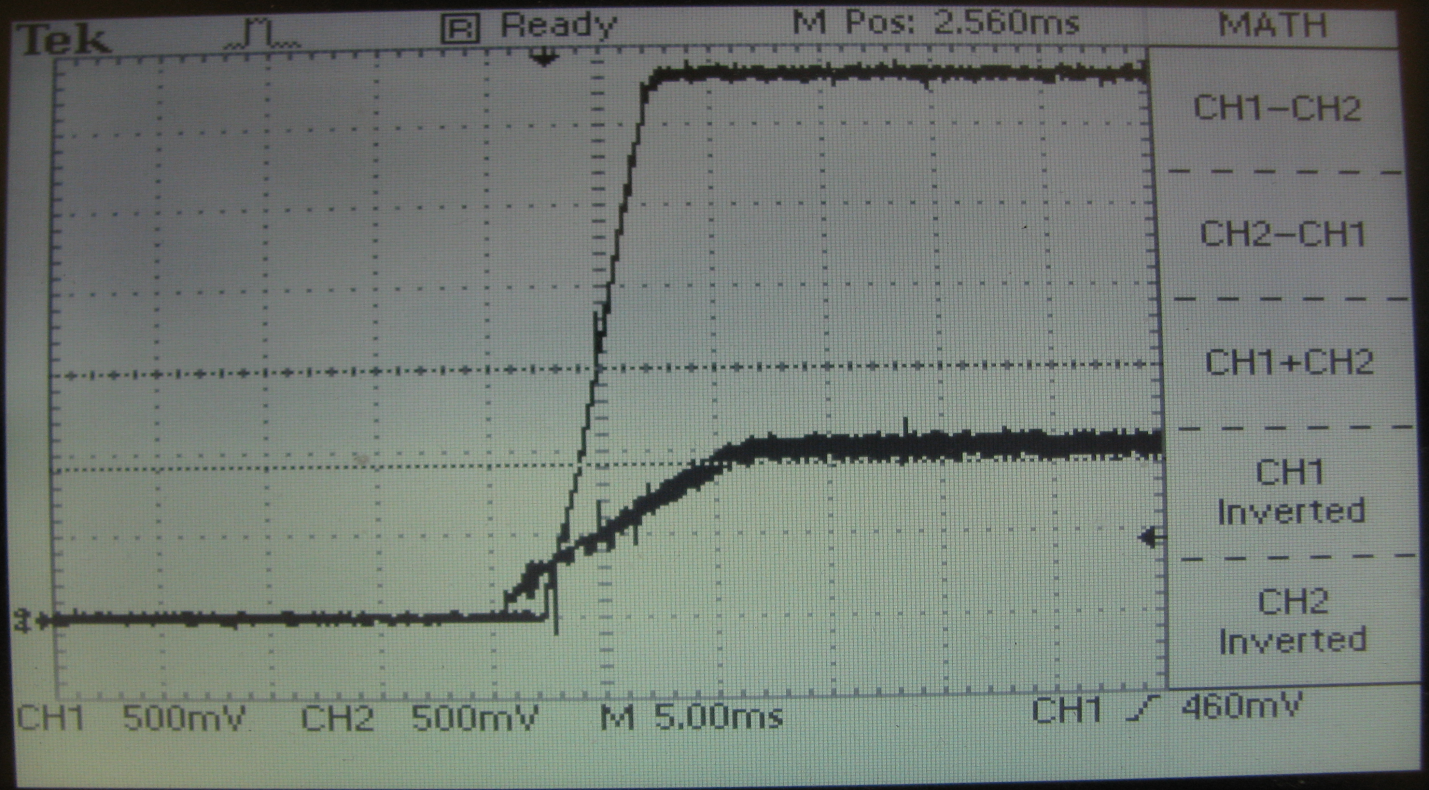

4.チップへの電源供給のシーケンス。

チップへの電源供給の順序は次のとおりです。VCCINT-> VCCBRAM-> VCCAUX&

VCCO; VCCINTとVCCBRAMは同時に供給できます。 このプロジェクトでは、シーケンスが壊れています。 これは、図4のオシログラムで確認できます。5ミリ秒以内

VCCO 3.3 V電圧は1.5 Vを超えており、VCCINTはまだ定格値に達していません。 それは

メーカーが推奨していません。

図4

ただし、このような状況では、電源投入時に障害が発生する可能性があります。 しかし、本当に

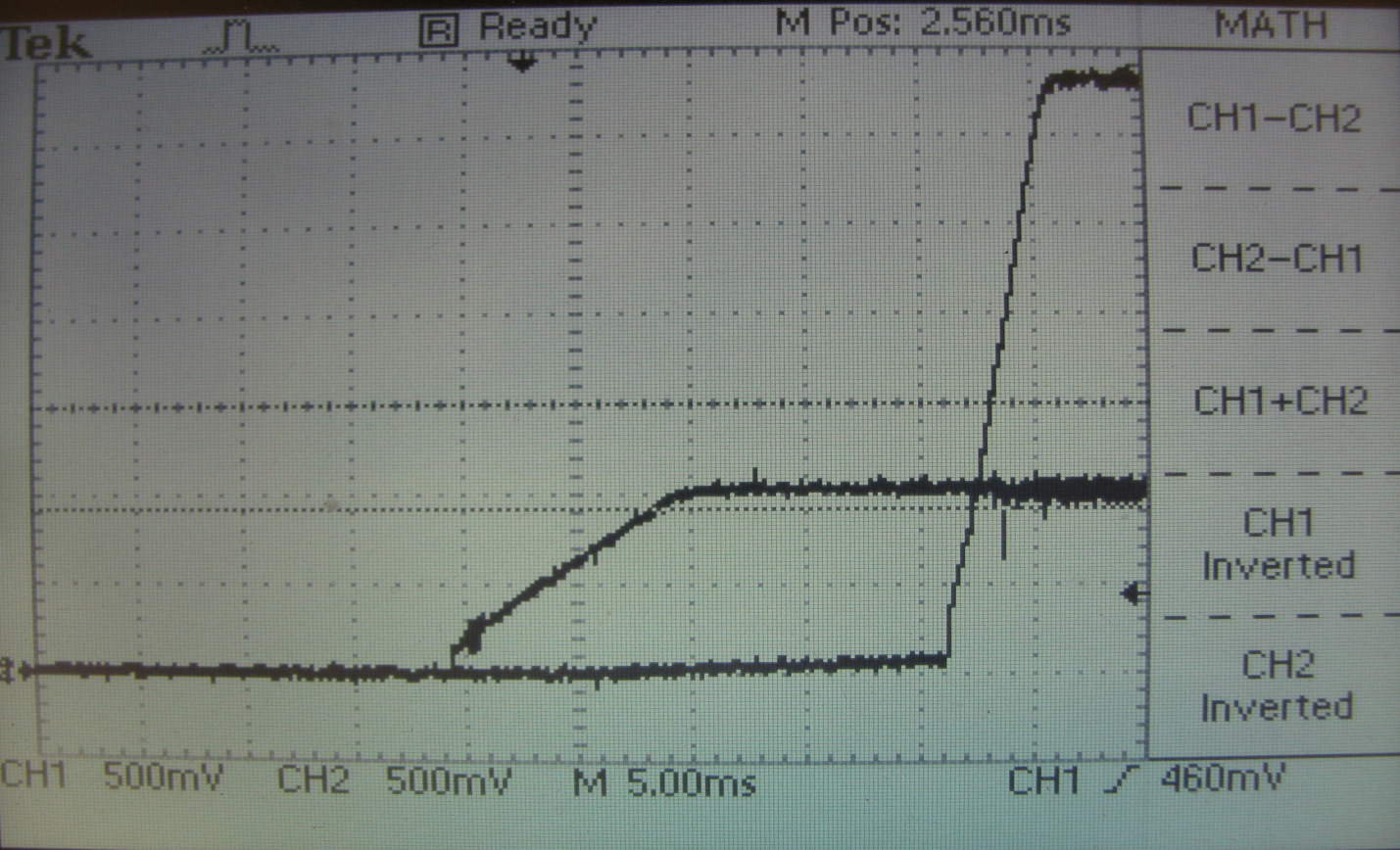

長期使用中に水晶が故障します。 ただし推奨

ピンINHIBITスタビライザー3.3 Vおよび1.8 Vは、GNDに1.0 uFのコンデンサを取り付けます。 それは

起動を数ミリ秒遅らせ、要件へのコンプライアンスを確保します

電源投入シーケンス。 図を参照してください。 5。

図5

5.基本スキーム

回路を調べると、M12 VCCADCピンに3.3 Vが供給されていることがわかりました。

このピンの2.0 Vである水晶の最大許容値は公称1.8 Vです。ボードを再構成してこのピンを1.8 Vに接続するか、電源を3.3 Vから1.8 Vに下げる必要があります。しかし、信号CFGBVS_0を切り替えてGNDに接続する必要があります。 また、他のモードを変更することもできるため、言い直したほうが良いようです。

6.欠陥のある結晶の状態の研究。

障害のあるデバイスがリセットの問題を検出しました。 すなわち オンにすると、すべてのLEDがオンになり、デバイスは動作モードになりません。 外部リセットを削除してクリスタル内で生成することで、問題を回避することができました。 ただし、不良サンプルでは、4つのチップのうち3つに問題があります。 それらのうち2つでは、内部RST信号はピンの状態の変化(J26)にまったく反応せず、1つでは、グラウンドに短絡した場合にのみ反応し、状態1になりますが、1である必要があります。 これは、これはピンに静電気が印加された結果(ピンは使用されていないと言われましたが)、または問題はADCVCC(M12)ピンの誤った電源、または誤ったパワーアップ順序に関連していることを示唆しています。

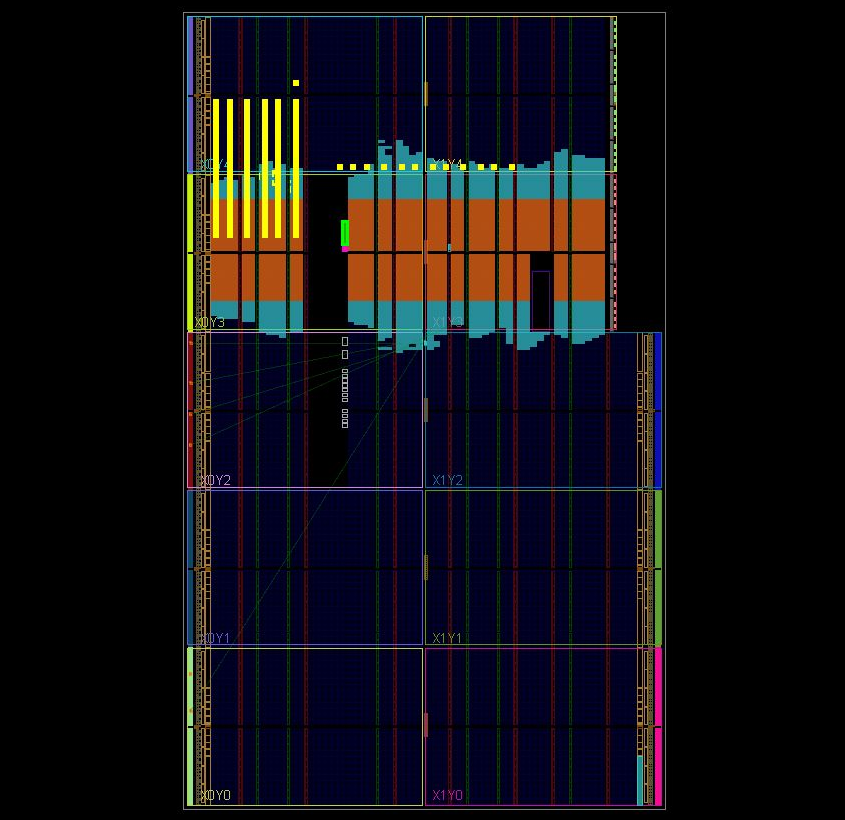

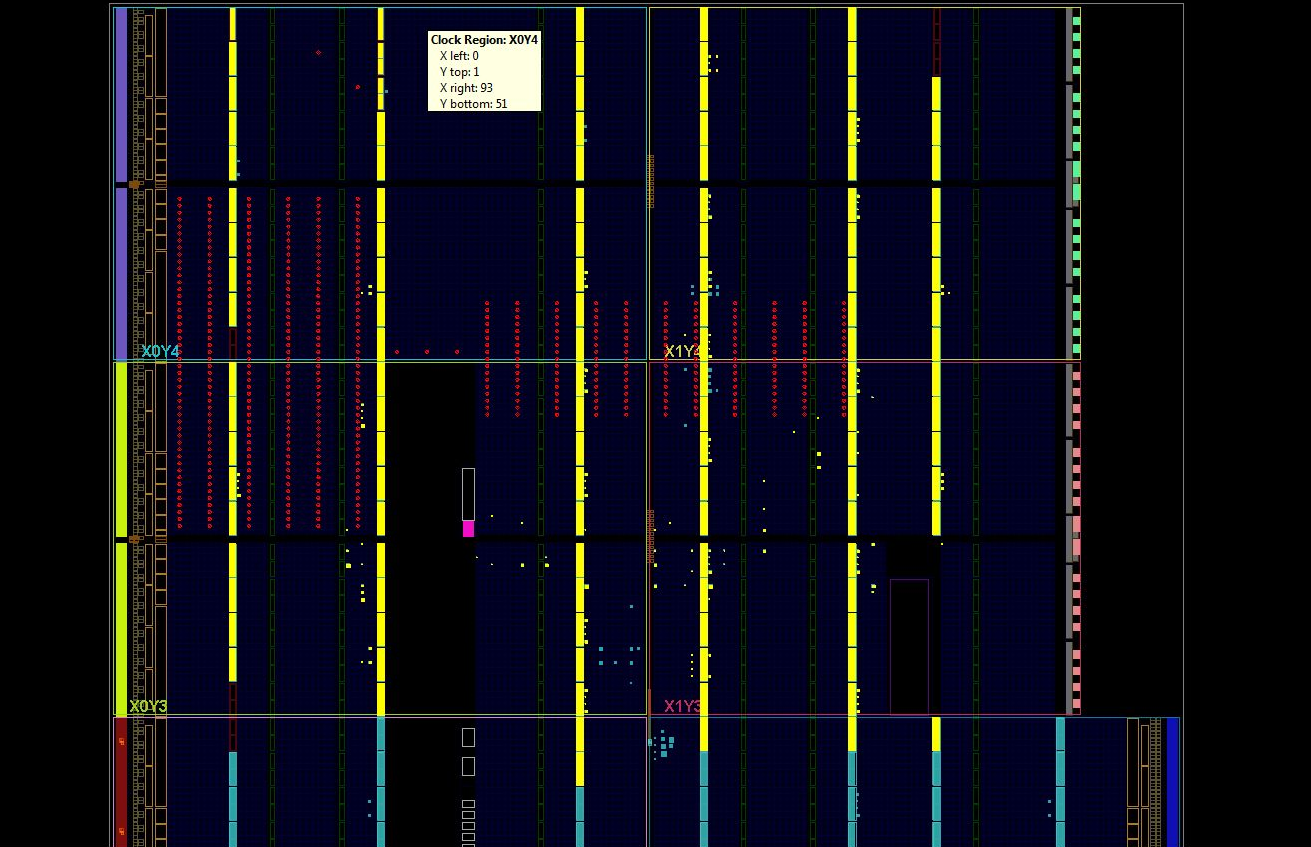

6.1スライス

今から楽しい部分です。 スライスを順番に埋めるためのプログラムが作成されました

(ユニットセル)トリガー、およびそれらのメモリの整理。 クリスタルスキャン

欠陥のある要素の存在を示しました。 図 図6は、これらの要素を黄色で示しています。 (除く

左端に淡黄色のストライプ)。 図7の詳細。

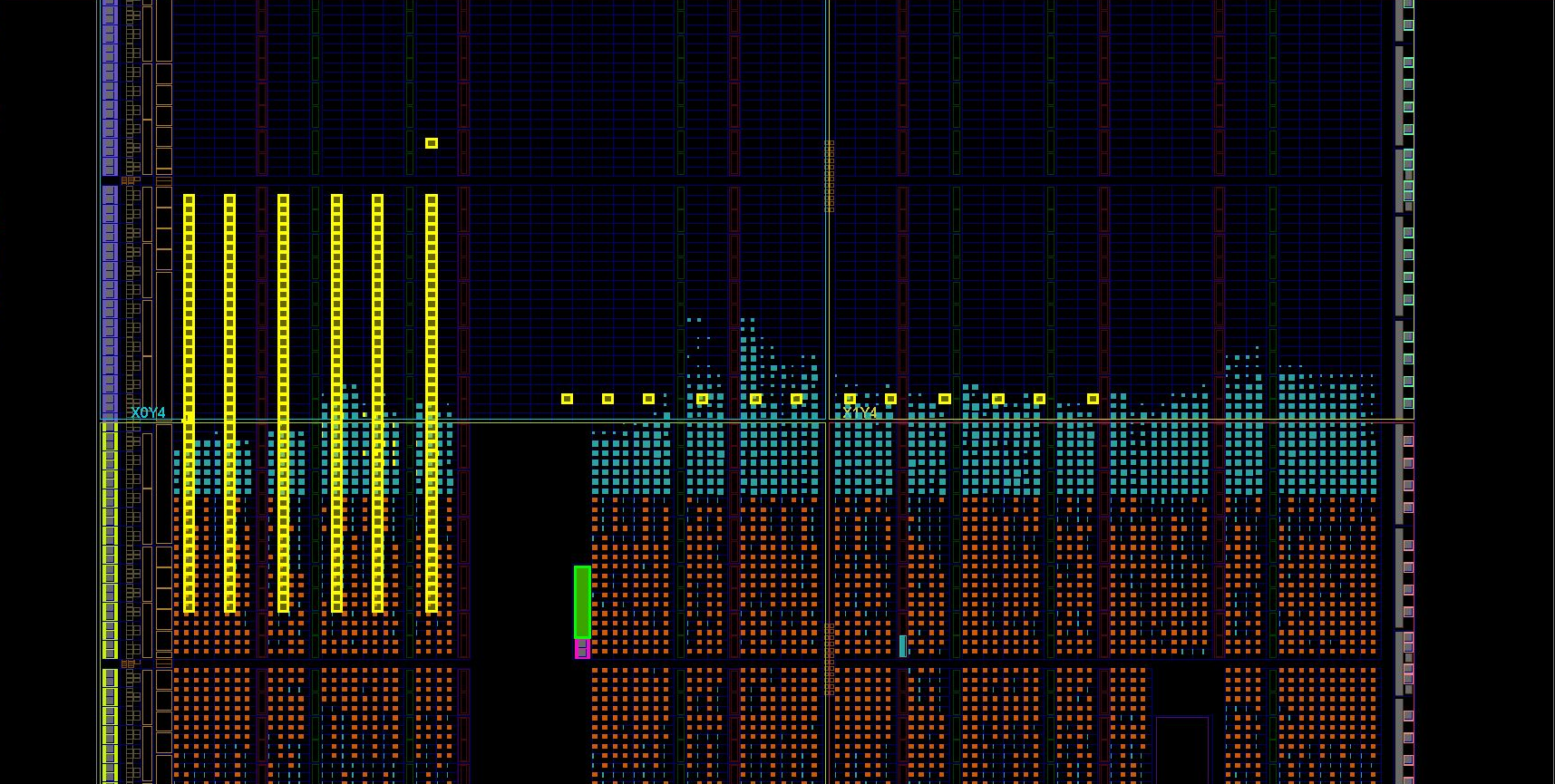

図6

図7

テスト結果はログファイルで確認できます。 障害のある要素の計算は次のようになります。たとえば、ファイル:test_X0-108Y160-191_Dev1(com5).txt

Aでのエラー:000D

WR:55555555

RD:43555555

アドレス0xD、13:スライス位置:X = 13、Y = 160 +(無効なビットの位置)= 160 + 25 = 185および残り:186、188。したがって、X = 13、Y = 185、186、188

したがって、障害のあるスライスの位置が取得されました。 TEST_SLICESアーカイブ(27'07'2016)のソースを使用したテスト自体。 Versionsフォルダーには、実行するビットファイルがあります。 これらはクォーツ125 MHz用に設計されており、ポート速度は115200です。緑色の長方形も図に表示されています。これは、1.8 Vではなく3.3 Vの間違った電源を持つXADCブロックです。 現実に近いXILINXが要素の位置を示している場合、この理由による水晶の損傷の仮定が正しい可能性があることは明らかです。 システムから壊れたスライスを除外し、ブリーダーが次のコマンドでそれらを使用できないようにすることができます。

set_property PROHIBIT 1 [get_sites SLICE_X17Y243]-個々のスライスを禁止します。

set_property PROHIBIT 1 [get_sites -range SLICE_X1Y176:SLICE_X25Y223]

-一連のスライスを禁止します。

このようなコマンドの完全なセットは、 BRAM_TESTアーカイブプロジェクトの main1.xdcファイルにあります。

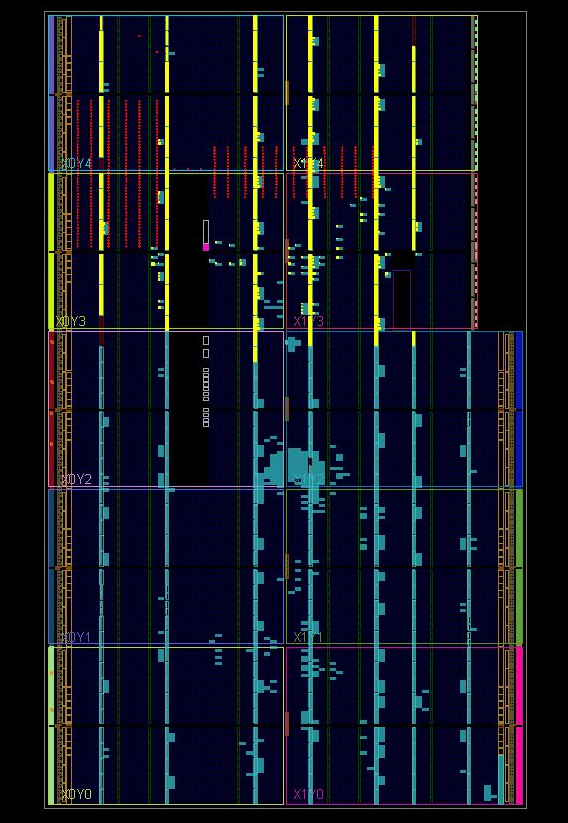

6.2ブラム

打たれたスライスのデータを使用して、98%ブロックを使用してテストが構築されました

メモリ。 図のテスト結果 8。

図8

詳細については、図9を参照してください。 赤い点は、使用されていない壊れたスライスを示します

テストが機能するため。

図9

BRAMメモリのほぼ半分が破損していることがわかります。 また、破損したエリアは

誤った電力が供給されているADCモジュールに近づけてください。 たぶんそれは

事故ではありません。 スライステストではすべての誤動作が表示されるわけではなく、

スライスごとに1つのトリガーと複数のLUT、制限のあるクリスタルの使用を検討

プロジェクトのコアの数は効果的ではありません。 彼の作品は予測不可能であり、そうではないかもしれない

信頼できる結果を表示します。 さらに、BRAMの損傷が大きすぎます。 そしてまた

他のチップには他の損傷があり、すでに見つかっているものと一致しない可能性があることに注意してください。

結論:

1.ボードは、ADC_VCC(M12)の電力補正とインストールで再配線する必要があります

端子INHIBITスタビライザー+ 3.3Vおよび+ 1.8Vへの追加コンデンサ。 また、

RST信号は、長いワイヤを使用してボードから出力されます(

LED)、静電気から保護することをお勧めします。

2.非常に必要な場合は、たとえば80〜90でプロジェクトを組み立てることができます。

コア、外部RSTピンを使用せず、内部生成リセットを使用して、BRAMおよびSLICESの使用を制限します。

PS:推奨事項1の実装後、問題はなくなりました。

M.E. Generalov、2018