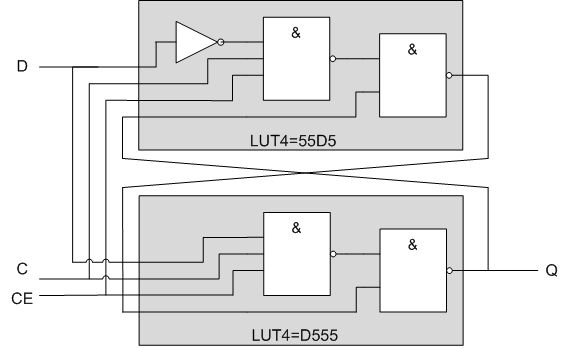

XC5VSX95Tチップを搭載したマザーボードが機能しなかったことがありました。 これは結晶の新しいバッチであることが知られていました。 問題をテストするために、すべてのFPGAスライスを連続してテストするテストが作成されました。 結晶のテストでは、1つのスライスに4つの要素が含まれるLUTモジュールの欠陥が示されました。 これらのスライス内のトリガーは順番通りであり、メモリーブロックがトリガー上に作成され、それがLUT上に作成されたことが判明しました。 図を参照してください。 1. LUT4のトリガーの例を次に示します。 テストの各セル(ビット)は、1つのスライスを担当します。 トリガーセルは、4つのLUTスライスすべてを使用します。 クリスタルは5つのエリアに分割され(別のテストでは9つのエリア)、それぞれが独自のファームウェアでテストされました。 使用されるスライスの適切な配置は、LOC属性によって管理されていました。 失敗の特徴は、テスト中のトリガーの状態を変更できないことです。 このようなトリガーの出力は、0または1を読み取ることができますが、常に同じです。 したがって、最初はメモリが1で満たされ、チェックされ、次に0でチェックされました。 スライスの全範囲はX0Y0-X91Y159です。 (14720スライス)

図1

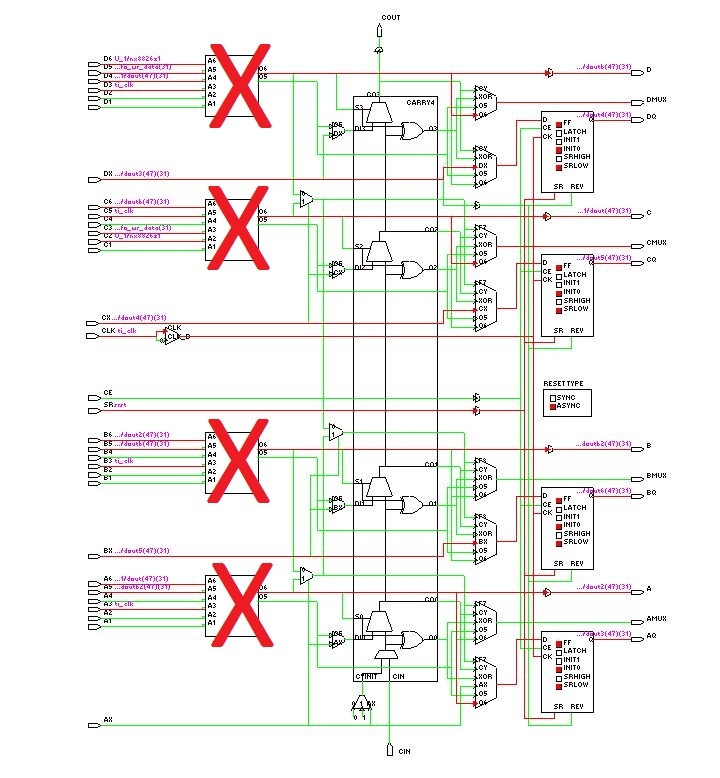

図2は、Virtex5 FPGAスライスの構造を示し、障害のあるコンポーネントを示しています。 LUT5が不良であることが判明しました。 完全なプロジェクトコードは、よく知られた理由で投稿されていません。 ただし、 アーカイブには、トリガーおよびLUTにメモリセルを実装するためのVHDLコードがあります。

図2

3つのボードのテスト結果:

ボード#2 18悪いスライス:

SLICE_X26Y120-SLICE_X26 Y128

SLICE_X27Y120-SLICE_X27 Y128

ボード#3 19悪いスライス:

SLICE_X26Y120-SLICE_X26 Y128

SLICE_X27Y120-SLICE_X27 Y128

SLICE_X26Y129

ボード#4 19悪いスライス:

SLICE_X26Y120-SLICE_X26 Y128

SLICE_X27Y120-SLICE_X27 Y128

SLICE_X26Y131

結論:

ボードを使用する場合、開発チームから不良スライスを除外する必要があります

CONFIG PROHIBIT = SLICE_X26Y120:SLICE_X27Y128;

CONFIG PROHIBIT = SLICE_X26Y129;

CONFIG PROHIBIT = SLICE_X26Y131;

または、マージンを使用してすべての可能なものをすぐに除外することをお勧めします:

CONFIG PROHIBIT = SLICE_X26Y120:SLICE_X27Y131;

リソースが不足しているため、これらのスライスの残りの正常な要素を使用できるように、欠陥のあるLUTの使用のシミュレーションを編成することができます。