これらすべてがロシアにどのように役立つのでしょうか? このようなプロジェクトについては、9月18〜22日にTomskで開催される会議で FPGAボードを配布します。 モスクワ州立大学、MIPT、MIET、ICST、イマジネーションテクノロジーズ、ナショナルインスツルメンツなどの代表が参加します。 彼らは大学のカリキュラムをどのように更新し、今日の学生が数年後に西洋の主要企業のレベルでロシアのチップを設計するように議論するでしょう。 また、 スタニスラフ・ゼルニーノ・ スパルフの最もシンプルなschoolMIPSから始めて、教育プロセッサを作成する方法を議論するセミナースクールもあります。

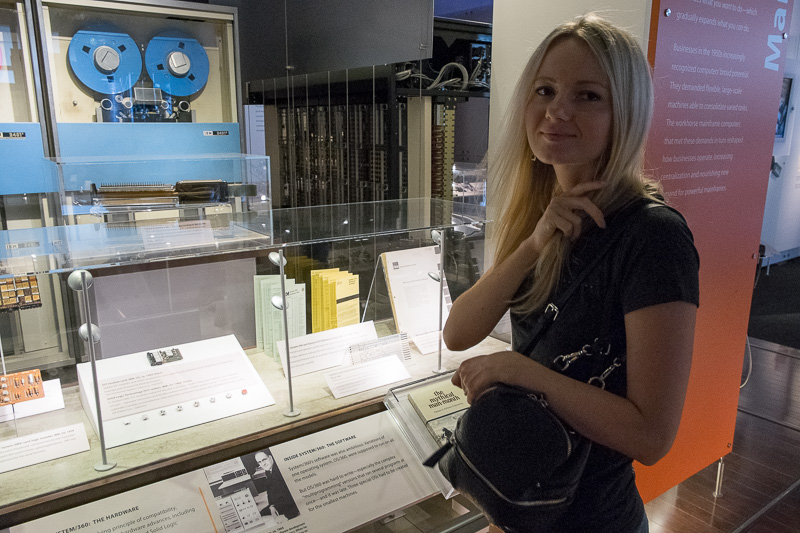

これが、マウンテンビューの博物館からの最初の写真です。イリーナとロケットに加えて、小さな箱が中央に見えます。 これは、ソビエトELAS協会のエンジニアによって設計されたMIR宇宙ステーションのオンボードコンピューターで 、現代のELVIS会社Zelenogradに変換されました。

したがって、教育プロジェクトのトピック-20世紀半ばの密な数十年から開始:

私たちの前には、ペンシルベニア大学のプレスパー・エッカートとジョン・モークリーによって1943年から1947年に開発された、温かいENIACチューブコンピューターの算術関数の計算結果のテーブルを保存するためのブロックがあります。 ある時点で、同僚のジョン・フォン・ノイマンは、このブロックを使用してプログラムを保存することを提案しました。 こうして、「フォン・ニーメンの建築」が生まれました。 一般に、それを「エッカート・モークリー・フォン・ノイマンの建築」と呼ぶのは正しいでしょうが、エッカートとモークリーは不運でした-彼らの名前は秘密にされ、フォン・ノイマンの名前はそうではありませんでした(コンピューターは砲兵テーブルを計算するためのものでした)

このコンピューターをFPGAに実装する場合、ENIAC_Operating_Manualをグーグルで検索しましたが、それをベリルのコードに変えるのは簡単ではありません:

トランジスタスーパーコンピューターIBM 7030 Stretch。 名前(ストレッチ-「ストレッチ」)は、以前のIBM 704の100倍の速さでコンピューターを作成するという作成者の約束に由来します。 しかし、この「失敗」の過程で、Aybemのエンジニアはパイプライン、マルチタスク、メモリ保護を思いつきました。

CDC 6600(1963)。 史上初の「本物の」スーパーコンピューターと、並外れた命令実行を備えた最初のプロセッサー。 マイクロアーキテクチャの講義でスコアボードの例としてまだ広く使用されています(たとえば、 バークレーの最初のグーグル(非常に新鮮ではありませんが) CDC 6600スライドを参照)。 簡略化されたCDC 6600のベリルおよびFPGAへの実装は、学生のコースワークプロジェクトの最も明白な候補の1つです。

これは、マイクロプロセッサアーキテクチャからのCDC 6600の一般的な組織に関する抜粋です。シンプルパイプラインからチップマルチプロセッサまで、Jean-Loup Baer(2009)。 並列で動作するいくつかの機能デバイス(パイプラインなし)と、命令間のデータ依存関係を追跡し、オペランドの準備ができるまで命令の実行を一時停止するスコアボード:

IBM 360(1964-1978)。 このコンピューターのラインは、ソ連のスーパーコンピューティング当局によるITMiVT(BESMおよびElbrus)の抵抗にもかかわらず、ソ連のCPSUの中央委員会に深い印象を与え、EUコンピューターの名前ですべての社会的国にIBM 360/370のソビエト実装を植え付けました。 これらのコンピューターは、「母の仕事にいる」ブレジネフ時代のソビエトの子供たちの絵にも描かれています。

原理的には、IBM / 360ラインが「統一アーキテクチャ(コマンドシステム)-さまざまなマイクロアーキテクチャの実装(コンベヤーデバイスとハードウェアブロックの構造)」という革新的なコンセプトを導入した理由がありました。 言い換えれば、同じソフトウェアがこのラインの低速、安価、高速の両方のコンピューターで再コンパイルせずに動作する可能性があります。 (確かに、これらのマシンのソフトウェアは、近々登場するミニコンピューターのソフトウェアと比較してあまり友好的ではありませんでしたが、IBMハードウェアエンジニアはこれを責めるべきではなく、IBMプログラマーとその管理者の責任でした)。

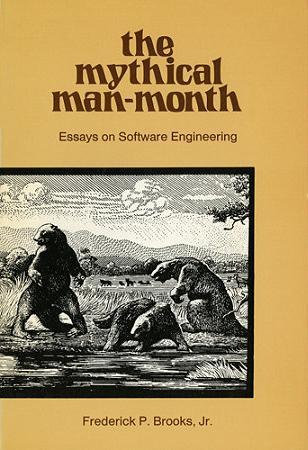

ただし、IBM / 360プロジェクトはプログラミングの世界にも利益をもたらしています。 イリーナのハンドバッグの左側に、フレデリックブルックスの「神話の男月」という本がありますか? この本の著者はOS / 360プロジェクトマネージャーであり、プロジェクトに新しいプログラマーを追加することで期限が切れているのを修正しようとすると、状況が悪化することがよくあります。期限はさらに苛立ちます。 この本は1975年に出版され、すぐにソビエト連邦に転送され、いくつかの場所ではまだ関連しています。

IBM / 360ラインは、1980年代の「RISC革命」の間に無関係になった「マイクロプログラミング」と「マイクロコード」の概念もメインストリームに導入しました(現代のマイクロプロセッサーは、すべてを伝える必要があるため、ほとんどが配線されています)。 しかし、これらの概念はコンピューターアーキテクチャに関するソビエトおよびソビエト後の教科書に深く根付いており、人々は「Verilogはマイクロプログラミングですか?」という質問をします。その後、マイクロプログラミングではないことを説明するには時間がかかります。

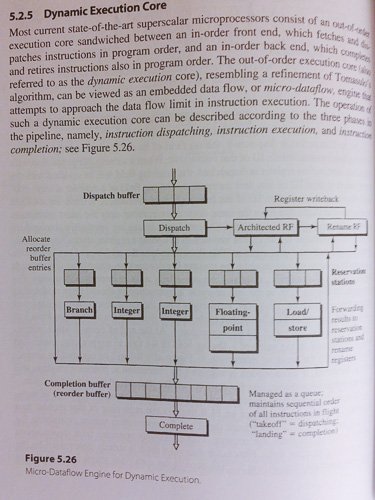

では、なぜFPGAにIBM / 360を実装するのでしょうか? すべてを実装することは無意味ですが、1つのモデルの1つの側面、つまりIBM System / 360 Model 91は、CDC 6600のスコアボード以上のマイクロアーキテクチャの現代の学生コースワークプロジェクトに現れます。私は、いわゆる「Tomasuloアルゴリズム」、異常な実行を整理する方法について話しますハードウェア「レジスタ名の変更」と「予約ブロック」を使用した算術演算(はい、これらはiPhoneのプロセッサにもあります。これらは巨大な遺物ではありません)。 ロシア語版ウィキペディアにトマスロのアルゴリズムに関する記事がないことはかなり奇妙ですが、ウクライナ語にはあります。

Tomasuloアルゴリズムは、ハードウェア保護、動的なチーム計画、効果的なパブリックファンクションブロックを介した海外訪問の送信のための、コンピューターアーキテクチャのウィザードのようなものです。 1967年のRobert Tomasuloによる断片化のアルゴリズム(IBMで勝つことができる場合)、およびIBM System / 360 Model 91でのコマ操作によるブロック操作のさらなる実装。

Tomasuloのアルゴリズムによって導入された主な革新は、計算に従って、デバイスのレジスタを変更し、すべての機能ブロックのブロックを予約し、データバス(SDL)をメモリブロックに同時に転送できることです。

プロセッサ開発に関する最も有用な現代の本の1つである、John Paul ShenとMikko H. LipastiによるModern Processor Design:Fundamentals of Superscalar Processors(2013)は、以前のIBM / 360-91浮動小数点ブロックの様子を示していますトマスロと彼の後。 パフォーマンス(異なる操作シーケンスのクロックサイクル数)と最大クロック周波数(FPGAに実装した場合)を比較することにより、学生プロジェクトでも同じ「前後」を実行できます。

その後、Shen-Lipastiの本は、ダイナミックパイプラインを備えた最新のプロセッサでこれがどのように行われるかを説明しています。

そして、ここに1958年に作られた日本の初期のトランジスターのメインフレームであるNEAC 2203があります。 日本以外では販売されていません。 一般的に、その後、世界の日本製品に対する軽薄な態度があったが、日本企業は西洋の偶像崇拝を抑制し、日本の資本主義に従事した。 最初に、彼らは国内市場(一種の「輸入代替品」)で技術的ソリューションをテストし、その後、世界市場を積極的に攻撃しました。 数十年後、日本はアメリカの企業をメモリチップと家電の市場から追い出し、同じNECが1992年に最も強力なスーパーコンピューターであるNEC SX-3 / 44を構築しました。 同時に、米国への政治的依存を減らす必要性についての声が日本に現れ始め、運輸大臣は「NO」と言える«(「日本は「NO」と言うことができる!」)という本を書きました。 残念ながら、この膝からの上昇はその後の経済危機を打ち倒しましたが、1950〜1980年代の日本の経験は研究にとって興味深いものです。

これで、博物館を歩く最初の部分は終わりです。 始めが気に入ったら、クレイとイリアックのスーパーコンピューター、HPミニコンピューター、DECとData General、最初のマイクロプロセッサーとマイクロコンピューター、RISCワークステーションとLispマシン、ゲームコンソール、ロボットについて詳しく説明します。

これがすべての目的を思い出します:

公教育を強化するためにこのタイプのオープンソースプロジェクトに興味がある場合は、SystemVerilogまたはVHDLでそれらを記述し、GitHubでコードをアップロードし、Habréでそれらに関する記事を(パフォーマンス分析を使用して)書く準備ができていますが、FPGAボードはありません次の3つの場所のいずれかで彼女(およびプロジェクトが成功した場合は永続的に取得):

1.モスクワのHSE MIEMのAlexander Romanov。 アレクサンダーは学生向けにVerilogコースを導入し、通常のボードに加えて、大学には、AlteraとXilinx FPGAのボードの幅広いコレクションがあります。どちらもTerasicとDigilentの一般的に使用されるボードと、文書化が不十分な中国語のボードです(特にオープンソースプロジェクト用)。

2.キエフ・モヒラ・アカデミーのヤロスラフ・ウォズニウク。 私は小学生向けのハッカソンに来て、「Habréの記事を伴うプロジェクト料金」のために、Xilinx Artix-7を搭載したDigilent Cmod A7 35Tボードをいくつか残しました。

3.ノボシビルスク工科大学のウラジミール・マクカ。 Tomskでの 1週間の会議用のボードセットがあります。 それらのいくつか(Digilent Nexys DDR4)はウラジミールに残り、いくつか(Terasic DE0-CV)はそのようなプロジェクトに行きます。

インスピレーションとして、 SparF 、 Frantony 、 oleh_plotnikov 、 Kingit 、 VMSS 、 kirill90 、 Boris_92のHabr上のFPGAベースのプロセッサを使用した既存のプロジェクトを見ることができます(コメントに追加できます)。

最新のプロセッサ設計の基礎に関する補足

古代のプロセッサは、ラジオチューブ、トランジスタ、わずかな集積度の超小型回路、および画面上でのマウスによる回路の描画で構成されていました。 今、これはすべてそうではありません。 Verilog、ASIC、およびFPGAが何であるかをよく知らない読者への言葉:

Geektimes »Microelectronics squiresの投稿から。 San Francisco Electronics Design Conferenceのビデオ :

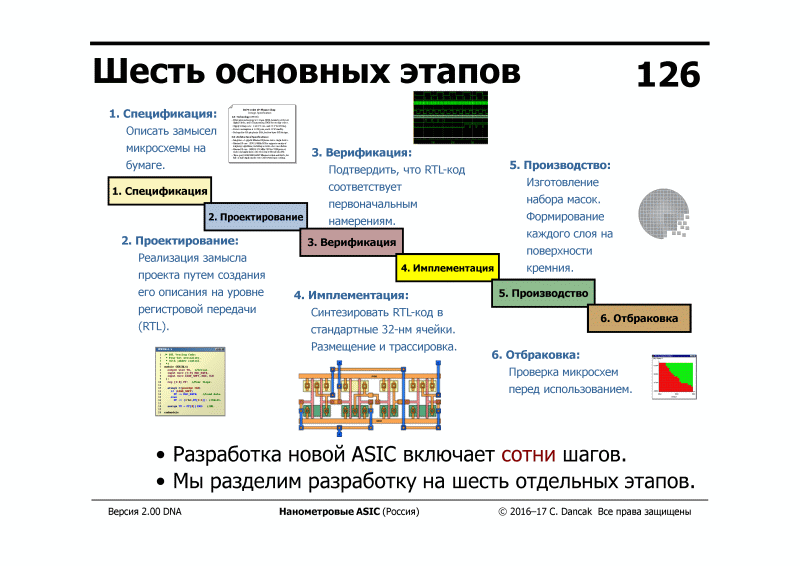

これまで、マイクロ電子プロジェクトの集大成である工場でのマイクロ回路の製造について説明してきました。 しかし、そのようなプロジェクトはどのように始まりますか?

過去25年間、マイクロ回路の設計は、ほとんどの場合、機器記述Verilog([以前]ヨーロッパおよび軍隊-VHDL)の言語で記述され、その後、特別なプログラム(論理合成)が設計をワイヤと論理プリミティブのグラフ、別のプログラム(静的タイミング解析)は、設計者に速度バジェットに適合するかどうかを伝え、3番目のプログラム(配置配線)はこの設計をチップのサイトに配置します。

デザインがすべての段階を通過するとき:ベリロコーディング、デバッグ、検証、合成、静的タイミング解析、フロアプラン、配置配線、寄生抽出など -工場に送信されるGDSIIというファイルが判明し、工場がチップを焼きます。 このタイプの最も有名な工場は、台湾半導体製造会社またはTSMCが所有しています。

Habrahabrの投稿からFPGAを使用して鉄の開発を開始する方法-ステップバイステップの手順 :

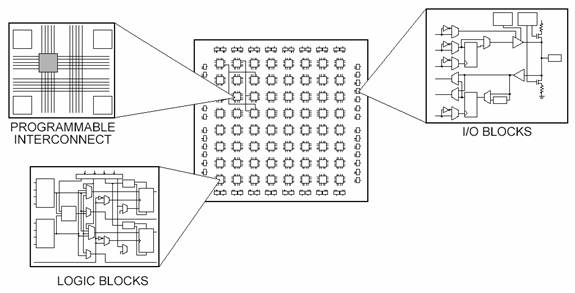

最も単純なバージョンでは、FPGAは同種のセルのマトリックスで構成され、各セルはコンフィギュレーションメモリのビットに接続されたマルチプレクサーを使用して機能に変更できます。 1つのセルは、4つの入力と1つの出力を持つANDゲートになり、別のセルはシングルビットレジスタなどになります。 ビットシーケンスをメモリからコンフィギュレーションメモリにロードします。特定の電子回路は、プロセッサ、ディスプレイコントローラなどのFPGAで形成されます。

FPGA / FPGAはプロセッサーではありません.FPGAの「プログラミング」(FPGAの構成メモリーを満たす)によって電子回路(ハードウェア)を作成しますが、プロセッサー(固定ハードウェア)のプログラミング時には、それに書かれた一連のプログラム命令のチェーンをスリップします(ソフトウェア)。