トロントのシンポジウムでサラ・ハリスが最近発表したMIPSfpgaに基づいた集合的な記事「 実務経験 」の翻訳。 2017年7月3日にリリースされたMIPSfpga 2.0の詳細な説明が提供されています。 私の意見では、バージョン1.3と比較した主な違いは、実験室作業パッケージが、プロセッサーの内部作業に焦点を合わせたセットで拡張されたことです。 したがって、最新のコアがどのように機能するかを知りたい場合は、MIPSfpga 2.0が高品質の自己教育に最適です。 この記事は、大学の教師にとって非常に役立ちます。コンピューターエンジニアリングの学部プログラムのIEEE / ACMガイドラインへの準拠を含む、MIPSfpga 2.0を教育プロセスに統合する問題について、詳細に、例とともに説明します。

記事にはマーケティングのちょっとしたタッチがありますが、MIPSfpga 2.0の尊厳を軽視していないように思えます。 オープンプロセッサコア間で教育プロセスに関するドキュメントの深さ、幅、方向が類似するものはまだ観察されていません。

この記事の著者の中には、デジタル回路とコンピューターアーキテクチャに関する人気の教科書であるYuriPanchulの著者であるDavid HarrisとSarah Harrisがいます。これらは、CIS諸国でのMIPSfpgaと教育イニシアチブの普及活動ですでにハーバーオーディエンスに知られています。 Imagination's University Programを監督するRobert Owenと、LinuxカーネルのメインブランチにMIPSfpgaサポートを追加したZubair L. Kakakhelに言及する価値があります(LinuxをMIPSfpga-plusにアップロードしたときに、カーネルコードを使用しました)。 元の記事へのリンク:[ L1 ]。

MIPSfpgaに基づく実用的な経験

著者:ダニエル・シャヴァー、ユーリ・パンチョル、エンリケ・セダノ、デビッド・M・ハリス、ロバート・オーウェン、ズバイル・L・カカケル、ブルース・アブライディンガー、サラ・L・ハリス

この記事では、学部課程または大学院課程の一部としてコンピュータアーキテクチャコースを教える際のMIPSfpgaソフトマイクロプロセッサの使用について説明します。 最新バージョン(MIPSfpga 2.0)は、スターターパック(MIPSfpga入門ガイド)、ラボパッケージ(MIPSfpga Labs)、およびチップシステム(MIPSfpgaシステムオンチップ)で構成されています。 この記事ではそれらについて簡単に説明し、マドリードのコンプルテンセ大学、ダルムシュタット工科大学での教育経験、およびロシアの大学や研究センターで開催されたセミナーに基づいて、MIPSfpgaをカリキュラムに統合する例を示します。 MIPSアーキテクチャの産業用プロセッサコアであるMIPSfpgaへのアクセスにより、MIPSアーキテクチャの研究と修正が可能になり、理論と実践のギャップを埋めることができます。

1.はじめに

MIPSfpgaプロジェクトは、コンピューターアーキテクチャの教育に焦点を当てた包括的な資料セットであり、イマジネーションテクノロジーズによって開発されました。 MIPS microAptiv UPカーネルソースコードに加えて、トレーニング資料と開発ツールが含まれています。 ソフトマイクロプロセッサは何十年も使用されてきましたが、MIPSfpgaはアカデミックライセンスで利用可能な最初の商用コアであり、コードは難読化されていません。 これにより、MIPSアーキテクチャの「おもちゃ」コアを使用して構築された既存の教育プログラムと、実際の産業用MIPSプロセッサおよび補助ツールとの間のギャップを埋めることができます。

2015年6月にリリースされたMIPSfpgaの最初のバージョンには、microAptiv UPカーネルソースに加えて、プロセッサ、システムオンチップ(SoC)、デバッグおよび開発ツールの説明が含まれた入門ガイドが含まれています。スクリプトとサンプルのセット。 次のパッケージ(MIPSfpga Fundamentals)には9つの実験室作業が含まれており、機器のセットアップ、プログラミング、デバッグ、およびさまざまな周辺機器のプロセッサコアへの接続について徐々に学習します。 最後に、3番目のパッケージ(MIPSfpga-SoC)はチップ上のシステムです。その例は、メモリ(DDR)、UART16550、I2C、イーサネットインターフェイスと相互作用するMIPSカーネルを中心に構築された完全なLinuxベースのソリューションを取得する方法を示しています、割り込みコントローラー。

2017年6月に、パッケージの2番目のバージョン(MIPSfpga 2.0)がリリースされました。 以前と同様に、3つの部分で構成されています:スターターパッケージ(MIPSfpga入門ガイド、GSG)、MIPSfpga Fundamentalsパッケージに代わる一連の研究成果(MIPSfpga Labs)、およびシステムオンチップ(MIPSfpgaシステムオンチップ、SoC)。 前のリリースと比較して、GSGパッケージには、Bus Blasterプログラマーを使用せずにカーネルのプログラミングとデバッグ、WindowsおよびLinuxを実行しているコンピューターでMIPSfpgaと連携するために必要なソフトウェアの展開に関する指示が追加され、VHDLのMIPSfpgaシステムの最上位モジュールの説明が追加されました。 MIPSfpga Labsパッケージには、マイクロアーキテクチャレベルでのコアの研究と変更に焦点を合わせた17の新しいラボ作業が含まれています。 それらの中には、キャッシュ構造とキャッシュコントローラーの分析と変更があります。 CorExtendインターフェイスを介してユーザー定義命令(UDI)を追加し、I / Oに割り込みとダイレクトメモリアクセス(DMA)を使用します。 MIPSfpgaカーネルに変更を加える方法を示します。

この記事のセクション2では、MIPSfpga 2.0の一部であるパッケージ(スターターパッケージ、実験室作業のセット、チップ上のシステム)、およびこれらの材料がコンピューターエンジニアリングの学部プログラム(IEEE / ACMのIEEE / ACMガイドラインに準拠する方法の分析)について説明しますコンピュータ工学の学部プログラムのカリキュラムガイドライン)[ 1 ]。 3つのコースを例として使用するセクション3では、MIPSfpgaをカリキュラムに統合する方法を示します。 セクション4では、MIPSfpgaに類似したプロジェクトについて説明します。結論はセクション5で示します。

2. MIPSfpga 2.0の概要

MIPSfpgaプロジェクトは、リソース[ 2 ]で利用可能な3つのパッケージで構成され、セクション2.1〜2.3で説明されています。 より詳細な説明は[3]にあります。 これらの資料は、コンピューターアーキテクチャコースの一部として教えられる理論的概念とよく一致しています。 セクション2.4では、コンピュータサイエンスの学部課程のIEEE / ACMガイドライン[ 1 ]の簡単な説明を提供し、このドキュメントの要件がMIPSfpga 2.0でどのように扱われるかを示します。

2.1。 スターターパック(MIPSfpgaスタートガイド、GSG)

検討中の最初のパッケージはGSGで、これにはMIPSプロセッサ向けの焦点の合っていないソースコードが含まれており、FPGA展開専用に設計されています。 このソフトマイクロプロセッサはmicroAptiv UPコアのバージョンであり、特に人気のあるMicrochip PIC32MZマイクロコントローラーで使用されています。 これは、5段階のパイプラインとMIPS32r3命令のセット[ 4 ]を備えたプロセッサの記述を含む(Verilog言語の)ファイルのセットです。 パッケージには、開発およびデバッグツール(Codescape MIPS SDK EssentialsおよびOpenOCD)、MIPSfpgaカーネルの説明、およびそれに基づいて構築されたシステム、MIPSfpgaおよびソフトウェアツールの使用ガイド、スクリプトおよびサンプルのセット( ノートトランスレーター:GSGにプロジェクトが含まれますSoKはベアメタルコードを実行するのに十分です.MIPSfpga-SoCパッケージには、より複雑なLinux向けSoCが示されています )。

図1. MIPSfpgaシステム

図1に示すMIPSfpgaシステムは、コア(MIPSコア)と、AHB-Liteバスを介して接続されている周辺機器で構成されています。 周辺機器には、メモリ(この場合、ブロックFPGAメモリ、ブロックRAM)と、FPGAデバッグボード上のLEDおよびスイッチへのアクセスを提供する汎用入出力インターフェイス(GPIO)が含まれます。 多くの大学がトレーニングコースでVerilogまたはVHDLを使用していることを考慮すると、MIPSfpga 2.0トップレベルモジュールは、リストされている言語ごとに2つのバージョンで利用できます。

MIPSfpgaを使用するには、FPGAを備えたデバッグボードとBusBlasterプログラマー(デバッガー)が必要です(翻訳者のメモ:より手頃な価格のデバッガーを使用できます[[ L2 ]を参照)。 上記の例ではNexys4 DDRとDE2-115についてのみ説明していますが、ドキュメントには、MIPSfpgaシステムをより控えめな機能(Basys3やDE0など)でデバッグするために移植する必要があるユーザー向けの詳細な手順が含まれています。 さらに、このマニュアルでは、FPGAの構成に必要なシミュレーションおよび合成ツール(VivadoまたはQuartus II)や開発ツールなど、MIPSfpgaの操作に必要なツールをダウンロード、インストール、および使用する手順について説明しています。 彼らの仕事には、WindowsまたはLinuxを実行しているコンピューターが必要です。

Imagination TechnologiesとEuropracticeおよびMOSISプロジェクトとの間でパートナーシップ契約が締結されていることは注目に値します。アカデミックおよび研究センターは、MIPSコアへのアクセスを提供されます。 Warrior M 5100および5150コアはこの契約に該当し、このクラスは、モノのインターネット、ウェアラブルデバイス、およびその他の組み込みアプリケーションのソリューションに焦点を当てたmicroAptivファミリーの拡張です。 したがって、研究者は、MIPSfpgaの一部として使用された同じカーネルの進化的に最新のバージョンにアクセスできます。 これらのコアは、浮動小数点ユニット(FPU)、DSP、一連のmicroMIPS命令、および特別なセキュリティ要件を伴うソリューションに必要なハードウェア仮想化ユニットを含む完全な構成で提供されます。 これにより、MIPSfpgaは、コンピューターアーキテクチャコースの一部として、および研究プロジェクトで使用可能な最終的なソリューションをシリコンで実装する可能性を含む、マスタープログラムのより複雑なセクションを教えるときに使用できる包括的な教育ソリューションとして位置付けられます。

2.2。 ラボ(MIPSfpga Labs)

2番目のMIPSfpgaパッケージは、GSGの一部であるSoCプロジェクトに基づいて、コンピューターアーキテクチャの実践的なトレーニングとチップ上のシステムの設計を目的としています。 実験室での作業を成功させるには、学生はデジタル回路、コンピューターアーキテクチャ、およびMIPS(ISA)命令セットの基本的な知識が必要です[ 5 ]。 ソフトウェア開発の経験は有用ですが、必須ではありません。 作業を実行する過程で必要なものを習得できます。

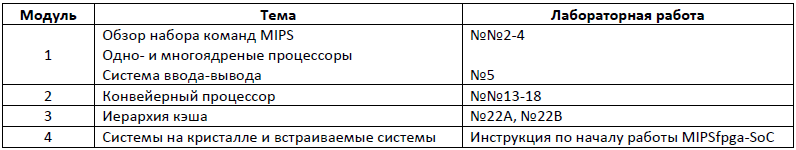

このパッケージには、学生がMIPSfpgaシステムの初期セットアップ手順を実行して、カーネルとそれに基づいたシステム内で発生する複雑な相互作用を研究できるようにする25の実験室作業が含まれています。 実験室の作業は、入力、入出力、マイクロアーキテクチャ、メモリの4つの部分に分けることができます。 研究室入門(No. 1-4)は、MIPSfpgaシステムを展開し、プログラムし、デバッグする方法を示しています。 入出力専用の作業例(No. 5-13)では、新しい周辺機器をシステムに接続する手順を説明しています。 3番目のグループの研究成果(No. 14-19)は、学生をmicroAptivプロセッサコアのマイクロアーキテクチャの詳細(MIPSfpgaの中心)に没頭させます。 そして最後に、最後のセット(No. 20-25)は、メモリ階層への変更の調査と導入に専念します。 表1には実験室作業のリストが含まれており、その詳細な説明を以下に示します。

表1.ラボ作業MIPSfpga

最初の部分(入門)は、MIPSfpgaを操作するために必要なツールを紹介する4つの実験室で構成されています。 作業番号1では、特定のFPGAのMIPSfpgaプロジェクトのアセンブリが、XilinxのVivadoソフトウェアまたはAlteraのQuartus IIソフトウェア( ノートトランスレーター:現在Intel )を使用して研究されています。Basys3およびDE0ボードの例は、さまざまなデバッグボードにMIPSfpgaを展開する方法を示しています。 Works No. 2,3では、Codescape SDK(MIPSアセンブリgccおよびgdbを含む)およびBus Blasterハードウェアデバッガーを使用してCおよびアセンブラープログラムをコンパイルし、それらをメモリにロードし、FPGAにデプロイされたMIPSプロセッサーで起動およびデバッグする手順を説明します。 作業番号4には、追加の実用的なプログラミングタスクが含まれています。

2番目の部分は、メモリマップI / Oデバイスとの相互作用に関する5つの論文から始まります。 MIPSfpgaシステムは、進行するにつれて、ますます複雑化する周辺機器と対話します。7セグメントインジケーター、ミリ秒タイムカウンター、音楽を再生するためのサウンドエミッター、SPIインターフェイス(LCDおよび光センサー)を備えた2つのデバイス。 作品7〜9の場合、追加のコンポーネントが必要です。これについては[3]で説明しています。

Works No. 10-12は、割り込みやダイレクトメモリアクセス(DMA)などのより複雑なトピックを扱います。 MIPSプロセッサで割り込みを使用する基本的な原則は、作品10で説明されています。 割り込みが周辺機器の定期的なポーリングを避けるのにどのように役立つかをすぐに示し、計算や入出力に関係しない他のタスクのためにプロセッサ時間を解放します。 以下の作業では、ダイレクトメモリアクセスモジュール(No. 11)およびDES標準に準拠した暗号化モジュール(No. 11)の分析、設計、構築、およびテストが考慮されます。 最後に、作業番号13では、microAptivコアで使用可能なパフォーマンスカウンターをセットアップして使用する手順を実用的な例で説明しています。 プログラムのパフォーマンスを評価するために、カウンターやさまざまな種類のイベントの使用を含むいくつかの演習が提案されています。 このメカニズムは、作品番号14-25のプログラムの有効性を評価するためにも使用されます。

実験室作業の第3部では、コアが内部作業に没頭します。特定のmicroAptiv機能の使用、CorExtendインターフェイスが示され、指示に従うときにコンベヤー操作が詳細に説明されます。 最初の4つの作業(No. 14-17)は、microAptivコアの内部コンポーネントとそのパイプラインの作業に当てられています。 ADD、AND、LW、およびBEQ命令の処理方法について説明します。 最初に、microAptivパイプラインのステージについて説明し、デコードされた命令が各ステージをどのように通過するかを示します。 その後、Verilogコードを参照した段階的なシミュレーション中に、これらの命令の処理に関連する主な信号が表示されます。 最後に、個々の制御信号を分析し、追加の指示を調べ、サポートされているmicroAptivコマンドのセットに新しい指示を追加するタスクが学生に与えられます。

作品番号18は、紛争解決ユニット(ハザードユニット)の作業を説明および示しています。 また、クロック周波数分周器の使用も導入されており、システムを使用すると、数MHz〜1 Hzの周波数範囲で動作できます。 クロック周波数を下げ、プロセッサコアの制御信号(パイプライン、競合解決ブロック、キャッシュ消去信号)をデバッグボードのLEDに接続することにより、ユーザーはプログラムの動作をリアルタイムで調査できます。

このパートの最後の作業(No. 19)は、MIPSプロセッサで使用可能なCorExtendインターフェイスの使用に当てられています。 これは、ユーザー定義命令(UDI)を宣言および実装するための強力なツールです。 CorExtendを使用すると、ユーザーは、専用のハードウェアモジュールをプロセッサコアに接続することにより、標準のMIPS32命令セットを使用して達成できるものと比較して、アルゴリズムの重要なセクションの実行速度を上げることができます。 このペーパーでは、CorExtendインターフェイスの機能、その機能、制限、プロセッサコア内のモジュール配置、時間特性、ユーザーコマンドブロックとmicroAptivパイプラインの相互作用、実験計画のいくつかの実践的な演習について説明します。

最後の実験室グループでは、MIPSfpgaメモリシステムが研究され、キャッシュ(No. 20-24)から始まり、内部(超手術)命令メモリ(Scratchpad RAM、No。25)の実装で終わります。 MIPSfpgaメモリシステムの動作の分析は、LEDへの対応する情報の出力(No. 20)を例としていくつかのプログラムを使用して、キャッシュのヒットとミスのデモンストレーションから始まります。

ペーパーNo. 21は、カーネルが使用するキャッシュを構成するさまざまなタイプのアレイ(アレイデータ、タグ、およびウェイセレクト)を分析します。 この作業では、キャッシュインターフェイスとその実装の両方について説明します。 詳細な説明の後、生徒には新しいキャッシュ構成を実装およびテストするタスクが与えられ、パフォーマンスカウンターを使用してコードを最適化するためのいくつかのアプローチが試されます。

次の3つのラボでは、キャッシュコントローラーの実装に焦点を当てます。 作品No. 22は、ヒットとミスの管理を分析し、ヒットまたはミスイベントに関係する主な段階、構造、および信号について説明しています。 これはすべてシミュレーションで示されています。 そして最後に、たとえば、キャッシュミスに関連するミスペナルティを推定することにより、キャッシュシステムを調べる演習が提供されます。 作業23では、microAptiv UPカーネルでサポートされるキャッシュ管理ポリシーについて説明しています。 学生は、さまざまな書き込みポリシーとキャッシュの割り当てライン(割り当てポリシー)を評価し、新しい置換ポリシーを実装する必要があります。 最後に、作業番号24では、データがデータキャッシュに書き込まれるまでデータを一時的に保存するストアバッファの動作について説明します。 また、ミス後にデータキャッシュに配置されるブロックを含むフィルバッファ(フィルバッファ)。

最後に、作業番号25は、命令内メモリ(命令スクラッチパッドRAM)をMIPSfpgaに追加する方法を示しています。 MIPSfpgaの基本構成には適切なインターフェイスがありますが、このモジュールの実装はありません。 このラボでは、システムに超動作メモリを追加し、命令/データキャッシュコントローラを介してシステムと対話する方法を示します。

実験室での作業が完了すると、学生は、新しい周辺機器(I2CやUARTなど)、プロセッサコアの新しい機能(ハードウェアプリフェッチユニットまたは遷移予測)、メモリシステム(2次キャッシュまたはウェイプレディクタ)、または教師を選択するその他の課題。

2.3。 システムオンチップ(MIPSfpga-SoC)

最新のMIPSfpga 2.0パッケージは、オープンソースオペレーティングシステムであるLinuxを実行しているプロセッサコアに基づいて、チップ上にシステムを構築する方法を示します。 複雑なプログラムの実行を提供する(組み込みシステムの要素としての)SoCデバイスの詳細な(レベル)説明が提供されます。

LinuxベースのSoCは、AHB-Liteバスを介して周辺機器を制御するMIPSプロセッサコアに基づいています。 バス上では、プロセッサがマスターとして機能し、周辺モジュールがスレーブとして機能します。 周辺機器として、ザイリンクス固有のIPコアが使用されるため、システム開発時間が大幅に短縮されます。 (翻訳者のメモ:他のメーカーのFPGAでオリジナルのMIPSfpga-SoCを起動することもできません。この状況から抜け出す方法はMIPSfpga-plus [ L3 ]-同様のSoCプロジェクトですが、プラットフォームに依存しない周辺機器からです)。 すべての周辺機器は、AHB-Liteバスを介してプロセッサコアに接続され、デバイスはメモリにマップされます(メモリマップI / O)。 ザイリンクスのペリフェラルモジュールはAXIバス(Advanced eXtensible Interface)を介して制御されるため、対応するインターフェイスコンバーター(ブリッジ)「AHB-Lite to AXI」がシステム(プロセッサとペリフェラル間)に含まれています。 すべてのSoCデバイスのうち、プロセッサコアとGPIOモジュールのみがImagination Technologiesによって提供され、その他の周辺機器はザイリンクスIPモジュールです。 シンプルなGPIOモジュールにより、プロセッサコアとボタンおよびLEDとの相互作用の例を使用して、周辺機器の構造と接続を理解できます。

図2.簡素化されたLinux SoC構造

Linuxオペレーティングシステムは、ユーザースペース(Linuxユーザースペース)とカーネル(Linuxカーネル)の2つの部分に分けることができます。 ユーザー空間のアプリケーションは、カーネルが提供するシステムコールの標準セットを使用してハードウェアと対話します。 ユーザー空間を構築するために、MIPSfpga-SoCは、優れたスケーラビリティを備えたBuildrootソフトウェアパッケージを使用します。 カーネルはハードウェアと相互作用し、抽象化のレベルを提供します。 SoCでLinuxカーネルを実行するには、少なくとも次の要件を満たす必要があります。MMUサポート付きプロセッサー、割り込みコントローラー、タイマー割り込み、UARTインターフェイス、メモリ、EJTAGインターフェイス。 上記のすべてが図2に示すシステムに存在することに注意してください。

さらに、MIPSfpga-SoCには、OSカーネルにシステムサポートを追加するLinux用のパッチセットが含まれています。 microAptiv UPプロセッサコアと周辺モジュールはカーネルで既にサポートされているため、既に存在するコードが使用され、MIPSfpga-SoCプラットフォームの説明のみが追加されます。 SoCのコアでBuildrootを実行するために、そのアセンブリはmips32r2アーキテクチャで実行されます。 その結果、標準のGNU Cライブラリを使用してアプリケーションを実行できるシステムが得られます。

2.4。 IEEE / ACM学部コンピューターサイエンスプログラムのガイドライン

コンピューターアーキテクチャの知識の分野に関連し、コンピューターエンジニアリングの学部プログラムのIEEE / ACMガイドラインで定義されているブロック(トレーニングトピック)のリストを表2に示します。

表2. IEEEガイドラインに従ったブロック

実験室での作業MIPSfpgaは、これらのブロックを幅広くカバーしています。 80年代前半に登場したMIPSアーキテクチャは、後のアーキテクチャで使用される多くのソリューションを定義しました。 したがって、コンピューティングシステムのアーキテクチャ開発の歴史において重要な役割を果たし、CE-CAO-1ブロックの主題に対応しています。 実験室作業№2-3には、Vivadoでのプロジェクトの作成、CE-CAO-2ブロックに対応するプログラムのコンパイル、実行、およびデバッグが含まれます。 パフォーマンスカウンター(CE-CAO-4)のトピックは、パフォーマンスカウンターを使用する場合の実験室作業番号13で取り上げられています。 カーネルとその要素のパフォーマンスに対するさまざまなイベントと実行された命令の組み合わせの影響を評価するために使用されます。 さらに、パフォーマンスカウンターは、実験室の作業番号14-25に関与しています。 特に、作業番号14では、トピックCE-CAO-5に対応するADDコマンドおよびその他の算術命令の実装が検討されています。

プロセッサアーキテクチャ(CE-CAO-6)は、前述のように、MIPSパイプラインの構造を考慮した実験室の作業番号14-18で研究されています。 作品番号20-25は、キャッシュ、およびCE-CAO-7ブロックを十分にカバーする超動作メモリを含むメモリ階層の包括的な概要を提供します。 CE-CAO-8ブロックおよびCE-CAO-9ブロックの主題は、さまざまな入出力デバイスのMIPSfpgaシステムへの接続、割り込み処理に基づく相互作用、ダイレクトメモリアクセスを使用したデータ転送、暗号化について説明している作業番号5-20に当てられています。

MIPSfpgaはシングルコアシステムであるため、マルチコアおよび分散システム専用の最後の2つのテーマブロック(CE-CAO-10およびCE-CAO-11)は資料に反映されていません。 それでも、MIPSfpgaに基づいて、より複雑なシステムを構築できます。 アカデミック向けに公開されています。 例として、[ 6 ]の著者は、MIPSfpgaコードに大規模な変更を加えることにより、120コアシステムを開発し、これをTerasic DE5-NET FPGAデバッグボードに展開しました。

3. MIPSfpgaを使用した実際の経験

MIPSfpga 2.0はすでにコース、セミナー、ハッカソンに使用されています。 この章では、教育プロセスにMIPSfpgaを統合する3つの例と、システムを使用するいくつかの追加例を示します。 検討中のすべてのケースで、MIPSfpgaはコンピューターアーキテクチャコースの指導とチップ上のシステムの設計に使用されます。

3.1。 コンプルテンセマドリード大学

2016/2017学年度の第2学期(2017年2月から6月まで)に、MIPSfpga 2.0はコンピューターアーキテクチャおよび組み込みシステムのコースの一部としてマドリードのコンプルテンセ大学で使用されました。研究の年。 このコースの学生は、デジタル回路、VHDL、コンピューターアーキテクチャ(MIPS命令セット、シングルおよびマルチコアプロセッサー、入出力サブシステム)、プログラミング(C ++)の分野で強力な基礎知識を実証します。 以下は、このコース、実験室の作業、評価基準、および学生のフィードバックの説明です。

3.1.1。 コース説明

12週間のコースは、4つのモジュールに分けられた24時間半の講義(週2回)で構成されています。 モジュール1は、以前に研究された資料、MIPS命令のセット、シングルおよびマルチコアプロセッサ、入出力システムに専念しています。 モジュール2では、MIPSプロセッサパイプラインが研究され、その実装は例とタスクを使用して研究されています。 モジュール3はキャッシュ階層を扱い、モジュール4はチップ上のシステムと組み込みシステムを紹介します。 MIPSfpga 2.0はこのコースに最適です。

[ 5 ] 4 ( ), 6 (), 7 () 8 ( -). , , , MIPSfpga : MIPSfpga, MIPSfpga ( 1) , -, [ 5 ].

3.1.2.

24 ( : , MIPSfpga, – , ). 12 , 2 . , MIPSfpga 25 , , : №№1-5, 13-18, 22 ( 1). , MIPSfpga-SoC. 3 :

3.

4. , . №2 MIPS, №4 – , – №6 №9 . , №1, Nexys4 DDR Bus Blaster. MIPSfpga GSG c [ 2 ], ( , Windows — B D, Linux – G). , ( 4.1, 4.2.1 7.4 – Windows, 4 G – Linux). Verilog ( 4 [ 5 ]), .. VHDL.

4.

1-2 . , №13 №6 №7: №6, () №6 №7. (№7) , .

№№14-18 3-4 . 5 5 1 . 30 .

, , . 60% ( №№13-17) .

3.1.3.

: 0.5 FE + 0.3 LM + 0.2*TM, FE – , LM – , ( 4), TM – .

3.1.4. コースレビュー

, (P. Fernandez, M. Sanchez, G. Diaz-Tejeiro, C. Oliver, J. Alvaro, A. Villarin, M. Cereceda, M. Perez, A. Dorda, PM Teba, FJ Oliva, EI Quezada, D. Fernandez, JA Canadas, A. Menendez, J. Martin, I. Diaz) . : «, , » (G. Diaz-Tejeiro); « , » (M. Sanchez); « » (J. Martin); « . , , , , , , - . -, » (A. Menendez). « , » (P. Fernandez). « » (A. Villarin).

3.2。

2015/2016 (TUD) « -, ». 14- ( ). 5 . [ 5 ]. (№№4-8) MIPSfpga ( 1).

5.

6 7 [ 5 ] MIPS . , MIPSfpga. №4 (MIPSfpga. ) №№1-3 ( 1). MIPSfpga №7, 9, 11 12 .

1-3 MIPS, , . MIPSfpga, – . 4 : - ; - (LCD); (DMA) AHB-Lite; DES. – . , .

(FPGA Nexys4 DDR, Bus Blaster, , -, ). ( GSG). 2-4 , , . , . 42 .

3.3。 ,

2015-2016 , MIPSfpga , : «», . . , «», , , - , , ( . – ), «». , MIPSfpga : Microchip Masters Russia, , SECR, Nanometer ASIC «». . , , . ASIC, - , , .

2015 , MIPSfpga , , . MIPSfpga ( , MIPS [ 5 ]) , , , (stalls) (forwarding). MIPSfpga , , , , , . ( , ), , HDL. , , MIPSfpga EDA . , , MIPSfpga 2.0. : ( 1 ), USB-UART , Bus Blaster, , CorExtend.

2016 . MIPSfpga HDL — . Nanometer ASIC MIPSfpga , ASIC MIPS M5150 ( MIPS microAptiv UP , Europractice). , , [ 8 ], MIPSfpga , SPI, I2C . : RTL- .

, MIPSfpga. , CorExtend ([ 9 ] , . ). MIPSfpga : SDRAM; ; Visual Studio Code ; UART16550 Linux Terasic DE10-Lite ( . : MIPSfpga MIPSfpga-plus [ L3 ], , [ L4 ]-[ L13 ] ). NGC-17 , MIPSfpga Wishbone () VGA- ( -- ). , , , .

4.

soft- , . MIPSfpga 2.0

4.1。 soft-

Xilinx Altera soft- Nios/Nios II [ 10 ] MicroBlaze [ 11 ] , . : , , / , , . ARM c : Cortex M0 Design Start [ 12 ] – (8K gates). , EJTAG . . .

. OpenSPARC [ 13 ] ( Oracle Sun Microsystems) LEON [ 14 ] ( Aeroflex Gaisler ). , , , (SPARC RISC) MIPS. : RISC-V [ 15 ], , openRISC, opencores.org [ 16 ]. , .

, MIPSfpga . , , PIC32MZ Microchip. (MIPS32r3) . MIPSfpga , . , , . MIPSfpga , Xilinx, Altera .

4.2。

[17] HIP- ( .: Hypothetical processor ), . 5- soft-, MIPS-. , , , . 52 , MIPS32r3, MIPSfpga. , , , . , MIPSfpga , , .

[18] BZK.SAU — . 59 . , , . , , , « ».

CNP, [19], , . MinIPS – , MIPS. — Tiny C. , MIPSfpga , MIPSfpga .

MIPS32r3命令セットは広く知られており、十分に文書化されているため、教師は独自のコンパイラを実装するか、Codescape MIPS SDK、gcc、LLVMなどの既存のサポートMIPSのいずれかを選択できます。さらに、MIPSfpga-SoCパッケージの例は、イーサネットコントローラーをMIPSfpgaコアに接続することが非常に実行可能なタスクであることを示しています。

最後に、[20]で、高度なマルチコアアーキテクチャのコースが紹介されています。 このコースは、MIPSfpgaの元のフレームワークを超えていますが、前述のように、教師は[ 6 ]に示すように、MIPSfpga GSGを自分のニーズに適合させることができます。

4.3。 結論

この記事では、2017年6月にリリースされたMIPSfpgaの最新バージョンの分析と、そのセミナーおよびトレーニングコースへの応用について説明します。 この出版物に示されているように、MIPSfpga学習インフラストラクチャは、コンピューターアーキテクチャコースで教えられているトピックに完全に適合しています。 さらに、学習プロセスでMIPSfpgaを使用すると、学生は開発エンジニアが解決すべき問題と同様の問題に直面します。

その中には、周辺機器のSoCへの統合、標準インターフェイス(CorExtendなど)の使用、および商用コア(microAptivなど)の変更による新しい命令の追加があります。 パフォーマンスカウンターを使用したさまざまなキャッシュ構成とポリシーの評価 Linux OSを起動して、ザイリンクスの商用コアおよび周辺モジュールに基づいた完全なSoCを構築します。 学習への単純化されたアプローチ(たとえば、[ 5 ]に示され、非常に原始的なコアに基づく)は、最初の学部コースにより適している場合があります。 同時に、解決すべき問題は学生が現実の世界で直面しなければならない問題に非常に近いため、教育における産業グレードのソリューションの使用への移行には利点があります。 MIPSfpgaが学部および大学院コースの優れたソリューションである理由。

5.謝辞

著者は、イマジネーションユニバーシティプログラムへの貢献について、次の個人および組織に感謝します。ネバダ大学、ラスベガス、インペリアルカレッジロンドン(イギリス)、マドリッドコンプルテンセのArTeCSグループ(UCM)、スペイン政府の研究契約TIN2015-65277- RおよびTIN2015-65316-P、Munir Hasan(IMG UK)、Prashant Deokar(IMG India)、Mahesh Firke(IMG India)、Parimal Patel(Xilinx)、Kent Brinkley(IMG USA)、Rick Leatherman(IMG USA)、Chuck Swartley (IMG USA)、Sean Raby(IMG UK)、阿部道夫(IMG Japan)、Bingli Wang(IMG China)、Sachin Sundar(IMG USA)、Alex Wong(Digilent Inc。)、Matthew Fortune(IMG UK)、Jeffrey Deans (IMG UK)、Laurence Keung(IMG UK)、Roy Kravitz(ポートランド州立大学)、Dennis Pinto(UCM)、Tejaswini Angel(ポートランド州立大学)、Christian White、Gibson Fahnestock、Jason Wong、Cathal McCabe(ザイリンクス)、およびラリッサスワンランド(Digilent)

6.参照

[1] CE2016-コンピューター工学の学部プログラムのカリキュラムガイドライン。 IEEEおよびACM、2016

[2] イマジネーション大学プログラム-リソース

[3] Harris、S.、Harris、D.、Chaver、D.、et al .: "MIPSfpga:コンピュータアーキテクチャ教育における商用MIPSソフトコアの使用"。 IET回路、デバイスおよびシステム、2017年。

[4] Imagination Technologies Ltd。、「MIPS32 microAptiv UPプロセッサコアファミリデータシート」、2013年7月31日

[5] Harris、D.、およびHarris、S.、「デジタル設計とコンピューターアーキテクチャ」(Elsevier Science and Technology、2007、第2版2012)

[6] Kumar HB、C.、Ravi、P.、Modi、G.、Kapre、N ..:「120コアmicroAptiv MIPSオーバーレイfor Terasic DE5-NET FPGAボード」、Int。 シンプ Field-Programmable Gate Arrays、米国モントレー、2017年2月

[7] Intro HDLデザイン

[8] NTUUハッカソン

[9] CorExtendインターフェイス

[10] アルテラ-NIOS-IIプロセッサ 、2017年2月

[11] ザイリンクス-MicroBlazeソフトプロセッサコア 、2017年2月にアクセス

[12] ARM-Cortex M0デザインスタート 、2017年2月にアクセス

[13] Oracle-OpenSPARC 、2017年2月

[14] Aeroflex Gaisler-LEONシリーズソフトコア 、2017年2月にアクセス

[15] Waterman、A.、Lee、Y.、Patterson、DA、et al。、 "The RISC-V Instruction Set Manual、Volume I:User-Level ISA"、version 2.0、2014

[16] OpenCores OpenRISC 、2017年2月にアクセス

[17] Buli´c、P.、Guˇstin、V.、ˇ Sonc、D。、およびˇ Strancar、A、。:「コンピューターアーキテクチャー向けのFPGAベースの統合環境」、工学教育におけるコンピューターアプリケーション、2013、21 (1)、pp。 26-35

[18] Oztekin、H.、Temurtas、F.、Gulbag、A。:「BZK.SAU:教育目的のためのハードウェアおよびソフトウェアベースのコンピューターアーキテクチャシミュレーターの実装」。 手続き 2番目の国際 確認 コンピューターの設計とアプリケーション、in皇島、中国、2010年6月、pp。 490-497

[19] Abe、K.、Tateoka、T.、Suzuki、M.、Maeda、Y.、Kono、K.、Watanabe、T .: "プロセッサー組織、コンパイラー設計、コンピューターネットワーキングのための統合研究所"、IEEE Trans 。 教育、2004、47、(3)

[20] Petit、S.、Sahuquillo、et。 al:「高度なマルチコアアーキテクチャに関する研究指向のコース:コンテンツとアクティブな学習方法論」、Journal of Parallel and Distributed Computing、Elsevier、2017

サイトリンク

[L2] MIPSfpgaおよびインサーキットデバッグ

[L3] プロジェクトMIPSfpga-plus

[L4] MIPSfpgaおよびSDRAM

[L5] MIPSfpgaおよび割り込み

[L6] MIPSfpgaおよびUART

[L7] MIPSfpgaだけでなく現在の活動

[L8] MIPSfpgaおよびAltera FPGAでLinuxを上げる

[L9] MIPSfpgaを他のボードに移植し、周辺機器をシステムに統合する

[L10] 例としてPmod KYPDキーボードを使用して、MIPSfpgaに周辺モジュールを接続する

[L11] 例として超音波距離センサーを使用して、MIPSfpgaに周辺モジュールを接続する

[L12] MIPSfpga:キヤノンから

[L13] MIPSfpgaの使用を開始する方法