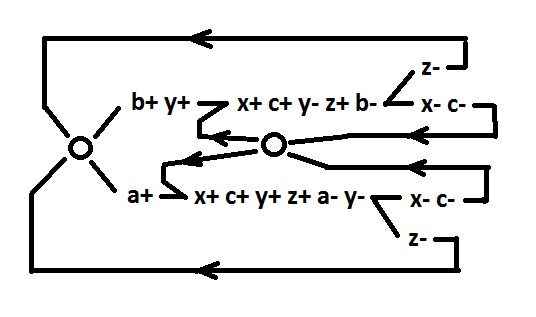

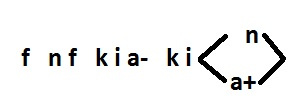

Petrifyを使用して回路を作成する方法の例を見つけました。 元のタスクは次のようになります。

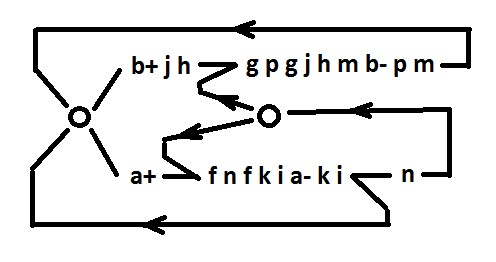

結果はこのSI回路です:

はい、彼らはミュラーから遠く離れていませんでした。まあ、Cエレメントだけがハングアップしていました。 それにもかかわらず、非同期回路の作成方法を示す必要があると思います。 始めるには、これに精通することをお勧めします。

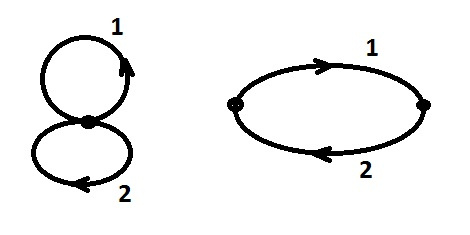

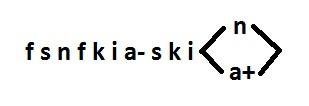

そして、ここで与えられた例を分析します。 最初に、元の動作をより便利に描画し、長い信号名を置き換えます。

dsr-a

dsw-b

ldtack-c

lds-x

d-y

dtack-z

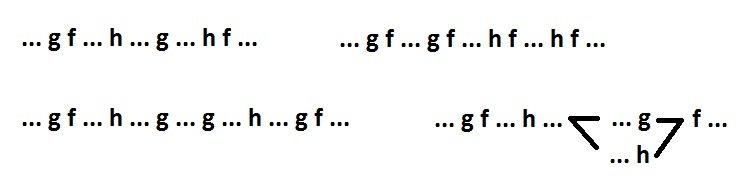

2入力要素でSI回路を合成するには、初期信号に新しい信号を追加して、各非入力信号(f)が次のパターン(またはそれらの組み合わせ)のいずれかに入力されるようにする必要があります。

選択動作に関連してパターンを使用する方法を理解するために、2つの代替ブランチで構成される動作を検討してください。 次に、同じ2つのブランチの動作を検討しますが、順番に順番に並べます。

これらの動作の両方の論理関数が同じであることを確認するのは簡単です。 これは理解できます。2番目の動作は最初の動作と同じですが、入力信号を切り替えるという固定された規律があります。 したがって、選択した動作に関連してテンプレートを使用するには、少なくとも1回は任意の順序ですべてのブランチを順番に処理する必要があります(ただし、元のタスクを許可するブランチのみ)。 そしてもう一つの注意:サインを修正せずに追加の信号が挿入されます。 標識は最後に配置されます。

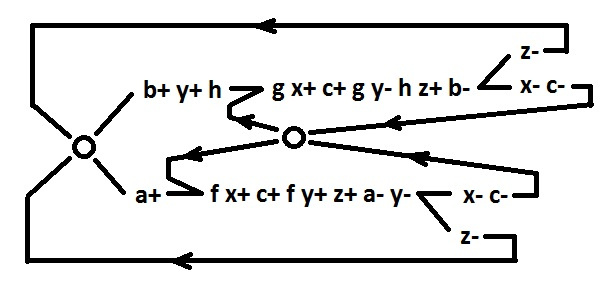

したがって、元の動作を見てください。 最初に解決する必要がある問題:並列分岐x- c-と同時に選択が発生します。 このブランチを同期する必要があります。 動作のさらなる断片化を念頭に置いて、代替ブランチごとに個別に同期することをお勧めします。 同時に信号を分離しますc。

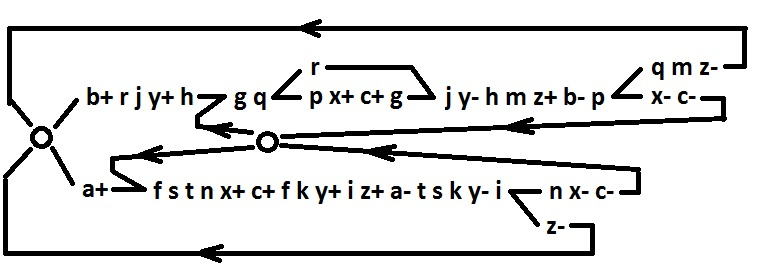

追加された信号fは、既存の信号(f = ac)を使用して、テンプレートに適合します(つまり、2入力実装です)。 信号gは、信号yとcを使用してパターンに入力できますが、信号yを分離するために後で使用できる信号hを追加することをお勧めします。 信号f、gは、疑似入力、つまり 新しい信号をそれらの前に置くことを禁止します(2入力実装を損なわないようにするため)。

調査した動作は、明らかに2つの代替ブランチに分かれています。 したがって、2つの独立した動作に分割でき、それぞれが代替ブランチの1つになります。 これを行うには、両方の分岐で見つかった信号を分離します。 信号xを分離するとは、この信号xおよびすべての信号結果(スイッチングが信号xの切り替えの結果である信号)の2入力実装(テンプレートに適合する)を取得することを意味します。 したがって、回路に対する信号xの影響を排除し、それを考慮しない場合があります。

両方の分岐に共通するのは信号-c、x、y、zです。 信号cは入力であり、実装する必要はありません。 その結果f、gはすでに実現されています。 信号xとzの結果は入力信号であり、実装する必要はありません。 信号yの結果については、hと新しい信号iを使用します(h = yb、i = yb)。 信号hとiは、擬似入力になりました。 信号yを実現するために、新しいjとkを導入します(y = jk)。 信号zは、既存の信号iと新しい信号m(z = im)を使用して実現されます。 信号xを実現するために、新しい信号nとpを追加します(x = np)。 信号y、z、xは擬似入力になりました。

分離された信号をグラフから削除します。 アクションは信号を追加するときと同じで、逆のシーケンスのみです。 信号を削除する理由は次のとおりです。分離された信号を使用して動作する回路を合成するには、同じ動作をするがリモートの分離された信号を使用して回路を構築するだけで十分です。

信号a、bは入力、f、g、h、iは擬似入力です。

(各ブランチに固有の信号を使用して)この動作の回路を合成するには、代替ブランチごとに2つの回路を個別に合成するだけで十分です。 分岐nが選択ポイントに平行であるという事実は、障害ではありません。 この分岐は、擬似入力信号gによって同期されます。

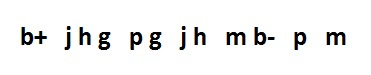

上部ブランチを個別に検討してください。

信号b、g、hは入力または擬似入力です。

分解の準備を検討してください。 CSC違反はありません。 信号mには既に2入力実装があります(m = ph)。 信号jの場合、信号gはデュアルとして使用できます。 信号pに対して、デュアル信号qを追加します。

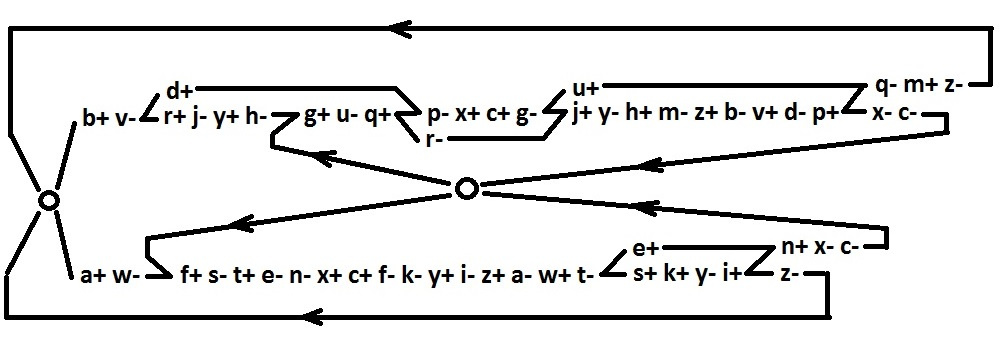

これで論理関数が見つかりました。 記号は配置されていませんが、関数の形式は条件付きです。

m = qh

p = bq

q = gp

j = g + bpまたはj = g + bq

jを分解します(これにより、新しい信号rが導入されます)。

j = rg

r = bpまたはr = bq

rは(-qの代わりに)pの結果になる可能性があることに注意してください。 これは、キャラクターを配置するときに便利です。

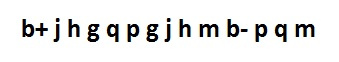

次に、下位ブランチを個別に検討します。

信号a、f、iは入力または擬似入力です。

CSC違反があります。 これらのシーケンスは、nfnfおよびki a-ki a +です。 可能な唯一の方法で除去されます(シグナルs)。

信号n、kには既に2入力実装があります(n = si、k = fs)。 信号sには、デュアル信号tが必要です。

論理関数は次のようになります。

n = ti

r = fs

s = ft

t = as

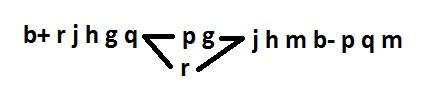

両方の代替分岐について、すべての信号が2入力ベースで実行可能性に低下します。 ここで、追加されたすべての信号を使用して、動作を完全に復元します。

そして最後に、標識を配置しましょう。 結果として生じる信号i、f、q、p、nの入力の不一致は、インバーターv、w、u、d、eをそれぞれ追加することによって修正されます。

そして、これがすべての信号の論理関数です。

スキームは次のようになります。

トランジスタペアのカウント。 耳をつんざくような優位性は機能しませんでした。 間違っていなければ78から94。 まあまあ。 無駄にしようとした、または何か。 公開します。