Habréで公開されているアマチュアFPGAプロジェクトのほとんどは、アルテラ(現在のIntel)の機器で作成されています。 主要な競合他社であるザイリンクスの製品で何ができるかを見てみましょう。 私たちは、実装の過程で必要となる十分に大きく複雑なプロジェクトを取り、作成します。

- 開発ボードとそれに必要なPMODを選択します

- プロジェクトの設計を決定し、クロックドメインとそれらの間の移行ルールを選択します。

- ザイリンクスVivadoの基本機能をマスターする-プロジェクトの作成、ブロック図の操作、コンパイル、シミュレーション、デバッグ

- AXI4インターフェイスで複数のIPを作成する

- 外部デバイスを操作する

- バスコントローラーと割り込み処理を使用して独自のプロセッサをゼロから作成する

- 検証用のモジュールを書く

- 最後に、すべてをまとめて、80年代半ばの伝説的な(少なくとも当時生きていた人たちの)コンピューターのFPGAに実装を取得します-BK-0010

このすべてを詳細に説明する一連の記事が計画されていますが、今日はそれらの最初のものです。 プロジェクトはSystem Verilogで記述されており、必要に応じて小さなVerilogとVHDLが挿入されます。 読者は、 Harris&HarrisブックレベルでVerilog / VHDL言語の基本原則を理解する必要があります。

BK-0010について一言

BK-0010は1986年に登場し、KR1801BM1プロセッサ(DEC PDP-11コマンドシステム)に基づくシングルボードコンピューターでした。 ストーリーが進むにつれて、そのアーキテクチャの機能の一部を検討する必要があります。今は、ボードやその他の機器を選択するのに重要なコンピューターの特性に限定します。

| 特徴 | 価値 |

|---|---|

| CPU | 3 MHz、約18000のトランジスタ数(n-MOS) |

| RAM | 32 KB |

| ROM | 8-32 KB |

出力デバイス

- 家庭用テレビ、512x256の白黒または256x256の色(各ドットは他とは独立して4色を持つことができます)

- サウンドトゥイーター(1ビット出力)とテープレコーダーへの出力の組み合わせ

入力機器

- JCUKENキーレイアウトのキーボード

ボードの選択

プロジェクトに使用するボードとチップは何ですか? 水晶の場合、Artix-7およびZynq-7000から要件に合わせて選択できます。どちらの場合も、最小の水晶で十分です。 開発ボード-ザイリンクス自体が行うことは、非常に豊富なスタッフがいるが、4桁の価格タグを持つボードです。 ヨーロッパの会社Trenz Electronic GmbHがありますが、彼らの製品は既製のデバイスの作成により重点を置いていると思います。 私の意見では、Digilentはアマチュア向けにザイリンクスチップを搭載した最適なマザーボードを製造しています。 Artix-7ではBasys-3、Nexus 4 DDR、Nexus Video、Zynq-7000ではZyboおよびZedBoardです。

私自身は、Zyboに決めました。 このボードは、最も安価なものの1つ(189ドル、Academic Discount Programの要件を満たしていることをDigilentに確信させた場合は125ドル)、VGA出力とHDMI出力の両方、多くのPMODポート、512MB RAMを備えています。 はい、このボードはSoCに基づいており、このプロジェクトでプロセッサコアの機能を使用する予定はありません。 しかし、FPGAのようにこのボードを使用する人はいません。 ボードには7セグメントデバッグインジケーターがなく、PS2またはUSBキーボードをFPGAパーツに接続する方法はありません(より高価なNexus 4 DDRとは異なります)が、これら2つのボードの価格差は、この機能を搭載できるPMODモジュールのコストよりもはるかに大きくなります受信する。

したがって、最終的には、プロジェクトには次の機器が必要になります。

ザイボ

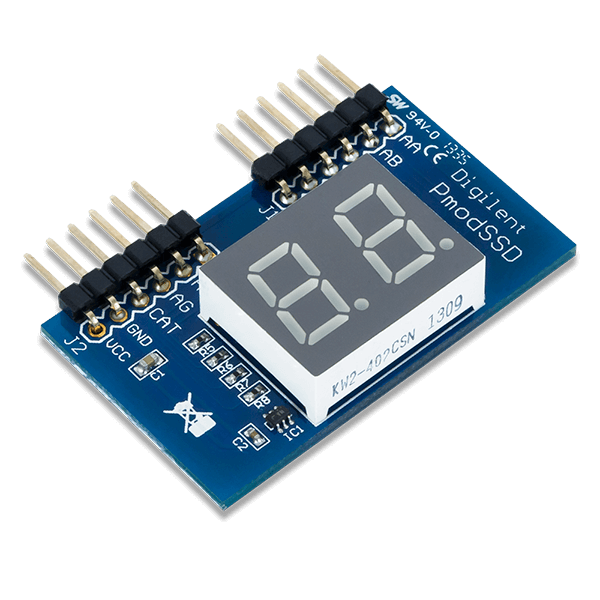

PMOD-SSD-デバッグ用の2つの7セグメントインジケーター

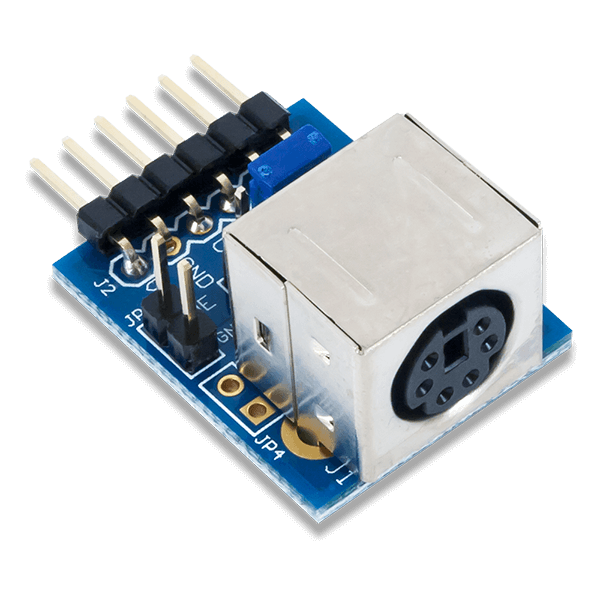

PMOD-PS2 -PS / 2キーボードを接続します。 購入するのを忘れていたので、自分でやらなければなりませんでした。 同時に、3.3Vのキーボードが機能しなかったため、DC-DCコンバーター3.3-> 5Vを配置しました。

古いPS / 2を使いたくないのですが、キーボードをUSBで接続したいです。

そうかもしれませんが、いくつかの困難があります。

ZyboにはUSBホストがありますが、PSパーツに接続されています。 PLプロジェクトを計画する場合は、別のUSBホストをボードに接続する必要があります。

USBプロトコルの完全な仕様(HOSTおよびすべてのタイプのデバイスのサポートを含む)をFPGAに実装するのは非常に難しく、USBインターフェイスはかなり高い頻度です。 妥当な妥協案は、例えばULPIインターフェイスを介して外部物理層コンバーターを接続することです。ULPIを操作するために、Verilog / VHDLで既製のIPモジュールを見つけることができます。 また、キーボードとマウスを操作するためのUSBホストがすでにある別のボード(Digilent、たとえばNexus 4 DDR)を選択することもできます。

ZyboにはUSBホストがありますが、PSパーツに接続されています。 PLプロジェクトを計画する場合は、別のUSBホストをボードに接続する必要があります。

USBプロトコルの完全な仕様(HOSTおよびすべてのタイプのデバイスのサポートを含む)をFPGAに実装するのは非常に難しく、USBインターフェイスはかなり高い頻度です。 妥当な妥協案は、例えばULPIインターフェイスを介して外部物理層コンバーターを接続することです。ULPIを操作するために、Verilog / VHDLで既製のIPモジュールを見つけることができます。 また、キーボードとマウスを操作するためのUSBホストがすでにある別のボード(Digilent、たとえばNexus 4 DDR)を選択することもできます。

ザイリンクスVivado入門

ザイリンクスのプロジェクト(この場合、第7シリーズのチップについて話している)は、ザイリンクスVivadoで作成されます。 ハイエンドチップ(UltraSCALE / UltraSCALE +)を使用する予定はないため、無料のザイリンクスVivado WebPACKエディションがこの目的に適しています。 xilinx.comに登録し、ダウンロードしてインストールします。

システム要件

これは主にRAMです。 Zyboにとっては難しいですが、8 GBで十分です。より強力なチップを使用するには、さらに多くが必要です。

Zyboを使用するには、Vivadoボードファイルパッケージをダウンロードして、Vivadoに追加する必要があります。これには、ボードで使用可能なインターフェイス、チップの周波数特性などの説明が含まれています。 Digilent Webサイト(またはGitHub )からダウンロードして、Vivadoに追加します。

また、チップコネクタとボードコネクタのピン番号の対応を記述したリソースファイルも必要です。 ボード、この場合はZyboをGitHub / Digilentで見つけてダウンロードします。

そして最後に、Verilogで最初のプロジェクトをやってみましょう。 BK-0010キーボードコントローラーを作成するには、今後このプロジェクトが必要になります。

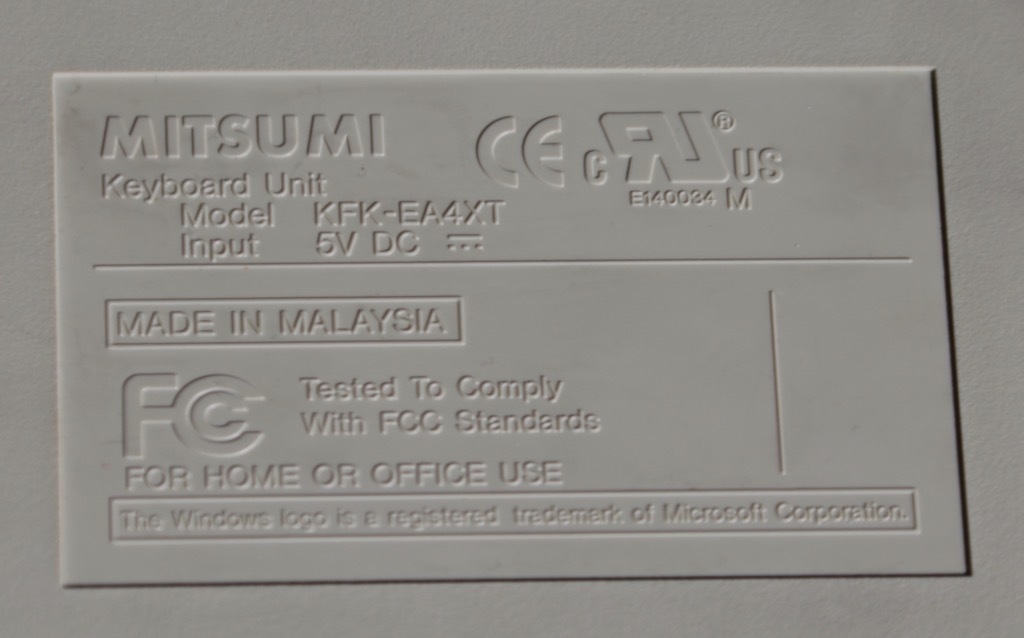

PS / 2インターフェイスを備えたこのような珍しいミツミキーボードがあります。

プロジェクトのishevchukは、 このコントローラーを使用してPS / 2キーボードを操作しました。

それを取り、少しやり直します。 コントローラは、50 MHzの固定クロック周波数を持っていることを除いて、すべての人に適しています。 BK-0010プロジェクトではこのような頻度はありません。また、そのようなことをハードコーディングするのは良くありません。 Vivadoで新しいプロジェクトを作成し、コントローラーファイルをダウンロードして、クロック周波数をパラメーターとして設定します。

数式モジュールヘッダー

module Altera_UP_PS2_Command_Out # ( parameter CLOCK = 100, // Timing info for initiating Host-to-Device communication // when using a 50MHz system clock parameter CLOCK_CYCLES_FOR_101US = (CLOCK * 101), // 5050; parameter NUMBER_OF_BITS_FOR_101US = $clog2(CLOCK_CYCLES_FOR_101US), parameter COUNTER_INCREMENT_FOR_101US = 1, // Timing info for start of transmission error // when using a 50MHz system clock parameter CLOCK_CYCLES_FOR_15MS = (CLOCK * 15000), // 750000; parameter NUMBER_OF_BITS_FOR_15MS = $clog2(CLOCK_CYCLES_FOR_15MS), parameter COUNTER_INCREMENT_FOR_15MS = 1, // Timing info for sending data error // when using a 50MHz system clock parameter CLOCK_CYCLES_FOR_2MS = (CLOCK * 2000), // 100000; parameter NUMBER_OF_BITS_FOR_2MS = $clog2(CLOCK_CYCLES_FOR_2MS), parameter COUNTER_INCREMENT_FOR_2MS = 1 )

プロジェクトの一部のモジュールには、名前にアルテラという単語が含まれています。 ザイリンクスでは、開発者を尊重するため、これらが機能しなくなることはありません。名前を変更しませんでした。

さらに、RESET信号の極性を変更します。標準IPの場合、RESET入力に0が適用されるとザイリンクスリセットが発生します。

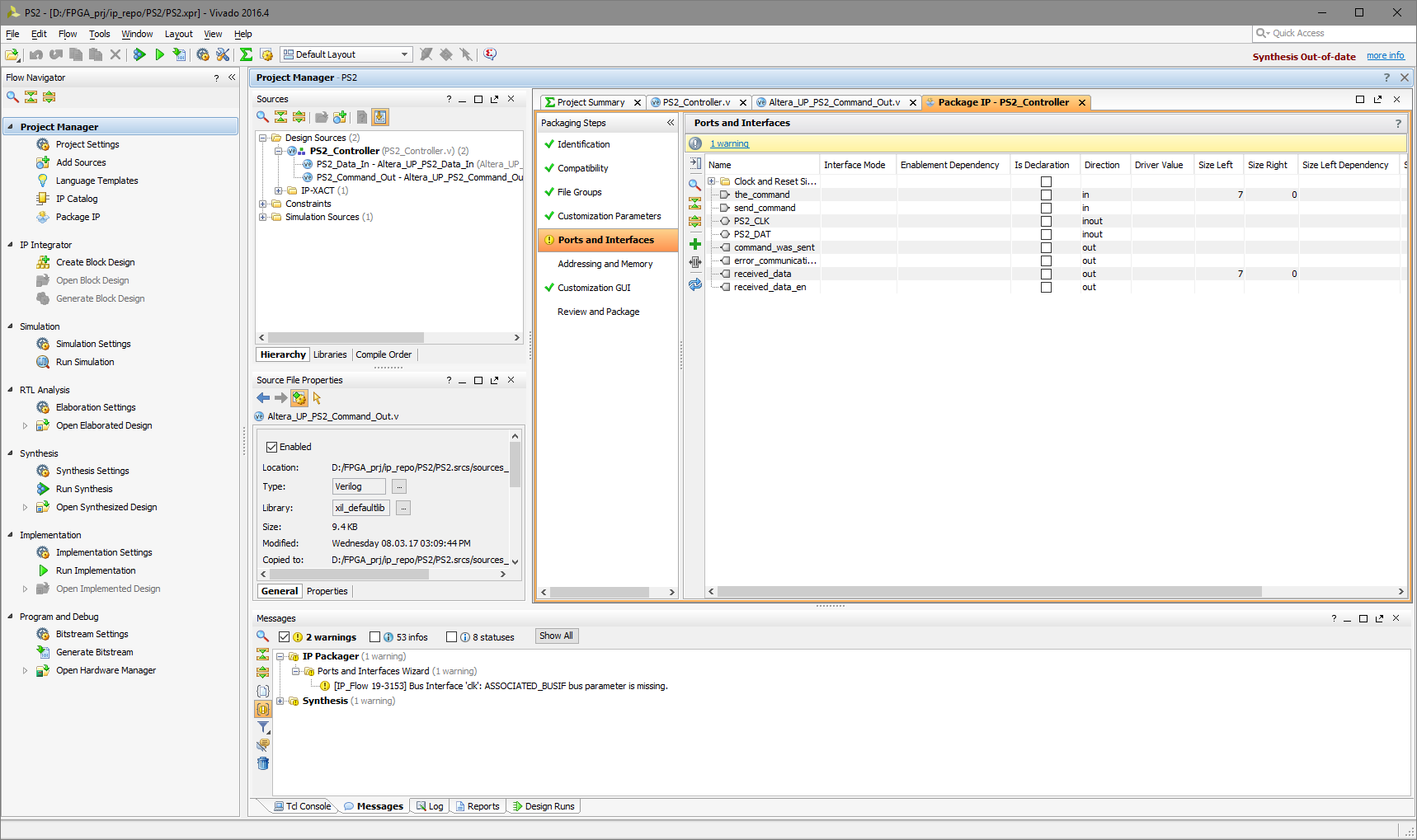

便宜上、プロジェクトをIP形式で手配します。 Vivadoにはこれを行う組み込みツールがあり、[ツール]-> [新しいIPの作成とパッケージ化]から呼び出されます。 プロジェクトヘッドファイルの入力と出力は、新しいIPの入力と出力になります。 Vivadoは、名前を分析してポートのタイプを判別しようとします。 この場合、プロジェクトをさらに組み立てる際の警告の数を減らすために、このプロセスに介入し、クロックおよびリセット信号番号からPS2_CLKポートを除外する必要があります。 PS2_CLKは、周波数が数十キロヘルツであるため、本格的なクロック信号とは言えません。

このツールは非常に柔軟性が高く、ポートのタイプを設定するだけでなく、さまざまなパラメーターを管理し、条件付きコンパイルオプションを設定し、パラメーターに応じてIPの外観を変更できます。 このプロジェクトには、Initialize Mouse(デバイスの選択-キーボードまたはマウス)とClock(クロック周波数(メガヘルツ))の2つのパラメーターがあります。 後でMPIバスを操作するためのモジュールを作成するときに、条件付きコンパイルの問題を検討します。

GitをVivadoに接続する

最後に(そして、一般的にこれはもちろん、新しいプロジェクトを作成した直後に行う必要があります)、それをVivado Gitに固定します。 Verilog / VHDLソースコード、制約、コンポーネントの説明、IPモジュールインターフェイスの説明、プロジェクト自体などはテキストファイルであり、それらはすべて簡単です。 ただし、複雑な点が1つあります。プロジェクトファイル(XML形式)には、ソーステキストへの絶対パスがあり、マシン間でプロジェクトを転送するときに問題が発生する可能性があります。 解決策の1つは、既製のツール(ザイリンクスエンジニアが作成)を使用することです。このツールは、Vivadoプロジェクトに基づいてポータブルtclスクリプトを作成し、ターゲットマシンで起動すると、元のプロジェクトと同一のプロジェクトを作成します。 このツールにラッパーが追加され、tclスクリプトの作成の自動化、.gitignoreファイルの入力、入力エラーの処理などが行われました。 このラッパーをインストールすると、Vivado TclコンソールからGitを直接操作できるようになります。

プロジェクトを鉄で埋めます

それでは、どのように機能するかを確認しましょう。 PS2コントローラープロジェクトを閉じて、キーボードからスキャンコードを受け取り、7セグメントインジケーターに発行するテストプロジェクトを作成します。 このプロジェクトでは、Verilogコードを1行も記述しませんが、既製のIPモジュールから回路を組み立てます。

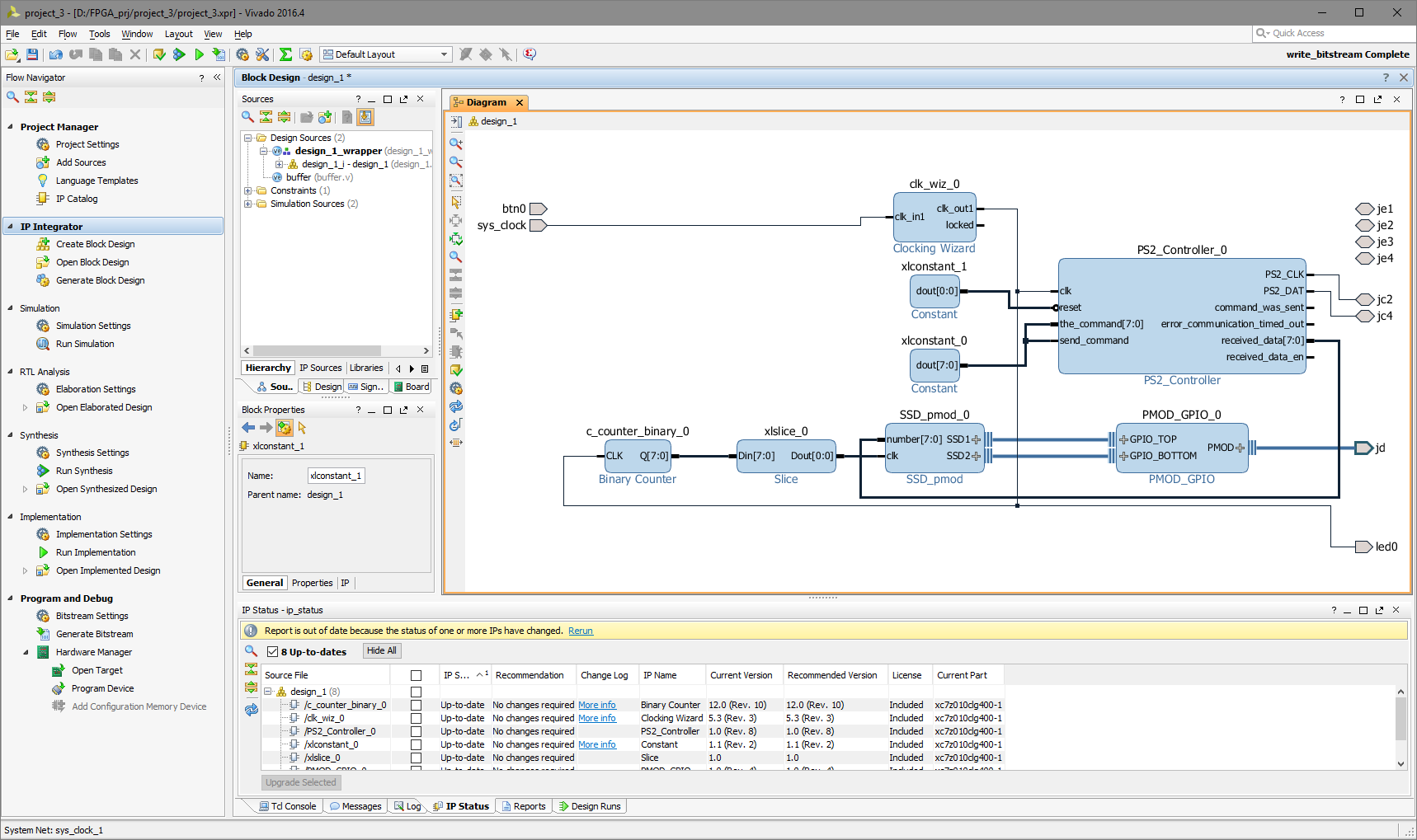

IPインテグレーターで、新しいブロックデザインを作成し、IPを追加して、このスキームが次のようになるまで接続します。

ここでは次のIPが使用されました。

クロッキングウィザードクロック信号を作成するためのモジュール。 異なる周波数とデューティサイクル(この場合は1つの100MHzの方形波)を持つクロック信号(最大6個)を作成するように設計されています。 システムクロック(125 MHz)が入力に供給されます。 PLLリソースを使用すると、出力クロック信号は対応する水晶リソースを伝播します。 ザイリンクス標準モジュール。

バイナリーカウンター カスタム区切り線、この場合は8ビット。 ザイリンクス標準モジュール。

スライス この場合、バスディバイダーはバイナリカウンターから最上位ビットを引き出し、256のディバイダーを形成します。標準のザイリンクスモジュール。

一般に、このようなことはクロック信号ではできません; Clocking Wizardから別の出力を取得し、Clock Domain Crossingを正しく設定する必要があります。 ただし、この場合、数百ヘルツから数百キロヘルツまでのあらゆる周波数が、まったく同期されていないため、SSD_pmodが機能するのに適しています。

SSD_pmod。 2桁の7セグメントDigilent PMOD-SSDインジケーターに16進形式でバイトを表示するモジュール。 バイトはモジュールの入力に到着します。 モジュールのソースコードはGitHubに投稿されています。

PMOD_GPIO。 PMODコネクターの信号の処理を説明するモジュール。 コネクタに接続されているモジュールのタイプに応じて、さまざまなプロトコルが使用されます-GPIO、SPI、I2C、UART。 私は、PMODをサポートするためにDigilentが作成したモジュールを基本とし、わずかに変更しました。 モジュールのソースコードはGitHubに投稿されています。

定数モジュール。 これは単に0または1の定数です。この場合、キーボード送信を使用しません。したがって、0は入力send_commandとthe_commandに送信され、1はリセット入力に適用されます(最終プロジェクトでは完全なリセット回路があります)。

最後に、 PS2_controller、前のステップで作成したモジュール。 追加できるように、プロジェクトプロパティでパスを指定することを忘れないでください。

次の外部接続を使用します。

sys_clockボード上の外部ジェネレーターからの125MHzクロック(ピンL16)。 PLLを開始するために使用されます。

PMOD_CキーボードはポートCに接続され、ビットJC2(W15)およびJC4(T10)が使用されます

PMOD_D 7セグメントインジケータはポートDに接続され、8ビットすべてが使用されます。

ブロックデザインを保存し、Verilogでラッパーを生成(HDLラッパーを生成...)、プロジェクトをコンパイル(ビットストリームを生成)、JTAGを介してボードにアップロード(ハードウェアマネージャーを開く、ターゲットを開く、プログラムデバイス)。 これで、キーボードのボタンを押すと、スキャンコードが7セグメントインジケーターに表示されます。

8'h4Eは '-'

参照資料

これをすべてハードウェアで試してみたい人のために、すべてのソースがGithubに投稿されています。

→ VivadoからGitを操作するためのVrapper

さらに、以下をインストールする必要があります。

→ Zyboを含むインターフェイスとDigilentボードの説明

→ 1つおよび2つ -7セグメントインジケーターに16進数を表示するための補助モジュール

→ PS2キーボードコントローラー

→ これらすべてが一緒に接続されているモジュール

モジュールをインストールするには、Githubからモジュールをダウンロードし、Vivadoの下からルートにある.tclファイルを実行する必要があります。