トリニティコンピューティング

それで、私は三元コンピューターの開発に関する一連の記事を続けます。 前回は、最も基本的な要素である3進(de-)マルチプレクサーに出会い、それに基づいて半加算器と全加算器を作成しました。 今回はメモリセルについてお話します。

前回の記事で、なぜそれが必要なのかを詳しく説明しました。これはデモ版の鉄です。 怠けないで、 私のモチベーションをチェックしてください。

そのため、ここにシリーズで公開されている記事のリストがあります(更新予定)。

- 3つまでカウント:回(3進マルチプレクサーと加算器)

- 3にカウント:2(メモリ)

- 3つに数えます:3つ(カウンター)

- 最大3つまでカウントします。4つ(1桁のコンピューターと3コマンドのコマンドシステム)

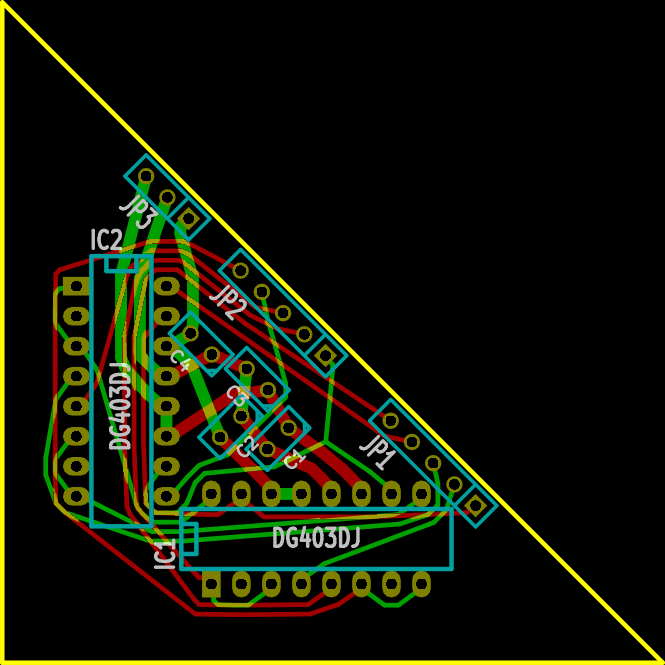

コンピューターの唯一の構成要素は3進マルチプレクサーであることを思い出してください。 こちらは、 アレクサンダーシャバルシンによるオリジナルのトリマックスデザインと私の表面実装の写真です。 そのようなボードの1つには、2つの3進(de)マルチプレクサが搭載されています。

表面実装用のTrimuxの私のバージョンは、「膝の上で」比較的簡単に再生できるように考案されました。ボードは、双方向ではありますが、ビアは12個しかありません。 ところで、フォーラムでnedopc.orgは、単一のビアなしでスルーインストールのオプションを実行しました。

ただし、チップの出力に穴を開ける必要があるため、私のオプションの方が経済的です:)

trimuxIO

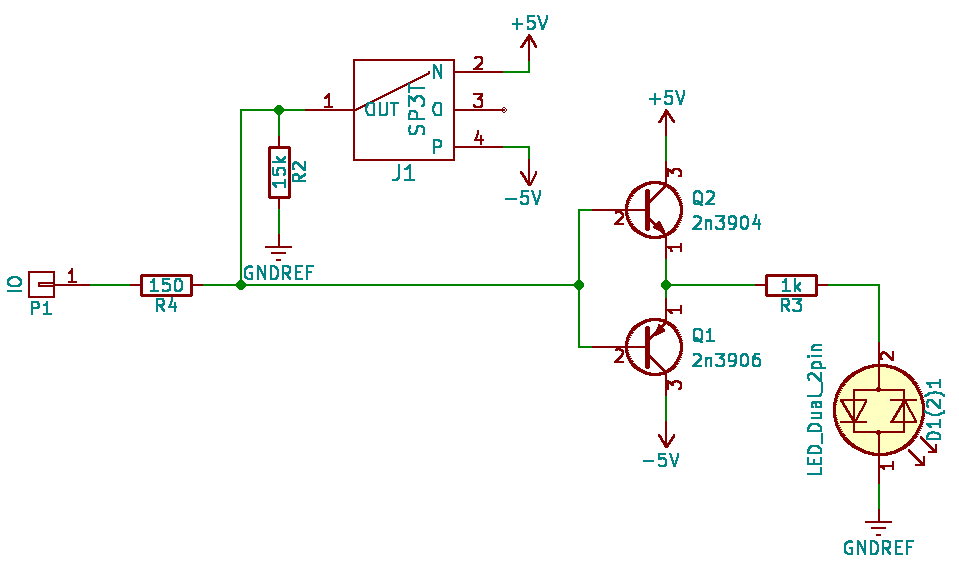

私の目標は理論化ではなく、完全に具体的な鉄片を構築することです。 現時点では、ブレッドボードモデルでテストする多数のマルチプレクサを取得しています。 前回、テストされた回路のすべての入力はブレッドボード上のジャンパーであり、出力は同じブレッドボード上のLEDのセットでした。 これはかなり不便です(特に入力を突くため)ので、1つの入出力のこの設計についてAlexanderで見ました。

各入力/出力には、単一の3ポジションスイッチがあり、デフォルトでは(中間ポジション)わずかに0Vにプルアップされています。 ピンがトリマックスの出力を示すために使用される場合、スイッチは中間位置のままにしておく必要があり、トリマックスは弱いプルを0Vに引き上げます。 エミッタリピータは、最も弱い信号でも信頼できる指標を提供します。

ピンを入力に使用する必要がある場合、スイッチを+ 5Vまたは-5Vに接続できます。 150オームの抵抗は、回路を短絡から保護します。

テストI / Oボードには、まったく同じ9つの回路があります。

このボードは、自宅で簡単に複製できるように設計されています。1層であり、1つのジャンパーは含まれていません。 そして、これは、たとえばスタティックメモリセルなどのテスト用にI / Oボードを接続する方法です。

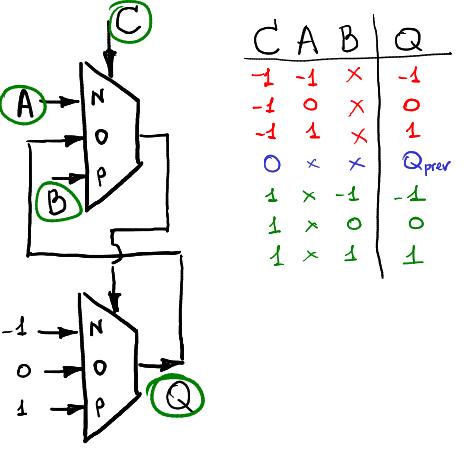

C、A、B、および1つの出力Qの3つの入力があります。

静的メモリセル(レベル記憶付きの3進トリガー)

次のように、2つのマルチプレクサーを接続します(1つのtrimuxショールに収まることを思い出してください)。

用語に同意しましょう:クロックトリガーは、 レベル制御とフロント駆動に分けられます 。 レベル制御について説明します 。つまり、クロック信号Cの1つのレベル(-1または1)では、トリガーは入力信号(それぞれAまたはB)を認識し、他のレベル(0)では認識せず、同じ位置に留まります。

回路は2つのマルチプレクサーで構成され、2番目のマルチプレクサーは単純に透過バッファーであり、1番目(クロック信号Cに応じて)はA、Bまたはバッファー出力を2番目のマルチプレクサーの入力に出力します! つまり、C = -1で出力Qは入力Aに閉じられ、C = 1で出力Qは入力Bに閉じられ、C = 0で出力Qは一定に保たれ、入力AとBは単に無視されます。 これはテキストが乱雑になる可能性があるため、次のビデオをご覧ください。

ダイナミックメモリセル:エッジ制御付きの3値トリガー

レベル制御とは対照的に、フロントを制御する場合、トリガーを切り替える許可は、クロック信号の差の瞬間にのみ与えられます。 残りの時間は、クロック信号のレベルに関係なく、トリガーは入力信号を認識せず、変更されません。

よく研究された地域への遠足

少しわかりやすくするために、バイナリ(brrr)の世界に少し移動してみましょう。 ロシア語の文献では、「トリガー」という言葉がそのようなすべてのスキームに適用されます(私を修正し、マスクを見つけました)。 レベル制御されたバイナリトリガーは、 ゲーテッドDラッチと呼ばれます。 大まかに言えば、D(データ)とE(有効)の2つの入力があります。 E = 1の場合、出力QはDのみであり、E = 0の場合、その値を保持します。

フリップフロップトリガーは、2つの通常のラッチ(ゲート付きDラッチ)と1つのインバータから構築できます。

この回路は、 マスタースレーブエッジトリガーDフリップフロップと呼ばれます。

三位一体の世界またはテラ(ほぼ)インコグニータに戻る

クロック信号のエッジに沿ってトリガーしたい場合は、次の図のように、バイナリの世界と同じように、2つの3値ラッチと1つのバイナリインバーターを使用できます。

ダイナミックメモリセルには、CとAmの2つの入力があります。 彼女には1つの出力Qがあります。 バイナリの世界では、インバータは、駆動ラッチをクロックする2番目の位相シフト信号を生成します。 3項スキームでは、クロック信号は2つに分割されます:min(C、0)およびmax(C、0)。それぞれが独自のラッチをクロックします。 信号Amが出力Qsに到達するには、信号Cの2つの連続した立ち上がりエッジが必要です。

回路をオンにした直後、信号Cがマイナス1から1にスイープする前に、出力信号Qsの値は不定であることに注意してください。 変数を初期化する:)

ところで、マスターとスレーブの両方のラッチには、使用されていない入力の1つがあることに注意してください。 これはメモリをすばやく初期化するために使用できますが、次回はさらに初期化します。

動的に制御されるメモリセルの関連するビデオ映像を次に示します。

おわりに

メモリセルの2つのオプションを検討しました。 動的制御を備えたメモリセルは、3次カウンタの主要な要素です。これについては、次に検討します。 次に、ALUなどについて説明します。 もちろん、この方法で1キロトリットのメモリを取得することは非常にコストのかかる(「膝の上で」行う場合)タスクですが、私の鉄片はデモンストレーションの目的のためであり、メモリがはるかに少ないため、これはそれほど怖くありません。

お楽しみください!