最初の部分へのリンク

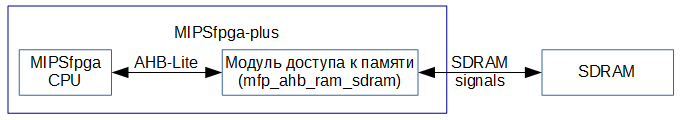

検討している構成は、次の要素で構成されています。

AHB-Liteバス

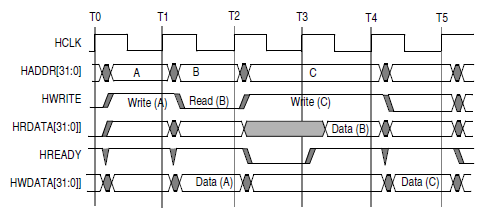

これは、MIPSfpgaコアを外部と通信するための主要なツールです。 そこから、情報の読み取りおよび書き込みの指示がSDRAMアクセスモジュールに受信され、読み取りおよび書き込みデータがそこを介して送信されます。 主な機能:後続のコマンドのアドレスフェーズは、現在のコマンドのデータフェーズと時間的に一致します。 これは、次の図で最もよくわかります。

表示される信号の簡単な説明:HCLK-クロック信号。 HADDR-次のフェーズで書き込みまたは読み取りを行うデータであるアドレスは、マスターによって設定されます。 HWRITE-次のフェーズの高レベルで、マスターによって設定された書き込み操作を実行する必要があります。 HRDATA-データの読み取り。 HREADY-現在の操作を完了するためのフラグ。 HWDATA-マスターによって設定された記録データ。 すべての信号と可能な組み合わせの説明を含むバスのドキュメントは、 MIPSfpgaパッケージに含まれています 。

SDRAM

SDRAMが構築される基本原則は、 Harris&Harris教科書の第5章[1]に非常に詳しく説明されています。 主な点に注意してください。

- コンデンサの充電の有無に関する情報は、1ビットを格納するために使用されます。

- メモリは、容量と制御ロジックのマトリックスの形式で編成されています。列と行があります。

- 読み取り操作中、セル(コンデンサ)の電荷は消費されますが、読み取り後は充電する必要があります。

- 非アクティブの間、蓄積された電荷の値も(よりゆっくりではあるが)減少します-メモリセルは定期的な再充電が必要です(いわゆる再生)。

Micron MT48LC64M8A2チップの例でさらに検討を続けます。 非常に便利で詳細なデータシートに加えて、同社はこのメモリチップでの作業をシミュレートするためのモデルをVerilogに提供しています。 これにより、開発が大幅に簡素化され、デバッグボードなしでシミュレータ内でMIPSfpgaを実行し、カーネルがSDRAMとどのように相互作用するかを確認できます。

メモリチップのブロック図を下図に示します。

主な要素:

- メモリのバンク(マトリックス)(4xバンクメモリアレイ)-ここに、関心のあるデータが保存されます。 このチップには4つのバンクがあり、各バンクには16ビットの8192行と1024列があります。 合計、合計チップ容量は4x8192x1024x16 = 512 Mb = 64 MBです。

- 制御デバイス(制御ロジック、バンク制御ロジック)-受信したコマンドのデコードと、他の要素への適切な制御信号の発行を提供します。

- アドレスバスのマルチプレクサ、ラッチ、デコーダー(行アドレスマルチプレクサ、4xバンク行アドレスラッチとデコーダー、列アドレスカウンター/ラッチ、列デコーダー)-異なるコマンドで受信した行、列、メモリバンクのアドレス情報のストレージを提供します。

- データバスのレジスタとロジック(データ出力レジスタ、データ入力レジスタ、I / Oゲーティング、dqmマスクロジック)-読み取りおよび書き込み操作用のデータ入力/出力を提供し、マスクを操作できるようにします(16ビットのうち、最も古いまたは最も古いもののみが必要です)バイト)、Z状態のデータバスの検出結果の変換を提供し、バスは双方向です。

運転条件

RAMを正しく動作させるには、いくつかの条件を満たす必要があります。 温度条件、周波数と電源の安定性、信号レベル(静的な規律)、ボード上の正しい配線の確保など、それらのいくつかは考慮しません。 私たちのビジョンの分野では、

- 1つまたは別のコマンドに対応する正しい制御信号を与える。

- 動的な規律の要件を満たしている( Harris&Harris教科書の第3章[1] )、 チップのドキュメントの要件を考慮[2] 。

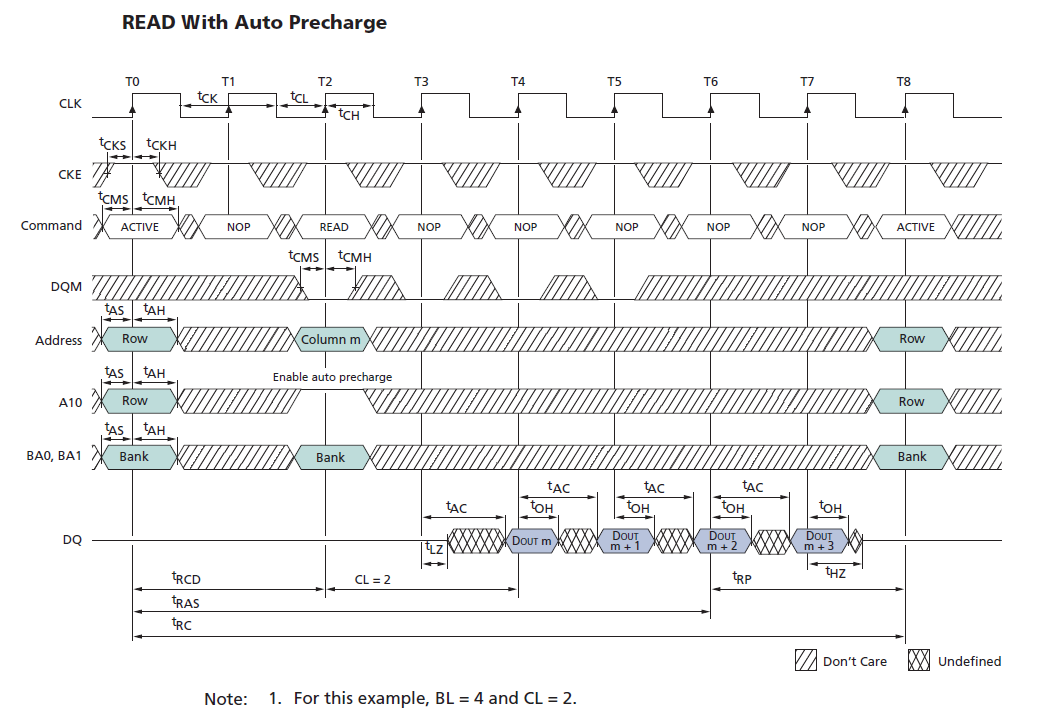

問題のあるものを客観的に理解するために、RAMからデータを読み取るときにメモリアクセスモジュールが何をすべきかを検討してください。 いわゆるの場合 自動プリチャージによる読み取り-読み取り操作後のマイクロ回路自体が、変更したセルの再充電を提供する場合。 モジュールの初期化(INIT)、書き込み操作(WRITE)、または自動再生成(AUTO_REFRESH)は同じ方法で実行されますが、実行されるコマンドと時間制限が異なります。

以下は、データシートからの抜粋です。コマンドの真理値表と、データを正しく読み取る方法を示すタイミングチャートです。

注:L-低レベル、H-高レベル、X-関係ありません、High-Z-高インピーダンス。

注:tCMS-コマンドのセットアップ時間、tCMH-コマンドのホールド時間、tAS-アドレスのセットアップ時間、tAH-アドレスのホールド時間、tRCD-アクティブな読み取りコマンド、tRAS-コマンド期間(ACTからPRE)、tRC-コマンド期間(ACTからACT)、tLZ-出力低インピーダンス時間、tAC-クロックからのアクセス時間、tOH-出力データ保持時間、tRP-コンマ期間(PREからACT)。 さまざまな条件のこれらおよびその他のパラメーターの最小値は、メモリチップのマニュアルに記載されています。

データを読み取るときのアクションのシーケンス(クロックごと)

T0。 CLKフロントの前のtCMSより前に、ACTIVEコマンドに対応するピンCS#、RAS#、CAS#、WE#、DQM(以降、コマンドと呼ぶ)に確立された信号が存在することを確認します。 示された信号は、CLKフロントの瞬間からtCMH中に状態を変更しないでください。 tCLKエッジの前のtASよりも前に、アドレスバスにラインアドレスを設定し(A [12:0])、メモリバンクアドレスバスにメモリバンクアドレスを設定します(BA [1:0])。 これらの信号は、CLKエッジ後のtAHの間安定している必要があります。

T1。 (tRCD-1クロック)中にNOPコマンドを与えます。 この時間間隔が経過した後、以前に送信されたラインアドレスは、対応するメモリバンクの行アドレスラッチおよびデコーダーに格納されることが保証され、8192ラインの1つが選択されます(チップ構造図を参照)。

T2。 CLKフロントの前のtCMSより前に、READコマンドの入力を確認し、tCMH中にCLKフロントの瞬間からコマンドを変更しないでください。 tCLKエッジの前のtASよりも前に、アドレスバスに列アドレスを設定し、メモリバンクアドレスバスにメモリバンクアドレスを設定します。 アドレスバスの10番目のビットは、読み取り後に自動プリチャージを実行する必要があることを示すために1に設定されます。

T3-T7。 NOPコマンドは、データが読み取られている間、ACTIVEコマンドが発行された時点から(tRC-1クロック)以上発行されていることを確認してください。

T4。 CLクロックサイクル(いわゆるCASレイテンシ、CAS)の後、読み取りデータはDQデータバスに存在することが保証されます。 より正確には、それらは後でバスに現れます(1サイクル+ tAC)-CAS = 2の場合。そして、それらはCLKフロント後少なくともtOHの間安定します。 この間、バスからデータを読み取る必要があります。

チップ内の相互作用を見ると、時間(1クロック+ tAC)の間、列アドレスは列アドレスカウンター/ラッチに保存され、対応する列デコーダーの出力でメモリバンク信号が設定され、必要な列の16ビットを選択し、このデータが送信されますデータ出力レジスタであり、最終的にはデータバス上にあります(DQ [15:0])。

T5-T7。 検討している例では、メモリチップがパケットサイズBL = 4(バースト長、LOAD MODE REGISTERコマンドで設定された他のパラメーターの中で、バーストモードを実行するように構成されていることを前提としています。現在のメモリアクセスモジュールの実装では、BL = 2として指定されています32ビットのデータを取得します)。 このため、次の3クロックサイクルにわたって、列アドレスカウンター/ラッチは自動的に1ずつ増加し、データバスの出力は別の3x16ビットを受け取ります。

図に示されているように、メジャーの数は必ずしも8に等しくないことに注意してください(T0-T7)-すべての制限時間(tRCD、tRCなど)の要件を満たすために、上方に増やす必要があります。

時間制約の要件は以下によって満たされます

- メモリアクセスモジュールが動作するクロック信号に対するメモリ(CLK)が動作するクロック信号の位相変位-短い間隔(tCMS、tCMH、tAS、tAH、tAC、tOH)

- 長い間隔(tRCD、tRC、tRP)で空のコマンド(NOP)を与える-遅延サイズが1クロックサイクルの幅を超える場合。 このために、対応する状態がモジュールの状態マシンの構成に導入されます。

クロック位相オフセット

クロック信号の位相シフトを決定する「科学的」アプローチと「試行錯誤」法を合理的に対比する優れたソース( [3]および[4] )がいくつかあります。 これらのドキュメントは、遅延値を置き換える必要がある「安全なウィンドウ」の境界を計算するための多くの公式を提供します。 その後、クロック信号をシフトして、それらのフロントがこれらの「ウィンドウ」の中心にできるだけ近くなるようにすることが提案されています。 説明した手法が機能することに同意し、同じアプローチのもう少し「怠yな」バージョンに注意を払いたいと思います(プレゼンテーションの12ページと20ページに描かれているようですが、それについてのコメントはないので、私はこれにいますわからない):

- 私たちはケージに2枚の紙/ストリップを取ります(グラフ用紙ができます);

- スケールを保ちながら、それぞれにいくつかのクロックサイクルを適用します。1つはfpga用で、もう1つはメモリチップ用です。

- スケールを観察して、それぞれについて注意します。

読み取り可能な入力信号が変化してはならない禁止ゾーン(A);

出力信号の値が定義されていないエリア。

出力信号が有効なゾーン(B)。 - 紙のストリップを平行に配置し、それらを相互に移動して(a-laスライドルール)、ゾーンAがゾーンBの中心にできるだけ近く、境界を越えないようにします。

- ルーラーを使用して、受信したクロックオフセットを測定し、スケールに従ってnsに変換します。

正確で安定した位相変位を確保するには、システムにPLLモジュールを含める必要があります。 通常、ハードウェアでメモリインタラクションをデバッグするときにロジックアナライザー(SignalTap)のクロック周波数として使用するために、他の3倍の周波数と小さな位相シフトを持つ3番目のクロック信号を追加します。

メモリアクセスモジュール

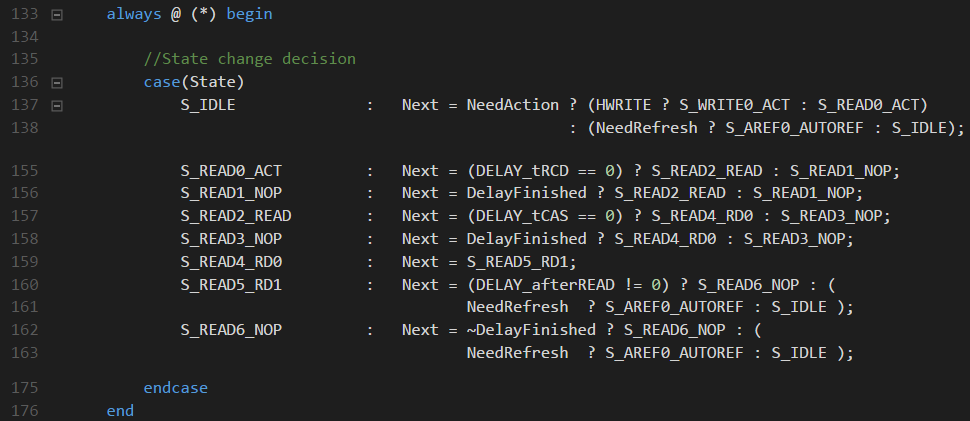

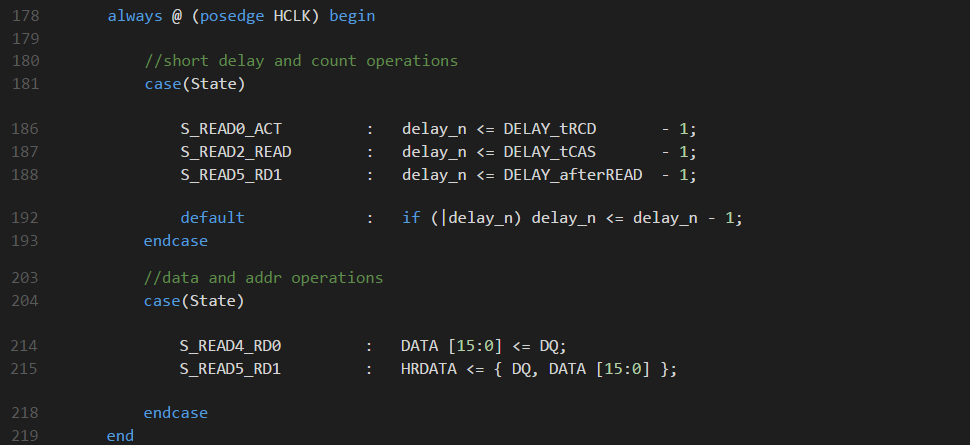

このセクションには、メモリアクセスモジュールのステートマシンの状態図と、データの読み取り手順を説明するモジュールコードの個々の行(ナビゲーションを簡素化するためのコードの行番号の表示)が含まれています。 モジュール全体のソースコード: mfp_ahb_ram_sdram.v 。 コードを使用してスクリーンショットを読むと不快になる場合は、記事のソースコードのフラグメント(コメントを含む)がgithubで複製されます。

読み取り手順を説明するステートマシンの状態は、自動プリチャージ付き読み取りの図の例で前述した内容と完全に一致しています。

これらの状態間の遷移の規則:

遅延が必要な場合、delay_nレジスタに入力されます。レジスタのゼロ値は、DelayFinishedフラグに対応します。 ステータスS_READ4_RD0およびS_READ4_RD1では、データはDQバスから読み取られます。

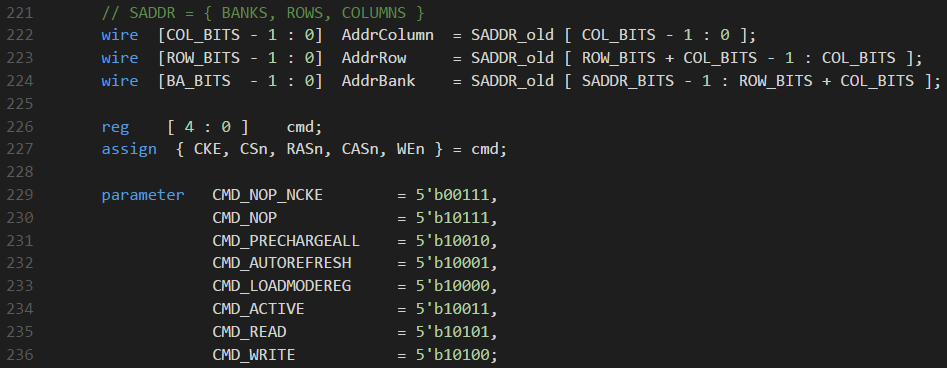

現在の状態に応じたエンコードコマンドとその出力:

すべての遅延は構成可能で、モジュールパラメーターで設定されます。これにより、クロック周波数が変更された場合に設定を変更するだけでなく、他のボードへの移植が簡単になります。

参照資料

[1] デビッドハリスとサラハリスの教科書「デジタル回路とコンピューターアーキテクチャ」

[2] Micron MT48LC64M8A2メモリチップのドキュメント。

[3] Quartusのドキュメント。 SDRAMコントローラコア(翻訳)

[4] SDRAM PLL Tuning(プレゼンテーション)

[5] ライアン・ドノヒュー。 デジタル論理回路の同期(プレゼンテーション)

[6] IS42S16320Dメモリチップのドキュメント

記事で参照されているすべてのデータシート、記事、プレゼンテーションはgithubで入手できます。