今週、 MIPSfpga-plusプロジェクトにSDRAMサポートを追加しました。 現在、 MIPSFpgaを使用する場合、 FPGAリソースによって制限されるブロックメモリに加えて、外部RAMも使用できます。

この記事は2つのパートで構成されています。

パート1. SDRAMアクセスモジュールの簡単な説明。 使用例。

パート2。以前にRAMチップを扱ったことのない人がモジュールを理解できるように、メモリの操作に関する詳細な説明。 参照資料

読者は少なくとも次のことが期待されます。

- Harris and Harris [1]の教科書の主題領域に精通している。

- C、アセンブラ、gccを使用したプログラミングの経験があります。

- MIPSfpgaの使用経験は最小限です。 そのような経験がなければ、より簡単なことから始めてから、システムでRAMを使用する方法について考えることは論理的です。

すでに経験豊富な開発者であれば、第1部は目を斜めに動かす価値があり、第2部には新しいものは含まれていません。 同時に、別のデバッグボードにSDRAMサポートを追加すると、コミュニティに間違いなくメリットをもたらすことができます。 現在、MIPSfpgaコアがMIPSfpga-plusプロジェクトの一部として移植された9つのボードの1つであるTerasic DE10-Liteにのみ実装されています。

一般的な情報

MIPSfpgaは、アカデミックライセンス(教育および研究プロジェクト用に無料ライセンス)で利用可能な産業用マイクロプロセッサコアMIPS microAptivです。 Yuri Panchulは、このカーネルのソースコードにアクセスする方法について詳しく説明しました 。

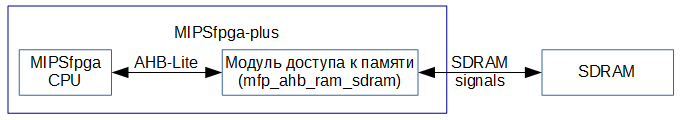

MIPSfpga-plusは、MIPSfpgaに基づくチップベースのシステム設計であり、コアに加えて、いくつかの追加の周辺機器バインディングが含まれています。 当初は、MIPSfpgaを操作する実験室での作業用に作成されましたが、システムの基礎として使用することを妨げるものはありません。 プロジェクトの主な「機能」の1つ:usb-uartコンバーター($ 5)を使用してプログラムをシステムのメモリに書き込む機能。これはBus Blaster($ 50)よりも手頃です。

システム構成

SDRAMアクセスモジュールの主要パラメーター( mfp_ahb_ram_sdram.v )

- 現在、16ビットデータバスを備えたチップのみがサポートされています-Terasic DE10-Liteのメモリはまさにこの容量です。

- 小さいモジュールサイズ(300行未満のコード);

- 作業に必要な最小限の操作セットを実装しました:INIT、READ、WRITE、AUTO_REF;

- モジュールはプロセッサ周波数(50 MHz)で動作し、同期またはクロックドメインの交差はありません。

- タイミングに関連するすべての設定はモジュールパラメーターで行われるため、他のボードへの転送が簡単になります。

- メモリへのページアクセスの最適化-なし。 バッチ操作(Burst Operation、AHB-Liteバス用語のWRAP4)は、一連の個別(SINGLE)操作として処理されます。

- シミュレーションモードで実行するには、MicronのVerilogモデルを使用しました 。

- ハードウェアでの正しい作業は、Terasic DE10-Liteボード(IS42S16320Dメモリチップ )で確認されています。

- 正確さを確認するために、MIPSfpga-plusで起動された別のCプログラム04_memtestが作成されました。 大きなアレイをメモリに書き込み、特定の頻度でこのアレイのデータの整合性をチェックし、LEDの現在のステージ、検証サイクルの数、7セグメントインジケーターのエラーの総数を表示します。

- 開発したモジュールのデバッグは、プロジェクトのフレームワーク内のMIPSfpga-plusコードから「分離して」利用できます。ahb_lite_sdramは、開発を開始したサンドボックスです。 テストベンチと、CPUなしでAHB-Liteマスターの動作をシミュレートするスタンドアロンモジュールがあります (ハードウェアテスト用)。 このプロジェクトは、他のボードへの移植を簡素化するために使用できます。

- SDRAMを使用する場合、MIPSfpga-plusで使用可能なCPUクロック控えめモードはサポートされていません(オプションMFP_USE_SLOW_CLOCK_AND_CLOCK_MUX)。

メモリテストの構成と実行の手順

MIPSfpgaおよびMIPSfpga-plusを既に展開およびコンパイルしていることを前提としています。 その場合、SDRAMを使用するには以下を行う必要があります。

- githubから最新のMIPSfpga-plusコードを入手してください。

- mfp_ahb_lite_matrix_config.vhで使用されるメモリのタイプを選択します

MFP_USE_BYTE_MEMORY-バイトストレージ付きブロックメモリ(x8);

MFP_USE_WORD_MEMORY-ワードストレージ付きブロックメモリ(x32);

MFP_USE_BUSY_MEMORY-動作の遅延をシミュレーションしたブロックメモリ。

MFP_USE_SDRAM_MEMORY-sdramメモリ。 - Programs \ 04_memtestディレクトリに移動します。

- main.cで適切な操作モードを選択します

シミュレーション

SDRAM_64M

SDRAM_8M - ファイル02_compile_and_link.batのモードとメモリ量に対応するスタックの境界を設定(選択)します。

シミュレーションモードの場合(SIMULATION)

- プログラムをビルドし、メモリを初期化するファイルを作成して、シミュレーションを実行します。

02_compile_and_link.bat

05_generate_verilog_readmemh_file.bat

06_simulate_with_modelsim.bat

ボードを使用する場合(SDRAM_64M、SDRAM_8M)

- fpgaで構成をビルドして入力します。

- ボード上でリセットを実行(押し)-リセット中に初期化されます。 sdramアクセスモジュール。

- プログラムをビルドし、ファームウェアをアップロードするためのファイルを作成し、ファームウェアをアップロードします。

02_compile_and_link.bat

08_generate_motorola_s_record_file.bat

12_upload_to_the_board_using_uart.bat - 動作中、LEDは検証の現在の段階を示します。

0-書き込みサイクル。

1-キャッシュフラッシュサイクル。

2-一時停止;

3-読み取りサイクル。

4-すべてのチェックが完了し、エラーはありません。

5-チェック中にエラーが検出されました。 - 操作中、7セグメントインジケーター(de10-liteには6個あります)は以下を示します。

2つの上位ビット-チェック番号。

最下位4ビット-検出された読み取りエラーの数。

他にできること

私の目標は、可能な限りシンプルで、透明で、他のボードに簡単に移植できるソリューションを作成することでした。 このモジュールは、「大人」のものに比べてやや原始的です。これにより、近代化と生産性の向上の余地が残されます。

- CPU周波数(50 MHz)と比較して、2倍の周波数(100 MHz)でメモリ動作を確保します。

- チップで利用可能な最大周波数でメモリ動作を確保するために、クロックドメインの交差を追加します。

- 異なる容量のメモリを操作する機能を提供します。

- ページメモリアクセス用にモジュールを最適化します。

- メモリ使用量に基づいて最適なAUTO_REFトリガー戦略を選択します。

バグ修正と新機能を備えたプルクエストに感謝します。

謝辞

著者は教科書のデビッド・ハリスとサラ・ハリスの「デジタル回路とコンピューター・アーキテクチャー」 、イマジネーション・テクノロジーズの会社、そして個人的にはユーリ・パンチョル・ユーリパンチュルの翻訳者のチームに感謝しています。