最近、私は自分のプロジェクトのために1Uのケースを見つける必要がありました。 そして、新しいデバイスに代わるものとして、 1U形式の古いデバイスを探し、中身を捨て、ケースをその目的に使用することにしました。 しかし、ケースを開けて、私はうれしく驚きました! アルテラの最大4つのFPGAと5ボルト。 私は抵抗することができなかったので、彼らのうちの1人はビジネスに挑戦しません!

はんだ付けステーションがなく、LUT技術を練習していません。 そのため、250度の建設用乾燥機を使用して、ボードからFPGAチップを突き出しました。 私もそのようなケース用のアダプターボードを持っていなかったので、通常のブレッドボードを取り、ラックをそれにはんだ付けし、 ラップとはんだ付けを使用して、マイクロ回路ピンをラックに接続しました。 彼はJTAGコネクタと電源を引き出し、発電機をねじ込みました。 チップを使い始めるのに必要なのはそれだけです。

このような小さなFPGAで何ができますか? 無線アマチュアは、このような問題を非常に簡単に解決します。理解できない状況では、送信機を作ります! 何から? はい、現時点で手に入れたものすべてから! そして今日、 アルテラEPM7064があります。

アルテラEPM7064の何が問題になっていますか?

彼女は大丈夫です! このチップの大きな利点は、5ボルトの動作電圧です。 これは、電源に問題がないことを意味します。古いTTLロジック(ZX Spectrumなどの古いコンピューターまたは個別のTTLチップ上のロジック回路)に接続するときに、レベルを調整する必要はありません。

このFPGAは、構成を内蔵の不揮発性メモリにも保存します。 外部フラッシュメモリチップは不要です。

ただし、そのボリュームは大きすぎず、64セルのみです。 これはそれほどではありません。 FPGAラティスのプロジェクトでは、なんとか時計を組み立てることができました。 64個のセルもありました。 興味深いことに、同じHDL回路が同じボリュームのFPGAに適合するのは、アルテラだけですか?

送信機を作る

実際、送信機の作成は非常に簡単です! 特定の周波数のジェネレーターを取り出してアンテナに接続するだけで十分です(マッチング、通信回線の波動インピーダンス、アンテナの共振周波数については説明しません)。 その後、この周波数と変調用の受信機があれば、信号を受信できます。 近距離では、マイクロコントローラを備えた従来のボードからでも、受信機でクロックを受信できます。

特定の周波数でトランスミッタージェネレーターをオンにするだけでは、有用な情報は送信されません。 したがって、トランスミッタ信号は何らかの方法で変調する必要があります。 変調には多くの種類があります。

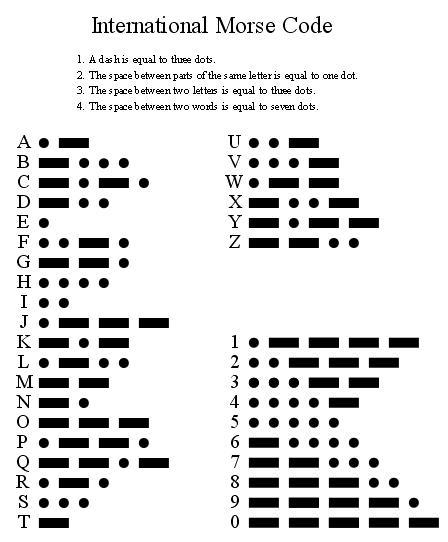

アマチュア無線の練習では、通信の最も簡単な形式は電信(CW)です。 電信は多くの点でユニークなコミュニケーション形式です。 一方では、それはコミュニケーションのデジタル形式、さらにはコミュニケーションの最初のデジタル形式であると考えることができます。 一方、訓練を受けた人はこのデジタル信号を耳でデコードできます。 現在、このためのデコーダプログラムがあります。 しかし、人間の耳は依然として受信のための最も正確なツールと考えられています。 別の電信は、最も「長距離」タイプの通信の1つです。 単一周波数での伝送速度と低い伝送速度により、すべての信号エネルギーは単一周波数に集中し、これは伝送範囲にプラスの影響を与えます。 受信には、狭帯域フィルターを使用できます。 電信信号はドットとダッシュで構成されています。 各電信アルファベット記号は、ドットとダッシュの組み合わせです。 最も一般的に使用される文字は、より少ない要素で構成されています。

ドットとダッシュは、送信機を有効にする事実です。 ドットとダッシュの間の間隔では、送信機がオフになり、信号は空中に送信されません。 ダッシュが3ポイントに等しい期間を持たなければならないという規則があります。 1文字のドットまたはダッシュの間隔は、1ポイントの期間と等しくなければなりません。 1つの単語の文字間のギャップは3ポイントに等しくなければなりません。 また、単語の間には、少なくとも7ポイントの休止が必要です。

FPGAのピンに(アンテナとして)短いワイヤを接続し、このピンにクロック信号を送ると、この信号を変調されていない搬送周波数として受信できます。 アンテナへの信号出力を有効または無効にすることにより、搬送波を変調します。 そして、ドットとダッシュの正しい時間間隔を形成して、電信無線信号を形成します。

電信信号生成

秒単位で時間間隔を形成するには、クロック信号を分割する必要があります。 私の場合、クロック周波数は25175000 Hzです。 私は23ビットのバイナリカウンターを使用することにしました。 結果として得られる頻度は次と等しくなります。

カウンター2 ^ 22 = 4194304

クロック周波数25175000 Hz

最終周波数25175000/4194304 = 6 Hz

ある時点で間隔を形成すれば十分です。

次に、非常に単純なものを作成してみましょう。 たとえば、SOS信号:3つのドット、3つのダッシュ、3つのドット。 タイムチャートを描く:

それから、30の手順が必要であることがわかります。 これは5ビットです。 つまり、カウンターの22ビットに、さらに5ビットを追加します。 そして、27ビットを取得します。

これで、ロジックは非常にシンプルになりました(複雑なロジックをこのような小さなFPGAに配置できないため)。カウンター値が0、2、4、8、9、10(図のさらに下)の場合、1を返します。 この信号(CW)は既にFPGAから出力され、たとえばLEDで制御できます。 また、無線信号を変調するには、信号CWの値が1に等しい場合にのみ、クロックジェネレータの信号を出力に出力します。

module epm7064_test(clk, out_lf, out_rf); input wire clk; output wire out_lf; output wire out_rf; reg [27:0] cnt; initial cnt <= 28'd0; always @(posedge clk) cnt <= cnt + 1'b1; wire [4:0] hi_bits = cnt[26:26-4]; // 5 wire cw = (hi_bits == 5'd0) || (hi_bits == 5'd2) || (hi_bits == 5'd4) || (hi_bits == 5'd8) || (hi_bits == 5'd9) || (hi_bits == 5'd10) || (hi_bits == 5'd12) || (hi_bits == 5'd13) || (hi_bits == 5'd14) || (hi_bits == 5'd16) || (hi_bits == 5'd17) || (hi_bits == 5'd18) || (hi_bits == 5'd22) || (hi_bits == 5'd24) || (hi_bits == 5'd26); assign out_lf = cw; assign out_rf = cw & clk; endmodule

それだけです、それは受信機をオンにする時間です

送信機から信号を受信する

残念ながら、送信機の放送受信機は私たちには適していません。 第一に、周波数範囲のために、そのような周波数は単に放送受信機にない場合があります。 第二に、変調のタイプが原因です。 ブロードキャストレシーバーは振幅変調(AM)で受信するため、電信信号がない場合、レシーバーはブロードキャストノイズを受信し、キャリアがある場合、レシーバーから無音が生じます(キャリアは振幅で変調されないため)。 その結果、AMレシーバーは、ポイントとダッシュでの無音によりノイズを中断します。

どのような受信機が必要ですか? 電信を受信するには、 シングルバンド受信機が必要です。 正直に言って、少しだまされた頻度を選択します。 USBレシーバーの受信下限は24 MHzであるため、このレシーバーで信号を受信できるという事実を考慮して、ジェネレーターの周波数を選択しました。 このような受信機は、約500ルーブルでebay / aliexpressで購入できます。 単語R820T2で検索します。 受信プログラムとして、SDRSharpを使用しています。

AM受信機で受信するために送信機を変更する

少し考えた後、中波受信機があることを思い出しました。 受信周波数は530〜1600 kHzです。 変調は振幅です。 ほとんどの場合、この範囲の受信機はほぼすべてのカーラジオに搭載されています。 そして私たちは息子とデザイナーからそのような受信機を集めました。

この受信機の周波数範囲でキャリア周波数を取得するには、クロック周波数を分周する必要があります。 カウンターから個々のビットを取得する場合、クロック値を2の累乗で除算した値を取得します。 たとえば、4番目のビット-これは16による除算と結果-1573 KHz、5番目のビットと786 KHzの周波数を選択しました(中国の可変コンデンサーはわずかに欠陥があり、周波数範囲全体をカバーしていないため)。

次に、信号の振幅変調を生成する必要があります。 私たちにとっては簡単です-電信信号があるので、搬送波周波数を音の周波数で中断するのに十分です。 100%変調します。 AM受信機で受信する場合(受信機の振幅検出器の動作用)、これで十分です。 カウンター分周器の周波数から適切なビットを選択します。 これは14番目のビットで、16384で割ることに相当します。結果は1536 Hzの周波数です。 この周波数は、人間の可聴範囲内であり、AMレシーバーが出力できる周波数範囲内です。

Verilogコードには少し調整が必要です。

wire audio = cnt[13]; // 14 - 1536 - wire rf = cnt[ 4]; // 5 - ~786 R - assign out_rf = cw & rf & audio;

そして、電信の振幅を得ました。

おわりに

私たちが使用したプロジェクトでは、FPGA Altera EPM7064、Quartus II 11.1、中国人プログラマー。 占有セルの数は64のうち30です。 そしてこれは、長いテキストを転送するためにプロジェクトを複雑にすることができることを意味します。

→ GitHub

フランケンシュタインについて心配する必要はありません。すぐに友人にFPGAを提供します。彼はまともなプリント基板を彼女に提供します。

明日の朝、フランキーの冒険の続きが待っています!