ADCをパラレルバスに接続するという古典的なタスクを見てみましょう。

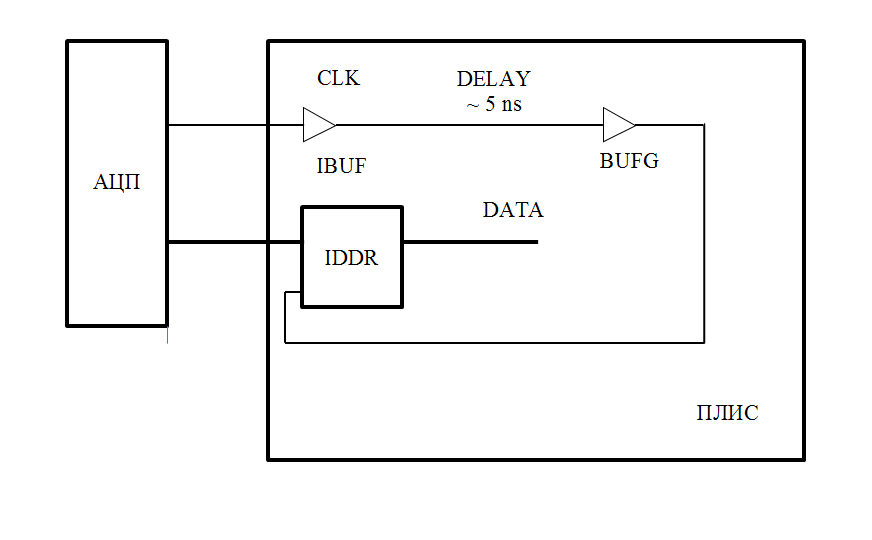

一般に、接続図は次のようになります。

ADCデータバスはFPGAピンに行き、I / Oブロック内に直接DDRトリガーまたはデシリアライザがあり、データはパラレルバスを介してFIFOに行きます。 問題は、クロック信号の通過です。 グローバルバッファを使用する場合、バッファへの信号の伝播時間は5 nsになります。 これはたくさんあります。 これは、簡単に200〜500 MHzのクロック周波数の周期に匹敵します。

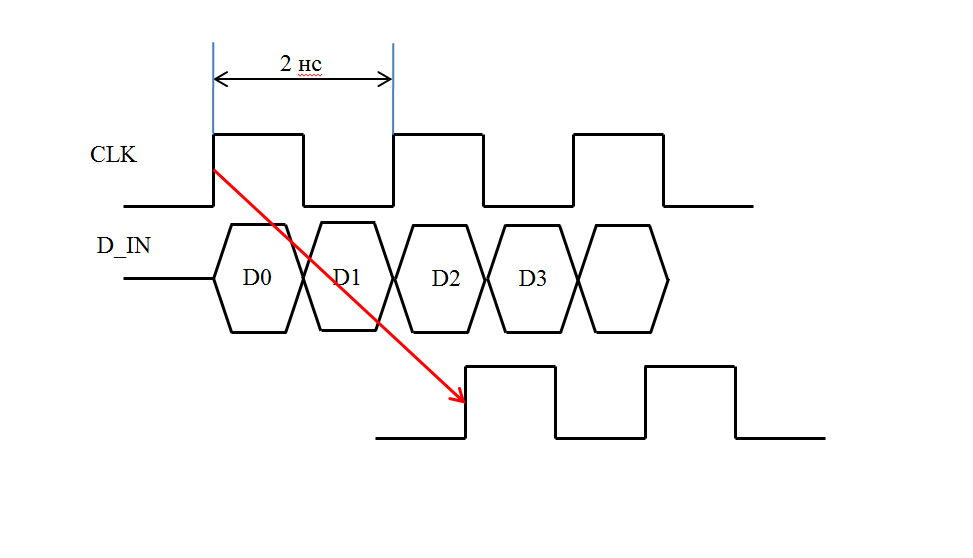

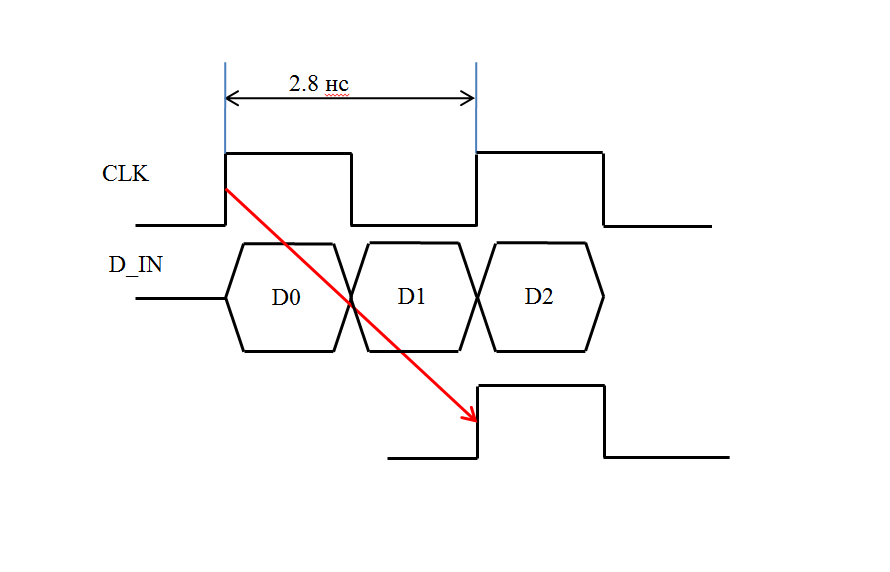

なぜこれが悪いのか一言。 一般に、ADCは特定の周波数範囲で動作する必要があります。 たとえば、500 MHzのクロック周波数でタクト2.8 nsの遅延がある状況を考えます。

一見、すべてが問題なく、ADCデータは完全にスナップします。 しかし、周波数が357 MHzに低下するとどうなりますか、それは正確に2.8 nsですか?

データは前面に向かって流れ、データに歪みが生じます。 頻度がさらに減少すると、ズームは消え、データは再び正確になります。

問題を解決する2つの古典的な方法があります。

1. IOBブロックに遅延要素があり、遅延を2.4 nsに設定できます。 ほとんどの場合、これで十分です。

2.特別な要素bufioがあり、それらを介してクロック周波数のパスがはるかに短くなります。

残念ながら、これだけでは十分ではありません。 特に大規模FPGAの場合、遅延は2.4 nsを超えることがあります。 また、常にクロック信号がbufio出力に接続されているわけではありません。

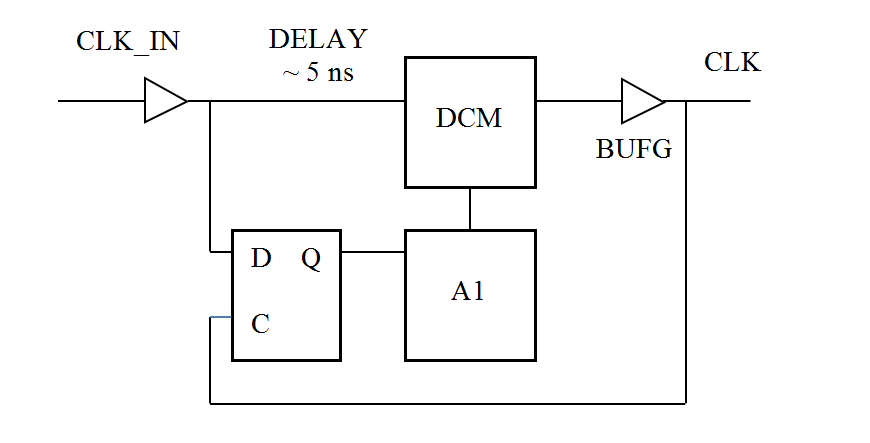

この問題にはシンプルでエレガントな解決策があります。 これを行うには、内部クロック信号の位相がADCクロック信号の位相と常に正確に一致するようにするだけで十分です。 FPGA内に存在するDCM、MMCM、またはPLLノードは、位相をスムーズに変更できます。 ただし、センサーはIOBブロック内でDトリガーとして機能できます。 配線図は次のとおりです。

入力クロック信号はIOBを通過してDCM入力に入り、同時にDトリガー入力に入ります。 DCMの後、信号はDフリップフロップのクロック入力に送られ、同じ信号がADCデータバストリガーに送られます。 そして、ここで何が起こるか、いくつかの状況を考えてみましょう:

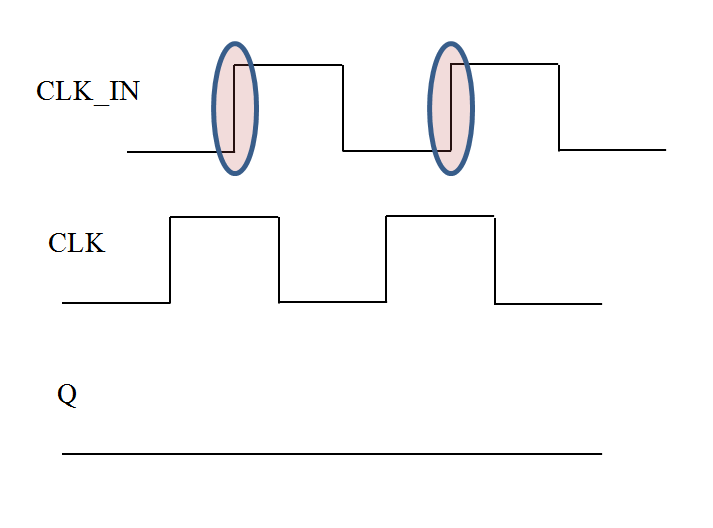

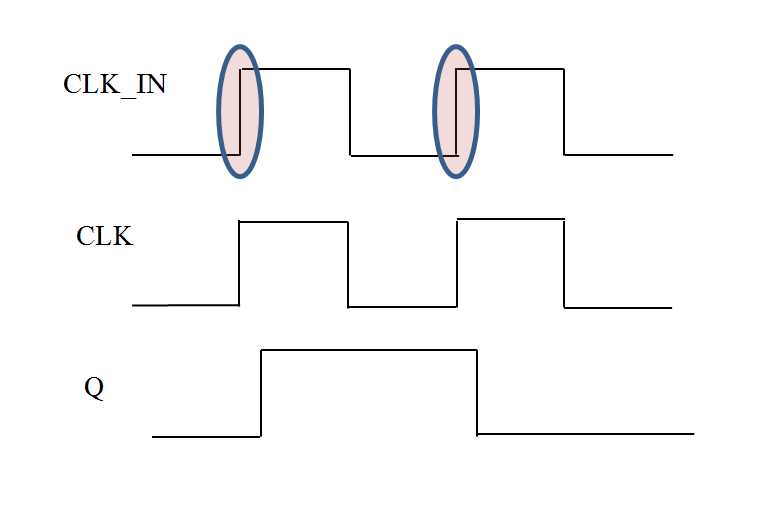

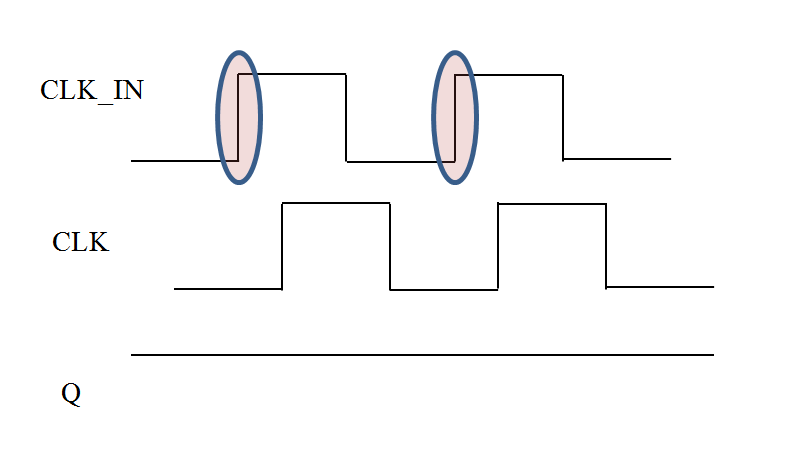

状況1-グローバル信号の前面は、入力信号の前面の左側です。 トリガー出力はゼロです。

状況2-ジッターゾーンのグローバル信号の前。 出力はランダムシーケンスです。 これはまさにジッタの非常に有用な特性です。 ランダムシーケンスの出現の事実は、クロック周波数のチューニングの事実を決定できます。

状況3-グローバル信号の前面が入力信号の右側にあります。 出力は単位です。

これらの状況はすべて、ステートマシンで簡単に処理できます。 私の実装では、1024サイクル中に累積サイクルがあり、カウントが1実行されます。カウンター値が576より大きい場合、左への位相シフトが実行されます。 カウンター値が448未満の場合、右への位相シフトが発生します。

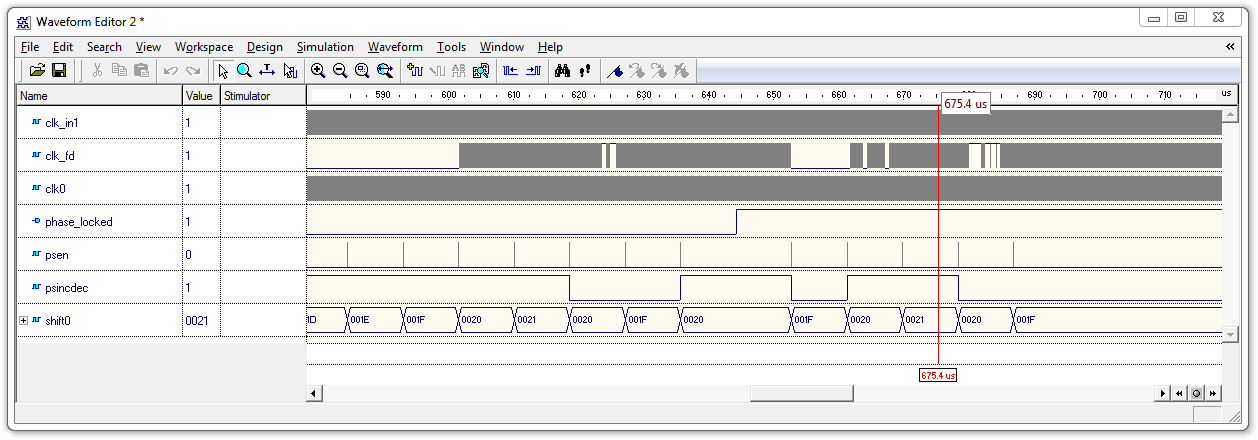

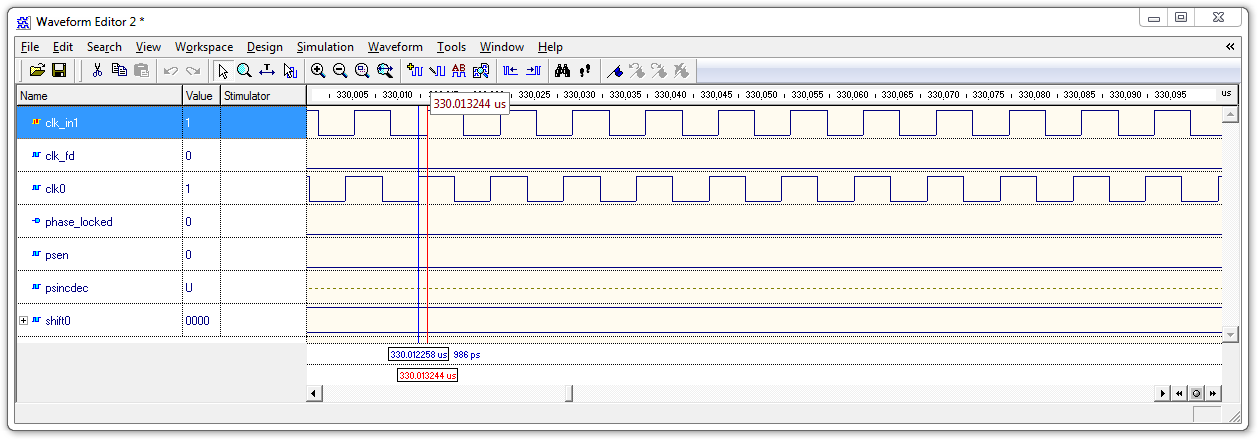

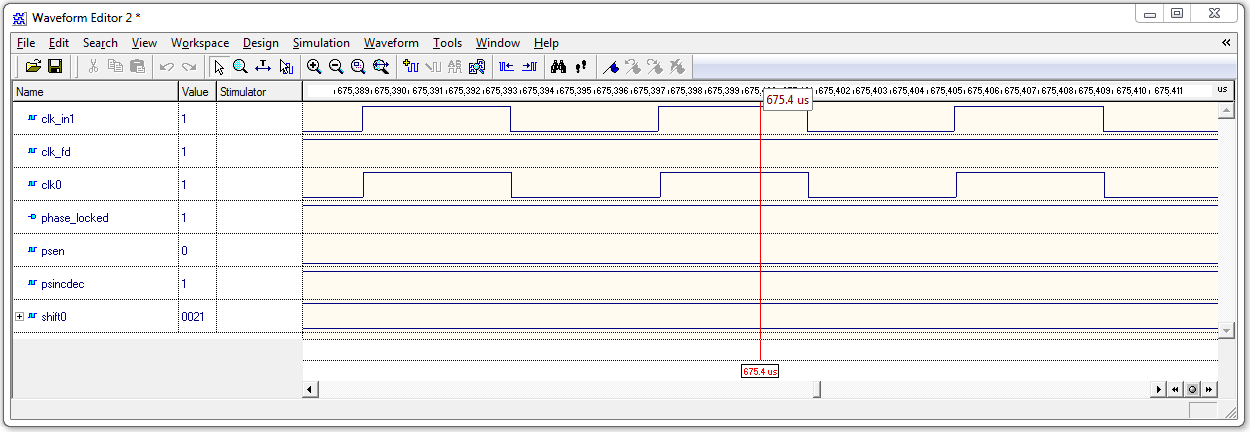

この図は、コンポーネントのモデリングの結果を示しています。

clk_in1信号は入力クロック周波数です

clk0-調整された周波数

clk_fd-位相検出器

信号phase_locked = 1は、位相調整が達成されたことを意味します。

psen-DCM位相シフト

psincdec-位相シフト方向

shift0-位相カウンターの現在の値

調整後、小さな振動プロセス、つまり同じ値内のシフトがあることがわかります。 定常状態の実際のシステムでは、1つまたは2つのサンプル内で位相変化も観察されます。 調整を開始する前は、次のようでした。

周波数間に大きなバイアスがあることがわかります。 そして、このようにチューニングした後:

周波数は同じです。

»既製のコンポーネントがGitHubに表示されます :

2つのコンポーネントをレイアウトしました。

ctrl_dcm_phase_v6 –DCMは内部でインストールされます。 これは、FPGA Spartan 3、Virtex 4、Virtex 5用です。

ctrl_dcm_phase_v8-外部DCMまたはMMCM、これはVirtex 6、Kintex 7用です。

モデリングに関するいくつかの言葉。 ランダムプロセスに基づいているため、これによりいくつかの問題が発生します。 しかし、それらは解決可能です。 コンポーネントmodel_line_v1はスタンドで使用され、クロック信号にジッタを形成します。 ジッタを形成するには、math_realライブラリのUNIFORM関数が使用されます。

結論として、これらのコンポーネントは多くのプロジェクトで使用されていることに注意してください。 そして、彼らは私たちを大いに助けてくれます。