面白い? 行こう...

TCLとは何ですか?

TCL(Tool Command Language)は、さまざまなタスクを実行するための高レベルのスクリプト言語です。 多くの場合、TCLはTkグラフィカルシェル(ツールキット)と組み合わせて使用されますが、この記事ではこの側面は考慮されません。 この言語は、プロセス自動化のさまざまなタスクで広く使用されています。

- 複雑なモジュール、ノード、コードパーツのテスト。

- スピードプロトタイピング

- コンソールアプリケーションのグラフィカルインターフェイスの作成。

- アプリケーションアプリケーションおよびタスクでの実装。

何らかの方法で、TCLの主な機能はルーチンタスクの自動 化と、開発に費やされる時間の大幅な削減です。 TCLプログラムは、 コンパイルとコンパイルを必要としません。これにより、スクリプトをデバッグするタスクが簡単かつ簡単になります。 TCLインタープリターは無料ライセンスで配布され、ほぼすべてのプラットフォームで使用できます(多くのLinuxディストリビューションでは、デフォルトで使用可能です)。 これは、プライベートプログラムやプロプライエタリアプリケーションの開発に制限なく使用できることを意味します。 執筆時点では、TCLの現在のバージョンは8.6です。 MyTcl、TclKit、ActiveTclなど、 TCLスクリプトの操作、デバッグ、視覚化に多くのディストリビューションを利用できます。 1 ActiveTclライセンスの価格は約1,500ドルで、商用アプリケーションの開発には不当です。 個人的な慣習から、ほとんどの開発者は使い慣れたコマンドラインを使用しています。

すべてのTCLプログラムは、 「;」で区切られたコマンドで構成されています または改行文字。 他の多くのプログラミング言語と同様に、最初の単語はコマンドであり、残りの単語はコマンドの引数です。

コマンドarg1 argt2 ... argN

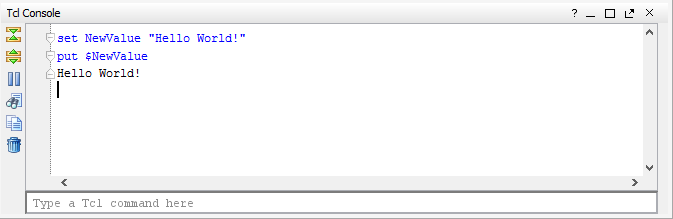

例:

set NewValue “Hello World!” puts $NewValue

最初のコマンドはNewValue変数を作成し、2番目のコマンドは変数の値をコンソールに出力します。 スペース付きの変数を使用するには、引用符を使用します。 その他の場合、それらは必要ありません。 コマンドの実行結果は、次の図に示されています。

私の意見では、TCLの主な利便性は、コマンドに対する引数を別のコマンドに置き換えることができることです。 これを行うには、角括弧内に配置する必要があります。 以下の例では、この機能を示します。 とりわけ、TCLはさまざまなイベントに基づいてプログラムの動作を制御できます。 つまり、コマンドハンドラーは、スクリプトに記録された条件だけでなく、さまざまな外部イベント(外部ファイル内の変数の値の変更、チャネル内のデータのキャプチャ、アプリケーションの終了、特定の値のタイマーカウンターへの到達、およびなど)。 TCL言語には一連のコマンドが豊富で、データ配列や正規表現を操作する非常に便利な手段が含まれています。 TCLでは、関数とプロシージャを作成する機能が実装されており、条件ごとのループと式の説明が利用できるため、コードの作成が非常に容易になります。

なぜTCLが必要なのですか?

ほとんどすべてのFPGA / ASIC開発者は、遅かれ早かれプロジェクトでTCLに遭遇します。 最新のFPGA開発では、TCLスクリプトが自動化およびプロセス統合タスクに積極的に使用されています。 TCLは、 アルテラの Quartus 、 ザイリンクスの ISE Design Suite 、 Vivadoのすべての主要なCAD FPGAに含まれています。 TCLを実行できるのはなぜですか?

- プロジェクトの作成(ソースファイルの追加、オプションの設定、設計階層、トップレベルファイルの割り当てなど)、

- 合成とトレース(異なる設定で独立したステージを作成するまで)、

- 完成したノード、個々のモジュール、プロジェクト全体のテスト、

- テンプレートに基づく制限ファイル(UCF / XCI)の自動生成、

- 合成およびトレースされたプロジェクトの時間制約を確認します。

- FPGA回路、コンポーネント、およびプリミティブのパラメーターの設定、IPコアのオプションの設定、

など

これらのすべての段階は、VHDL / Verilog言語でのノード動作のモデルの作成から、合成およびトレース段階でのCADでの完成したプロジェクトのデバッグまで、FPGAでの開発プロセスの基本的な操作です。 通常、複雑なプロジェクトには、さまざまな開発者が作成した多数のモジュール、いくつかのIPコア、制限ファイル、ライブラリ、および機能パッケージが含まれます。 その結果、完成したプロジェクトには、特定の階層構造と、特定のモジュールを必要なプロジェクトノードに接続するための一連のルールがあります。 開発者にとって、デバッグモジュールがどこでどのように配置されるべきか、作業で使用する場合に実行する機能に関する知識を覚えておくのは困難ですが、開発段階では作業の知識は必要ありません(いわゆる「 ブラックボックス 」モジュール)。 TCLスクリプトは、プロジェクト構造を管理し、事前に準備されたテンプレートに従って必要なノードをリンクします。 これにより、開発の柔軟性が提供され、あるプロジェクトから別のプロジェクトに移行するときに、完全なノードの再現性が可能になります。

原則として、FPGA用の新しいノードを作成する段階と同時に、これらのノードをプロジェクトとは別に、完成したシステムと一緒にデバッグする段階が進みます。 一次シミュレーションは、専用のCADシステムとシミュレーション環境のコンピューター上のFPGAから抽象化されて実行されます。これらはModelsim、ISim、Aldec Active-HDLなどです。 プロジェクトをデバッグするタスクを実装するために、TCLスクリプトも役立ちます。これにより、モデリング中に発生するイベントを処理し、モデルの結果に基づいて決定を下すことができます。 純粋にHDL言語でRTLノードをデバッグする場合、回路の動作を変更するとモデルとテストスイートを変更する必要があるため、モデルの作成が困難になる場合があります。 HDL言語とTCLスクリプトで多数のモデルを使用することは非常に便利であり、多くのソリューションでは、デバッグプロセスを高速化し、複雑なテストを統合できます。

コードの記述とデバッグの段階の後に、FPGAチップでプロジェクトを合成、配置、トレースする通常の手順が続きます。 おそらくこれは最も困難なステップの1つであり、ワークステーションの大きなコンピューティングリソースと完了までに長い実行時間が必要です。 TCLスクリプトを使用すると、各段階で実行イベントを管理し、特定の計算結果を分析して、プロジェクトの最適な配線とトレース特性(使用されるリソースの量、最大クロック周波数、タイミングの許容レイテンシ値など)を達成できます。 さらに、TCLを使用すると、FPGAファームウェアファイルを作成するときに、設定の選択と変更、検証ステージの再起動、特定のステージの再起動のためのルーチンアクションを除外できます。 このような設計の自動化により、これらの段階で人が常に存在することが完全になくなります。

これらの行を読んだ後、TCLがプロジェクトで絶対に使用する必要がある便利で強力なものであることを既に確信していることを願っています。 以下では、Vivado環境でプロジェクトを作成するためにチームが使用する便利なスクリプトの1つを分析し、既に書き込まれたソースファイル、あらゆる種類のIPカーネル、XCI制限ファイルなどを追加します。

FPGAをTCL!

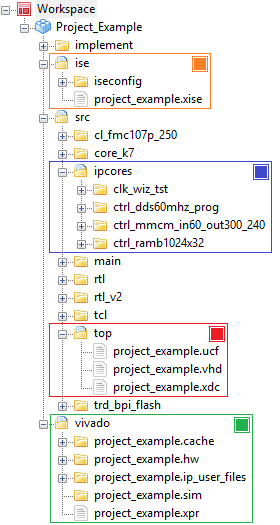

FPGAでプロジェクトを自動的に作成するための最も単純なTCLスクリプトの1つを検討してください。 次の図に示すように、準備手順はごくわずかです。ローカルマシンには、プロジェクトのソースコードを含むディレクトリが必要です。

便宜上、FPGAファミリで許可されている場合( シリーズ7:Artix、Kintex、Virtex )、 ザイリンクスISE Design SuiteおよびVivadoで作成されたプロジェクトに独立したカタログを使用します。 ソースファイルは/ srcディレクトリにあり、 vivadoプロジェクトは同じ名前のディレクトリにあり、ISE環境のプロジェクトは/ iseディレクトリに作成されますが、合成および配線の結果は/ implementディレクトリに保存されます。 これはすべて、プロジェクト全体の管理の便宜と、異なる環境での独立した管理のために行われます。 また、階層がより視覚的になり、ソース内の大量のジャンクファイルからあなたを救います。 最上位ファイルと必要な制限ファイルがあるソースディレクトリの/ topディレクトリに個別に注意する必要があります(ISEの場合は* .ucfファイル、Vivadoの場合は* .xdcファイル)。

プロジェクトには、ISEで作成された古いIPコアとVivadoで作成された新しいIPコアが混在しています 。 core_k7ディレクトリには、ISE用のCoreGeneratorで作成されたすべてのカーネルが含まれています。 これらは、Vivadoプロジェクトで使用した場合、再生成または更新されません(* .vhdファイルはモデリングに使用され、* .ngcファイルは合成に使用され、* .xcoファイルはVivadoプロジェクトに追加されません)。 / ipcoresディレクトリには、Vivado環境で直接作成された* .xci形式の新しいカーネルが含まれています。 各コアには個別のサブディレクトリが必要です。そうでない場合、プロジェクトのIPコアには「 LOCKED 」属性が設定されるため、カーネルを更新して合成用に再生成することはできません。

TCLスクリプトの説明に移りましょう。

# Stage 1: Specify project settings set TclPath [file dirname [file normalize [info script]]] set NewLoc [string range $TclPath 0 [string last / $TclPath]-5] set PartDev "xc7k325tffg900-2" set PrjDir [string range $TclPath 0 [string last / $NewLoc]] set TopName [string range $NewLoc [string last / $NewLoc]+1 end]

最初の行は、ローカルマシン( src / tclディレクトリにある)でTCLスクリプトの場所を探し、ファイルへのフルパスを持つ文字列変数を作成します。

2行目は、パスの一部が切り取られる追加の変数を作成します。 次の変数がプロジェクトへのパスと最上位ファイルの名前を手動で指定しないように、両方の変数が必要です。

変数PartDevには、FPGAチップの名前が含まれています。 そして、これはプロジェクトで変更される唯一の変数です! スクリプトの他のすべての行は、どのプロジェクトでも変更されません。

# Stage 2: Auto-complete part for path set PrjName $TopName.xpr set SrcDir $PrjDir/$TopName/src set VivNm "vivado" set VivDir $PrjDir/$TopName/$VivNm cd $PrjDir/$TopName pwd if {[file exists $VivNm] == 1} { file delete -force $VivNm } file mkdir $VivNm cd $VivDir

次の段階で、ソースファイルの場所を決定する追加の変数が作成されます。そうでない場合は、vivadoディレクトリを作成します。 ローカルマシン上のvivadoディレクトリの存在を確認していることに注意してください。 ディレクトリが存在する場合は、新しいプロジェクトで競合が発生しないように、ディレクトリが削除されて再作成されます。

cdコマンドは作業ディレクトリを変更し、pwdコマンドは作業ディレクトリの場所を表示します。

# Stage 3: Find sources: *.vhd, *.ngc *.xci *.xco *.xdc etc. # This stage used instead of: add_files -scan_for_includes $SrcDir set SrcVHD [findFiles $SrcDir "*.vhd"] set SrcVer [findFiles $SrcDir "*.v"] set SrcNGC [findFiles $SrcDir "*.ngc"] set SrcXCI [findFiles $SrcDir "*.xci"] set SrcXDC [findFiles $SrcDir "*.xdc"] set SrcPCI [findFiles $SrcDir "cl_pcie*"] set NewLoc [string range $SrcPCI 0 [string last / $SrcPCI]-6]

ここではすべてが原始的で明確です-/ srcディレクトリ内のすべてのソースファイルの名前を定義する変数が作成されます。 ファイルを見つけるには、findFilesプロシージャを使用します。これは後で戻ります。

PCI-Eノードのコンポーネントを個別に検索します。これは、すべてのプロジェクトの基本的かつ不可欠な部分です。

# Stage 4: Find all subdirs for IP cores (VHD, XCO, NGC, EDN) set PrjAll {} lappend PrjAll $DirIps $DirAdm $SrcDir/core_v2_ise $SrcDir/core_v4_ise $SrcDir/core_v5_ise $SrcDir/core_v6_ise $SrcDir/core_k7 $SrcDir/TestBench set SrcSim {} for {set i 0} {$i < [llength $PrjAll]} {incr i} { set SrcXXX [findFiles [lindex $PrjAll $i] "*.vhd"] put $SrcXXX foreach SrcAdd $SrcXXX { lappend SrcSim $SrcAdd } }

次の段階で、プロジェクト内のすべてのIPコアが検索されます。 さらに、モデリングに使用されるファイルの名前は、SrcSim変数に書き込まれます。 ループ内のlappendコマンドは、他の値を変数に追加し、TCLではシートと呼ばれる配列を形成します。 これで、スクリプトの準備部分が終了し、プロジェクトの作成が開始されます。

# Stage 5: Create project and add source files create_project -force $TopName $VivDir -part $PartDev set_property target_language VHDL [current_project] add_files -norecurse $SrcNGC add_files -norecurse $SrcXCI export_ip_user_files -of_objects [get_files $SrcXCI] -force -quiet add_files $SrcVHD add_files -fileset constrs_1 -norecurse $SrcXDC

プロジェクトを作成し、最上位ファイルを定義し、FPGAチップのタイプ(この例ではKintex-7 K325T)を設定し、見つかったソースファイルを追加します。

# Stage 6: Set properties and update compile order set_property top $TopName [current_fileset] for {set i 0} {$i < [llength $SrcSim]} {incr i} { set_property used_in_synthesis false [get_files [lindex $SrcSim $i]] } set NgcGlb [findFiles $DirIps "*.ngc"] for {set i 0} {$i < [llength $NgcGlb]} {incr i} { set_property IS_GLOBAL_INCLUDE 1 [get_files [lindex $NgcGlb $i]] } set_property IS_GLOBAL_INCLUDE 1 [get_files $SrcPCI]

シミュレーションファイルのオプションを設定し(合成から除外)、PCI-Eノードで使用されるコアのGLOBAL_INCLUDEパラメーターを設定します(これはプロジェクトに必要な特定の機能です)。

# Stage 7: Upgrade IP Cores (if needed) report_ip_status -name ip_status set IpCores [get_ips] for {set i 0} {$i < [llength $IpCores]} {incr i} { set IpSingle [lindex $IpCores $i] set locked [get_property IS_LOCKED $IpSingle] set upgrade [get_property UPGRADE_VERSIONS $IpSingle] if {$upgrade != "" && $locked} { upgrade_ip $IpSingle } } report_ip_status -name ip_status

この段階で、プロジェクトのIPコアがXCI形式で検索され、カーネルバージョンの更新の必要性とロックされたパラメーターがチェックされます。これはFPGAチップの変更の影響を受けます。 カーネルの分析後、更新が行われ、正常に完了した操作に関するレポートが発行されます。

# Stage 8: Set properties for Synthesis and Implementation (Custom field) set_property strategy Flow_PerfOptimized_high [get_runs synth_1] set_property strategy Performance_ExtraTimingOpt [get_runs impl_1] launch_runs synth_1 wait_on_run synth_1 open_run synth_1 -name synth_1 launch_runs impl_1 -to_step write_bitstream wait_on_run impl_1

合成およびトレース設定がセットアップされる最終段階では、利用可能なリストから戦略を選択します。 次に、FPGAファームウェアが完全に配線されるまで、合成、配置、トレースが1つずつ開始されます。

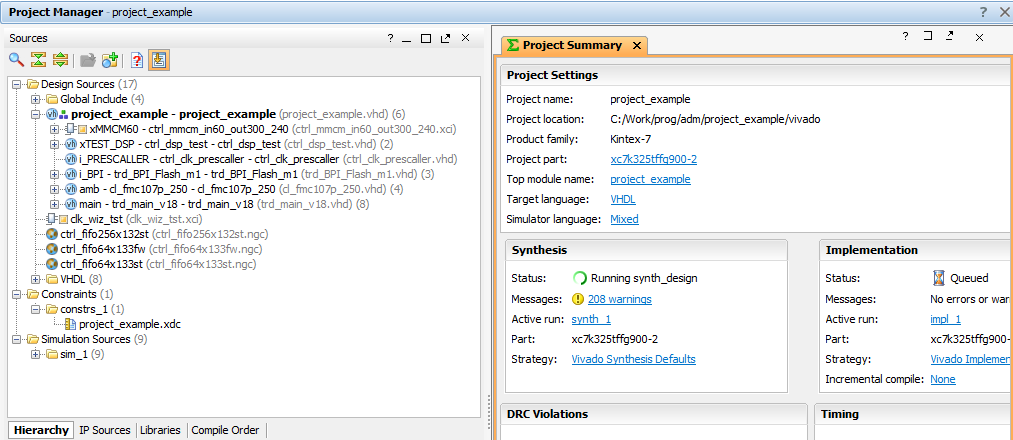

ご覧のとおり、スクリプトを使用すると、プロジェクトの作成、新しいファイルの追加、IPコアの更新など、同じ種類の多くの面倒な作業からユーザーを救うことができます。 スクリプトは完全に自動化されており、単一の引数-FPGAチップのタイプをインストールする必要があります。 ファイル内の変数、またはTCLスクリプトの起動と同時に実行される引数として設定できます。 次の図は、スクリプトを使用して起動されたVivado環境のプロジェクトワークスペースのスクリーンショットを示しています。

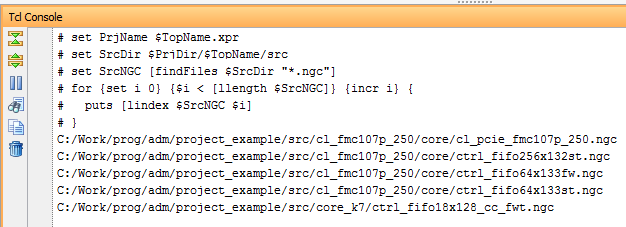

それとは別に、ディレクトリ内のすべてのファイルを検索できるfindFilesプロシージャに注意する必要があります。 関数の引数: basedir-検索ディレクトリ、 pattern-検索マスク。

proc findFiles { basedir pattern } { set basedir [string trimright [file join [file normalize $basedir] { }]] set fileList {} foreach fileName [glob -nocomplain -type {fr} -path $basedir $pattern] { lappend fileList $fileName } foreach dirName [glob -nocomplain -type {dr} -path $basedir *] { set subDirList [findFiles $dirName $pattern] if { [llength $subDirList] > 0 } { foreach subDirFile $subDirList { lappend fileList $subDirFile } } } return $fileList }

検索はいくつかのステップで実行されます:作業ディレクトリをファイルテンプレートとして決定し、フルパスでファイル名でリストを作成し、見つかったファイルが複数ある場合はリストタイプリストの配列を形成します。 findFiles関数の例を次の図に示します。 明確にするために、見つかったすべてのファイルを表示するサイクルが記述されています。 ご覧のとおり、各ファイルへのフルパスが示されています。

スクリプトは、コマンドラインから、またはVivadoアプリケーションGUIを使用して実行されます。 最初のケースでは、Vivado TCLシェルを実行し、簡単なコマンドを記述する必要があります

vivado –mode tcl –source %full_path/example.tcl

注:起動モードをguiに変更して、コマンドラインからグラフィカル環境を開始することもできます。

Vivado環境では、スクリプトは単純な方法で実行されます 。 メニュー->ツール-> TCLスクリプトの実行...

これで、TCL言語の紹介は完了です。 プロジェクト自動化の可能性はこれで終わりではありません。 この簡単な例では、TCLスクリプトを使用して、FPGAデザインを自動化する方法を示したいと思いました。 TCLは非常に便利で、理解しやすく、そして最も重要なこととして、オープンに使用できます。 個人的な見積もりによると、開発者の生活におけるスクリプトの実装により、プロジェクトを初期段階から最終段階まで完全に作成するのにかかる時間を数回短縮でき、「クリーンな」開発(コードの作成)に時間をかけることができます。 以下は、FPGAでTCLスクリプトを調べるのに役立つリンクです。

参照:

- Vivado Design Suiteユーザーガイド-Tclスクリプトの使用

- Vivado Design Suite Tclコマンドリファレンスガイド

- TCLチュートリアル

- RoverプロジェクトでTCLを使用する

- FPGA静的時間分析

- SOCを上げる:ARM + FPGA

ご清聴ありがとうございました!