ネットワークデバイスの操作では、コントロールプレーン(コントロールプレーン)と送信レベル(データプレーン)の2つの抽象化を区別できます。 コントロールプレーンは、ネットワークデバイスのロジックを担当して、将来のパケット送信の可能性を保証します(たとえば、ルーティング、さまざまなサービスプロトコルARP / STP /などのさまざまなテーブルへの入力)。 また、データプレーンは、ネットワークデバイスを介して有用なトラフィックを送信する役割を直接果たします。 つまり コントロールプレーンは、ネットワークトラフィックの送信場所と送信方法に関する情報を提供し、データプレーンは割り当てられたタスクを既に実行しています。 抽象化データは、論理レベルと物理レベルの両方で区別できます。 しかし、ネットワーク機器には常にそのような分離があり、各抽象化の機能は正確にどこで実行されますか? これを理解してみましょう。

この分離は、ネットワークデバイスのパフォーマンスを改善するためにずっと前に登場しました。 1つの抽象化を使用してネットワークトラフィックを管理および送信することは非効率的であることが明らかになりました。 制御レベルにはかなり複雑な作業ロジックがあり、1秒あたりの膨大な数の操作は実行されません。 反対に、送信レベルは比較的均一な操作を実行しますが、多くの操作があります。 したがって、制御レベルにはインテリジェントなハードウェアが必要であり、トランスミッターには高性能が必要です。 1つのチップで両方のパラメーターを実現することは困難であり、多くの場合費用がかかるため、ネットワークデバイスのロジックを分割することにしました。 これにより、たとえば汎用プロセッサに基づいて複雑なロジックを実装し、特殊なマイクロ回路で高いパフォーマンスを得ることができます。 ネットワーク機器メーカーの前では、機能とパフォーマンスはスケールの一方にあり、ソリューションのコストは他方にあります。 さまざまな種類のネットワークデバイス(スイッチとルーター)の例によって、制御と送信レベルの職場を検討することを提案します。 ネットワークエンジニアとして働くとき、デバイスのハードウェアを常に深く掘り下げるとは限りません。 ただし、デバイスの適切な選択、ネットワーク設計、およびネットワークの問題を解決するためには、アーキテクチャの一般原則を理解することが必要です。

ソフトウェア定義型ネットワーク(SDN)に目を向けると、一般に制御レベルが完全にまたは部分的に専用デバイスに転送されていることがわかります。 ただし、このような決定の検討はこの記事の範囲外です。

スイッチ

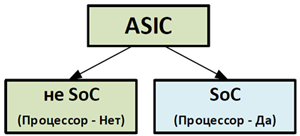

スイッチから始めましょう。なぜなら、ここでは抽象化を最も視覚的に分離できるからです。 スイッチの主なものは、データ転送速度です。 すべてのパケット処理はポート速度(ワイヤ速度)で実装する必要があります。そうしないと、スイッチがネットワークのブレーキ要素になります。 この点で、個別のマイクロ回路-ASIC(ASIC-特別な目的のための集積回路)で送信レベルの実装を見つけることができるのはスイッチです。 実際、スイッチでは、制御レベルは汎用プロセッサに基づいており、すでに述べたように、送信レベルはASICに基づいています。

ネットワーク機器にインストールされているプロセッサは、多くの場合、PCやサーバー上のプロセッサとは異なります。 これらは、多くの場合、さまざまなデバイス(ネットワーク、ストレージシステムなど)内で使用されるように設計された専用プロセッサであり、組み込みプロセッサのクラスに属します。 通常、それらはサイズが小さく、ほとんどエネルギーを消費せず、シングルチップシステム(チップオンシステム-SoC)の一部です。 SoCは、単一のマイクロサーキット((マイクロ)プロセッサー、RAM、I / Oコントローラー、インターフェースなど)に基づいて作成されたほぼ完全なコンピューターです。 これらのプロセッサの一部は、ネットワークデバイス上で操作を実行することを目的としており、他のプロセッサはより広範なアプリケーションを備えています。 この場合、ほとんどの場合、それらは主に汎用プロセッサのままであるため、たとえばUnix / Linuxベースのソリューションなどで実行できます。

クラシックASICには、ハードウェアで実行される定義済みの機能セットがあります。 実際、パケット処理の一般的なロジックは、チップの製造段階でASICに組み込まれていますが、変更は困難です。 ASICでは、許容可能なレベルのロジックと、高いパケット処理速度が得られます。 したがって、ASICで伝送層の機能を実行することにより、スイッチの高性能が実現されます。 また、スイッチのロジックが比較的制限されている理由はASICであり、これをさらに変更することは困難です。 ASICを使用する代わりに、再プログラム可能なFPGA(Field-Programmable Gate Array)を使用できます。 しかし、それらは高価でエネルギー集約型です。 したがって、ネットワーク機器の製造業者は、デバイスのコストを増加させないために、一方でパケット処理の一部を汎用プロセッサー(つまり、制御レベルが機能する場所)に転送しようとしますが、これは常にデバイスのパフォーマンスに良い影響を与えません。 一方、彼らはASICをアップグレードして、より機能的でプログラム可能なものにしようとしています(たとえば、Cisco ASIC UADP)。

ご注意

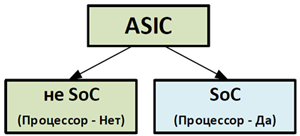

頭字語ASICは、頭字語SoCと組み合わせて使用される場合があります。 マイクロプロセッサとメモリがあるASICが実際にSoCソリューションになるため、ここで簡単に混乱する可能性があります。

これは少し簡略化された表現ですが、一般的な理解のためには十分だと思います。 したがって、従来のASICはより具体的な操作を実行し、SoCはより一般的です。そこにはプロセッサがあります。

これは少し簡略化された表現ですが、一般的な理解のためには十分だと思います。 したがって、従来のASICはより具体的な操作を実行し、SoCはより一般的です。そこにはプロセッサがあります。

通常、スイッチには1つ以上のASICがあります。 たとえば、12/24ポートごとに独自のASICがインストールされます。 ASICの動作ロジックのプログラミングは、制御レベルによって実行されます。 ASIC内のすべてのテーブル(ルート、アクセスリストなど)を埋めるのは彼です。 ASICは、パケットを内部でスイッチングするのに十分なインテリジェンスであるか、外部バス/スイッチングファクトリを介してパケットをスイッチングする場合があります。 このアーキテクチャは、主に固定構成スイッチ(モジュラーではない)で使用されます。 そのようなスイッチの例は、Cisco Catalyst 2960/3650/3850です。

ご注意

この記事では、ほとんどの場合、Ciscoデバイスが例として使用されます。 これは、このメーカーがすべてのデバイスのハードウェアアーキテクチャに関する十分に詳細な情報を提供している数少ないメーカーの1つであるためです。

この記事に記載されているスイッチとルーターの構造図は、主に制御レベルと送信レベルの場所に焦点を当てるために簡略化されています。 デバイスのすべての構造要素が含まれているわけではありません。

モジュラースイッチ(さまざまなタイプのポートを備えたボードをインストールできるスイッチ)を扱っている場合、アーキテクチャはより複雑になる可能性があります。 ポートが増えると、パフォーマンスとASICが増えます。 このようなスイッチのアーキテクチャを実装するには、少なくとも2つのアプローチがあります。

前者の場合、送信層は、別のボードにある専用ASICで集中的に実行されます。 この場合、ラインカード上のASICはそれほどインテリジェントではなく、非常に限られた機能セットを実行します。 制御レベルは引き続きプログラミングロジックに関与し、プログラミングロジックはハードウェア容量で起動されます(再び、別のモジュール(スーパーバイザー)にある汎用プロセッサが使用されます(さらに、複数存在する可能性があります))。 このようなスイッチの例は、Cisco Catalyst 4500およびCisco Catalyst 6500/6800(セントラルスイッチング)です。

*ラインカードにインストールされたポートASICチップは、高度なインテリジェンスを持たず、非常に限られた機能セットを実行します

ご注意

私の意見では、伝送層に専用ASICを使用するのは、各ラインカードのポートにサービスを提供する十分にスマートなASICを使用するよりも、モジュラースイッチ全体に1つまたは2つのインテリジェントASICを配置する方が安価であるという事実によるものです。 さらに、これにより、デバイスのライフサイクルを延ばすことができます。さらに、中央のASICでボードを変更すると、古いラインカードを使用してデバイスに新しい機能を追加できます。

リニアポートを備えた各モジュールが専用の伝送ボードを備えている場合は、バリエーションが可能です。 この場合、各モジュールには独自の送信レベルがあり、「ボックス」全体のパフォーマンスを向上させることができます。 これは、モジュラースイッチのアーキテクチャを実装するための最初のアプローチと2番目のアプローチの中間オプションであると言えます。 このようなスイッチの例は、Cisco Catalyst 6500/6800(分散スイッチング)です。

*ラインカードにインストールされたポートASICチップは、高度なインテリジェンスを持たず、非常に限られた機能セットを実行します

2番目のアプローチは、ラインカードでかなりインテリジェントなASICを使用することです。 この場合、各ASICはネットワークトラフィックを個別に処理し、基本的な機能セットを実行できます。 つまり すぐに分散送信層ができます。 これは、より高価なソリューションになる可能性がありますが、多くの場合、より生産的です。 このアーキテクチャにより、パケット転送の遅延も最小限に抑えられます。 このようなスイッチの例は、Cisco Nexus 9500です。

モジュラースイッチのアーキテクチャは非常に複雑になる場合があります。 特に、単一のラインカード内で複数の異なるASICを使用して、伝送層を実装できます。 それぞれが独自の範囲のタスクを実行するか、下位ASICを統合します。 スイッチングファクトリは、ラインカード間の通信機能と特定のタイプの処理の両方を実行するASICに基づいて構築することもできます。

スイッチでは、制御レベルの分布を設定できることに注意してください。 たとえば、Cisco Nexus 9500スイッチでは、1つのデバイス内の制御レベルが分離されています。一部の機能はスーパーバイザで実行され、一部はラインポートボードで実行されます(各ボードには独自の汎用プロセッサがあります)。

ここまでは、すべての考慮事項が1つのデバイスのフレームワーク内で行われていました。 ただし、スタッキングを使用して、多くのスイッチを1つの論理デバイスに結合できます。 スイッチのスタックを組み立てた場合、制御レベルは通常メインスイッチで起動されます(アクティブ/マスターとも呼ばれます)。 また、送信レイヤーはスタック内の各スイッチで個別に起動されます。 つまり スタック通信チャネルを介して、メインスイッチにある制御レベルは、スタック内のすべてのスイッチに制御情報を配信し、送信レベルがローカルで機能するようにします。 このような作業モデルの例は、Cisco StackWiseスタックまたはHPE IRFです。

ルーター

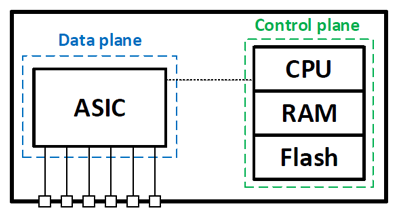

ここで、ルータの抽象化で物事がどのようになっているかを見てみましょう。 比較的低コストのルーターを検討する場合、制御および伝送レベルは同じハードウェア(汎用プロセッサ(ほとんどの場合SoC形式))で実行されます。 この場合、プロセッサ時間は両方の抽象化の間で分配されます。 スイッチのように、伝送層用の特殊なマイクロ回路は見つかりません。 この点で、デバイスの非常に柔軟なロジックが得られますが、最も優れたパフォーマンス値(1秒あたり数十および数百メガビット)は得られません。 さらに、ベンダーのさまざまなトリック(たとえば、シスコエクスプレスフォワーディング)は、標準のハードウェアベースに基づいたソフトウェアレベルでのパケット処理の最適化にすぎません。 そのようなデバイスの例としては、Cisco 800、1900、2900などがあります。汎用プロセッサがマルチコアになると(たとえば、Cisco ISR 4300で)、状況によって変わります。また、そのようなプロセッサが複数ある場合もあります(たとえば、Cisco ISR 4400で)。 この場合、制御と送信レベルは異なるコアとプロセッサで実行できます。 さらに、パケットの並列処理を受信するために、複数のコアが一度に送信レイヤーに割り当てられます。これは、デバイスのパフォーマンスを向上させることを意味します。 一部のコアは一般にサードパーティのサービスに提供できることに注意してください(もちろん、プロセッサが許可している場合)。

最新のSoCにはマルチコアプロセッサが搭載されています。 48コアは誰も驚かないでしょう。 また、SoCに統合されたバッチ処理アクセラレータと組み合わせると、1つのSoCに基づいて非常に優れたパフォーマンスを得ることができます。市場には、最大40 Gb / sの速度でネットワークトラフィックを処理できるSoCソリューションがあります。

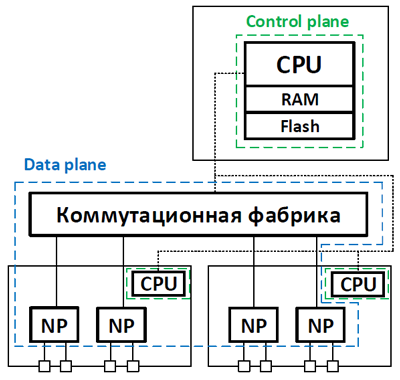

別の会話は、高性能ルーターです。 この場合、従来の汎用プロセッサの容量では不十分な場合があります。 ネットワーク機器の製造業者は、伝送層を別のハードウェアに転送し、より多くのトラフィックフローを処理するように適合させます。 実際、スイッチアーキテクチャに移行しています。 ただし、ルーターはより機能的であるため、通常のASICでは十分ではありません。 この点で、各メーカーは独自のソリューションを提供しています。

1つのオプションは、特殊なネットワークプロセッサ(ネットワークプロセッサ-NPまたはネットワーク処理ユニット-NPU)を使用することです。 ネットワークプロセッサはASICよりもかなり機能的ですが、汎用プロセッサよりも生産的です。

ご注意

最新のネットワークプロセッサは、主にRISCアーキテクチャに基づいて構築されており、次のような類似の特性があります。

- プログラム可能-L2 / L3の標準ネットワーク機能に限らず、さまざまなサービス(ITU、IPSec、NATなど)を実行できます。 また、プログラマビリティにより、ハードウェアを交換せずに新しい機能を追加できます。

- マルチスレッド-スレッド数は数百単位で測定されます(プロセッサはマルチコアであるため)。これにより、パフォーマンスを向上させることができます。

- エネルギー効率-従来のプロセッサと比較した場合、ネットワークプロセッサは最高のスループット/ワット比を提供します。 このパラメータは、主にデバイスのラインカードのポートの密度に影響します。

例として、伝送層の主な機能が別のボードで実行されるCisco ASR 1000ルーターを考えます。 このボードには、トラフィックの処理に直接関与する1つまたは2つの専用ネットワークプロセッサCisco QuantumFlow Processor(QFP)があります。 このプロセッサにはRISCアーキテクチャがあり、特にトラフィック転送用に設計されています。 第2世代のQFPには最大128のプロセッサコアが含まれ、それぞれが4つの個別のプロセスを実行できます。 つまり 1つのボードに最大256個のコアがあります(2つのプロセッサの場合)。 すべてが複数のコアで実行される単純なルーターのアーキテクチャと比較すると、そのようなルーターは生産性が高いとすぐに結論付けることができます。

ネットワークプロセッサは、さまざまな企業(Cisco、EZChip、Broadcomなど)によって製造されており、ネットワーク機器の多くのメーカーが伝送層の機能を実行するために使用されます。 たとえば、ネットワークプロセッサは、Huawei機器で使用されます(たとえば、NetEngine40EなどのルーターとS12700スイッチの両方で)。

ご注意

多くの場合、高性能スイッチ(大規模ネットワークのコアへのインストール用に設計された)を構築する際のネットワーク機器のメーカーは、高性能ルーターのアーキテクチャを基礎として使用します。 この場合、スイッチとルーターの区別があいまいになります。

ネットワークプロセッサに加えて、ジュニパートリオチップセットなどの特殊なチップセットが市場に出回っています。 ネットワークプロセッサとASICの間に配置されます。 概して、一般的な意味は変わりません。送信レベルは、特殊なハードウェア(この場合はTrioチップセットチップセット)で実行されます。 Trioチップセットを発売する前に、ジュニパーはルーターで独自のプログラマブルASIC(インターネットプロセッサASICおよびI-Chip)を積極的に使用していました。

最上位のソリューションでは、異なる鉄の間で制御と伝達のレベルを分離するだけでなく、各レベル内の分布も持つことに注意してください。 たとえば、Cisco ASR 9000ルータでは、1つのデバイス内の制御レベルには間隔があります。機能の一部はプロセッサボードで実行され、一部はラインポートボードで実行されます。 同じことが送信レベルにも当てはまります。多くのネットワークプロセッサがあり、それらはラインカードに直接配置されています。

結論として

1つのベンダーでも多くのアーキテクチャを実装しているため、それらをすべて考慮することは非常に困難です。 ただし、さらにパフォーマンスが必要な場合は、ネットワークプロセッサ、特殊なチップセット、通常またはプログラム可能なASICなど、特殊なハードウェアで送信レイヤーが実行されることがほとんどです。 一部のデバイスでは、これらの超小型回路の組み合わせもあります。 多くの場合、自社の機器のネットワーク機器のメーカーは、サードパーティのマイクロサーキット(たとえば、ASICやネットワークプロセッサ)を使用しています。