HP 3PAR StorServコントローラーボックス

従来のモジュラーおよびモノリシックアレイと比較したHP 3PAR StorServの機能は、負荷の急激な増加、アレイコントローラーの均一な負荷、および高いシステムフォールトトレランスを備えた安定したパフォーマンスを提供する完全接続フルメッシュアーキテクチャの使用であることを思い出してください。 フルメッシュのおかげで、アレイ内の各論理ボリュームは、そのすべてのコントローラーによって同時に提供されます。 フルメッシュを使用する古いHP 3PAR StorServモデルでは、最大8つのアレイコントローラーが単一のシステムに結合され、若いシステムでは最大4つが結合されます。 HP 3PAR StorServのもう1つの機能は、コントローラーで特殊なThin Express ASICチップを使用することです。これは、ハードウェアレベルで、コントローラーが従来のアレイで実行するストレージ管理機能(RAIDチェックサム計算など)を実装します。 ASICはデータとメタデータを独立して処理し、アレイの応答時間を短縮します。 Thin Express ASICを使用すると、コントローラーの中央処理装置の負荷が軽減されるため、アレイの全体的なパフォーマンスが向上し、データアクセスのアプリケーションからの要求処理の遅延が軽減されます。 最後に、HP 3PAR StorServの3番目の機能は、Thin Express ASICの実装です。ThinExpress ASICは、3PARアーキテクチャに元々組み込まれていたシンプロビジョニングの動的プロビジョニングから始めて、さまざまな「シン」テクノロジーのストレージ効率とディスクスペース使用率を改善します。

新ラインナップ

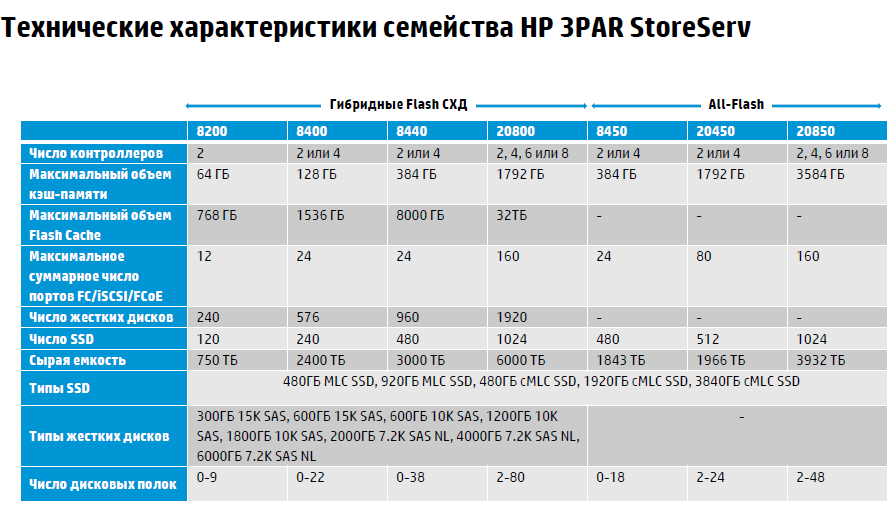

HP 3PAR StorServのアップグレードは2つのステップで行われました。 最初に、6月1日にラスベガスのHP Discoverで、HP 3PAR StorServ 20000シリーズの2つの上級モデルが発表され、8月26日に、HP 3PAR StorServ 8000シリーズの4つの若いモデルと20000シリーズの別のモデルの発表が発表されました。

新しいアレイの前世代のHP 3PAR StorServと比較すると、オプションのソリッドステートドライブはメインタイプのドライブになりました。 3つのオールフラッシュモデルは、最大数が「50」(8450、20450、20850)で終わる最大パフォーマンスの取得に焦点を当てており、SSDドライブのみを使用し、従来のハードドライブはサポートされていません。 他の4つのモデル(8200、8400、8440、および20800)は、ソリッドステートドライブとハードドライブの組み合わせ用に設計されたハイブリッドアレイです。 小規模モデル8200および8400は、IT予算が限られているお客様向けに設計されており、より強力なHP 3PAR StorServ 8440および20800は、最大容量のスケーラビリティを必要とするお客様向けに設計されています。

ラックHP 3Par StorServ 20000

前世代のHP 3PAR StorServの最大ソリッドステートドライブ容量が1.92 TBであった場合、新しいモデルは3.84 TBの容量のSSD商用MLC(cMLC)ドライブをサポートします。 マルチテラバイトのcMLCを使用すると、ソリッドステート構成のスケーラビリティとソリッドステートメモリの密度が向上し(デュアルユニットディスクシェルフに収まる使用可能容量280テラバイト、1ラックに5.5ペタバイトの使用可能容量)、フラッシュメモリ容量1ギガバイトのコストも削減されました。 HP 3PAR StorServで使用されるさまざまなテクノロジー、新しいcMLCを使用する際のフラッシュメモリのより効率的な使用(アダプティブスペアリング、シンプロビジョニング、重複排除)を考慮すると、1 GBのデータを保存するコストは10K RPMハードドライブよりも低くなります。

HP 3PAR StorServ 8000および20,000は、容量の増加したSSDに加えて、ハードウェアを大幅にアップグレードしました。最新のIntel Xeon Ivy Bridgeプロセッサーがコントローラーにインストールされ、キャッシュサイズが増加し、システムバスはPCI Express Gen3に基づいており、内部インターコネクトとして12ギガビットSASが使用されています、およびアレイの光ポートは16ギガビットファイバチャネルをサポートします。 HP 3PAR StorServソフトウェアの強化と、HP 3PAR Gen5 Thin Express ASICの2倍強力な第5世代の新しいチップと組み合わせることで、HP 3PAR StorServ 20000は、応答時間0.2〜0.8で320万IOPSを実現しました。最大75 GB / sのミリ秒と帯域幅、および最大15ペタバイトの使用可能な容量の1つのシステムのスケーラビリティ。 したがって、HP 3PAR StorServのマルチコントローラーメッシュアーキテクチャにより、ソリッドステートメモリの使用に切り替えたときに最大のパフォーマンスゲインを得ることができます。 さらに、ストレージフェデレーションの組み込み機能により、特別なハードウェア「ストレージバーチャライザー」を使用せずに最大4つのHP 3PAR StorServアレイと最大60 Pバイトの有効容量を組み合わせることができ、8から2万のモデルとモデルの両方が1つの「フェデレーション」の一部として機能します前世代。

新しいHP 3PAR StorServ機能

HPのエンジニアは、HP 3PAR OS 3.2.2オペレーティングシステムの機能に多くの新しいテクノロジーを追加し、ディスクスペースの効率を向上させ、データセキュリティと常時可用性を確保する追加の手段を実装しています。

シン重複排除

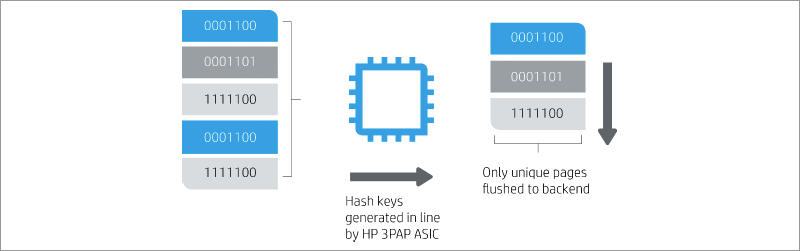

HP 3PAR Gen5 Thin Expressチップを使用して、シン重複排除が実装され、同じデータの再記録を防止することでアレイの容量を節約します。 シン重複排除はオンラインで機能し、アレイコントローラーの中央処理装置を使用しないため、アレイへのデータの書き込み操作に最小限の遅延が発生します。 ディスクアレイで重複排除を提供するほとんどのベンダーとは異なり、HPは、アプリケーションが可能な限り最高の書き込み速度を提供する必要がある場合や、データの再現性が低いために重複排除の使用が意味をなさない場合に、シン重複排除を無効にするオプションをサポートしています。

ASICは、ハッシュ署名を生成し、各着信書き込み要求に割り当てます。 HP 3PAR StoreServは、HP 3PAR Express Indexing Indexing Engineを使用します。これにより、テーブル検索が高速化され、以前に行われた同一の書き込み要求を非常にすばやく見つけることができます。 新しい書き込み要求がシステムに届くと、Express Indexingはメタデータで検索し、この要求の署名を以前の書き込み操作の署名と比較します。 同一のクエリが見つかった場合、システムは新しいクエリに重複のフラグを立て、アレイディスクに同一のデータを再書き込みする代わりに、アレイに既に保存されているデータブロックへのポインタがメタデータテーブルに書き込まれます。 ハッシュの競合を防ぐために、ASICは新しい書き込み要求を重複としてマークする前にビットごとの比較を実行します。

ASICが生成するオンライン重複排除

永続的なチェックサム

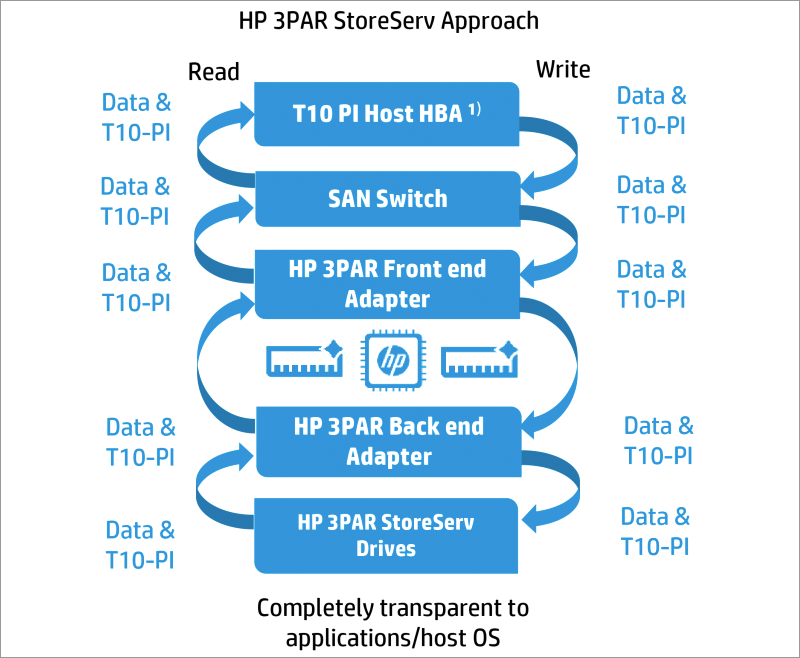

アレイコンポーネント内のデータ転送中にデータの整合性を確保するために、HP 3PAR StoreServの新世代は、T10-PI(保護情報)データ保護標準の要件に従って動作する3PAR Gen5 Thin Express ASIC内のハードウェアレベルで実装された永続的チェックサムメカニズムを使用します。 永続的チェックサムは、「見えない破損」からデータを保護するように設計されています。「目に見えない破損」は、サーバーHBAからアレイHBAアダプターにサーバーHBAからソリッドステートドライブへ/からデータを転送するときにI / Oスタックの個々のコンポーネントの障害によって発生する可能性があります。 永続的チェックサムは、ホストアプリケーションおよびオペレーティングシステムに対して完全に透過的に機能し、HBAアダプターおよびサーバーハードウェアドライバーと統合されます。これにより、サーバーからHP 3PAR StoreServドライブまでのデータ整合性チェックが保証されます。

T10-PIは、ディスクの各セクターにオプションの8バイトのデータ整合性フィールド(DIF)を備えたデータ保護の追加レイヤーを提供するSCSI標準です。 通常、正常なディスク読み取りの結果として取得されたデータは正しいと見なされ、それを要求したホストにすぐに転送されます。 T10-PIは、ホストに転送される前にディスクから読み取られたデータの検証を実装します。 書き込み要求の場合、T10-PIを使用すると、ホストが記録のために送信したデータが正確にSSDに書き込まれます。 データの破損が検出されると、HP 3PARオペレーティングシステムは書き込み要求にエラーメッセージで応答し、ホストは再び書き込み要求を発行します。

永続的なチェックサムデータ整合性チェッカー

非同期ストリーミングレプリケーション

ハードディスクを使用する場合、データ要求への応答時間が数十ミリ秒で測定されると、リモートアレイへの同期レプリケーションによって生じる遅延はSLAの観点から許容されます。 ただし、フラッシュメモリに切り替えると、応答時間が1ミリ秒未満に減少すると、同期レプリケーションによる遅延がアプリケーションデータへのアクセスを大幅に「遅く」するため、HP 3PAR Remote Copyリモートレプリケーションパッケージに非同期ストリーミングモードのサポートが追加されました。リモートアレイには、数秒以内の回復ポイント(RPO)でデータのほぼ正確な(ほぼ正確な)コピーがあります。 非同期ストリーミングレプリケーションを使用すると、このデータを使用するアプリケーションのパフォーマンスを犠牲にすることなく、メインデータセンターで重大な事故が発生した場合にデータの可用性が確保されます(この新しいモードに加えて、HP 3PAR Remote Copyは3つのデータセンター間の同期および定期的な非同期レプリケーションをサポートします)。

HP 3PAR 8000および20,000のその他の新機能のうち、Peer Motionを使用した4つのアレイのフェデレーション間でのボリュームの双方向移動の実装と、Thin Express ASICレベルで実装されているこのテクノロジーを使用して、廃止された日立製アレイ(以前のPeer Motion EMCアレイからのインポートのみがサポートされています。 更新されたPriority Optimizationソフトウェアを使用すると、ターゲットアクセス時間を最大0.5ミリ秒に設定して、重要なビジネスアプリケーションに必要なレベルのサービスを提供できます。

さらに、3PAR StoreServ用のStoreOnce Recovery Manager Central for VMware(RMC-V)仮想マシンのバックアップおよび復元パッケージは、仮想マシンの一貫したスナップショットを作成し、HP 3PAR StoreServからHP StoreOnceディスクライブラリに自動的にコピーします。 VMware Virtual Volumes(VVOL)を使用したVMware vSphere 6.0のサポートと、個々の仮想マシンおよびファイルの詳細なリカバリ機能を実装しました。 RMC-Vを使用すると、バックアップおよび専用ソフトウェアを管理する専用サーバーに基づく従来の方法と比較してバックアップコストが削減され、階層バックアップからフラットバックアップへの移行により、バックアップ操作が最大17倍、最大5倍に回復それらに仮想マシン。

結論

Gartnerの分析機関からのレポートによると、昨年、HPは主要なストレージ市場のプレーヤーの中で最も高いフラッシュ売上成長を達成しました。 今年の夏に導入された新世代のHP 3PAR StorServは、フラッシュ効率を向上させ、SSDのコストを削減する新機能を組み込んでおり、成長著しいフラッシュ市場におけるHPのリーダーシップを強化します。